# Technical Reference Manual Hardware and BIOS

HP Vectra VL 5/xx series 4 PC and HP Vectra VL 5/xx MT series 4 PC

December 1995

#### NOTICE

Information contained in this document is subject to change without notice.

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated into another language without the prior written consent of Hewlett-Packard Company.

Centronics® is a U.S. registered trademark of Centronics Data Computer Corporation.

LANManager, Microsoft Windows, Windows 95 and OS/2 are products of Microsoft Corporation.

Microsoft® and MS-DOS® are registered trademarks of Microsoft Corporation.

Novell® and Netware® are registered trademarks of Novell Inc.

Pentium<sup>™</sup> is a trademark of Intel Corporation.

©1995 Hewlett-Packard Company

| NOTICE                                                       |          |

|--------------------------------------------------------------|----------|

| PREFACE  OPPERING INFORMATION FOR THE PHOENIX PIOC MANUAL    | <u>5</u> |

| ORDERING INFORMATION FOR THE PHOENIX BIOS MANUAL CONVENTIONS | 5<br>5   |

| BIBLIOGRAPHY                                                 | <u></u>  |

|                                                              |          |

| SYSTEM OVERVIEW 7 SYSTEM OVERVIEW                            | 7        |

| HP VECTRA VL 5/XX SERIES 3 – VL 5/XX SERIES 4 COMPARISON     | 7        |

| HP VECTRA VL 5/XX SERIES 4 DESKTOP – MINI-TOWER              |          |

| COMPARISON                                                   | 8        |

| VL 5/XX SERIES 4 PC BLOCK DIAGRAM                            | 9        |

| PRINCIPAL COMPONENTS AND FEATURES                            | 9        |

| VL 5/XX SERIES 4 SYSTEM BOARD                                | 10       |

| VL 5/XX MT SERIES 4 DESKTOP BACKPLANE                        | 11       |

| VL 5/XX MT SERIES 4 MINI-TOWER BACKPLANE                     | 11       |

| PROCESSOR                                                    | 11       |

| SUPERSCALAR ARCHITECTURE                                     | 12       |

| FLOATING POINT UNIT (FPU)                                    | 12       |

| DYNAMIC BRANCH PREDICTION                                    | 12       |

| INSTRUCTION AND DATA CACHE                                   | 12       |

| DATA INTEGRITY                                               | 13       |

| PCI CHIP SET                                                 | 13       |

| PCI, CACHE AND MEMORY CONTROLLER (82437FX)                   | 14       |

| DATA PATH UNIT (82438FX)                                     | 15       |

| THE PCI/ISA BRIDGE AND IDE CONTROLLER (82371FB)              | 15       |

| THE 82438FX AND 82371FB FEATURE SUMMARY                      | 16       |

| SUPER I/O CHIP                                               | 17       |

| NS PC87332VF FEATURE SUMMARY                                 | 17       |

| FLEXIBLE DRIVE CONTROLLER (FDC)                              | 17       |

| SERIAL/PARALLEL PORTS                                        | 18       |

| GRAPHICS/INTEGRATED VIDEO                                    | 18       |

| IDE TO PCI CONTROLLER                                        | 19       |

| FLASH ROM                                                    | 19       |

| SECURITY FEATURES                                            | 19       |

| PHYSICAL CHARACTERISTICS                                     | 19       |

| ELECTRICAL SPECIFICATIONS                                    | 20       |

| POWER AVAILABILITY (CONTINUOUS OPERATION):                   | 20       |

| ENVIRONMENTAL SPECIFICATIONS                                 | 21       |

| SUMMARY OF THE HP/PHOENIX BIOS 22                            |          |

| HP/PHOENIX BIOS DESCRIPTION                                  | 22       |

| OVERVIEW OF ADDRESS SPACE                                    | 22       |

| I/O ADDRESSES USED BY THE SYSTEM*                            | 22       |

|                                                              |          |

**23**

**BIOS I/O PORT MAP**

| ADDRESSING SYSTEM BOARD COMPONENTS            | 24 |

|-----------------------------------------------|----|

| 3 DESKTOP MANAGEMENT INTERFACE 26             |    |

| DMI INFORMATION STRUCTURE                     | 26 |

| ACCESSING BIOS DMI INFORMATION                | 27 |

| THE DMI HEADER                                | 28 |

| VERIFYING THE DMI INFORMATION STRUCTURE       | 28 |

| DMI SUB-STRUCTURE TABLES                      | 29 |

| 4 POWER-ON SELF-TESTS AND ERROR MESSAGES 32   |    |

| POWER-ON SELF TEST (POST)                     | 32 |

| SHADOW RAM                                    | 32 |

| ERROR MESSAGES                                | 34 |

| BEEP CODES                                    | 36 |

| 5 THE ULTRA VGA VIDEO CONTROLLERS 37          |    |

| THE MATROX MGA MILLENNIUM VIDEO ADAPTER BOARD | 37 |

| VIDEO MEMORY                                  | 37 |

| AVAILABLE VIDEO RESOLUTIONS                   | 37 |

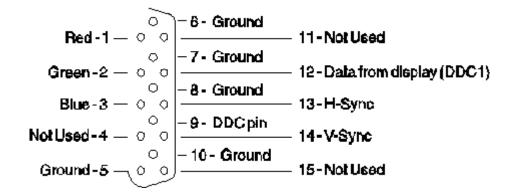

| VESA CONNECTOR                                | 38 |

| FURTHER INFORMATION                           | 38 |

| THE INTEGRATED ULTRA VGA VIDEO CONTROLLER     | 38 |

| VIDEO MEMORY                                  | 39 |

| VIDEO MODES                                   | 39 |

| AVAILABLE BIOS VIDEO RESOLUTIONS              | 42 |

| VESA CONNECTOR                                | 43 |

| DB15 CONNECTOR PINOUT                         | 43 |

| VIDEO CONTROLLER SUMMARY                      | 43 |

#### **PREFACE**

This manual is a technical reference and BIOS document for engineers and technicians providing system level support. It is assumed that the reader possesses a detailed understanding of AT-compatible microprocessor functions and digital addressing techniques.

Technical information that is readily available from other sources, such as manufacturer's proprietary publications, has not been reproduced.

This manual contains summary information only. For additional reference material, refer to the bibliography.

#### ORDERING INFORMATION FOR THE PHOENIX BIOS MANUAL

System BIOS for IBM PCs, Compatibles, and EISA Computers (ISBN 0-201-57760-7) by Phoenix Technologies is available in many bookstores. It can also be ordered directly from the publisher as follows:

#### In the U.S.A.

Call Addison-Wesley in Massachusetts at +1-800-447-2226, and be prepared to give a credit card number and expiry date.

#### In Europe

Send your request to Addison-Wesley at the address given below, and be prepared to give a credit card number and expiry date.

Addison-Wesley Concertgebouwplein 25 1071 LM Amsterdam, The Netherlands Tel: +31 (20) 671 72 96 Fax: +31 (20) 675 21 41

#### **CONVENTIONS**

The following conventions are used throughout this manual to identify specific elements:

- Hexadecimal numbers are identified by a lower case h.

For example, 0FFFFFFFh or 32F5h

- Binary numbers and bit patterns are identified by a lower case b. **For example,** 1101b or 10011011b

# **BIBLIOGRAPHY**

• System BIOS for IBM PCs, Compatibles, and EISA Computers (ISBN 0-201-57760-7) by Phoenix Technologies. Addison-Wesley (publisher).

The following Hewlett-Packard publications may also assist the reader of this manual.

- HP Vectra VL 5/xx series 4 PC User's Guide (supplied with PC).

- HP Vectra VL 5/xx MT series 4 PC User's Guide (supplied with PC).

- HP Vectra VL 5/xx series 4 PC and HP Vectra VL 5/xx MT series 4 PC Familiarization Guide (D3645-90901)

- HP Vectra PC Service Handbook 9th edition (Available January 1996)

The following Intel® publication provides more detailed information:

Pentium Processor (241595-1)

# 1 SYSTEM OVERVIEW

This chapter provides a description of the HP Vectra VL 5/xx series 4 desktop and HP Vectra VL 5/xx MT series 4 mini-tower PC with detailed system specifications.

#### SYSTEM OVERVIEW

The HP Vectra VL 5/xx series 4 PC is a Pentium processor, ISA/PCI-based PC and features the Intel Triton chip set.

#### HP VECTRA VL 5/XX SERIES 3 - VL 5/XX SERIES 4 COMPARISON

|                                   | Vectra VL 5/xx series 3                                                                 | Vectra VL 5/xx series 4                                                                                                                                                         |

|-----------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor                         | Pentium 75 (VL 5/75) Pentium 90 (VL 5/90) Pentium 100 (VL 5/100) Pentium 120 (VL 5/120) | Pentium 90 Pentium 100 Pentium 120 Pentium 133 Pentium 150 Pentium 166                                                                                                          |

| Level-two cache memory            | 256 KB asynchronous cache                                                               | 256 KB synchronous cache                                                                                                                                                        |

| Main memory                       | 8 MB or 16 MB standard<br>192 MB maximum                                                | 8 MB or 16 MB standard<br>128 MB maximum                                                                                                                                        |

| Video controller                  | Cirrus Logic GD 5434<br>integrated on PCI bus                                           | Trio 765 64V+ or 764 integrated on<br>PCI bus or<br>Matrox MGA Millennium video card                                                                                            |

| Video memory                      | 1 MB standard<br>upgradable to 2 MB                                                     | 1 MB standard     upgradable to 2 MB     Matrox Models     2 MB standard     upgradable to 4 MB or 8 MB*                                                                        |

| Enhanced IDE hard disk controller | CMD PCI0640B<br>Integrated on PCI bus<br>dedicated for hard disk drives                 | Integrated in chip set (part of 82371FB multipurpose chip) Integrated on PCI bus Primary channel dedicated for hard disk drives Secondary channel recommended for CD-ROM drives |

| Secondary IDE controller          | Integrated in NS 87332 Super I/O chip on ISA bus dedicated for CD-ROM drives            | No secondary IDE controller<br>(Two channels on enhanced IDE<br>controller - see above)                                                                                         |

| Flexible disk controller          | Integrated in NS 87332 Super I/O chip on ISA bus                                        | Integrated in SMC 932 Super I/O chip on ISA bus                                                                                                                                 |

| Serial / parallel port controller | Integrated in NS 87332 Super I/O chip on ISA bus                                        | Integrated in SMC 932 Super I/O chip on ISA bus                                                                                                                                 |

<sup>\*</sup>The 6 MB video upgrade module is available only from Matrox Electronic Systems Limited.

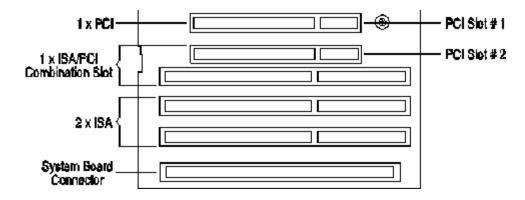

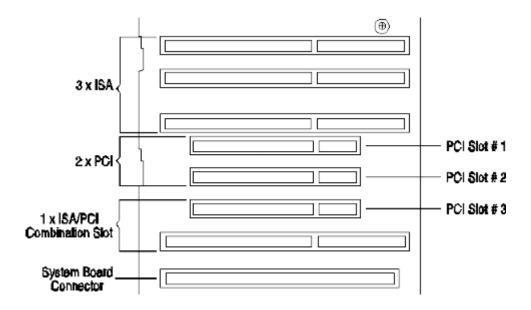

# HP VECTRA VL 5/XX SERIES 4 DESKTOP - MINI-TOWER COMPARISON

|                                                | Desktop                                                                                                                                                            | Mini-Tower                                                                                                                                                 |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDE Controller Primary channel connectors      | Two connectors for hard disk drives                                                                                                                                | Two connectors for hard disk drives                                                                                                                        |

| IDE Controller<br>Secondary channel connectors | One red connector recommended for CD-ROM                                                                                                                           | Two red connectors recommended for CD-ROM and supplementary hard disk drive                                                                                |

| Flexible disk controller connectors            | Two connectors for 3.5-inch flexible disk drive or tape drive                                                                                                      | Two connectors for 3.5-inch flexible disk drive or tape drive One connector for 5.25-inch flexible disk drive Maximum two devices connected simultaneously |

| Accessory board slots (on backplane)           | One 16-bit ISA (short 16cm/<br>6.3-inch)<br>One 16-bit ISA (full-length)<br>One 32-bit PCI/16-bit ISA<br>Combination (full-length)<br>One 32-bit PCI (full-length) | Three 16-bit ISA (full-length) One 32-bit PCI/16-bit ISA Combination (short 16cm/ 6.3-inch) Two 32-bit PCI (full-length)                                   |

| Internal device shelves                        | One for hard disk drive                                                                                                                                            | Two for hard disk drives                                                                                                                                   |

| Front-access device shelves                    | One 3.5-inch<br>One 5.25-inch<br>One 5.25-inch, 1-inch high                                                                                                        | One 3.5-inch<br>Three 5.25-inch                                                                                                                            |

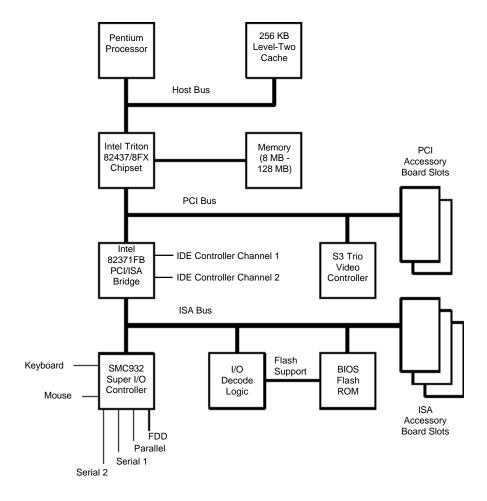

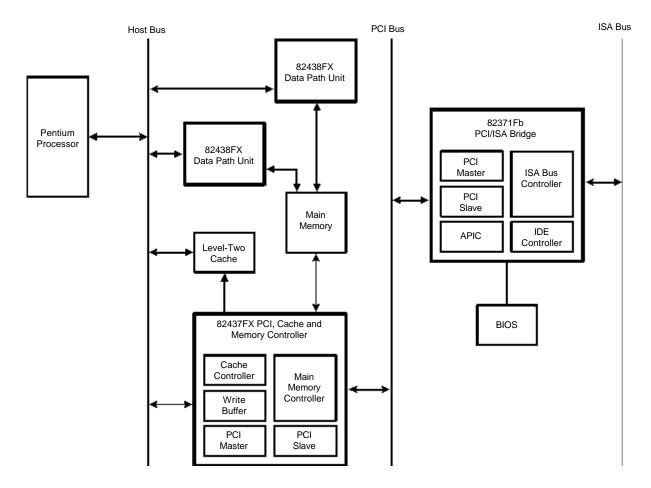

#### **VL 5/XX SERIES 4 PC BLOCK DIAGRAM**

#### PRINCIPAL COMPONENTS AND FEATURES

The main features of the system board are:

- supports Pentium processors of several different clock speeds (90, 100, 120 or 133 MHz, and 150 and 166 MHz when available) with accompanying voltage regulator module (VRM)

- a PCI bus video controller: most models of the Vectra VL 5/xx series 4 have an integrated 64-bit Ultra VGA controller on the PCI bus (S3 Trio 765 64V+ on D3xxxA models and S3 Trio 764 on D3xxxB models)

- an Enhanced IDE controller with two channels on the PCI bus

- a primary IDE channel for two IDE hard disk drives

- a secondary IDE channel for an IDE CD-ROM drive and, in the mini-tower models, a fourth IDE device (such as a third IDE hard disk drive)

- · a combined controller on the ISA bus for

- 2 flexible disk drives and/or tape drives

- 2 serial ports

- 1 parallel port

- sockets for DRAM main memory: the Vectra VL 5/xx series 4 PCs provide six sockets for main memory, allowing installation of up to 128 MB

- a system ROM (using flash ROM technology) that can be easily updated with the latest firmware, using the *Phlash.exe* program supplied with the firmware upgrade. The system ROM contains:

- the BIOS (system BIOS, video BIOS and low option ROM)

- a power-on hardware test that allows you to view the results of the diagnostics as well as a corrective action message (error message utility)

- menu-driven SETUP with context-sensitive help (in US English only)

- a keyboard/mouse controller and interface.

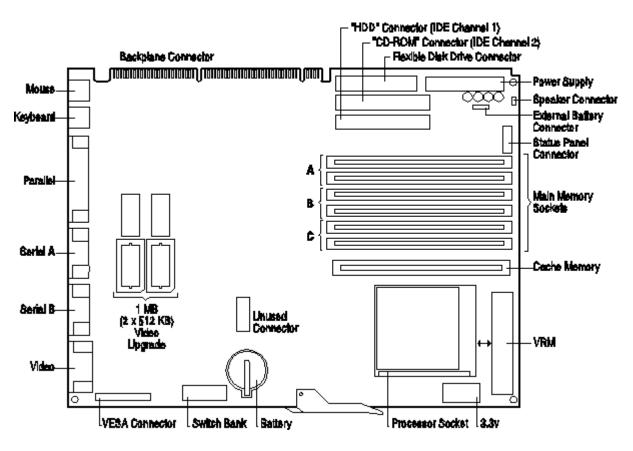

#### **VL 5/XX SERIES 4 SYSTEM BOARD**

<sup>\*</sup>This video upgrade applieso nly to themodels with integrated video controller.

#### **VL 5/XX MT SERIES 4 DESKTOP BACKPLANE**

#### **VL 5/XX MT SERIES 4 MINI-TOWER BACKPLANE**

#### **PROCESSOR**

The Pentium processor uses 64-bit architecture and is 100% compatible with Intel's family of x86 processors. All application software written for Intel386 and Intel486 processors can run on the Pentium without modification. The Pentium processor contains all the features of the Intel 486 processor, with the following added features which enhance performance:

- Superscalar Architecture

- Floating Point Unit

- Dynamic Branch Prediction

- Instruction and Data cache

- Data Integrity

- Supports MultiProcessor Specification (MPS) 1.1

- PCI bus architecture

- Advanced Power Management capability for reducing power consumption

The processor is seated in a Zero Insertion Force (ZIF) socket.

#### SUPERSCALAR ARCHITECTURE

The Pentium processor's superscalar architecture has two instructions pipelines and a floating-point unit, each capable of independent operation. The two pipelines allow the Pentium to execute two integer instructions in parallel, in a single clock cycle. Using the pipelines halves the instruction execution time and almost doubles the performance of the processor, compared with an Intel486 microprocessor of the same frequency.

Frequently, the microprocessor can issue two instructions at once (one instruction to each pipeline). This is called instruction pairing. Each instruction must be simple. One pipeline will always receive the next sequential instruction of the one issued to the other pipeline.

#### **FLOATING POINT UNIT (FPU)**

The Floating Point Unit incorporates optimized algorithms and dedicated hardware for multiply, divide, and add functions. This increases the processing speed of common operations by a factor of three.

#### DYNAMIC BRANCH PREDICTION

The Pentium processor uses dynamic branch prediction. To dynamically predict instruction branches, the processor uses two prefetch buffers. One buffer is used to prefetch code in a linear way, and one to prefetch code depending on the contents of the Branch Target Buffer (BTB). The BTB is a small cache which keeps a record of the last instruction and address used. It uses this information to predict the way that the instruction will branch the next time it is used. When it has made a correct prediction, the branch is executed without delay, thereby enhancing performance.

#### INSTRUCTION AND DATA CACHE

The Pentium processor has separate code and data caches on-chip. Each cache is 8 KB in size with a 32-bit line. The cache acts as temporary storage for data and instructions from the main memory. As the system is likely to use the same data several times, it is faster to get it from the on-chip cache than from the main memory.

Each cache has a dedicated Translation Lookaside Buffer (TLB). The TLB is a cache of the most recently accessed memory pages. The data cache is configured to be Write-Back on a line-by-line basis (a line is an area of memory of a fixed size).

The data cache tags (directory entries used to reference cached memory pages) are triple ported to support two data transfers and an inquire cycle in the same clock cycle. The code cache tags are also triple ported to support snooping (a way of tracking accesses to main memory by other devices) and split line accesses.

Individual pages of memory can be configured as cacheable or non-cacheable by software or hardware. They can also be enabled and disabled by hardware or software.

#### **DATA INTEGRITY**

The processor uses a number of techniques to maintain data integrity. It employs two methods of error detection:

- Data Parity Checking

This is supported on a byte-by-byte basis, generating parity bits for data addresses sent out of the microprocessor. These parity bits are not used by the external subsystems.

- Internally

The processor uses functional redundancy checking to provide maximum error detection of the processor and its interface.

#### **PCI CHIP SET**

The chip set consists of three devices:

- The PCI, Cache, and Memory Controller (82437FX)

- Two Data Path Units (82438FX)

- The PCI/ISA bridge and IDE controller (82371FB)

The 82437FX and 82438FX2 devices provide the core cache and memory system architecture, and the PCI interface.

#### PCI, CACHE AND MEMORY CONTROLLER (82437FX)

The 82437FX device integrates cache and memory control functions and provides bus control functions for the transfer of information between the microprocessor, cache, main memory and the PCI bus. The cache controller supports the Pentium Cache Write-Back mode and 256 KB of direct mapped, write-back level-two cache, using synchronous pipeline burst SRAMs.

#### 82437FX Feature Summary

| Function         | Features                                                                                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache controller | <ul> <li>Direct mapped organization</li> <li>Buffered write-back</li> <li>External cache tags</li> <li>32-byte line size</li> <li>Uses synchronous pipeline burst SRAM</li> <li>Supports 3-1-1-1* burst reads</li> </ul> |

| Write buffer     | <ul> <li>Buffers all processor writes to main memory</li> <li>Buffers memory writes to PCI for selected memory regions</li> <li>Supports 3-1-1-1* write access timing</li> </ul>                                         |

\*The Pentium's internal cache has a 32-byte line size, which is four times the width of the Pentium's host data bus. Burst reads and writes by the Pentium involve a full cache line, and so require four back-to-back cycles to complete. The first cycle in each burst of four always requires more time to complete than the three subsequent cycles. This is because the first cycle includes the addressing phase and precharge timing (for memory).

| Function             | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM controller      | <ul> <li>Uses dedicated DRAM memory address and data buses</li> <li>Page mode - one or two pages open simultaneously</li> <li>Supports pipelined accesses</li> <li>Full RAS/CAS programmability</li> <li>Flexible bank configurations (each bank programmable for DRAM size, bank width and single or double-sided modules)</li> <li>Self configuring bank start addresses</li> <li>Shadow RAM support for the memory region 640 KB - 1 MB (in 16 KB segments)</li> <li>System management memory support</li> <li>RAS only refresh</li> <li>Fast memory access 7-2-2-2* with Extended Data Out (EDO) memory</li> </ul> |

| PCI slave interface  | <ul> <li>Becomes processor (local) bus master to generate DRAM requests on behalf of other PCI bus masters</li> <li>Supports PCI bus burst cycles</li> <li>Supports posted writes to DRAM for PCI burst writes</li> <li>Supports read-ahead from DRAM for PCI burst reads</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

| PCI master interface | <ul> <li>Provides for programmable PCI bus memory regions in memory address map</li> <li>Supports PCI bus burst cycles for 64-bit and 32-bit misaligned Pentium reads and writes</li> <li>Optional posting of PCI memory and I/O writes</li> <li>Optional buffering of PCI memory writes</li> <li>Optional read-ahead for processor to PCI accesses</li> </ul>                                                                                                                                                                                                                                                         |

| PCI bus arbiter      | <ul><li>Supports PCI bus arbitration for up to four masters</li><li>Supports rotating priority scheme</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

\*The Pentium's internal cache has a 32-byte line size, which is four times the width of the Pentium's host data bus. Burst reads and writes by the Pentium involve a full cache line, and so require four back-to-back cycles to complete. The first cycle in each burst of four always requires more time to complete than the three subsequent cycles. This is because the first cycle includes the addressing phase and precharge timing (for memory).

### **DATA PATH UNIT (82438FX)**

The 82438FX component contains a 64-bit data path between the host bus and main memory. A 4x64-bit deep buffer provides 3-1-1-1 writes to main memory.

This buffer is used for:

- writes from processor to main memory

- level-two cache write back cycles

- transfers from PCI to main memory.

#### THE PCI/ISA BRIDGE AND IDE CONTROLLER (82371FB)

The 82371FB device serves as a bridge between the PCI bus and the ISA expansion bus, and incorporates a two-channel PCI IDE controller. It incorporates the logic for a PCI interface, a DMA interface, a DMA controller that supports fast DMA transfers, data buffers to isolate the PCI and ISA buses, Timer/Counter logic, and NMI control logic.

The 82371FB PCI/ISA bridge also provides decode for the following peripheral devices:

- Flash BIOS

- Real Time Clock/CMOS Memory

- Keyboard/Mouse Controller

- Flexible Disk Controller

- Two Serial Ports

- One Parallel Port

- PCI Accessory Board Slots.

# THE 82438FX AND 82371FB FEATURE SUMMARY

| Function                                             | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data buffer<br>(for 82438FX and 82371FB<br>together) | <ul> <li>Provides a high performance 64-bit data path between the processor (local) bus and main memory</li> <li>Provides a 32-bit data path to the PCI bus</li> <li>Provides a 8-deep x 64-bits wide write buffer for all processor writes to main memory</li> <li>Provides a one-level posted write buffer for all processor writes to PCI bus memory</li> </ul>                                                                                                               |

| PCI master / slave interface<br>(for 82371FB only)   | <ul> <li>Fully compatible with PCI specification</li> <li>Supports PCI-to-ISA / ISA-to-PCI bus master cycle translations</li> <li>Supports programmable memory regions to provide fast positive decode for PCI master accesses</li> <li>Implements subtractive decoding for unclaimed PCI cycles</li> <li>Supports PCI-to-ISA posted memory writes</li> <li>Translates DMA transfers for PCI slaves</li> <li>Supports PCI address/data parity generation and checking</li> </ul> |

| ISA bus controller<br>(for 82371FB only)             | Fully compatible with ISA bus standard     Supports asynchronous ISA bus operation up to 16 MHz     Integrates:         two 82C37A DMA controllers         two 82C59A interrupt controllers         82C54 timer         hidden ISA refresh controller         support for BIOS         port A, B and NMI logic                                                                                                                                                                   |

| Fast IDE controller<br>(for 82371FB only)            | <ul> <li>Supports PIO and Bus Master IDE</li> <li>Supports up to Mode 4 timings</li> <li>Up to 22 MB/s transfer rate</li> <li>8x32-bit buffer for Bus Master IDE PCI burst transfers</li> </ul>                                                                                                                                                                                                                                                                                  |

#### **SUPER I/O CHIP**

The basic input/output control functions are provided by the Super I/O chip, the SMC 932. This chip is 100% compatible with ISA architecture and provides:

- an integrated flexible drive controller that supports 3.5-inch and 5.25-inch flexible disk drives, and tape drives

- a multi-mode parallel port

- two serial ports

- keyboard controller

- RTC

- 256 bytes of CMOS memory.

#### **NS PC87332VF FEATURE SUMMARY**

| Function                    | Features                                                                                                                              |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Flexible disk controller    | Software compatible with the DP8473, the 765A, and the N82077                                                                         |

|                             | 16-byte FIFO (default disabled)                                                                                                       |

|                             | Burst and non-burst modes                                                                                                             |

|                             | Perpendicular recording drive support                                                                                                 |

|                             | New high-performance internal digital data separator (no external filter components required)                                         |

|                             | Low-power CMOS with enhanced power-down mode                                                                                          |

|                             | Automatic media-sense support                                                                                                         |

| UARTs                       | Software compatible with the PC16550A and PC16450                                                                                     |

|                             | MIDI compatible                                                                                                                       |

| Bidirectional parallel port | Enhanced Parallel Port (EPP) compatible                                                                                               |

|                             | Extended Capabilities Port (ECP) compatible                                                                                           |

|                             | Bidirectional under either software or hardware control                                                                               |

|                             | Ability to multiplex FDC signals on parallel port pins for external FDD                                                               |

|                             | <ul> <li>Includes protection circuit against damage caused when printer is<br/>switched on, or operated at higher voltages</li> </ul> |

| Address decoder             | Provides selection of all primary and secondary ISA addresses including COM 1 - 4 and LPT 1 - 3                                       |

| Enhanced power              | Special configuration registers for power down                                                                                        |

| management                  | Enhanced programmable power down FDC command                                                                                          |

|                             | Auto power down and wake up modes                                                                                                     |

|                             | 3 special pins for power management                                                                                                   |

|                             | • Typical current consumption during power down is less than 10µA                                                                     |

|                             | Reduced pin leakage current                                                                                                           |

# FLEXIBLE DRIVE CONTROLLER (FDC)

The FDC is software and register compatible with the 82077AA, and 100% IBM compatible. It has an A and B drive-swapping capability and a non-burst DMA option.

#### SERIAL/PARALLEL PORTS

The Super I/O chip supports two serial ports and one bidirectional parallel port. The serial ports are high speed UARTs with 16 Byte FIFOs, and can be programmed as COM1, COM2, COM3, COM4, or disabled.

The parallel port can operate in four modes:

- Standard mode (PC/XT, PC/AT, and PS/2 compatible)

- Bidirectional mode (PC/XT, PC/AT, and PS/2 compatible)

- Enhanced mode (Enhanced Parallel Port or EPP compatible)

- High speed mode (MS/HP Extended Capabilities Port or ECP compatible).

It can be programmed as LPT1 (378h, IRQ7), LPT2 (278h, IRQ5), or disabled.

#### GRAPHICS/INTEGRATED VIDEO

The integrated video subsystem is composed of a PCI bus video controller and a DRAM array. The Vectra VL 5/xx series 4 PC uses the S3 Trio 765 64V+ or S3 Trio 764 video controller. These video controller embed a RAMDAC, and supports video resolutions of up to 1280 x 1024.

#### **Video Controller**

The S3 Trio 765 64V+ and S3 Trio 764 video controllers offer full compatibility with VGA. In addition, the features are enhanced beyond Super VGA by hardware which accelerates graphical user interface operation in environments such as Microsoft Windows or OS/2.

| NOTE | The S3 Trio 765 64V+ and S3 Trio 764 video drivers are not compatible. |

|------|------------------------------------------------------------------------|

|      | D3xxxA models use the S3 Trio 765 64V+.                                |

|      | D3xxxB models use the S3 Trio 764.                                     |

The enhanced features include:

- direct connectivity to PCI bus

- true acceleration for 8, 16 and 32-bit pixel depths

- 60 MHz clock for video memory

- fully programmable Pixel Clock Generator up to 135 MHz

- supports 2 MB DRAM

- fast linear addressing with full software relocation.

#### Video DRAM

The Vectra VL 5/xx series 4 PC is supplied with 1 MB of video DRAM as standard. An additional 1 MB video DRAM accessory can be installed, to give a total of 2 MB video DRAM. The upgrade consists of two 512 KB video memory chips.

#### **Video Resolutions Supported**

A table detailing all the video resolutions supported can be found in chapter 5 of this manual.

#### **IDE TO PCI CONTROLLER**

This IDE to PCI controller implementation supports the full Enhanced IDE feature set. The BIOS uses the auto-detected drive geometry information to select the fastest configuration supported by each installed IDE drive.

- Supports data transfer rate of up to 12 MB/s.

- 32-bit Windows and DOS I/O transfers (many IDE controllers use Windows integral IDE driver which only supports 16-bit I/O transfers).

#### **FLASH ROM**

The PC uses 128 KB of 200ns, Flash ROM. The HP BIOS boot code contains SETUP, video BIOS, error messages, and ISA and PCI initialization. During programming of the Flash ROM, the power supply switch and the reset button are disabled to prevent accidental interruption.

#### **SECURITY FEATURES**

The PC has many security features to protect stored data, to protect the SETUP configuration, and to prevent unauthorized operation of software applications:

- user password

- administrator password (system configuration protection)

- power-on prompt, with user of administrator password

- power-on keyboard and mouse lock, with user password

- space bar power-on protection (feature can be disabled in SETUP)

- communications port protection (ports can be disabled in SETUP)

- flexible disk drive protection (disks can be read and/or write protected in SETUP)

- boot protection (boot on flexible disk, CD-ROM, and hard disk can be enabled or disabled in SETUP)

- cover lock and, in the desktop, security bracket.

#### PHYSICAL CHARACTERISTICS

**Desktop Unit**

Weight: 0 lbs (9 kg)

Dimensions: 15.3 inches (D) by 16.5 inches (W) by 4.9 inches (H)

(39 cm by 42 cm by 12.5 cm)

Footprint:  $1.8 \text{ sq ft } (0.17 \text{ m}^2)$

**Mini-Tower Unit**

Weight: 28.7 lbs (13 kg)

Dimensions: 17.3 inches (D) by 7.6 inches (W) by 17.2 inches (H)

(44 cm by 19.2 cm by 43.8 cm)

Footprint:  $0.9 \text{ sq ft } (0.084 \text{ m}^2)$

Keyboard

Flat: 18 inches (W) by 7 inches (D) by 1.3 inches (H)

(464mm by 178mm by 33mm)

Standing: 18 inches (W) by 7 inches (D) by 2 inches (H)

(464mm by 178mm by 51mm)

#### **ELECTRICAL SPECIFICATIONS**

#### **Desktop Models**

#### Input voltage:

The Desktop VL 5/xx series 4 PCs are equipped with a 100 W (rated) power supply.

This power supply requires an input voltage in the following range:

100-127 Vac and 200-240 Vac auto-ranging at a frequency of 50 and 60 Hz.

# POWER AVAILABILITY (CONTINUOUS OPERATION):

- 100 W continuous.

- For each ISA accessory board:

4.5 A at 5 V

1.5 A at 12 V

0.3 A at -12 V

0.1 A at -5 V.

For PCI accessory boards:

4.5 A at 5 V

0.5 A at 12 V

0.1 A at -12 V

#### **Mini-Tower Models**

#### Input voltage:

The Mini-Tower VL 5/xx series 4 PCs are equipped with a 160 W continuous (rated) power supply.

This power supply requires an input voltage in the following range:

100-127 Vac and 176-264 Vac at a frequency of 47 Hz to 63 Hz, with manual switching between 115 and 230 V.

#### **Heat Dissipation:**

• Maximum thermal dissipation: 91 kcal per hour (360 BTUs per hour).

#### **Power Availability (Continuous Operation):**

- 160 W continuous, 200 W peak.

- For each ISA accessory board:

1.4 A at 5 V

0.13 A at 12 V

0.1 A at -12 V

0.03 A at -5 V.

For PCI accessory boards:

3 x 5V PCI slots.

#### **ENVIRONMENTAL SPECIFICATIONS**

#### **Desktop Unit (with hard disk)**

Operating Temperature  $+40^{\circ}$  to  $104^{\circ}$  F ( $+5^{\circ}$ C to  $+40^{\circ}$ C) Recommended Operating Temperature  $+59^{\circ}$ F to  $+158^{\circ}$ F ( $+15^{\circ}$ C to  $+30^{\circ}$ C) Storage Temperature  $-40^{\circ}$ F to  $+158^{\circ}$ F ( $-40^{\circ}$ C to  $+70^{\circ}$ C)

Over Temperature Shutdown +122°F (+50°C)

Operating Humidity 15% to 80% (relative)

Storage Humidity 8% to 80% (relative)

Operating Altitude 10000 ft (3100m) max

Storage Altitude 15000ft (4600m) max

#### Mini-Tower Unit (with hard disk)

Operating Temperature  $+ 41^{\circ}$  to  $104^{\circ}$  F (+5°C to +40°C) Recommended Operating Temperature  $+ 59^{\circ}$ F to  $+158^{\circ}$ F (+15°C to  $+30^{\circ}$ C) Storage Temperature  $-40^{\circ}$ F to  $+158^{\circ}$ F (-40°C to  $+70^{\circ}$ C)

Over Temperature Shutdown +122°F (+50°C)

Operating Humidity 15% to 80% (relative)

Storage Humidity 8% to 80% (relative)

Operating Altitude 10000 ft (3100m) max

Storage Altitude 15000ft (4600m) max

| NOTE | Operating temperature and humidity ranges may      |

|------|----------------------------------------------------|

|      | vary depending upon the mass storage devices       |

|      | installed. High humidity levels can cause improper |

|      | operation of disk drives. Low humidity levels can  |

|      | aggravate static electricity problems and cause    |

|      | excessive wear of the disk surface.                |

The 6 MB video upgrade module is available only from Matrox Electronic Systems Limited.

# 2 SUMMARY OF THE HP/PHOENIX BIOS

This chapter is a summary of the main features of the new HP/Phoenix system BIOS.

For a more detailed description, refer to the manual *System BIOS for IBM PCs, Compatibles, and EISA Computers* by Phoenix Technologies Ltd. Information for ordering this manual is given in the preface.

#### HP/PHOENIX BIOS DESCRIPTION

This chapter and the following two chapters give an overview of the HP/Phoenix BIOS. The information is divided into three main sections:

- The address space, with details of the interrupts used, described in this chapter.

- The Desktop Management Interface or DMI, which is the new method for storing and accessing information about the PC, described in chapter 3.

- The Power-On-Self-Test or POST, which is the sequence of tests the PC performs to ensure that the system is functioning correctly, described in chapter 4.

#### **OVERVIEW OF ADDRESS SPACE**

Peripheral devices, accessory devices and system controllers are accessed via the system I/O space, which is not located in system memory space. The 64 KB of addressable I/O space comprises 8-bit and 16-bit registers (called I/O ports) located in the various system components. When installing an accessory board, ensure that the I/O address space selected is in the free area of the space reserved for accessory boards (100h to 3FFh).

#### I/O ADDRESSES USED BY THE SYSTEM\*

| 170h-177h, 376h | IDE secondary channel                     |

|-----------------|-------------------------------------------|

| 1F0h-1F7h, 3F6h | IDE primary channel                       |

| 278h-27Fh       | Parallel port                             |

| 2E8h-2EFh       | Serial Port                               |

| 2F8h-2FFh       | Serial Port                               |

| 370h-371h       | Integrated I/O Controller                 |

| 378h-37Fh       | Parallel Port                             |

| 3B0h-3DFh       | Integrated video graphics controller      |

| 3E8h-3EFh       | Serial Port                               |

| 3F0h-3F5h, 3F7h | Integrated flexible disk drive controller |

| 3F8h-3FFh       | Serial Port                               |

| 496h-497h       | HP reserved                               |

| 678h-67Bh       | Parallel port if ECP mode is selected     |

| 778h-77Bh       | Parallel port if ECP mode is selected     |

|                 |                                           |

<sup>\*</sup>If configured.

Refer to the "HP BIOS I/O Port Map" in this chapter for more detailed information.

#### **System Memory Map**

00000h - 9FFFh640 KB-Base Memory AreaA0000h - BFFFFh128 KB-Video MemoryC0000h - C7FFFh32 KB-Video BIOS

C8000h - DFFFFh 96 KB-Accessory Boards Memory

E0000h - E7FFFh 32 KB-Available

E8000h - EFFFFh Reserved

F0000h - FFFFFh 64 KB-System BIOS

100000h - FFFFFFFh 1 MB plus–Extended Memory

NOTE Reserved memory used by accessory boards must be located in the area from C8000h to EFFFFh.

#### **BIOS I/O PORT MAP**

This section describes the HP BIOS port map. The next section provides more details about how the BIOS uses the system board components mentioned in the I/O port list.

| I/O Address Ports | Function                           | Bits |

|-------------------|------------------------------------|------|

| 0000-000F         | DMA Controller 1                   | 8    |

| 0020-0021         | Interrupt Controller 1             | 8    |

| 0040-0043         | Interval Timer 1                   | 8    |

| 0060, 0064        | Keyboard Controller                | 8    |

| 0061              | NMI Status and Control             | 8    |

| 0070              | NMI Mask register, RTC address     | 8    |

| 0071              | RTC data                           | 8    |

| 0081-0083, 008F   | DMA Low Page register              | 8    |

| 0092              | Alternate reset and A20 Function   | 8    |

| 0096-009F         | Internal Ports                     | 8    |

| 00A0-00A1         | Interrupt Controller 2             | 8    |

| 00C0-00DF         | DMA Controller 2                   | 8    |

| 00F0-00FF         | Co-processor error                 |      |

| 0170-0177         | Secondary IDE Controller           |      |

| 01F0-01F7         | IDE Controller                     |      |

| 0278-027F         | Parallel Port 3                    |      |

| 02E8-02EF         | Serial Port 4                      |      |

| 02F8-02FF         | Serial Port 2                      |      |

| 0370-0377         | Secondary Flexible Disk Controller |      |

| 0378-037F         | Parallel Port 2                    |      |

| 03B0-03DF         | Video                              |      |

| 03BC-03BF         | Parallel Port 1                    |      |

| 03E8-03EF         | Serial Port 3                      |      |

| 03F0-03F7         | Flexible Disk Controller           |      |

| 03F8-03FF         | Serial Port 1                      |      |

| 0CF8-0CFF         | Used for PCI Configuration**       |      |

<sup>\*</sup>These addresses are dedicated to configuration registers for PCI devices.

#### ADDRESSING SYSTEM BOARD COMPONENTS

This section provides more details of how the BIOS uses the system board components mentioned in the I/O port list.

#### **DMA Channel Controllers**

The system controller supports seven DMA channels, each with a page register used to extend the addressing range of the channel to 16 MB. The only types of DMA transfer allowed are:

"I/O-to-I/O" and "memory-to-memory" transfers are disallowed by the hardware configuration. The following table summarizes how the DMA channels are allocated.

| First DMA controller (used for 8-bit transfers) |                                              |  |  |

|-------------------------------------------------|----------------------------------------------|--|--|

| Channel                                         | Function                                     |  |  |

| 0                                               | Available                                    |  |  |

| 1                                               | Available or ECP mode for parallel port      |  |  |

| 2                                               | Flexible disk I/O                            |  |  |

| 3                                               | Available or ECP mode for parallel port      |  |  |

| Second                                          | d DMA controller (used for 16-bit transfers) |  |  |

| Channel                                         | Function                                     |  |  |

| 4                                               | Cascade from first DMA controller            |  |  |

| 5-6                                             | Available                                    |  |  |

| 6-7                                             | Available                                    |  |  |

<sup>&</sup>quot;I/O-to-memory" and "memory-to-I/O"

#### **Interrupt Controllers**

The system has two 8259A compatible interrupt controllers. They are arranged as a master interrupt controller and a slave that is cascaded through the master.

The following table shows how the master and slave controllers are connected. The Interrupt Requests (IRQ) are numbered sequentially, starting with the master controller, and followed by the slave.

| IRQ (Interrupt Vector) |            | Interrupt Request Description                                 |

|------------------------|------------|---------------------------------------------------------------|

| IRQ0(08h)              |            | System timer                                                  |

| IRQ1(09h)              |            | Keyboard controller                                           |

| IRQ2(0Ah)              | Slave IRQ  | Cascade connection from INTC2 (Interrupt Controller 2)        |

|                        | IRQ8(70h)  | Real time clock                                               |

|                        | IRQ9(71h)  | Available for PCI accessory boards, if not used by ISA boards |

|                        | IRQ10(72h) | Available for PCI accessory boards, if not used by ISA boards |

|                        | IRQ11(73h) | Available for PCI accessory boards, if not used by ISA boards |

|                        | IRQ12(74h) | Mouse                                                         |

|                        | IRQ13(75h) | Pentium                                                       |

|                        | IRQ14(76h) | Primary channel of IDE controller                             |

|                        | IRQ15(77h) | Free, if not used by secondary channel of IDE controller*     |

| IRQ3(0Bh)              |            | Free, if not used used for serial port**                      |

| IRQ4(0Ch)              |            | Free, if not used used for serial port**                      |

| IRQ5(0Dh)              |            | Free, if not used used for parallel port***                   |

| IRQ6(0Eh)              |            | Flexible disk drive controller                                |

| IRQ7(0Fh)              |            | Free, if not used used for parallel port***                   |

<sup>\*</sup>IRQ 15 can be made available by disabling the secondary channel of the IDE controller in the SETUP program.

#### **PCI Interrupt Request Lines**

PCI devices generate interrupt requests using up to four PCI interrupt request lines (INTA#, INTB#, INTC#, and INTD#).

When a PCI device makes an interrupt request, the request is re-directed to the system interrupt controller. The interrupt request will be re-directed to one of the IRQ lines made available for PCI devices.

All PCI devices with interrupt transfer support will use and share INTA#. A multiple-function PCI device may support several INT lines. These devices will require more than one system interrupt request line.

<sup>\*\*</sup>IRQ3 and IRQ4 can be made available by disabling the serial ports in the SETUP program.

<sup>\*\*</sup>IRQ5 and IRQ7 can be made available by disabling the parallel ports in the SETUP program.

# 3 DESKTOP MANAGEMENT INTERFACE

This chapter describes an important feature of HP's new style BIOS, the Desktop Management Interface or DMI.

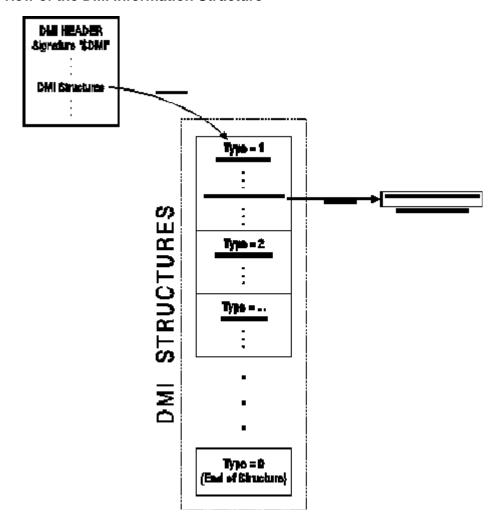

#### **DMI INFORMATION STRUCTURE**

This BIOS presents a new method for storing and accessing information about the PC, called the Desktop Management Interface or DMI.

The system administrator uses the DMI to access information about the PC, such as the BIOS version number, the serial number, the processor type, and the size of the hard disk drive. This information is stored in the Management Information Format Database, or MIF.

Pointers are used to indicate the position of a table or a string value. The following rules apply to pointers:

- Pointers must never be zero. For empty strings, the pointer must point to a null (zero) value

- Far pointers are in Intel (little endian) format, with the segment in the high word and the

offset in the low word.

All string values are terminated by a null (zero) value.

#### **Overview of the DMI Information Structure**

#### **ACCESSING BIOS DMI INFORMATION**

To access BIOS information, do the following steps:

- 1 **Locate the DMI header.**Search for the "\$DMI" signature in the segment E0000:0 or F0000:0.

- Verify the checksums.

Refer to "Verifying the DMI Information Structure," in this chapter.

- 3 **Locate the first sub-structure table** using the far pointer given in the DMI header.

- 4 Walk through the tables to locate the desired table.

Each table is identified by a unique type. The type is given by the first byte of the table. The length of the table is given by the second byte. The next table follows immediately after the current one.

5 Read off the required values.

Each type of table has a pre-defined format. For a list of the major table types, refer to "DMI Sub-Structure Tables," in this chapter.

6 Use the pointer to retrieve string values.

All string values are terminated by a null (zero) value.

#### THE DMI HEADER

The DMI header is the starting point for all DMI information.

| Field                      | Offset | Length          | Value                  |

|----------------------------|--------|-----------------|------------------------|

| DMI Header Signature       | 0h     | 4 bytes         | "\$DMI"                |

| Version                    | 4h     | 1 byte          | 00010010 (Ver 1.2)     |

| DMI Header Length          | 5h     | 1 byte          | 0Eh                    |

| Pointer to DMI structures  | 0Ah    | 4 bytes (DWORD) | Far pointer (variable) |

| Length of DMI structures   | 0Ch    | 2 bytes (WORD)  | variable               |

| Checksum of DMI structures | 0Ch    | 1 byte          | variable               |

| Checksum of DMI header     | 0Dh    | 1 byte          | variable               |

#### VERIFYING THE DMI INFORMATION STRUCTURE

Before accessing the DMI tables, the checksums must be verified to ensure the reliability of the information. To calculate a checksum value of a structure, do the following steps:

- 1 Add together all the bytes of the structure.

- 2 Convert the value to negative.

- 3 Cast the value to a byte (take the low byte).

There are two checksums, one for the DMI header and another for the remaining DMI structure. To verify these two checksums, do the following steps:

- 1 Locate the DMI header.

- Using the length value of the DMI header, calculate the checksum value for the DMI header. (When adding together the bytes of the header, exclude the checksum byte, offset 0Dh.)

- 3 Verify this value against the checksum given for the DMI header.

- 4 Retrieve the position and length of the DMI structures.

- 5 Calculate the checksum value for the DMI structures.

- 6 Verify this value against the checksum given for the DMI structures.

#### **DMI SUB-STRUCTURE TABLES**

Each type of table has a pre-defined format. Although the structure can evolve over time, new fields are always added to the end of the table and the length value reflects this new size.

To parse several tables in order to find a specific table, simply use the table length. Using this method will ensure that the parser can function even when the tables evolve over time.

To locate specific BIOS information, use the DMI sub-structure tables which are listed on the following pages.

Type 1: BIOS Information

| Field                    | Offset | Length             | Value                 | Description                                                                                                                                |

|--------------------------|--------|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                     | 0h     | 1 byte             | 1                     | BIOS information table                                                                                                                     |

| Length                   | 1h     | 1 byte             | 15h                   | Table length (in bytes)                                                                                                                    |

| Vendor                   | 2h     | 4 bytes<br>(DWORD) | variable              | Far pointer to string containing BIOS vendor name.                                                                                         |

| BIOS Version             | 6h     | 4 bytes<br>(DWORD) | variable              | Far pointer to string containing BIOS version number.                                                                                      |

| BIOS Starting<br>Address | Ah     | 2 bytes<br>(WORD)  | variable              | Segment location of BIOS starting address, i.e. E800h.                                                                                     |

| BIOS Release Date        | Ch     | 4 bytes<br>(DWORD) | variable              | Far pointer to string containing BIOS release date.                                                                                        |

| BIOS<br>Characteristics  | 10h    | 4 bytes<br>(DWORD) | variable<br>bit field | Bit field value indicating which functions the BIOS supports.                                                                              |

| BIOS ROM Size            | 14h    | 1 byte             | variable              | Value indicating the size of the BIOS ROM: $0 \rightarrow 64$ K, $1 \rightarrow 128$ K, $2 \rightarrow 256$ K, $3 \rightarrow 512$ K, etc. |

Type 2: Component ID

| Field                      | Offset | Length            | Value    | Description                                            |

|----------------------------|--------|-------------------|----------|--------------------------------------------------------|

| Туре                       | 0h     | 1 byte            | 2        | Component ID table                                     |

| Length                     | 1h     | 1 byte            | 0Ah      | Table length                                           |

| Manufacturer               | 2h     | 2 bytes<br>(WORD) | variable | Near pointer to string containing manufacturer's name. |

| Product                    | 4h     | 2 bytes<br>(WORD) | variable | Near pointer to string containing product name.        |

| Version (oard<br>Revision) | 6h     | 2 bytes<br>(WORD) | variable | Near pointer to string containing date code.           |

| Serial Number              | 8h     | 2 bytes<br>(WORD) | variable | Near pointer to string containing serial number.       |

**Type 3: Processor Information**

| Field                     | Offset | Length            | Value    | Description                                                                                                                                                                                                |

|---------------------------|--------|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                      | 0h     | 1 byte            | 3        | Processor information table                                                                                                                                                                                |

| Length                    | 1h     | 1 byte            | 0Bh      | Table length                                                                                                                                                                                               |

| Processor Type            | 2h     | 1 byte            | ENUM     | Value indicating processor type:  1 → Other  2 → Unknown  3 → Central Processor  4 → Math Processor  5 → DSP Processor  6 → Video Processor                                                                |

| Processor Family          | 3h     | 1 byte            | ENUM     | Value indicating processor family: $1 \rightarrow \text{Other}$ $2 \rightarrow \text{Unknown}$ $6 \rightarrow 80486$ $A \rightarrow 80487$ $B \rightarrow \text{Pentium}$ $20 \rightarrow \text{Power PC}$ |

| Processor<br>Manufacturer | 4h     | 2 bytes<br>(WORD) | variable | Near pointer to string containing processor manufacturer's name.                                                                                                                                           |

| Processor Version         | 6h     | 2 bytes<br>(WORD) | variable | Near pointer to string describing the processor.                                                                                                                                                           |

| Max Speed                 | 8h     | 2 bytes<br>(WORD) | variable | Decimal value of maximum processor speed.<br>Example: 66d for a 66 MHz processor.                                                                                                                          |

| Processor Upgrade         | Ah     | 1 byte            | ENUM     | Value indicating processor upgrade type:  1 → Other  2 → Unknown  3 → Daughter Board  4 → ZIF Socket  5 → Replaceable Piggy Back  6 → None                                                                 |

# **HP-Specific DMI Sub-Structure Structures**

Type 80h: HP ID

| Field        | Offset | Length | Value    | Description                                                                                                                                                                                                                                                                                 |

|--------------|--------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре         | 0h     | 1 byte | 80h      | HP ID information table                                                                                                                                                                                                                                                                     |

| Length       | 1h     | 1 byte | 6        | Table length                                                                                                                                                                                                                                                                                |

| Signature    | 02h    | 2      | "HP"     | Hewlett-Packard signature                                                                                                                                                                                                                                                                   |

| PC ID        | 04h    | 1 byte | variable | PC Identification                                                                                                                                                                                                                                                                           |

| Capabilities | 05h    | 1 byte | BITMAP   | Bit 7=1 → Tatooing supported  Bit 6=1 → PCMCIA device is present  Bit 5=1 → Infrared is present  Bit 4=1 → Two embedded serial ports present  Bit 3=1 → Mini-Tower (1) or Desktop (0)  Bit 2=1 → Embedded LAN present  Bit 1=1 → Using integrated video  Bit 0=1 → Supports HP LAN boot ROM |

Type 81h: HP Configuration ID

| Field                    | Offset | Length | Value    | Description                                    |

|--------------------------|--------|--------|----------|------------------------------------------------|

| Туре                     | 0h     | 1 byte | 81h      | HP Configuration table                         |

| Length                   | 1h     | 1 byte | 3        | Table length                                   |

| Serial/Parallel<br>Count | 02h    | 1 byte | variable | Bits 7-4 → Number of integrated parallel ports |

| Count                    |        |        |          | Bits 3-0 → Number of integrated serial ports   |

Type 84h: HP System Information

| Field                   | Offset | Length  | Value    | Description                                                                                                                           |

|-------------------------|--------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Туре                    | 0h     | 1 byte  | 84h      | HP system information table                                                                                                           |

| Length                  | 1h     | 1 byte  | Eh       | Table length                                                                                                                          |

| System Power-on<br>Time | 02h    | 2 bytes | variable | Short pointer to string containing date and time of last boot. Format: "ccyymmddHHMM" The value "************************************ |

| Base Memory Size        | 04h    | 2 bytes | variable | Size of base memory in kilobytes                                                                                                      |

| Extended Memory<br>Size | 06h    | 2 bytes | variable | Extended Memory size in 64 KB blocks                                                                                                  |

| HP BIOS Version         | 08h    | 4 bytes | variable | Long pointer to string describing HP BIOS version                                                                                     |

| CPU Name                | 0Ch    | 2 bytes | variable | Short pointer to string describing CPU name                                                                                           |

# 4 POWER-ON SELF-TESTS AND ERROR MESSAGES

This chapter describes the power-on self-tests (POST), which are contained in the PC's ROM BIOS, and the error messages which can result.

## **POWER-ON SELF TEST (POST)**

Each time the system is powered on, or a reset is performed, the POST is executed. The POST process verifies the basic functionality of the system components and initializes certain system parameters. The POST performs the tests in the order described in this chapter.

The POST displays a graphic screen with the HP Vectra logo. If the POST detects an error, the error message is displayed. To see the tests performed during the POST, press [ESC] when the HP Vectra logo appears and the display will switch to text mode. In this mode, a summary configuration screen will be displayed at the end of the POST. Pressing the PAUSE/ BREAK key at any time will allow you to inspect the screen contents. Press any key to resume

If the POST is initiated by a soft reset [CTRL] [ALT] and [DELETE], the RAM tests are not executed and shadow RAM is not cleared. In all other respects, the POST executes in the same way following power-on or a soft reset.

| NOTE | The POST does not detect when a <i>slave hard disk drive</i> ("HDD 1" or "HDD 3" in the setup) has been installed or changed. |

|------|-------------------------------------------------------------------------------------------------------------------------------|

|      | 5                                                                                                                             |

#### **SHADOW RAM**

On HP personal computers, access to certain ROM data is enhanced by using shadow RAM. During the POST, the BIOS and other ROM data is copied into high-speed shadow RAM. The shadow RAM is addressed at the same physical location as the original ROM in a manner which is completely transparent to applications. This technique provides faster access to the system BIOS firmware.

| POST Test                  | Description                                                                                                                                                                                                                                                          |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System BIOS Tests          |                                                                                                                                                                                                                                                                      |  |  |

| LED Test                   | Tests the LEDs on the control panel.                                                                                                                                                                                                                                 |  |  |

| Processor Test             | Tests the processor's registers. Test failure causes the boot process to abort.                                                                                                                                                                                      |  |  |

| System (BIOS) ROM Test     | Calculates an 8-bit checksum. Test failure causes the boot process to abort.                                                                                                                                                                                         |  |  |

| RAM Refresh Timer Test     | Tests the RAM refresh timer circuitry. Test failure causes the boot process to abort.                                                                                                                                                                                |  |  |

| Interrupt RAM Test         | Checks the first 64 KB of system RAM used to store data corresponding to various system interrupt vector addresses.  Test failures cause the boot process to abort.                                                                                                  |  |  |

| Shadow the System ROM BIOS | Tests the system ROM BIOS and shadows it. Failure to shadow the ROM BIOS will cause an error code to display. The boot process will continue, but the system will execute from ROM. This test is not performed after a soft reset (using [CTRL] [ALT] and [DELETE]). |  |  |

| Load CMOS Memory                          | Checks the serial EEPROM and returns an error code if it has been corrupted. Copies the contents of the EEPROM into CMOS RAM.                                                                                                                                                          |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMOS RAM Test                             | Checks the CMOS RAM for start-up power loss, verifies the CMOS RAM checksum(s). Test failure causes error codes to display.                                                                                                                                                            |

| Internal Cache Memory Test                | Tests the processor's internal level-one cache RAM. Test failure causes an error code to display and the boot process to abort.                                                                                                                                                        |

|                                           | Video Tests                                                                                                                                                                                                                                                                            |

| Initialize the Video                      | Initializes the video subsystem, tests the video shadow RAM, and, if required, shadows the video BIOS. A failure causes an error code to display, but the boot process continues.                                                                                                      |

|                                           | System Board Tests                                                                                                                                                                                                                                                                     |

| Test External Cache                       | Tests the level-two cache. A failure causes an error code to display and disables the external cache.                                                                                                                                                                                  |

| Shadow SCSI ROM                           | Tests for the presence of HP SCSI ROMs. If SCSI ROMs are detected, their contents are copied into the shadow RAM area. A failure will cause an error code to display.                                                                                                                  |

| 8042 Self-Test                            | Downloads the 8042 and invokes the 8042 internal self-test. A failure causes an error code to display.                                                                                                                                                                                 |