## **Table of Contents**

| NoticeIV                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introductionv                                                                                                                                                                                                                                                                                                                              |

| Chapter 1 Pre-Configuration1                                                                                                                                                                                                                                                                                                               |

| Step 1Setting the Jumpers3Jumper Locations4CMOS Reset5Disk-on-Chip Selection5Flash BIOS Write Protect5Clock Speed Selection6Watchdog Timer Selection6On-board Ethernet7On-board CRT video controller/LCD(optional)7ATX Power Supply Enhancements8Step 2DRAM, CPU, Disk-on-Chip and<br>Cables Installation9Raptor LPX Memory Configuration9 |

| CPU Installation 9 Disk-on-Chip installation 10 Installing Cables 10 Power and Control Panel Cables 10 Installing Peripheral Cables 10 Index of Connectors 13  Chapter 2 HIFLEX BIOS                                                                                                                                                       |

| Chapter 2 HIFLEX BIOS Setup15                                                                                                                                                                                                                                                                                                              |

| Standard Setup                                                                                                                                                                                                                                                                                                                             |

| Change User Pa<br>Change Supervi<br>Change Langua<br>Auto Configurat<br>Auto Configurat<br>Save Settings a                                                   | d Disk                      | 34<br>35<br>35<br>36 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|

| Chapter 3                                                                                                                                                    | Upgrading                   | 37                   |

| Upgrading the S<br>Upgrading the M                                                                                                                           | System Memorylicroprocessor | 37<br>37             |

| Appendix A                                                                                                                                                   | Technical Specifications    | 39                   |

| System Memory Bios Embedded I/O Industrial Device Miscellaneous Memory Map DMA Channels I/O Map On-board Device PCI Configuratio Interrupts PCI Interrupt Ro | eseseseseseses              | 39404343454646       |

| Appendix B                                                                                                                                                   | Flash BIOS programming      | 59                   |

| Appendix C                                                                                                                                                   | Disk-On-Chip                | 61                   |

| Appendix D                           | On-Board Devices    |          |

|--------------------------------------|---------------------|----------|

| Watchdog Timer .<br>Post Code Displa | y                   | 63<br>64 |

| Appendix E<br>Ethe                   | On-Board<br>ernet   | 75       |

| Appendix F<br>Con                    | On-Board<br>troller |          |

### **Notice**

The company reserves the right to revise this publication or to change its contents without notice. Information contained herein is for reference only and does not constitute a commitment on the part of the manufacturer or any subsequent vendor. They are in no way responsible for any loss or damage resulting from the use (or misuse) of this publication.

This publication and any accompanying software may not, in whole or in part, be copied, photocopied, translated or reduced to any machine readable form without prior consent from the vendor, manufacturer or creators of this publication, except for copies kept by the user for backup purposes.

Brand and product names mentioned in this publication may or may not be copyrights and/or registered trademarks of their respective companies. They are mentioned for identification purposes only and are not intended as an endorsement of that product or its manufacturer.

First Edition.

©May, 2001

### Introduction

Thank you for your purchase of the Raptor LPX industrial embedded motherboard. The Raptor LPX design was based on the Intel 440BX chipset providing the ideal platform to industrial applications. The Raptor LPX design is based on the Intel Celeron and PIII processor.

With proper installation and maintenance, your Raptor LPX will provide years of high performance and trouble free operation.

This manual provides a detailed explanation into the installation and use of the Raptor LPX industrial embedded motherboard. This manual is written for the novice PC user/installer. However, as with any major computer component installation, previous experience is helpful and should you not have prior experience, it would be prudent to have someone assist you in the installation. This manual is broken down into 3 chapters and 6 appendixes.

#### **Chapter 1 - System Board Pre-Configuration**

This chapter provides all the necessary information for installing the Raptor LPX. Topics discussed include: installing the CPU (if necessary), DRAM installation, jumper settings for CPU and standard I/O. Connecting all the cables from the system board to the chassis and peripherals.

#### Chapter 2 - BIOS Configuration

This chapter shows the final step in getting your system firmware setup.

#### **Chapter 3 - Upgrading**

The Raptor LPX provides a number of expansion options including memory. All aspects of the upgrade possibilities are covered.

#### **Appendix A - Technical Specifications**

A complete listing of all the major technical specifications of the Raptor LPX is provided.

#### Appendix B - Flash BIOS Programming (optional)

Provides all the information necessary to program your optional AMIBIOS Flash BIOS.

#### Appendix C - Disk-on-Chip

One on-board socket for a solid state flash disk device.

#### **Appendix D - Industrial Devices**

Watchdog Timer and On-Board POST (Power On Self Testing) code display.

#### **Appendix E - Ethernet**

On-board 10/100 Ethernet.

#### Appendix F - LCD/CRT video controller

On-board CRT video controller/LCD(optional) 2MB (optional 4MB).

### Static Electricity Warning!

The Raptor LPX has been designed as rugged as possible but can still be damaged if jarred sharply or struck. Handle the motherboard with care.

The Raptor LPX also contains delicate electronic circuits that can be damaged or weakened by static electricity. Before removing the Raptor LPX from its protective packaging, it is strongly recommended that you use a grounding wrist strap. The grounding strap will safely discharge any static electricity build up in your body and will avoid damaging the motherboard. Do not walk across a carpet or linoleum floor with the bare board in hand.

#### Warranty

This product is warranted against material and manufacturing defects for two years from the date of delivery. Buyer agrees that if this product proves defective the manufacturer is only obligated to repair, replace or refund the purchase price of this product at manufacturer's discretion. The warranty is void if the product has been subjected to alteration, misuse or abuse; if any repairs have been attempted by anyone other than the manufacturer; or if failure is caused by accident, acts of God, or other causes beyond the manufacturer's control.

### **Raptor LPX - An Overview**

The Raptor LPX represents the ultimate in industrial embedded motherboard technology. No other system board available today provides such impressive list of features:

### **CPU Support**

• Supports full series of Intel Celeron and PIII PGA370 processors (up to 100MHz FSB).

### **Supported Bus Clocks**

66 and 100MHz.

#### **Memory**

• Three DIMM sockets up to 384MB or 768MB(registered) SDRAM, PC100 recommended (required for PIII or 100MHz).

#### On-Board I/O

- 2 Floppies up to 2.88 MB.

- Dual channel PCI 32-bit EIDE controller.

- Two high speed RS-232 serial ports 16 Bytes FIFO (16550).

- ullet One Centronics  $^{TM}$  compatible bidirectional parallel port. EPP/ECP mode compatible.

- One PS/2 mouse and one PS/2 keyboard headers.

- Two Universal Serial Bus connectors.

- One Disk-on-Chip on-board up to 288MB with FFS for diskless applications.

- Software and hardware programmable Watchdog Timer & onboard POST Display Diagnostics.

- ISA/PCI riser slot for commercial adapters expansion.

- RJ45 Ethernet connector.

- One PC104-Plus expansion/stack-up interface and power connector.

- Power Button advanced management support.

- Automatic CPU voltage & temperature monitoring device (optional).

### **ROM BIOS**

• AMI BIOS<sup>TM</sup> BIOS HIFLEX with optional FLASH ROM

### **On-Board Ethernet**

• On-board 10/100 Ethernet.

#### **LCD/CRT video controller**

• On-board CRT video controller/LCD(optional) (C&T 65555) 2MB – 4MB(optional).

### Conventions Used in this Manual

Notes - Such as a brief discussion of memory types.

Important Information - such as static warnings, or very important instructions.

When instructed to enter keyboard keystrokes, the text will be noted by this graphic.

# Chapter 1 Pre-Configuration

This chapter provides all the necessary information for installing the Raptor LPX into a standard PC chassis. Topics discussed include: installing the CPU (if necessary), DRAM installation, jumper settings for CPU and standard I/O.

### **Handling Precautions**

The Raptor LPX has been designed to be as rugged as possible but it can be damaged if dropped, jarred sharply or struck. Damage may also occur by using excessive force in performing certain installation procedures such as forcing the system board into the chassis or placing too much torque on a mounting screw.

Take special care when installing or removing the system memory DIMMs. Never force a DIMM into a socket. Screwdrivers slipping off a screw and scraping the board can break a trace or component leads, rendering the board unusable. Always handle the Raptor LPX with care.

#### Special Warranty Note:

Products returned for warranty repair will be inspected for damage caused by improper installation and misuse as described in the previous section and the static warning below. Should the board show signs of abuse, the warranty will become void and the customer will be billed for all repairs and shipping and handling costs.

### **Static Warning**

The Raptor LPX contains delicate electronic semiconductors that are highly sensitive to static electricity. These components, if subjected to a static electricity discharge, can be weakened thereby reducing the serviceable life of the system board. BEFORE THE BOARD IS

REMOVED FROM ITS PROTECTIVE ANTISTATIC PACKAGING, TAKE PROPER PRECAUTIONS! Work on a conductive surface that is connected to the ground. Before touching any electronic device, ground yourself by touching an unpainted metal object or, and highly recommended, use a grounding strap.

### Step 1 Setting the Jumpers

Your Raptor LPX is equipped with a large number of peripherals and has the ability to run at a variety of speeds without the need to change any crystals or oscillators. As such, there are a large number of configuration jumpers on the board. Taken step by step, setting these jumpers is easy. We suggest you review each section and follow the instructions.

#### **Jumper Types**

Jumpers are small copper pins attached to the system board. Covering two pins with a shunt closes the connection between them. The Raptor LPX examines these jumpers to determine specific configuration information. There are three different categories of jumpers on the Raptor LPX.

- A. Two pin jumpers are used for binary selections such as enable, disable. Instructions for this type of jumper are open, for no shunt over the pins or closed, when the shunt covers the pins.

- B. Three or four pin jumpers are used for multiple selections. Instructions for these jumpers will indicate which two pins to cover. For example: for JPx 2-3 the shunt will be covering pins 2 and 3 leaving pins 1 and 4 exposed.

- C. Grouped jumpers are used when a certain function has multiple selections. There are two grouped jumpers on the board and careful attention should be given when setting these jumpers. Instructions for grouped jumpers are similar to those above.

Some jumpers are actually a set of micro-switches. Moving the micro-switch to the position assigned "ON" will have the same effect as closing a regular jumper.

How to identify pin number 1 on *Figure 1-1*: Looking to the solder side (The board side without components) of the PCB (Printed Circuit Board), pin number 1 will have a squared pad . Other pins will have a circular pad . They are numbered sequentially.

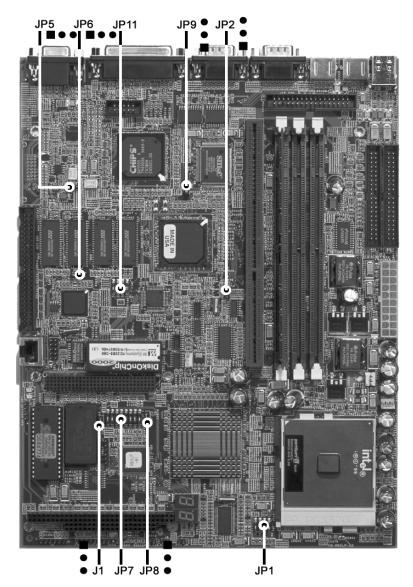

### **Jumper Locations**

Use the diagram below and the tables on the following pages to locate and set the on-board configuration jumpers.

Figure 1-1 Jumper Locations

### **CMOS Reset**

This option is provided as a convenience for those who need to reset the CMOS registers. It should always be set to "Normal" for standard operation. If the CMOS needs to be reset, turn off the system, move J1 to 2-3, turn the system on, move jumper to 1-2 and press reset.

Table 1-1 CMOS Reset

| <b>Reset CMOS</b> | Normal | Clear CMOS |

|-------------------|--------|------------|

| J1                | 1-2*   | 2-3        |

<sup>\*</sup> Manufacturer's Settings.

### **Disk-on-Chip Selection**

The jumper JP7 (SW6 and SW7) allows selection for the address on Disk-on-Chip device.

Table 1-2 Disk-on-Chip Selection

| Address | JP7 (SW6) | JP7 (SW7) |

|---------|-----------|-----------|

| D000h*  | On        | On        |

| D400h   | Off       | On        |

| D800h   | On        | Off       |

| DC00h   | Off       | Off       |

<sup>\*</sup> Manufacturer's Settings.

### **Flash BIOS Write Protect**

To program the optional flash BIOS (Location U42 – *Figure 1-2*) use JP8 to disable write protection. For regular standard BIOS use default settings.

**Table 1-3 Flash BIOS Programming Selection**

| Flash<br>Write-protect | Enabled | Disabled |

|------------------------|---------|----------|

| JP8                    | 1-2*    | 2-3      |

<sup>\*</sup>Manufacturer's Settings.

<sup>\*</sup>JP7 (SW8) is Reserved (default Off).

### **Clock Speed Selection**

The Raptor LPX has a CPU automatic speed selector device. The jumper JP1 allows selection for this option.

**Table 1-4 Clock Frequency Selection**

| Clock<br>Frequency | JP1<br>(SW1) | JP1<br>(SW2) | JP1<br>(SW3) | JP1<br>(SW4) |

|--------------------|--------------|--------------|--------------|--------------|

| AUTODETECT*        | On           | Off          | Off          | Off          |

| 66MHz              | Off          | On           | Off          | Off          |

| 100MHz             | Off          | Off          | Off          | Off          |

| RESERVED           | Off          | Off          | On           | Off          |

| RESERVED           | Off          | Off          | Off          | On           |

| RESERVED           | Off          | On           | Off          | On           |

| RESERVED           | Off          | On           | On           | Off          |

<sup>\*</sup> Manufacturer's Settings.

DO NOT set the switches to RESERVED settings.

RESERVED settings are for internal testing purposes only.

### **Watchdog Timer Selection**

The watchdog timer can be set as hardware, software or disabled through JP7 (SW3 and SW4). JP7 (SW1 and SW2) sets the time-out and JP7 (SW5) set the addresses. Please refer to appendix D for more details.

**Table 1-5 Watchdog Timer Selection**

| Watchdog<br>Type | JP7 (SW3) | JP7 (SW4) |

|------------------|-----------|-----------|

| Hardware         | On        | Off       |

| Disabled*        | Off       | On        |

| Software         | On        | On        |

| Reserved         | Off       | Off       |

<sup>\*</sup> Manufacturer's Settings.

Table 1-6 Watchdog Time-out Selection

| Watchdog<br>Timeout | JP7 (SW1) | JP7 (SW2) |

|---------------------|-----------|-----------|

| 150 ms              | Off       | On        |

| 600 ms              | Off       | Off       |

| 1200 ms*            | On        | Off       |

| Reserved            | On        | On        |

<sup>\*</sup> Manufacturer's Settings.

Table 1-7 Watchdog Address Selection

| Watchdog<br>Address | JP7 (SW5) |

|---------------------|-----------|

| 110h*               | Off       |

| 310h                | On        |

<sup>\*</sup> Manufacturer's Settings.

### **On-board Ethernet**

The Raptor LPX has a built-in 10/100 Ethernet. The jumper JP6 either disables (2-3) or enables (1-2) this feature. For more information please refer to Appendix E.

**Table 1-8 Ethernet Selection**

| Ethernet Selection | Enabled | Disabled |

|--------------------|---------|----------|

| JP6                | 1-2*    | 2-3      |

<sup>\*</sup> Manufacturer's Settings.

#### On-board CRT video controller/LCD(optional)

The Raptor LPX has a built-in CRT video controller/LCD(optional) (C&T 65555) 2MB – 4MB(optional). The jumper JP9 either disables (2-3) or enables (1-2) the VGA. The switches JP11 select the LCD panel type. The jumper JP5 selects the LCD operating voltage. For more information please refer to Appendix F.

Table 1-9 On-board VGA CRT/LCD(optional) Selection

| VGA<br>Selection | Enabled | Disabled |

|------------------|---------|----------|

| JP9              | 1-2*    | 2-3      |

<sup>\*</sup> Manufacturer's Settings.

Please, refer to Appendix F for the LCD(optional) jumper settings.

### **ATX Power Supply Enhancements**

The Raptor LPX has a Power on mode selection. The jumper JP2 selects the power on mode.

Table 1-10 POWER ON Mode Select

| Power on mode | Power on immediately | Power on upon PWR_SW signal (Button press) |

|---------------|----------------------|--------------------------------------------|

| JP2           | 1-2*                 | 2-3                                        |

<sup>\*</sup> Manufacturer's Settings.

# Step 2 DRAM, CPU, Disk-on-Chip and Cables Installation

Depending upon how your Raptor LPX is configured you may need to install the following:

- DRAM (DIMMs)

- CPU

- Disk-on-chip

### **Raptor LPX Memory Configuration**

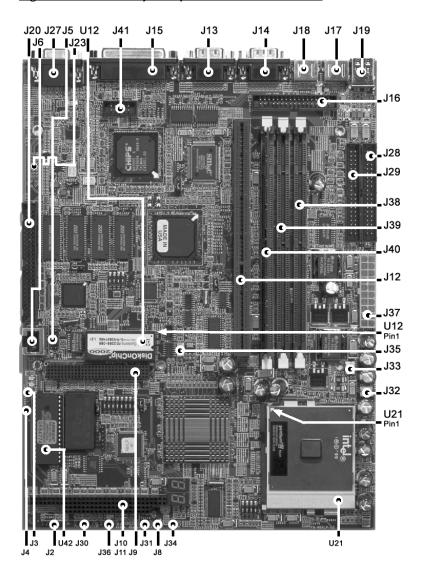

The Raptor LPX offers 3 DIMM memory sockets (Locations J38, J39 and J40 – *Figure 1-2*). They can be configured with 3.3V unbuffered SDRAM modules. It is very important that the quality of the DIMMs is good. Unreliable operation of the system may result if poor quality DIMMs are used. Always purchase your memory from a reliable source. We strongly recommend using PC100 memory module (REQUIRED when using PIII or 100MHz operation). The Raptor LPX also supports ECC memories.

The Raptor LPX uses standard DIMMs. To determine the actual capacity of a 1 by 64 DIMM, simply multiply the 1MB by 8.

### **CPU Installation**

The Raptor LPX currently supports the following CPUs:

• Full series of Intel Celeron and PIII processors (PGA 370).

- 1. Improper installation of the CPU may cause permanent damage to both the system board and the CPU. -- Void of warranty

- 2. Always handle the CPU by the edges, never touch the pins.

- 3. Always use a heatsink and a CPU fan.

Locate the CPU socket on your Raptor LPX system board (PGA Socket – Location U21 – *Figure 1-2*). To install the processor, lift the lever of the ZIF socket and gently insert the CPU. The CPU will fit only in the right alignment. Make sure the CPU is inserted all the way. Lower the lever. Install the CPU fan. Make sure it is locked and connected to J32 (see pin-out in Appendix A).

This completes the installation of the CPU. Now is it a good time to double check both the CPU and DIMM installation to make sure that these devices have been properly installed.

#### **Disk-on-Chip installation**

The Raptor LPX supports One Disk-on-Chip on-board up to 288 MB with FFS for diskless applications.

Locate the Disk-on-Chip socket on your Raptor LPX system board (Location U12 – *Figure 1-2*). Locate pin 1 (*Figure 1-2*). To install the Disk-on-Chip gently insert the chip. Make sure the Disk-on-Chip is inserted all the way.

#### **Installing Cables**

#### **Power and Control Panel Cables**

The Raptor LPX gets power from the power connector J37.

#### Installing Peripheral Cables

Now it is a good time to install the internal peripherals such as floppy and hard disk drives. Do not connect the power cable to these peripherals, as it is easier to attach the bulky ribbon cables before the smaller power connectors. If you are installing more than one IDE drive double check your master/slave jumpers on the drives. Review the information supplied with your drive for more information on this subject.

Connect the floppy cable (not included) to the system board. Then connect remaining ends of the ribbon cable to the appropriate peripherals. Connect the Ethernet cable (included). Finally, connect the

IDE cable (not included) to the system. Then connect remaining ends of the ribbon cable to the appropriate peripherals. This concludes the hardware installation of your Raptor LPX system. Now it is a good time to re-check all of the cable connections to make sure they are correct.

Figure 1-2 Location of Components and Connectors

### **Index of Connectors**

Please refer to Appendix A for pin-out descriptions.

Table 1-11 Connectors descriptions

| Connector | Description                |  |

|-----------|----------------------------|--|

| J2        | Infra Red                  |  |

| J3        | LAN ACT LED                |  |

| J4        | LAN Speed LED              |  |

| J5        | Ethernet Header            |  |

| J6        | Ethernet RJ45              |  |

| J8        | RESET                      |  |

| J9        | PC 104 – Plus              |  |

| J10       | PC 104                     |  |

| J11       | PC 104                     |  |

| J12       | LPX Riser Slot             |  |

| J13       | COM 1                      |  |

| J14       | COM 2                      |  |

| J15       | LPT - Parallel             |  |

| J16       | FDD                        |  |

| J17       | Keyboard – PS/2            |  |

| J18       | Mouse – PS/2               |  |

| J19       | USB (2x)                   |  |

| J20       | LCD Header                 |  |

| J23       | DVI-I Connector (optional) |  |

| J27       | VGA                        |  |

| J28       | Primary IDE                |  |

| J29       | Secondary IDE              |  |

| J30       | Power LED/Keylock          |  |

| J31       | HDD LED                    |  |

| J32       | CPU Fan                    |  |

| J33       | Sys. Fan                   |  |

| J34       | Power Switch               |  |

| J35       | Wake On LAN                |  |

| J36       | Speaker                    |  |

| J37       | ATX Power                  |  |

### Raptor LPX – Installation Guide

| Connector | Description            |

|-----------|------------------------|

| J41       | Auxiliary COM 2 Header |

### **User's Notes:**

# Chapter 2

# HIFLEX BIOS Setup

Your Raptor LPX features AMI BIOS. The system configuration parameters are set via the HIFLEX AMIBIOS setup. Since HIFLEX BIOS Setup resides in the ROM BIOS, it is available each time the computer is turned on.

#### Starting BIOS Setup

As POST executes, the following appears:

Hit <DEL> if you want to run SETUP

#### Using the Keyboard with BIOS Setup

The BIOS Setup has a built-in keyboard driver that uses simple keystroke combinations:

#### **Keystroke Function**

<Tab> Move to the next window or field.

Move to the next field to the right, left, above, or below.

<Enter> Select in the current field.

+ Increments a value.

- Decrements a value.

<Esc> Closes the current operation and return to previous level.

<PgUp> Returns to the previous page.

<PgDn> Advances to the next page.

<Home> Returns to the beginning of the text.

<End> Advances to the end of the text.

<Alt> <H> Access a help window.

<Alt> <Spacebar> Exit WINBIOS Setup.

Alphabetic keys A to Z are used in the Virtual Keyboard, and are not case-

ensitive.

Numeric keys 0 to 9 are used in the Virtual Keyboard and Numeric Keypad.

#### BIOS Setup Main Menu

The BIOS Setup main menu is organized into 14 windows. Each window is discussed in this chapter.

Each window contains several options. Clicking on each option activates a specific function. The BIOS Setup options and

functions are described in this chapter. Some options may not be available in your BIOS. The windows are:

- Standard CMOS Setup

- Advanced CMOS Setup

- Advanced Chipset Setting

- Power Management Setup

- PCI/Plug and Play Setup

- Peripheral Setup

- Auto-Detect Hard Drive

- Change User Password

- Change Supervisor Password

- Change Language Settings

- Auto Configuration with Optimal Settings

- Auto Configuration with Fail Safe Settings

- Save Settings and Exit

- Exit Without Saving

#### **Standard Setup**

Standard Setup options are displayed by choosing Standard option from the HIFLEX BIOS Setup menu. All Standard Setup options are described below.

#### Date/Time

Select the Date/Time option to change the date or time. The current date and time are displayed. Enter new values through the displayed window.

#### Floppy Drive A, B

Choose either Floppy Drive A or B to specify the floppy drive type. The settings are  $360 \text{ KB } 5\frac{1}{4}$ ",  $1.2 \text{ MB } 5\frac{1}{4}$ ",  $720 \text{ KB } 3\frac{1}{2}$ ",  $1.44 \text{ MB } 3\frac{1}{2}$ " and  $2.88 \text{ MB } 3\frac{1}{2}$ ".

Pri Master Pri Slave Sec Master Sec Slave

Select one of these options to configure the hard disk drive. Select Auto from the drive parameters screen to let AMIBIOS automatically configure the drive. Choose the desired option to configure the drive. Auto will automatically detect your hard drive every time the computer boots. If required, a specific Hard Drive type may be selected.

#### **Boot Sector Virus Protection**

The options are either Enabled or Disabled.

### **Advanced CMOS Setup**

Advanced CMOS Setup options are displayed by choosing the Advanced CMOS Setup option from the AMIBIOS Setup main menu. All Advanced CMOS Setup options are described in this section.

#### Quick Boot

Set this option to Enabled to instruct AMIBIOS to boot quickly when the computer is powered on. This option replaces the old **Above 1 MB Memory Test** Advanced Setup option. The settings are: Enabled and Disabled.

Pri Master ARMD Emulated as Pri Slave ARMD Emulated as Sec Master ARMD Emulated as Sec Slave ARMD Emulated as

If set to Auto, the default emulation depends on ARMD drive. The default emulation type is floppy for LS120, hard drive for MO and hard drive for ZIP drives.

1st Boot Device 2nd Boot Device 3rd Boot Device 4th Boot Device

These options set the drive boot sequence that Raptor LPX attempts to boot from after AMIBIOS POST completes. The settings are Disabled, 1st IDE, 2nd IDE, 3rd IDE, 4th IDE, Floppy, ARMD-FDD, ARMD-HDD, ATAPI-CDROM, SCSI, Network and I2O. The default is:

1st Boot Device - Floppy 2nd Boot Device - 1st IDE-HDD 3rd Boot Device - ATAPI-CDROM 4th Boot Device - Disabled

#### Try Other Boot Devices

Set this option to Yes (*default*) to instruct AMIBIOS to attempt to boot from any other drive in the system if it cannot find a boot drive among the drives specified in the 1st, 2nd, 3rd and 4th Boot Device options.

#### Initial Display Mode

Set this option to BIOS (*default*) to obtain the normal boot-up screen. Set to Silent to obtain the customized graphic boot-up screen.

#### Floppy Access Control

This option selects usage right from the floppy drive. The setting is either Read/Write (*default*) or Read-Only.

#### Hard Disk Access Control

This option selects usage right from the hard disk. The setting is either Read/Write (*default*) or Read-Only.

#### S.M.A.R.T. for Hard Disks

Set this option to Enabled to permit AMIBIOS to use the SMART (System Management and Reporting Technologies). The setting is either Enabled or Disabled (*default*).

#### **Boot Up Num Lock**

Set this option to Off to turn the Num Lock key off when the computer is booted so you can use the arrow keys on both the numeric keypad and the keyboard.

#### Floppy Drive Swap

Set this option to Enabled to permit drives A: and B: to be swapped. The setting is either Enabled or Disabled (*default*).

#### Floppy Drive Seek

Set this option to Enabled to specify that floppy drive A: will perform a Seek operation at system boot. The setting is either Disabled (*default*) or Enabled.

#### PS/2 Mouse Support

Set this option to Enabled (*default*) to enable AMIBIOS support for a PS/2-type mouse. Disabling mouse will also free up IRQ12.

#### Typematic Rate

The setting is either Fast (default) or Slow.

#### System Keyboard

This option does not specify if a keyboard is attached to the computer. Rather, it specifies if an error message is displayed when a keyboard is not attached. This option permits you to configure workstations with no keyboards.

#### Primary Display

This option configures the type of video card attached to the computer. The settings are Mono, CGA40x25, CGA80x25, VGA/EGA (*default*) and Absent. Use Absent for systems without video cards.

#### Password Check

This option enables password checking every time the system boots or when you run AMIBIOS Setup. If Always is chosen, a user password prompt appears every time the computer is turned on. If Setup is chosen, the password prompt appears if AMIBIOS is executed. See the Advanced Setup chapter for instructions on changing a password. The Optimal and Fail-Safe default is Setup.

#### BOOT to OS/2

Set this option to Enabled if running OS/2 operating system and using more than 64 MB of system memory on the motherboard. The setting is either Yes or No (*default*).

#### Wait for <F1> If Error

If this option is set to Enabled, AMIBIOS waits for the user to press <F1> before continuing. If this option is set to Disabled, AMIBIOS continues the boot process without waiting for <F1> to be pressed.

#### Hit Del Message Display

Set this option to Disabled to prevent the message

```

Hit <DEL> if you want to run Setup

```

from appearing on the first AMIBIOS screen when the computer boots. The setting is either Disabled or Enabled. The Optimal and Fail-Safe default setting is Enabled.

#### Internal Cache

This option enables or disables the L1 internal Cache.

#### System BIOS Cacheable

When set to Enabled, the contents of the F0000h system memory segment can be read from or written to cache memory. The content of this memory segment is always copied from the BIOS ROM to system RAM for faster execution. The setting is either Enabled or Disabled.

C000,16K Shadow C400,16K Shadow

These options specify how the 32 KB of video ROM at C0000h is treated. The settings are: Enabled (*default*), Disabled and Cached.

C800,16K Shadow CC00,16K Shadow D000,16K Shadow D400,16K Shadow D800, 16K Shadow DC00,16K Shadow

These options enable shadowing of the contents of the ROM area named in the option. The ROM area not used by ISA adapter cards is allocated to PCI adapter cards. The settings are: Disabled (*default*), Cached and Enabled.

### **Advanced Chipset Setup**

#### **USB** Function

Set this option to Enabled to enable USB (Universal Serial Bus) support. The setting is either Enabled or Disabled (*default*).

#### USB KB/Mouse Legacy Support

The settings for this option are: Disabled (*default*), Keyboard, Auto and Keyboard+Mouse.

#### Port 64/60 Emulation

The setting for this option is either Enabled or Disabled (*default*).

#### SERR#

The options are Enabled and Disabled (default).

#### PERR#

The options are Enabled and Disabled (default).

#### WSC# Handshake

The options are Enabled (default) and Disabled.

#### **USWC WRITE POST**

The options are Enabled (default) and Disabled

#### BX/GX Master Latency Timer (CLKS)

The options are Disabled, 32, 64 (*default*), 96, 128, 160, 192 and 224.

#### Multi-Trans Timer (CLKS)

The options are Disabled, 32 (*default*), 64, 96, 128, 160, 192 and 224.

#### PCI 1 TO PCI 0 Access

The options are Enabled and Disabled (default).

#### Aperture Access Global Enable

The options are Enabled and Disabled (default).

#### PCI 0 Agent to Aperture Access

N/A.

#### Memory Autosizing Support

The settings for the option are: Auto (*default*) (uses SPD) and Enabled (BIOS test).

#### **DRAM Integrity Mode**

The options are None (default), EC and ECC Hardware.

#### DRAM Refresh Rate

The settings for the option are: 15.6 (*default*), 31.2, 62.4, 124.8, 7.8 and External.

#### **Memory Hole**

The settings for the option are: Disable (*default*), 512K-640K and 15M-16M.

#### SDRAM CAS# Latency

The options are Auto (default), 3 DCKLs and 2 DCKLs.

#### SDRAM RAS# to CAS# Delay

The options are Auto (default), 3 SCKLs and 2 SCKLs.

#### SDRAM RAS# Precharge

The options are Auto (default), 3 SCKLs and 2 SCKLs.

#### SDRAM Precharge Control

The settings for this option are: All, Miss (default) and Miss/All.

#### Power Down SDRAM

The settings for this option are: Enabled and Disabled (default).

#### ACPI Control Register

The settings for this option are: Enabled and Disabled (default).

#### **Gated Clock**

The settings for this option are: Enabled (default) and Disabled.

#### **Graphics Aperture Size**

The settings for this option are: 4, 8, 16, 32, 64 (*default*), 128 and 256.

#### Search for MDA Resources

N/A.

#### 8 bit I/O Recovery Time

The settings are Disabled (default), 1, 2, 3, 4, 5, 6 and 8 Sysclk.

#### 16bit I/O Recovery Time

The settings are Disabled (default), 4, 1, 2 and 3 Sysclk.

#### PIIX4 SERR#

The settings for this option are: Enabled and Disabled (default).

#### USB Passive Release

The settings for this option are: Enabled (default) and Disabled.

#### PIIX4 Passive Release

The settings for this option are: Enabled (default) and Disabled.

#### PIIX4 Delayed Transaction

The settings for this option are: Enabled (default) and Disabled.

#### Type F DMA Buffer Control 1 Type F DMA Buffer Control 2

The settings for these options are: Enabled and Disabled (default).

### DMA-0 Type Thru DMA-7 Type

The settings for these options are: Normal ISA (*default*), PC/PCI and distributed.

#### Memory Buffer Strength

The settings for this option are: Strong (default), Medium and Auto.

#### Manufacture Setting

The settings for this option are: Mode 0 (*default*), Mode 1, Mode 2, Mode 3 and Mode 4.

### Power Management Setup

All Power Management Setup options are described in this section.

#### Power Management/APM

Set this option to APM to enable the power management and APM (Advanced Power Management) features. The settings for this option are: APM (*default*) and Disabled.

#### Power button Function

This option specifies how the power button mounted externally on the computer chassis is used. The settings are: On/Off and suspend. The default setting is On/Off.

#### Green PC Monitor Power State

This option specifies the power state that the green PC-compliant video monitor enters when AMIBIOS places it in a power saving state after the specified period of display inactivity has expired. The settings are Off, Standby and Suspend. The default setting is Suspend.

#### Video Power Down Mode

This option specifies the power management state that the video subsystem enters after the specified period of display inactivity has expired. The settings are Disabled, Standby and Suspend. The default setting is Suspend.

#### Hard Disk Power Down Mode

This option specifies the power management state that the hard disk drive enters after the specified period of display inactivity has expired. The settings are Disabled, Standby and Suspend. The default setting is Suspend.

#### Hard Disk Timeout (Minute)

This option specifies the length of a period of hard disk inactivity. When this period expires, the hard disk drive enters the power-conserving mode specified in the *Hard Disk Power Down Mode* option described on the previous page. The settings are Disabled, 1 Min (minutes) and all one-minute intervals up to and including 15 Min. The default setting is Disabled.

## Power Saving Type

The settings for this option are: Sleep, Stop Clock and Deep Sleep. The default setting is Sleep.

## Standby / Suspend Timer Unit

This option allows a timer to be set for stand by and suspend modes. The options are: 32 seconds, 4 miliseconds, 4 minutes (*default*) and 4 seconds.

## Standby Timeout

This option specifies the length of the period of system inactivity when the computer is in Full-On mode before the computer is placed in Standby mode. In Standby mode, some power use is curtailed. The settings are multiples of the standby suspend timer unit. The default setting is Disabled.

## Suspend Timeout

This option specifies the length of the period of system inactivity when the computer is already in Standby mode before the computer is placed in Suspend mode. In Suspend mode, nearly all power use is curtailed. The settings are multiples of the standby suspend timer unit. The default setting is Disabled.

#### Slow Clock Ratio

This option specifies the speed at which the system clock runs in the Standby Mode power saving state. The settings are expressed as a percentage between the normal CPU clock speed and the CPU clock speed when the computer is in the power-conserving state. The settings are 0-12.5%, 12.5-25%, 25-37.5%, 37.5-50%, 50-62.5%, 62.5-75% and 75-87.5%. The Optimal and Fail-Safe default setting is 50-62.5%.

Display Activity

Device 6 (Serial 1)

Device 7 (Serial2)

Device 8 (Parallel)

Device 5 (Floppy)

Device 0 (Primary Master IDE)

Device 1 (Primary Slave IDE)

Device 2 (Secondary Master IDE)

Device 3 (Secondary Slave IDE)

When set to Monitor, this option enables event monitoring on the device. If set to Monitor and the computer is in a power saving state, AMIBIOS watches for activity. The computer enters the Full On state if any activity occurs. AMIBIOS reloads the Standby and Suspend timeout timers if device activity occurs. The settings are either Monitor or Ignore.

## LAN Wake-Up

The settings for this option are: Disabled (default) and Enabled.

## PCI/Plug and Play Setup

PCI/PnP Setup options are displayed by choosing the PCI/PnP Setup from the AMIBIOS Setup main menu. All PCI/PnP Setup options are described in this section.

#### Plug and Play Aware OS

Set this option to Yes if the operating system installed in the computer is Plug and Play-aware. AMIBIOS only detects and enables PnP ISA adapter cards that are required for system boot. The Windows 95 and 98 operating systems detect and enable all other PnP-aware adapter cards. Windows 95 is PnP-aware. Set this option to No if the operating system (such as DOS, OS/2, Windows 3.x) does not use PnP. You must set this option correctly or PnP-aware adapter cards installed in your computer will not be configured properly. The setting is either No or Yes. The Optimal and Fail-Safe default setting is No.

## PCI Latency Timer (PCI Clocks)

This option sets latency of all PCI devices on the PCI bus. The settings are in units equal to PCI clocks. The settings are 32, 64,

96, 128, 160, 192, 224 and 248. The Optimal and Fail-Safe default setting is 64.

#### PCI VGA Palette Snoop

This option must be set to Enabled if any ISA adapter card installed in the computer requires VGA palette snooping. The setting is either Disabled or Enabled. The default setting is Disabled.

#### Allocate IRQ to PCI VGA

This option determines if the BIOS should assign an IRQ to the VGA card. The settings are either Yes or No. The default setting is No.

#### PCI IDE Bus Master

Set this option to Enabled to specify that the IDE controller on the PCI local bus has bus mastering capability. The setting is either Disabled or Enabled. The default setting is Disabled.

## Off-board PCI IDE Card

This option specifies if an off-board PCI IDE controller adapter card is used in the computer. You must also specify the PCI expansion slot on the motherboard where the off-board PCI IDE controller card is installed. If an off-board PCI IDE controller is used, the onboard IDE controller on the CPU board is automatically disabled. The settings are Auto (default), Slot1, Slot2, Slot3, Slot4, Slot5 and Slot6. If Auto is selected, AMIBIOS automatically determines the correct setting for this option.

## Off-board PCI IDE Primary IRQ

This option specifies the PCI interrupt used by the primary IDE channel on the off-board PCI IDE controller. The settings are: Disabled, INTA, INTB, INTC, INTD and Hardwired. The Optimal and Fail-Safe default setting is Disabled.

## Off-board PCI IDE Secondary IRQ

This option specifies the PCI interrupt used by the secondary IDE channel on the off-board PCI IDE controller. The settings are Disabled, INTA, INTB, INTC, INTD and Hardwired. The Optimal and Fail-Safe default setting is Disabled.

```

PCI Slot1 IRQ Priority

PCI Slot2 IRQ Priority

PCI Slot3 IRQ Priority

PCI Slot4 IRQ Priority

```

These options specify the IRQ priority for PCI devices installed in the PCI expansion slots. The settings are Auto, (IRQ) 3, 4, 5, 7, 9, 10, 11, 12 and 14. The Optimal and Fail-Safe default setting is Auto.

DMA Channel 0 DMA Channel 1 DMA Channel 3 DMA Channel 5 DMA Channel 6 DMA Channel 7

These options allow you to specify the bus type used by each DMA channel. The setting is either PNP or ISA/EISA. The optimal and fail-safe default setting is PNP.

IRQ3 IRQ4 IRQ5 IRQ7 IRQ9 IRQ10 IRQ11 IRQ12 IRQ14 IRQ15

> These options specify the bus that the specified IRQ line is used on. These options allow you to reserve IRQs for legacy ISA adapter cards. These options determine if AMIBIOS should remove an IRQ from the pool of available IRQs passed to

devices that are configurable by the system BIOS. If more IRQs must be removed from the pool, the end user can use these options to reserve the IRQ by assigning an ISA/EISA setting to it. Onboard I/O is configured as PCI/PNP. IRQ12 only appears if the mouse support option in advanced setup is set to disabled. IRQ14 and 15 will not be available if the onboard PCI IDEs are enabled. The optimal and fail-safe default setting is PCI/PNP.

#### Reserved Memory Size

This option specifies the size of the memory area reserved for legacy ISA adapter cards. The settings are Disabled, 16K, 32K and 64K. The Optimal and Fail-Safe default setting is Disabled.

#### Reserved Memory Address

This option specifies the beginning address (in hex) of the reserved memory area. The specified ROM memory area is reserved for use by legacy ISA adapter cards. The settings are C8000, CC000, D0000, D4000, D8000 and DC000. The Optimal and Fail-Safe default setting is CC000.

#### PCI Device Search Order

This option determines which order the PCI slots will be scanned. The setting is either First-Last (*default*) or Last-First.

## **Peripheral Setup**

Peripheral Setup options are displayed by choosing Peripheral Setup from the AMIBIOS Setup main menu. All Peripheral Setup options are described here.

## Onboard FDC

Set this option to Enabled to enable the floppy drive controller on the motherboard. The settings are Auto (AMIBIOS automatically determines if the floppy controller should be enabled), Enabled and Disabled. The default setting is Auto.

## Onboard Serial Port1

This option specifies the base I/O port address of serial port 1. The settings are Auto (AMIBIOS automatically determines the correct base I/O port address), Disabled, 3F8h, 2F8h, 3E8h and 2E8h. The Optimal and Fail-Safe default setting is Auto.

#### Onboard Serial Port2

This option specifies the base I/O port address of serial port 2. The settings are Auto (AMIBIOS automatically determines the correct base I/O port address), Disabled, 3F8h, 2F8h, 3E8h and 2E8h. The Optimal and Fail-Safe default setting is Auto.

## Serial Port2 Mode

This option allows installation of a Infra-red device by the Serial Port. The settings are Normal (*default*), IRDA and ASK IR.

### Infra-Red Transmission Mode

The settings are Full Duplex (default) or Half Duplex.

#### Receiver/Transmitter Polarity

Sets polarity for IR modes.

#### **Onboard Parallel Port**

This option specifies the base I/O port address of the parallel port on the motherboard. The settings are Auto, Disabled, 378h, 278h and 3BCh. The Optimal default setting is Auto.

#### Parallel Port Mode

This option specifies the parallel port mode. The settings are: normal, ECP (*default*) and EPP.

## **EPP Version**

1.7 and 1.9 (default) (available only for EPP mode).

## Parallel Port IRQ

This option specifies the IRQ always used by the parallel port. When the port is set to a fixed address the settings are (IRQ) 5 and (IRQ) 7 (*default*), otherwise it is set to Auto.

#### Parallel Port DMA Channel

This option is only available if the setting for the Parallel Port Mode option is ECP. This option sets the DMA channel used by the parallel port. When the port is set to a fixed address the settings are DMA Channel 0, 1 and 3 (*default*), otherwise it is set to Auto.

### CPU Current Temperature

The current CPU temperature is shown (only available with the optional hardware monitor).

## CPU Overheat Warning

The setting is either Enabled or Disabled (*default*) (only available with the optional hardware monitor).

## CPU Overheat Warning Temperature

Sets the CPU Overheat Warning Temperature set point (only available with the optional hardware monitor).

HW Monitor IN0 (CPU) HW Monitor IN2 (+3.3V) HW Monitor IN3 (+5V) HW Monitor IN4 (+12V) HW Monitor IN5 (-12V) HW Monitor IN6 (-5V) The current voltage is shown (only available with the optional hardware monitor).

## CPU Fan Secondary Fan

The current fan speed is shown (only available with the optional hardware monitor).

#### Onboard IDE

This option specifies the IDE channel used by the onboard IDE controller. The settings are Disabled, Primary, Secondary and Both (*default*).

## **Auto Detect Hard Disk**

Choose this option to let AMIBIOS find the IDE hard disk drive parameters for all IDE drives connected to the primary and secondary IDE channels installed in the system. AMIBIOS automatically configures the drive parameters after it has detected these parameters.

## **Change User Password**

Select the Change User Password from the Security section of the AMIBIOS Setup main menu. Enter the password and press <Enter>. The screen does not display the characters entered. After the new password is entered, retype the new password as prompted and press <Enter>. This option will be available only if Supervisor Passwords exists.

## **Change Supervisor Password**

Select the Change Supervisor Password from the Security section of the AMIBIOS Setup main menu. Enter the password and press <Enter>. The screen does not display the characters entered. After the new password is entered, retype the new password as prompted and press <Enter>.

Remember the Password Keep a record of the new password when the password is changed. If you forget the password, you must erase the system configuration information in NVRAM (Non-Volatile Random Access Memory).

## **Change Language Settings**

N/A.

## **Auto Configuration with Optimal Settings**

You can load the optimal default settings for the AMIBIOS by selecting the Optimal option. The Optimal default settings are best-case values that should optimize system performance. If CMOS is corrupted, the Optimal settings are loaded automatically.

## **Auto Configuration with Fail-Safe Settings**

You can load the Fail-Safe AMIBIOS Setup option settings by selecting the Fail-Safe option from the Default section of the AMIBIOS Setup main menu. The Fail-Safe settings provide far from optimal system performance, but are the most stable settings. Use this option as a diagnostic aid if the system is behaving erratically.

## **Save Settings and Exit**

Exit AMIBIOS saving the changes.

## **Exit without Saving**

Allows to exit AMIBIOS setup without saving.

# Chapter 3

# **Upgrading**

## **Upgrading the System Memory**

The Raptor LPX allows an upgrade of the system memory with up to 384MB unbuffered SDRAM and up to 768MB registered SDRAM DIMM modules. ECC and non-ECC modules are supported. PC100 memory modules are recommended, but required for PIII or 100MHz FSB operation. The Raptor LPX offers 3 DIMM memory sockets. It is very important that the quality of the DIMM is good. Undesirable operation of the system may result if poor quality DIMMs are used. Always purchase your memory from a reliable source.

## **Upgrading the Microprocessor**

The latest revision of the Raptor LPX currently supports socket PGA370 architecture Intel Celeron Processors and PIII PGA processors. Please, check the manufacturer's web site for details and revisions regarding CPU speed.

Since the Raptor LPX features CPU auto-sensing device there is only one jumper to be set when changing the CPU, JP1, if it's no set to auto. This jumper is the Clock Speed selector.

| Raptor | LPX- | Installation | Guide |

|--------|------|--------------|-------|

|        |      |              |       |

**User's Notes:**

# Appendix A

# Technical Specifications

## **Chipsets**

Core Logic

Intel 440BX Chipset.

Peripheral I/O

Standard Microsystems (SMSC) FDC37B722.

Micro Processor Support

Celeron and PIII PGA processors up to 100MHz FSB.

## **System Memory**

**Memory Capacity**

Up to 768MB registered SDRAM or up to 384MB unbuffered SDRAM DIMM Modules.

Memory Type

Three sockets for JEDEC standard (168 pins) DIMMs. The memory configuration is set automatically through BIOS via SPD. Supports SDRAM 3.3V SDRAM PC66 and PC100 memory modules. ECC and non-ECC, registered and unbuffered modules are supported.

## **Bios**

System BIOS

AMI Hiflex BIOS with Flash BIOS option.

## Flash BIOS

Optional feature for System BIOS. Flash programming built into the BIOS. BIOS to be flashed is read from a floppy.

## **Embedded I/O**

## IDE

Two PCI EIDE controllers. Supports up to 4 devices. Ultra DMA up to 33MB/sec. supported. ATAPI compatible. 34 pin headers on-board.

## **Floppy**

Up to two floppy disk drives. Sizes supported are: 5.25" 360K and 1.2MB; 3.5" 720K, 1.44MB and 2.88MB.

#### Serial Ports

Two high speed 16550 compatible UARTS. BIOS configurable as COM1 - 4.

## **USB** Interfaces

On-board dual USB.

#### Parallel Port

One Centronics compatible, bi-directional (PS/2 compatible). Microsoft/HP EPC/EPP high speed.

#### Mouse Port

One PS/2 compatible mouse controller.

## PC 104 - Plus Interface

One PC 104-Plus expansion/stack-up interface and power connectors.

## Disk-On-Chip - Solid State Flash Disk

On-board support for one Disk-on-Chip device, currently up to 288MB. Addresses selectable through jumper JP7.

#### **On-board Ethernet**

On-board auto-sensing, bus mastering 10/100 Ethernet (Intel 82559ER).

## LCD/CRT video controller

On-board CRT video controller/LCD(optional) (C&T 65555) 2MB - 4MB(optional).

## **Industrial Devices**

## Watchdog Timer

On-board 150, 600 and 1200ns hardware and software watchdog timer with VCC monitor.

### POST Code

On-board POST code display for self-diagnostics and custom applications (refer to Appendix D).

## Temperature and Voltage Device

On-board voltage, CPU fan speed and CPU temperature monitoring devices (optional).

## Power Management

Power button function: advanced power management support.

## **Miscellaneous**

## CMOS/Battery

RTC with lithium battery. No external battery is required.

## **Control Panel Connections**

Reset, Keylock, Speaker. LEDs for power and IDE.

## CPU Socket

Standard ZIF (Zero Insertion Force), PGA 370.

#### Form Factor

LPX form factor (8.3" x 11").

## **PCB** Construction

Six Layers, dry film mask.

## **Manufacturing Process**

Automated surface mount.

## Reliability

MTBF: 52,300 hours.

Table A-1 Environmental

| Environmental Operating |                                    | Non-operating                      |

|-------------------------|------------------------------------|------------------------------------|

| Temperature             | 0° to +55° C                       | -40° to +65° C                     |

| Humidity                | 5 to 95% @ 40° C<br>non-condensing | 5 to 95% @ 40° C<br>non-condensing |

| Shock                   | 2.5G @ 10ms                        | 10G @ 10ms                         |

| Vibration               | 0.25 @ 5-100Hz                     | 5 @ 5-100Hz                        |

## **Memory Map**

| Address   | Address           |        |              |

|-----------|-------------------|--------|--------------|

| Range     | Range             | Size   | Description  |

| Decimal   | Hexadecimal       |        |              |

| 960K-1M   | 0F0000-           | 64 KB  | Upper BIOS   |

| 900K-1WI  | 0FFFFF            | 04 KD  | Opper BIOS   |

| 896K-960K | 0E0000-           | 64 KB  | Lower BIOS   |

| 890K-900K | 0EFFFF            | 04 KD  | Lower BIOS   |

|           | 00000             |        | Expansion    |

| 768K-896K | 0C0000-<br>0DFFFF | 128 KB | Card BIOS    |

|           |                   |        | and Buffer   |

|           |                   |        | Standard     |

| 640K-768K | 0A0000-<br>0BFFFF | 128 KB | PCI/ISA      |

| 040K-/08K |                   |        | Video        |

|           |                   |        | Memory       |

| 512K-640K | 080000-<br>09FFFF |        | Ext.         |

|           |                   | 128 KB | Conventional |

|           |                   |        | memory       |

| 017 71017 | 000000-           | 512 VD | Conventional |

| 0K- 512K  | 07FFFF            | 512 KB | memory       |

## **DMA Channels**

| DMA# | Data Width    | System Resource         |

|------|---------------|-------------------------|

| 0    | 8- or 16-bits |                         |

| 1    | 8- or 16-bits | Parallel port (for ECP) |

| 2    | 8- or 16-bits | Floppy Drive            |

| 3    | 8- or 16-bits | Parallel port (for ECP) |

| 4    | Reserved-     | cascade channel         |

| 5    | 16-bits       | Open                    |

| 6    | 16-bits       | Open                    |

| 7    | 16-bits       | Open                    |

# I/O Map

| Address (hex)  | Description                                 |  |

|----------------|---------------------------------------------|--|

| 0000-000F      | DMA 1                                       |  |

| 0020-0021      | Interrupt Controller 1                      |  |

| 0040           | Timer/Counter 0                             |  |

| 0041           | Timer/Counter 1                             |  |

| 0042           | Timer/Counter 2                             |  |

| 0043           | Timer Control Word                          |  |

| 0060           | Keyboard Controller Byte _ Reset IRQ        |  |

| 0061           | NMI Status and Control                      |  |

| 0070, bit 7    | NMI enable                                  |  |

| 0070, bits 6:0 | RTC Index                                   |  |

| 0071           | RTC Data                                    |  |

| 0072           | RTC Extended Index                          |  |

| 0073           | RTC Extended Data                           |  |

| 0000 0000      | DMA page registers / POST code display also |  |

| 0080-008F      | located at 0080h                            |  |

| 0092           | Port 92                                     |  |

| 00A0-00A1      | Interrupt Controller 2                      |  |

| 00B2-00B3      | APM control                                 |  |

| 00C0-00DE      | DMA 2                                       |  |

| 00F0           | Coprocessor Error                           |  |

| 0110           | Watch-Dog Timer (default)                   |  |

| 0170 _ 0177    | Secondary IDE channel                       |  |

| 01F0_01F7      | Primary IDE channel                         |  |

| 029x           | LM79                                        |  |

| 0278-027F      | LPT2 (if selected)                          |  |

| 02E8-02EF      | COM4 (if selected)                          |  |

| 02F8-02FF      | COM2 (default)                              |  |

| 0310           | Watch-Dog Timer (if selected)               |  |

| 0376           | Secondary IDE channel command port          |  |

| 0377           | Floppy channel 2 command                    |  |

| 0377, bit 7    | Floppy disk change, channel 2               |  |

| 0377, bits 6:0 | Secondary IDE channel status port           |  |

| 0378-037F      | LPT1 (default)                              |  |

| 03B4-03B5      | Video (VGA)                                 |  |

| 03BA           | Video (VGA)                                 |  |

| 03BC-03CD      | LPT3 (if selected)                          |  |

| 03C0-03CA      | Video (VGA)                                 |  |

| 03CC           | Video (VGA)                                 |  |

| 03CE-03CF      | Video (VGA)                                 |  |

| Address (hex)  | Description                         |

|----------------|-------------------------------------|

| 03D4-03D5      | Video (VGA)                         |

| 03DA           | Video (VGA)                         |

| 03E8-03EF      | COM3 (if selected)                  |

| 03F0-03F5      | Floppy Channel 1                    |

| 03F6           | Primary IDE channel command port    |

| 03F7           | Floppy Channel 1 command            |

| 03F7, bit 7    | Floppy disk change channel 1        |

| 03F7, bits 6:0 | Primary IDE channel status report   |

| 03F8-03FF      | COM1 (default)                      |

| 04D0-04D1      | INTC-1 Edge/Level Control           |

| 0CF8-0CFB - 4  | PCI configuration address register  |

| bytes          | r Ci configuration address register |

| 0CF9           | Reset control register              |

| 0CFC-0CFF - 4  | PCI configuration data register     |

| bytes          | 1 C1 configuration data register    |

## **On-board Devices**

## DISK ON CHIP

Memory address selectable between: D000(default), D4000, D8000, DC000.

## **PCI Configuration Space Map**

| Bus# | Device # | Function # | Description            |

|------|----------|------------|------------------------|

| 00   | 00       | 00         | 440BX (Host Bridge)    |

| 00   | 01       | 00         | 440BX A.G.P. bus       |

| 00   | 07       | 00         | PIIX4 PCI/ISA bridge   |

| 00   | 07       | 01         | PIIX4 IDE bus master   |

| 00   | 07       | 02         | PIIX4 USB              |

| 00   | 07       | 03         | PIIX4 Power Management |

| 00   | 12       | 00         | PCI expansion slot 1   |

| 00   | 14       | 00         | PCI expansion slot 2   |

| 00   | 0F       | 00         | PCI expansion slot 3   |

| 00   | 0D       | 00         | Video Controller       |

| 00   | 0E       | 00         | 82559ER Ethernet       |

## <u>Interrupts</u>

| IRQ | System Resource                                   |

|-----|---------------------------------------------------|

| NMI | I/O channel check                                 |

| 0   | Reserved, interval timer                          |

| 1   | Reserved (keyboard)                               |

| 2   | Reserved (cascade)                                |

| 3   | COM2*                                             |

| 4   | COM1*                                             |

| 5   | User Available                                    |

| 6   | Floppy Drive                                      |

| 7   | LPT1*                                             |

| 8   | Real time clock                                   |

| 9   | User Available                                    |

| 10  | User Available                                    |

| 11  | User Available                                    |

| 12  | PS/2 mouse port (if present, else user available) |

| 13  | Reserved (math coprocessor)                       |

| 14  | Primary IDE (if present, else user available)     |

| 15  | Secondary IDE (if present, else user available)   |

<sup>\*</sup>Default, but can be changed to another IRQ

## **PCI Interrupt Routing Map**

| PIIX4<br>Signal | IDSEL | PIRQA | PIRQB | PIRQC | PIRQD |

|-----------------|-------|-------|-------|-------|-------|

| PCI Slot 1      | AD29  | INTA  | INTB  | INTC  | INTD  |

| PCI Slot 2      | AD31  | INTB  | INTC  | INTD  | INTA  |

| PCI Slot 3      | AD26  | INTC  | INTD  | INTA  | INTB  |

| Video           | AD24  |       |       |       |       |

| Ethernet        | AD25  |       | INTB  |       |       |

| USB             | -     |       |       |       | INTD  |

## **SMBUS**

| Device      | Slave Address |

|-------------|---------------|

| MAX1617     | 0011000b      |

| LM79        | 0101101b      |

| DIMM0       | 1010000b      |

| DIMM1       | 1010001b      |

| DIMM2       | 1010010b      |

| SDRAM Clock | 1101001b      |

## **Connectors Pin-out**

How to identify pin number 1: Looking to the solder side (The board side without components) of the PCB (Printed Circuit Board), pin number 1 will have a squared pad . Other pins will have a circular pad .

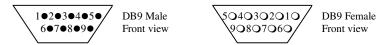

How to identify other pins: Connectors type DB, PS/2, RJ45, Power ATX and PC 104/plus are industry standards. DB connectors, for instance, are numbered sequentially. The first row is numbered in sequence (be aware that male and female connectors are mirrored – male connectors are numbered from left to right when viewed from front and female connectors are numbered from right to left when viewed from front). The following rows resume the counting on the same side of pin number 1. The counting is NOT circular like Integrated Circuits (legacy from electronic tubes).

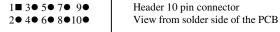

Header connectors are numbered alternately, i.e. pin number 2 is in the other row, but in the same column of pin number 1. Pin number 3 is in the same row of pin 1, but in the next column and so forth.

<u>Table A-9 Serial Ports COM 1 and COM 2 Connectors</u>

| Pin# | Serial Ports DB9M – J13 and J14 |

|------|---------------------------------|

| 1    | DCD                             |

| 2    | RX                              |

| 3    | TX                              |

| 4    | DTR                             |

| 5    | GND                             |

| 6    | DSR                             |

| 7    | RTS                             |

| 8    | CTS                             |

| 9    | RI                              |

Table A-10 J30 Power LED/Keylock Header Connector Pin-out

| Pin# | PWR LED/KBD Lock Header – J30 |

|------|-------------------------------|

| 1    | Power LED Anode               |

| 2    | NC                            |

| 3    | Cathode                       |

| 4    | KEYLOCK#                      |

| 5    | Cathode                       |

Table A-11 Auxiliary COM 2 Serial Port Header

| Pin# | Serial Port Header – J41 |  |  |  |  |

|------|--------------------------|--|--|--|--|

| 1    | DCD                      |  |  |  |  |

| 2    | DSR                      |  |  |  |  |

| 3    | RX                       |  |  |  |  |

| 4    | RTS                      |  |  |  |  |

| 5    | TX                       |  |  |  |  |

| 6    | CTS                      |  |  |  |  |

| 7    | DTR                      |  |  |  |  |

| 8    | RI                       |  |  |  |  |

| 9    | GND                      |  |  |  |  |

| 10   | Speaker                  |  |  |  |  |

Table A-12 Ethernet RJ45

| Pin# | Ethernet RJ45 – J6 |  |  |  |  |

|------|--------------------|--|--|--|--|

| 1    | TX+                |  |  |  |  |

| 2    | TX-                |  |  |  |  |

| 3    | RX+                |  |  |  |  |

| 4    | Shorted to 5       |  |  |  |  |

| 5    | Shorted to 4       |  |  |  |  |

| 6    | RX-                |  |  |  |  |

| 7    | Shorted to 8       |  |  |  |  |

| 8    | Shorted to 7       |  |  |  |  |

Table A-13 Parallel DB25 Connector

| Pin#  | Parallel DB25F – J15 |

|-------|----------------------|

| 1     | -STROBE              |

| 2     | +DATA BIT 0          |

| 3     | +DATA BIT 1          |

| 4     | +DATA BIT 2          |

| 5     | +DATA BIT 3          |

| 6     | +DATA BIT 4          |

| 7     | +DATA BIT 5          |

| 8     | +DATA BIT 6          |

| 9     | +DATA BIT 7          |

| 10    | ACK1                 |

| 11    | BUSY                 |

| 12    | PAPER EMPTY          |

| 13    | SLCT                 |

| 14    | AUTOFEED             |

| 15    | ERROR                |

| 16    | INIT                 |

| 17    | SLCT IN              |

| 18-25 | GND                  |

Table A-14 USB Connector Pin-out

| Pin# | USB Connector – J19 |  |  |  |

|------|---------------------|--|--|--|

| 1    | +5V – USB1          |  |  |  |

| 2    | -D – USB1           |  |  |  |

| 3    | +D – USB1           |  |  |  |

| 4    | GROUND - USB1       |  |  |  |

| 5    | +5V – USB2          |  |  |  |

| 6    | -D – USB2           |  |  |  |

| 7    | +D – USB2           |  |  |  |

| 8    | GROUND – USB2       |  |  |  |

Table A-15 J20 LCD Header Pin-out

| Pin# | LCD Header – J20 |  |  |  |

|------|------------------|--|--|--|

| 1    | VDDSAFE          |  |  |  |

| 2    | +12VSAFE         |  |  |  |

| 3    | VEESAFE          |  |  |  |

| 4    | NC               |  |  |  |

| 5    | ENABLE BACKLIGHT |  |  |  |

| 6    | GROUND           |  |  |  |

| 7    | M                |  |  |  |

| 8    | DE               |  |  |  |

| 9    | GROUND           |  |  |  |

| 10   | LP               |  |  |  |

| 11   | FLM              |  |  |  |

| 12   | GROUND           |  |  |  |

| 13   | SHIFT CLOCK      |  |  |  |

| 14   | GROUND           |  |  |  |

| 15   | P0               |  |  |  |

| 16   | P1               |  |  |  |

| 17   | GROUND           |  |  |  |

| 18   | P2               |  |  |  |

| 19   | P3               |  |  |  |

| 20   | GROUND           |  |  |  |

Appendix A: Technical Specifications

| Pin# | LCD Header – J20 |

|------|------------------|

| 21   | P4               |

| 22   | P5               |

| 23   | GROUND           |

| 24   | P6               |

| 25   | P7               |

| 26   | GROUND           |

| 27   | P8               |

| 28   | P9               |

| 29   | GROUND           |

| 30   | P10              |

| 31   | P11              |

| 32   | GROUND           |

| 33   | P12              |

| 34   | P13              |

| 35   | GROUND           |

| 36   | P14              |

| 37   | P15              |

| 38   | GROUND           |

| 39   | P16              |

| 40   | P17              |

| 41   | GROUND           |

| 42   | P18              |

| 43   | P19              |

| 44   | GROUND           |

| 45   | P20              |

| 46   | P21              |

| 47   | GROUND           |

| 48   | P22              |

| 49   | P23              |

| 50   | GROUND           |

<u>Table A-16 Infra Red, HDD LED, CPU Fan, SYS FAN, LAN ACT LED, LAN Speed LED, Speaker and Wake On LAN.</u>

| Connector | Description                    |       |       |           |            |       |          |

|-----------|--------------------------------|-------|-------|-----------|------------|-------|----------|

| J2        | Infra Red                      |       |       |           |            |       |          |

| 02        | 1)Rx                           | 2)Tx  | 3)GND | 4)NC      | 5)I        | Key   | 6)Vcc    |

|           |                                |       |       |           |            |       |          |

| J31       |                                |       |       | DD L      |            |       |          |

|           |                                | 1)An  | ode   |           | 2          | 2)Cat | hode     |

|           |                                |       |       |           |            |       |          |

| J32       |                                |       |       | PU F      |            |       |          |

| 002       | 1)5                            | Sense |       | 2)+12     | V          |       | 3)GND    |

|           |                                |       |       |           |            |       |          |

| J33       |                                |       | S     | YS F      | AN         |       |          |

| 000       | 1)5                            | Sense |       | 2)+12     | 12V 3)GND  |       | 3)GND    |

|           |                                |       |       |           |            |       |          |

| J3        |                                |       |       | I ACT     |            |       |          |

|           |                                | 1)An  | ode   |           | 2)Cathode  |       |          |

|           |                                |       |       |           |            |       |          |

| J4        |                                |       |       | Spee      | d LED      |       |          |

| U-T       | 1)Anode                        |       |       | 2)Cathode |            |       |          |

|           |                                |       |       |           |            |       |          |

| J36       | Speaker                        |       |       |           |            |       |          |

|           | 1)+5V 2)NC                     |       |       |           | 3)NC       | )     | 4)Signal |

|           |                                |       |       |           |            |       |          |

| J35       | Wake On LAN                    |       |       |           |            |       |          |

| 000       | 1)5V Standby 2)GND 3)WOL Signa |       |       |           | VOL Signal |       |          |

Table A-17 J27 DB15 Standard VGA CRT Connector Pin-out

| Pin# | CRT Header- J27 |  |  |  |  |

|------|-----------------|--|--|--|--|

| 1    | RED             |  |  |  |  |

| 2    | GREEN           |  |  |  |  |

| 3    | BLUE            |  |  |  |  |

| 4    | NO CONNECT      |  |  |  |  |

| 5    | GROUND          |  |  |  |  |

| 6    | GROUND          |  |  |  |  |

| 7    | GROUND          |  |  |  |  |

| 8    | GROUND          |  |  |  |  |

| 9    | +5V             |  |  |  |  |

| 10   | GROUND          |  |  |  |  |

| 11   | NO CONNECT      |  |  |  |  |

| 12   | DDC DATA        |  |  |  |  |

| 13   | HORIZONTAL SYNC |  |  |  |  |

| 14   | VERTICAL SYNC   |  |  |  |  |

| 15   | DDC CLOCK       |  |  |  |  |

Table A-18 J5 Ethernet Header Connector Pin-out

| Pin# | Ethernet Header – J5           |  |  |  |

|------|--------------------------------|--|--|--|

| 1    | Connected to pin 4 & 5 of RJ45 |  |  |  |

| 2    | Connected to pin 7 & 8 of RJ45 |  |  |  |

| 3    | RX+                            |  |  |  |

| 4    | RX-                            |  |  |  |

| 5    | Speed LED Cathode              |  |  |  |

| 6    | Speed LED Anode                |  |  |  |

| 7    | ACT LED Cathode                |  |  |  |

| 8    | ACT LED Anode                  |  |  |  |

| 9    | TX+                            |  |  |  |

| 10   | TX-                            |  |  |  |

Table A-19 J12 Riser Slot Pin-out

| Pin# | Description | Pin# | Description |

|------|-------------|------|-------------|

| 1    | IOCHK#      | 40   | MEMR#       |

| 2    | SD7         | 41   | MEMW#       |

| 3    | SD6         | 42   | SD8         |

| 4    | SD5         | 43   | SD9         |

| 5    | SD4         | 44   | SD10        |

| 6    | SD3         | 45   | SD11        |

| 7    | SD2         | 46   | SD12        |

| 8    | SD1         | 47   | SD13        |

| 9    | SD0         | 48   | SD14        |

| 10   | IOCHRDY     | 49   | SD15        |

| 11   | AEN         | 50   | GND         |

| 12   | SA19        | 51   | BRSTDRV     |

| 13   | SA18        | 52   | VCC         |

| 14   | SA17        | 53   | IRQ9        |

| 15   | SA16        | 54   | NC          |

| 16   | SA15        | 55   | DRQ2        |

| 17   | SA14        | 56   | NC          |

| 18   | SA13        | 57   | ZEROWS#     |

| 19   | SA12        | 58   | +12V        |

| 20   | SA11        | 59   | GND         |

| 21   | SA10        | 60   | SMEMW#      |

| 22   | SA9         | 61   | SMEMR#      |

| 23   | SA8         | 62   | IOW#        |

| 24   | SA7         | 63   | IOR#        |

| 25   | SA6         | 64   | DACK#3      |

| 26   | SA5         | 65   | DRQ3        |

| 27   | SA4         | 66   | DACK#1      |

| 28   | SA3         | 67   | DRQ1        |

| 29   | SA2         | 68   | REFRESH#    |

| 30   | SA1         | 69   | SYSCLK      |

| 31   | SA0         | 70   | IRQ7        |

| 32   | SBHE#       | 71   | IRQ6        |

| 33   | LA23        | 72   | IRQ5        |

| 34   | LA22        | 73   | IRQ4        |

| 35   | LA21        | 74   | IRQ3        |

| 36   | LA20        | 75   | DACK#2      |

| 37   | LA19        | 76   | TC          |