# SI54P AIO

(for Award BIOS)

USER'S MANUAL

## SI54P-AIO User's Manual

### **Trademarks**

All brand and product names used in this manual may be trademarks or registered trademarks of their respective companies.

## Table of Contents

| Introduction                                 |    |

|----------------------------------------------|----|

| General Specifications                       | 1  |

| System Chipset                               | 3  |

|                                              |    |

| System Memory                                |    |

| Cache Memory Subsystems                      | Q  |

| Cache Memory Subsystems                      |    |

| Lucia and Catting on a social Canada and and |    |

| Jumper Settings and Connectors               |    |

| Setting the Jumpers                          |    |

| Connectors                                   |    |

| Board Layouts                                | 11 |

|                                              |    |

| Built-in BIOS SETUP Program                  |    |

| SETUP Program                                | 11 |

| Standard CMOS SETUP                          | 14 |

| BIOS Features SETUP                          |    |

| Chipset Features SETUP                       |    |

| Power Management SETUP                       |    |

| PCI Configuration SETUP                      |    |

| Load BIOS Defaults                           |    |

| Load SETUP Defaults                          |    |

| Supervisor & User Password                   | 35 |

| IDE HDD Auto Detection                       |    |

| Quitting SETUP                               |    |

| C                                            |    |

## 1 Introduction

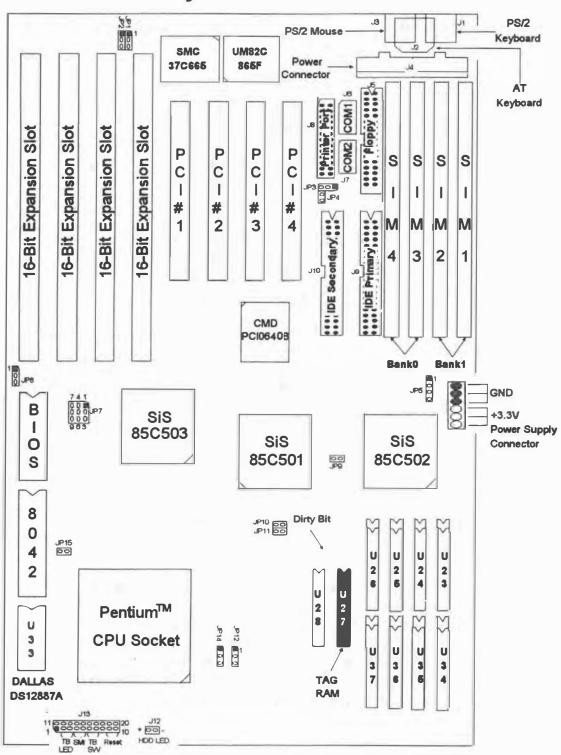

The SI54P AIO is a Pentium<sup>TM</sup> PCI Bus mainboard. It uses the SiS 85C501, 85C502, 85C503 system chipset, CMD PCI0640B PCI Bus IDE Controller, and SMC 37C665 Super I/O Controller. Other on-board specifications include 4 AT Bus slots and 4 PCI slots, 2 memory banks with memory sizes of up to 128MB, and cache sizes from 256KB to 1MB.

## 1.1 General Specifications

Processor:

Intel Pentium™ 75/90/100

Chipset:

SiS 85C501 (PCI/ISA Cache Memory Controller)

SiS 85C502 (PCI Local Data Buffer)

SiS 85C503 (PCI System I/O)

CMD PCI0640B (PCI Bus IDE Controller) SMC 37C665 (Super I/O Controller) UMC 82C865 (I/O TTL Integration)

**External Cache:**

256/512 KB or 1MB cache supporting write

back or write-through policies

**Memory Size:**

2 banks of DRAM with memory size capacity of

up to 128MB, all supporting double-sided SIMMs

**BIOS:**

Award

**Slots:**

Four 16-bit ISA slots

Four PCI slots

**Connectors:**

Power

**Keylock & Power LED**

Hardware Reset

Speaker Turbo LED Turbo Switch Suspend HDD LED

**Form Factor:**

Baby-AT

PCB:

4 layers

### System Chipset

#### SIS 85C501

- Supports Pentium™ processor at 50/60/66 MHz bus speed

- Integrated second level (L2) cache modes

- write-through and write-back cache modes

- direct mapped organization

- supports standard and burst SRAMs

- supports 128KB to 2MB cache sizes

- cache read/write cycle of 3-2-2-2 or 4-3-3-3 using standard SRAM at 66MHz

- Integrated DRAM controller

- supports 2MB to 128MB of cacheable main memory

- 1 level posted write buffer of 4 Qwords deep

- concurrent write back

- CAS#-before-RAS# transparent DRAM refresh

- 256K/1M/4M/16M\*N 70ns fast page mode DRAM support

- programmable DRAM speed

#### **SIS 8**5C502

- Three integrated posted write buffers and two read buffers increase system performance

- 1 level CPU-to-Mem posted write buffer with 4 Qwords deep

- 4 levels CPU-to-PCI posted write buffer with 4 Dwords deep

- 1 level PCI-to-Mem posted write buffer with 1 Qword deep

- 1 level Mem-to-CPU read buffer with 1 Qword deep

- 1 level Mem-to-PCI read buffer with 1 Qword deep

- Provides a 64-bit Pentium<sup>TM</sup>, DRAM data bus and 32-bit PCI data bus

- Operates synchronously to the 66.7MHz CPU and 33.3MHz PCI clocks

- Provides parity generation for memory writes

#### SIS 85C503

Integrated bridge between PCI Bus and ISA Bus

- translates PCI Bus cycles into ISA Bus cycles

- translates ISA master or DMA cycles into PCI Bus cycles

- provides PCI-to-ISA memory one Dword posted write buffer

- Integrated ISA Bus compatible logic

- Supports reroutability of four PCI interrupts to any unused IRQ interrupt

- Supports Flash ROM

#### CMD PC10640B

- Fully compatible with the latest PCI IDE and ATAPI specifications

- The most complete 32-bit driver support in the industry (DOS, Windows 3.1 Past Disk, Windows NT, OS/2, Novell & SCO Unix 32-bit driver support)

- Programmable data transfer timing supports customized setting for 4 IDE devices

- Read-ahead and write-back buffers enhance transfer rates and allow concurrent operations

- Suitable for PCI motherboard or PCI expansion card applications

- Fully supports and surpasses enhance IDE Mode-3

- Supports program I/O function

#### **SMC 37C665**

- Super I/O controller

- Two 16C550 compatible UARTs

- One multi-mode parallel port which include EPP and ECP support

## 2 System Memory

SI54P AIO accepts a minimum of 2MB and a maximum of 128MB onboard. There are two memory banks which support 256/512 KB or 1/2/4/8/16 MB 72-pin type, single- and/or double-density modules.

Important: DRAM insertion on every bank should come in pair and of the same type. For instance, if you only have two DRAM modules, you cannot install one DRAM module in socket SIM1 and another DRAM module of the same type on SIM3. Likewise, memory type mixing is NOT allowed within a bank.

The following table lists all the possible DRAM module combinations and the total memory amount for each option.

| Bank 0    |           | Bank1     |           | Total       |  |

|-----------|-----------|-----------|-----------|-------------|--|

| SIM3      | SIM4      | SIM1      | SIM2      | Memory Size |  |

| 256K x 36 | 256K x 36 | None      | None      | 2MB         |  |

| 256K x 36 | 256K x 36 | 256K x 36 | 256K x 36 | 4MB         |  |

| 512K x 36 | 512K x 36 | None      | None      | 4MB         |  |

| 512K x 36 | 512K x 36 | 512K x 36 | 512K x 36 | 8MB         |  |

| 512K x 36 | 512K x 36 | 4M x 36   | 4M x 36   | 36MB        |  |

| 1M x 36   | 1M x 36   | None      | None      | 8MB         |  |

| 1M x 36   | 1M x 36   | 1M x 36   | 1M x 36   | 16MB        |  |

| 1M x 36   | 1M x 36   | 4M x 36   | 4M x 36   | 36MB        |  |

| 2M x 36   | 2M x 36   | None      | None      | 16MB        |  |

| 2M x 36   | 2M x 36   | 2M x 36   | 2M x 36   | 32MB        |  |

| 2M x 36   | 2M x 36   | 4M x 36   | 4M x 36   | 48MB        |  |

| 4M x 36   | 4M x 36   | 4M x 36   | 4M x 36   | 64MB        |  |

| 8M x 36   | 8M x 36   | None      | None      | 64MB        |  |

| 8M x 36   | 8M x 36   | 8M x 36   | 8M x 36   | 128MB       |  |

Table 2-1. Memory Configurations and Requirements

## **Cache Memory Subsystems**

| Cache Size | Darity RAM<br>(U28) | TAG RAM<br>(U27) | Data (U23-26)<br>(U34 - U37) |

|------------|---------------------|------------------|------------------------------|

| 256KB      | 32Kx8 (5V)          | 32Kx8 (5V)       | 32Kx8 (3.3V)                 |

| 512KB      | 32Kx8 (5V)          | 32Kx8 (5V)       | 64Kx8 (3.3V)                 |

| 1MB        | 32Kx8 (5V)          | 32Kx8 (5V)       | 128Kx8 (3.3V)                |

Table 2-2. Second Level Cache Memory Configurations

## 3 Jumper Settings and Connectors

## 3.1 Setting the Jumpers

The table below summarizes the functions and jumper settings on the SI54P AIO.

|                                   | Function                                 | Jumper Settings          |

|-----------------------------------|------------------------------------------|--------------------------|

|                                   | 50MHz (for 75MHz CPU)                    | JP7 short 2-3, 5-6, 7-8  |

| <b>CPU Clock Select</b>           | 60MHz (for 90MHz CPU)                    | JP7 short 2-3, 4-5, 8-9  |

|                                   | 66MHz (for 100MHz CPU)                   | JP7 short 1-2, 5-6, 7-8  |

|                                   | Internal Cache Write-back                | JP12 short 1-2           |

| CPU Signal Select                 | Internal Cache Write-<br>through         | JP12 short 2-3           |

|                                   | Always invalidated                       | JP14 short 1-2           |

|                                   | Write to invalidated                     | <b>JP14</b> short 2-3    |

| External Cache<br>Memory Settings | 256KB (with 32Kx8<br>SRAMs)              | JP11 open<br>JP10 open   |

|                                   | 512KB (with 64Kx8<br>SRAMs)              | JP11 short<br>JP10 open  |

|                                   | 1MB (with 128Kx8 SRAMs)                  | JP11 short<br>JP10 short |

| ROM BIOS                          | For Programming Flash<br>ROM (+5V) used  | JP8 short 1-2            |

|                                   | For Programming Flash<br>ROM (+12V) used | JP8 short 2-3            |

|                                   | EPROM                                    | JP8 open                 |

| Function          |                                                                                                       | Jumper Settings                |  |

|-------------------|-------------------------------------------------------------------------------------------------------|--------------------------------|--|

|                   | Enable IDE                                                                                            | JP4 open                       |  |

| On-board PCI IDE  | Disable IDE                                                                                           | JP4 short                      |  |

|                   | Enabled                                                                                               | JP3 short 1-2                  |  |

| On-board I/O      | Disabled                                                                                              | JP3 short 2-3                  |  |

|                   | ECP Mode Parallel Port DRQ1<br>DACK1 Selection                                                        | JP1 short 1-2<br>JP2 short 2-3 |  |

| ECP Mode          | ECP Mode Parallel Port DRQ3<br>DACK3 Selection                                                        | JP1 short 2-3<br>JP2 short 1-2 |  |

|                   | Enabled                                                                                               | JP9 short                      |  |

| DRAM Parity Check | Disabled                                                                                              | JP9 open                       |  |

|                   | All SIMMs are single density modules                                                                  | JP5 short 2-3                  |  |

| Memory Select     | All SIMMs are double density modules or SIMMs 3/4 are double density and SIMMs 1/2 are single density | JP5 short 1-2, 3-4             |  |

#### Table 4-1. Jumper Settings

Note1: If a flash ROM is installed on the mainboard, please refer to the README.DOC file in the Flash Utility diskette

before programming the Flash ROM BIOS.

Note2: Before installing the driver for on-board PCI IDE (CMD

PCI0640B), consult the readme file in the CMD Driver

Diskette.

Note3: 1. JP8 open for EPROM and Flash ROM normal use.

2. When you update your system BIOS with Flash ROM

or JP8 to short 2-3 for +12V Flash ROM.

3. After updated the system BIOS, you should remove the jumper JP8.

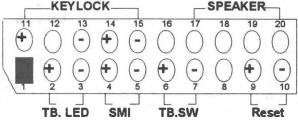

### 3.2 Connectors

There are several connectors located on the SI54P AIO. Their functions are listed below.

| Connector                                            | Function                                                                                                                                                                                                         |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J2<br>J4<br>J5<br>J6<br>J7<br>J8<br>J9<br>J10<br>J11 | AT Keyboard Connector Power Connector Floppy Connector COM1 Port Connector COM2 Port Connector Printer Port Connector IDE Primary Connector IDE Secondary Connector Power Connector (For 3.3V) HDD LED Connector |

| J13                                                  | 2X10 JUMPER BLOCK                                                                                                                                                                                                |

|                                                      | KEYLOCK SPEAKE                                                                                                                                                                                                   |

pin 2-3: Turbo LED

pin 4-5: Suspend Push Button (SMI)

PIN 6-7: Turbo Switch

pin 9-10: Hardware Reset

pin11-13: System Power LED & pin 14-15 Keylock

pin 17-20: Speaker

Note:

J13 (pin6-7), Turbo Switch Function Procedure:

a. Short 2-3 for the jumper setting of JP12.

b. Set the L1 Cache Update Mode into (WT) Write Through within the BIOS Chipset Features SETUP.

c. After finishing Steps a & b, the H/W turbo switch will function normal and the Turbo LED will turn on/off when system in the Turbo/De-turbo mode.

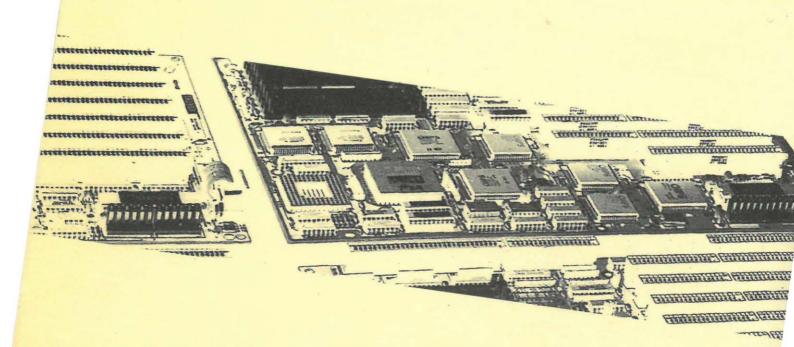

## 3.3 Board Layouts

Figure 4-1. SI54P AIO Mainboard Layout

## 4 Built-in BIOS SETUP Program

## 4.1 SETUP Program

ROM PCI/ISA BIOS (2A5IAE11)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC.

| STANDARD CHOS SETUP                   | SUPERVISOR PASSWORD                            |

|---------------------------------------|------------------------------------------------|

| BIOS FEATURES SETUP                   | USER PASSWORD                                  |

| CHIPSET FEATURES SETUP                | IDE HDD AUTO DETECTION                         |

| POWER MANAGEMENT SETUP                | SAVE & EXIT SETUP                              |

| PCI & ONBOARD I/O SETUP               | EXIT WITHOUT SAVING                            |

| LOAD BIOS DEFAULTS                    |                                                |

| LOAD SETUP DEFAULTS                   |                                                |

| Esc : Quit<br>F10 : Save & Exit Setup | ↑↓ + : Select Item<br>(Shift)F2 : Change Color |

|                                       |                                                |

| Time, Date                            | , Hard Disk Type                               |

Figure 4-1. SETUP Main Menu

It is highly recommended that you list down all the values of the SETUP program before making any changes. Doing so will save a lot of time restoring the system back in the event of a configuration memory loss.

Note:

On-screen instructions at the bottom of each screen explain how to use the program.

- **Standard CMOS SETUP** allows checking or modification of general configuration information.

- BIOS Features SETUP used to set the various system options for the user, including the virus warning, internal/external cache memory functions, quick power on self test, boot operations, gate A20 option, memory parity, security option, typematic rate settings, and BIOS shadowing.

- **Chipset Features SETUP** dedicated for the user who wishes to program the chipset registers of the DRAM, cache, cacheable BIOS, non-cacheable block 1 size/start address etc.

- Power Management Setup allows the programming of the timeout functions of six devices. It the device is not active, Power Management Function will slow down the CPU speed to 8 MHz and both IDE and monitor will be put into standby mode.

- **PCI & Onboard I/O SETUP** used to set the various system functions and internal addresses of the PCI devices and onboard PCI IDE controller.

- Load BIOS Dolaults allows for automatic configuration of all the options in the Standard CMOS SETUP/BIOS Features SETUP/Chipset Features SETUP with the BIOS defaults.

- Load SETUP Dolaults loads the SETUP default values which would allow safe booting of the system in the event a BIOS configuration memory loss.

- **SUpervisor Password** required when entering and changing the SETUP option or booting your system. The supervisot can change the current password stored in the CMOS by accessing the option.

- **User Password** required when entering the SETUP program or booting your system. The user can change the current password stored in the CMOS by accessing this option.

- IDEHDD Auto Dotoction allows for automatic detection of the hard disk drive type(s) including the number of cylinders and heads, write precompensation time, read/write head landing zone, and number of sectors per track.

- Save a Exit SETUP saves the changes you have made in the SETUP program, then exits and reboots the system.

- **Edt Without Saving** abandons all previous settings then exits and reboots the system.

To choose an item from the SETUP main menu, move the cursor using the <Left/Right> and <Up/Down>arrow keys and press <Enter>. To modify the setting of an option, simply press the <PgUp> or <+> and the <PgDn> or <-> keys. Press the <F2> key when changing the color setting, <F1> for a context sensitive help function, and the <ESC> key when quitting SETUP.

### 4.2 Standard CMOS SETUP

ROM PCI/ISA BIOS (2A5IAE11) CMOS SETUP Utility AWARD SOFTWARE, INC.

```

Date (mm:dd:yy) : Fri, Dec 24 1994

Time (hh:mm:ss) : 7 : 10 : 25

Primary HDDs

CYLS. HEADS PRECOMP LANDZONE SECTORS MODE

Master : None (

OMb)

0

0

0

θ

Slave : None (

OMP)

A

O

Θ

O

Secondary HDDs

Master : None (

OMb)

0 0

Slave : None (

OMP)

A

Drive A: 1.2M, 5.25 in.

Drive B: 1.44M, 3.5 in

Base Memory:

640K

Extended Memory: 31744K

Other Memory:

Video : EGA/UGA

Halt On : All Errors

Total Memory: 32768K

ESC : Quit

↑ ↓ + : Select Item

PU/PD/+/- : Modify

F1 : Help

(Shift)F2 : Change Color

```

Figure 4-2. Standard CMOS SETUP Screen

Date - allows manual setting of the electronic calendar on the mainboard.

**Time** - sets the system's internal clock which includes hour, minutes, and seconds.

Primary/Socondary Master and Slavo: - specify the physical and electronic properties of the standard hard disk drives installed. Relevant specifications include the type, number of cylinders (CYLS.), heads (HEADS), write precompensation time (PRECOMP), read/write head landing zone (LANDZONE), number of sectors per track (SECTORS), and HDD mode (MODE). Selecting "AUTO" in the hard disk type item avoids the necessity of loading the HDD specifications and the function of the IDE HDD Auto Detection option in the main menu. The system BIOS will automatically detect the hard drive(s) installed on the system upon bootup.

**Drive A:/B:** - specify the capacity and format of the floppy drives installed in your system.

**VIDEO** - specifies the display adapter installed.

**Halt On** - enables the system to halt on several conditions/options. The default value is set at "All Errors".

**Base/Extended/Other Memory** - A small section in the lower right corner of the screen displays important information about your system which includes the base, extended, and other memory sizes. They are updated automatically by the SETUP program according to the status detected by the BIOS self-test. This section of the Standard CMOS SETUP screen is for viewing purpose only and manual modifications are not allowed.

### 4.3 BIOS Features SETUP

ROM PCI/ISA BIOS (ZASIAE11)

BIOS FEATURES SETUP

AWARD SOFTWARE, INC.

| Virus Warning CPU Internal Cache External Cache Quick Power On Self Test Boot Sequence Swap Floppy Drive Boot Up Floppy Seek Boot Up NumLock Status Boot Up System Speed Gate A20 Option Typematic Rate Setting Typematic Rate (Chars/Sec) Typematic Delay (Msec) Security Option | : Enabled<br>: Enabled<br>: Disabled<br>: A,C<br>: Disabled<br>: Enabled<br>: On<br>: High<br>: Fast<br>: Disabled<br>: 6<br>: 250 | D0000-D3FFF Shadow : Disabled D4000-D7FFF Shadow : Disabled D8000-DBFFF Shadow : Disabled |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| desiring operan                                                                                                                                                                                                                                                                   | · Secup                                                                                                                            | ESC: Quit                                                                                 |

Figure 4-3. BIOS Features SETUP Screen

Wris Warning - allows the virus warning feature for the hard disk boot sector to display a warning message and produce a beep sound whenever an attempt is made to write on the hard disk's boot sector. The default value for this option is "Disabled."

**CPU internal Cacho** - enables the internal 16KB code/data cache of the Intel Pentium<sup>TM</sup> CPU when set to "Enabled" (default).

**External Cacho** - enables the on-board secondary cache (either standard non-burst or burst cache) when set to "Enabled" (default).

Quick Pewer On Self Test - allows the power on self test to run at either a fast or a normal speed. The available options are:

- Disabled (default)

- Enabled

| <b>Swap Floppy Drive</b> - "Enabled" will effectively change the A: drive to B: and the B: to A: drive. "Disabled" (default) sets the floppy drives in their default states.                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boot Up Hoppy Sook - checks whether the floppy drives installed on the system are correct or not. This option's operation usually occurs when the magnetic heads of the floppy drives produce a sound during power on self test. The available options are:  Enabled (default)  Disabled |

| Boot Up NumLock Status - sets the Num Lock key to either on or off during system boot-up. The available options are:  On (default)  Off                                                                                                                                                  |

| Boot Up System Spood - sets the speed of the system during power on self test sequence. The available options are:  High (default) Low                                                                                                                                                   |

| Gate A20 Option - boosts the performance of systems with softwares using the 80286 protected mode such as OS/2 or UNIX. This option determines the accessibility of the extended memory. The available options are:  Fast (default)  Normal                                              |

| Typematic Rate Setting - defines the setting of the keyboard's typematic rate. The available options are:                                                                                                                                                                                |

Boot Soquence - selects the drive where the system would search for the op-

erating system to run with. The available options are:

A,C (default)

C,A

Enabled

Disabled (default)

Typematic Rate (Chars/Sec) - specifies the key repeat rate, in seconds, of keyboard characters. The available options are: 2/sec 18.5/sec 6/sec (default) 21.8/sec 26.7/sec 10/sec 13.3/sec 30/sec Typematic Delay (MSec) - selects the delay, in milliseconds, before a key repeats itself. The available options are: 1/4 sec (default) 3/4 sec 1/2 sec 1 sec

**Security Option** - determines whether the password will be asked for in every boot (**System**), or when entering into the SETUP program (**Setup** - default). Refer to the section entitled Password Setting for the password setting procedure.

**Indee BIOS Shadow** - enables the system shadowing and achieve the best performance of the system. The available options are:

- Enabled (default)

- Disabled

**C8000-CBFFF, CC000-CFFFF, D0000-D3FFF, D4000-D7FFF, D8000-DBFFF, DC000-DFFF Shadow** - if you have a shadowing of the BIOS at any of the above segments, you may set the appropriate memory cacheable function to "Enabled". Otherwise, select "Disabled" (default).

## 4.4 Chipset Features SETUP

ROM PCI/ISA BIOS (2ASIAE11) CHIPSET FEATURES SETUP AWARD SOFTWARE, INC.

| Auto Configuration : Enabled Read CAS Pulse Width : 4T DRAM Write CAS Width : 2T L2 Cache Update Mode : WB L1 Cache Update Mode : WB DRAM Relocate (2,4 & 8M): Disabled SRAM Speed Option : Slower SRAM Burst R/W Cycle : 3T Refresh RAS Active Time : 5T DRAM RAS to CAS Delay : 4T DRAM RAS Precharge Time : 5T Gate A20 Emulation : Enabled Fast Reset Emulation : Enabled Slow Refresh (1:4) : Disabled System BIOS Cacheable : Disabled Turbo/Deturbo Switch : Enabled | Latency from ADS# status: 2T Refresh When CPU Hold : Disabled Post Write CAS Active : 1T CPU/PCI Post Write Delay: 1T PCI Clock Frequency : CPUCLK/2 Max. Burstable Range : 0.5Kb CPU/PCI Burst Mem. Write: Disabled CPU/PCI Post Mem. Write: Disabled ISA Bus Clock Frequency : PCICLK/4 Non-Cacheable Block 1 : Disabled Block 1 Start Address : 0500000H Block 1 Size : 64KB  ESC : Quit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 4-4. Chipset Features SETUP Screen

Auto Configuration - loads the default values, if "Enabled" (default), for the following DRAM and cache options. Otherwise, "Disabled" allows you to program each option as required.

**Read CAS Pulse Width** - determines the pulse width length of the CAS during DRAM read cycles. The available options are:

2T 4T (default)

**DRAM Write CAS Width** - determines the pulse width length of the CAS during DRAM write cycles. The available options are:

- 2T (default)

- **3**T

L2 Cache Update Mode - determines the mode wherein the external (L2) cache will operate. Choosing "WB" will set the cache in its fastest mode since writes as well as reads are cached. The available options are:

- WT

- WB (default)

| L1 Cache Update Mede - sets the state of the (L1) internal cache of the Pentium <sup>TM</sup> CPU and determines the mode wherein data will be updated. The available options are:  WB (default) WT                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM Relecate (2,4 & 8M) - remaps the 256K DRAM region to the top of the DRAM size. This option is only applicable when the D & E segments are not shadowed, and when total on-board memory is 2MB, 4MB, or 8MB. The available options are:  Enabled  Disabled (default) |

| SRAM Speed Option - specifies the speed of the standard SRAM cache during normal read/write operations. The available option are:  Slower (default) Faster Fastest                                                                                                       |

| SRAM Burst R/W Cyclo - defines the speed of the cache SRAM burst read/write cycles. The available options are:  3T (default) 2T                                                                                                                                          |

| Refresh RAS Active Time - defines the amount of active time needed for the row address strobe (RAS), during DRAM refresh time, to be refreshed. The available options are:  5T (default) 6T                                                                              |

| DRAM RAS to CAS Dolay - defines the amount of time required after which a CAS# will be succeeded by RAS# signal during normal DRAM operations.  The available options are:  3T 4T (default)                                                                              |

| <b>DRAM RAS Precharge Time</b> - sets the amount of time for DRAM RAS recovery. The available options are:                                                                                                                                                               |

4T 5T (default)

**Gato A20 Emulation** - allows access and increases the speed of the Gate A20 feature incorporated in the on-board chipset. When enabled, the SiS85C501 responds the cycle by asserting DEVSEL# in slowest timing. Otherwise, the cycle is subtractively decoded by SiS85C503, and then is passed to 8042 on the ISA Bus. The available options are:

- Enabled (default)

- Disabled

**Fast Reset Emulation** - enhances the speed of the software reset by delaying the assertion of INIT or CPURST by  $2\mu s$  or  $6\mu s$ , and holding them for 25 CPUCLK. The available options are:

- Enabled (default)

- Disabled

**Slow Rolrosh (14)** - allows you to turn the DRAM's slow refresh feature to on or off. The available options are:

- Enabled

- Disabled (default)

**System BIOS Cachoable** - allows caching of the different segments where there is system BIOS shadowing. The available options are:

- Enabled

- Disabled (default)

**Turbo/Deturbo Switch** - enables the hardware turbo switch on-board and/or the keyboard control when changing the system speed.

- Enabled (default)

- Disabled

Latency from ADS# status - determines the CPU to PCI Post write speed. When this is set to "3T", the Post write rate is 5T for each double word. When this option is set to "2T" (default), the rate is 4T per double word. For a Qword PCI memory write, the post write rate is 7T (2T) or 8T (3T).

- 2T (default)

- **3**T

| Refresh When CPU Hold - enables the refresh HOLD state. The available options are:  Enabled Disabled (default)                                                                                                                | esh cycle when the CPU is in                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Post Write CAS Active - defines the pulse veter writes to DRAM. The available options  1T (default)  2T                                                                                                                       |                                                                                                        |

| CPU/PCI Post Write Dolay - pertains to the data into the PCI Bus. The available option 1T (default) 2T                                                                                                                        |                                                                                                        |

| PCI Clock Frequency - selects the timing of options are:  CPUCLK/1.5  CPUCLK/2 (default)                                                                                                                                      | f the PCI Bus clock. The available                                                                     |

| Max Burstable Range - defines the maxim FRAME# asserting. The available options a  0.5Kb (default)  1Kb                                                                                                                       |                                                                                                        |

| cpu/pci Burst Mom. Write - If enabled, bacory write cycles to PCI are translated to PCI disabled, each single write to PCI will have quence. The available options are:  Enabled                                              | CI burst memory write cycles. If                                                                       |

| cpu/pci post Memory Write ~ enabling alle posted to PCI. Disabling this option not or limits the completion of CPU write (CPU v PCI transaction completes). In general, this of the PCI slots when "Enabled" (default Enabled | nly disables the buffering but also write does not complete until the soption enhances the performance |

|                                                                                                                                                                                                                               |                                                                                                        |

| Hon-cacheable Block 1 - allow a certain block of the local DRAM to be classified as non-cacheable. The available options are:  Enabled Disabled (default)  Block 1 Start Address - accommodates ISA devices that have their memory mapped into the 1MB to 15.5MB range (i.e., an ISA LAN card or an ISA frame buffer), and defines a hole in main memory that transfers the cycles in this address space to the PCI Bus instead of main memory. This area is not cacheable and its default is "0500000H."  Block 1 Size - defines the size or Block 1. If the frame buffer range is programmed below 16MB and within main memory space, this option must include the frame buffer range. The amount of main memory |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ory mapped into the 1MB to 15.5MB range (i.e., an ISA LAN card or ar ISA frame buffer), and defines a hole in main memory that transfers the cycles in this address space to the PCI Bus instead of main memory. This area is not cacheable and its default is "0500000H."  Block 1 Size - defines the size or Block 1. If the frame buffer range is programmed below 16MB and within main memory space, this option must include the frame buffer range. The amount of main memory                                                                                                                                                                                                                                |

| programmed below 16MB and within main memory space, this option must include the frame buffer range. The amount of main memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| specified in the following options is remapped to the top of main memory. The options are:  64KB (default)  128KB 256KB 4MB 512KB 8MB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 4.5 Power Management SETUP

ROM PCI/ISA BIOS (2A5IAE11) POWER MANAGEMENT SETUP AWARD SOFTWARE, INC.

| POMER PANAGEMENT : Disabled                                          | VGA Activity : Disabled           |  |

|----------------------------------------------------------------------|-----------------------------------|--|

| PM Control by APM : Yes                                              | IRQ3 (COM2) : Enabled             |  |

|                                                                      | 1RO4 (CDM1) : Enabled             |  |

| Video Off Option : Suspend->Off<br>Video Off Method : V/H SYNC+Blank | IROS (LPT2) : Enabled             |  |

| Suspend Switch : Enabled                                             | IRQ6 (Floppy Disk) : Enabled      |  |

| Done Speed (div by) : 2                                              | IRU7 (LPT1) : Enabled             |  |

| Stdby Speed (div by): 3                                              | IRQB (RTC Alarm) : Disabled       |  |

|                                                                      | IRQ9 (IRQ2 Redir) : Enabled       |  |

| ** PM Timers ***                                                     | IRQ10 (Reserved) : Enabled        |  |

| HDD Power Down : Disabled                                            | IRQ11 (Reserved) : Enabled        |  |

| Doze Mode : Disabled                                                 | IRQ12 (PS/2 Mouse) : Enabled      |  |

| Standby Mode : Disabled                                              | IRQ13 (Coprocessor) : Enabled     |  |

| Suspend Mode : Disabled                                              | IRQ14 (Hard Disk) : Enabled       |  |

|                                                                      | IRQ15 (Reserved) : Enabled        |  |

| ** PM Events **                                                      |                                   |  |

| COM Ports Activity : Enabled                                         | ESC : Quit 11 +: Select Item      |  |

| LPT Ports Activity : Enabled                                         | F1 : Help PU/PD/+/- : Modify      |  |

| HDD Ports Activity : Enabled                                         | F5 : Old Values (Shift)F2 : Color |  |

| PCI/ISA Master Act : Enabled                                         | F6 : Load BIOS Defaults           |  |

| IRQ1-15 Activity : Enabled                                           | F7 : Load Setup Defaults          |  |

Figure 4-5. Power Management Screen

| rigure 4-3. Fower management                                                    | 3016611                                |

|---------------------------------------------------------------------------------|----------------------------------------|

| Power Management - The available Disabled (default) Max Saving                  | options are:  Min Saving User Define   |

| PM Centrel By APM - sets the power The available options are:  Yes (default)    | management (PM) control by the APM  No |

| Mdee Off Option ~ The available opti<br>Suspend ->Off (default) All Modes ->Off | ions are: Susp. Stby ->Off Always On   |

| Video Off Method ~ The available op  V/H SYNC+Blank (default)                   | tions are:  Blank Screen               |

| <b>Suspend Switch</b> - sets the system of tions are:                           | the suspend switch. The available op-  |

| Enabled (default)                                                               | Disabled                               |

| Rese Creed (dly by) Wes socilate serious                                                                      |                         |

|---------------------------------------------------------------------------------------------------------------|-------------------------|

| Deze Speed (div by) ~ The available options 2 (default)                                                       | are:<br>1/3/4/5/6/7/8   |

| Stdby Speed (div by) - The available option  3 (default)                                                      | s are:<br>1/2/4/5/6/7/8 |

| HDD Power Down - The available options and Disabled (default)  When Suspend                                   | re:<br>1/2/3/4/515 Min  |

| Doze Mede - sets the time interval after sys enters DOZE mode. The available options a Disabled (default)     | •                       |

| Standby Mede - sets the timer interval after<br>tem events enters STANDBY mode. The opt<br>Disabled (default) |                         |

| Suspend Mede - sets the time interval after<br>tem enters SUSPEND mode. The available of<br>Disable (default) |                         |

| _ ` '                                                                                                         |                         |

## 4.6 PCI Configuration SETUP

ROM PCI/ISA BIOS (2A5IAE11)

PCI & ONBOARD I/O SETUP

AWARD SOFTWARE, INC.

| Slot 1 Using INT8 : AUTO Slot 2 Using INT8 : AUTO Slot 3 Using INT8 : AUTO Slot 4 Using INT8 : AUTO  1st Available IRQ : 9 2nd Available IRQ : 10 3rd Available IRQ : 11 4th Available IRQ : NA | Onboard FDC Controller : Enabled Onboard Serial Port 1 : COM1 Onboard Serial Port 2 : COM2 COM3 & COM4 Address : 3E0H, 2E0 Onboard Parallel Port : 370H Parallel Port Mode : Normal  IDE HDD Block Mode : Disabled IDE 32-bit Transfer Mode : Disabled Onboard CMD IDE Mode 3 : Disabled |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCI IDE IRQ Map To : ISA                                                                                                                                                                        | ESC: Quit 11 +: Select Item F1: Help PU/PD/+/-: Modify F5: Old Values (Shift)F2: Color F6: Load BIOS Defaults F7: Load Setup Defaults                                                                                                                                                    |  |

Figure 4-6. PCI Slot Configuration Screen

**PCI Slot 1/2/3/4 Using INT#** - defines the INTx# assigned to every PCI slot. The available options are:

| AUTO (default) | С |

|----------------|---|

| Α              | D |

| R              |   |

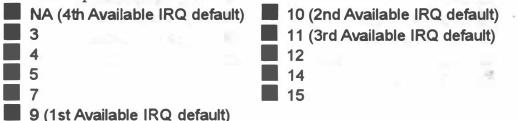

**1st/2nd/3rd/4th Available IRQ** - specify the IRQ for the PCI devices. The end user should assign an available IRQ if the PCI device needs an IRQ service. The available options are:

**PCI IDE IRQ Map To** - defines the CMD PCIO640B IRQ Routing either from the **PCI** Bus or the **ISA** Bus. The default setting of this option is "**ISA**."

| Onbeard FOC Controller - sets the diskette controller modern PCIO640B PCI Bus IDE controller chip to either on or of tions are:  Enabled (default) Disabled                                                                                                              |                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                          | imary and secondary  DM3  DM4                                                                  |

| COM3 & COM4 Address - assigns the addresses of COM3 on-board. The available options are:  3E8H,2E8H (default)  2E8H,2E0H                                                                                                                                                 | 3 and COM4 ports                                                                               |

| Onbeard Parallel Pert - assigns the address of the LPT p board. This option also prevents the system from encount when an add-on card with parallel port is installed in able options are:  278H  Disabled  378H (default                                                | intering any conflict<br>the future. The avail-                                                |

| Parallel Port Mode - specifies the mode under which the signed to operate. In "ECP+EPP" mode, EPP can be seen to operate the content of ECR register of ECP mode 100. "Normal" (default) had lected through the ECR register as mode 000. The available Normal (default) | elected through the owever can be selable options are:  dependent on the ents multiple IRQ re- |

**IDE 32-bit Transfer Modo** ~ refers to the setting of the 32-bit transfer rate of hard disk drives. Normally, I/O transfer cycles are accessed in 16 bits however by enabling this option, system transfer cycles perform faster because the BIOS reads hard disk data twice before it sends request signals to the CPU. The available options are:

- Enabled

- Disabled (default)

**Onbeard CND IDE Mede 3** - permits access into the option ROM at segment E800 of the system BIOS. The option ROM then programs the timing registers of the CMD PCI0640B into a faster speed (minimum of 180ns - to IDE Mode 3 hard drives only), and turns on the Mode 3 feature of the installed hard drive. In the event that the installed hard disk drive does not support Mode 3, the option ROM will still program the timing registers to an acceptable rate compared to the chip's default timings. In general, this option enhances the hard drive's performance. The available options are:

- **Enabled**

- Disabled (default)

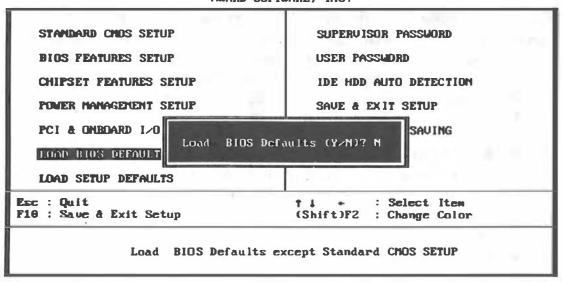

### 4.7 Load BIOS Defaults

ROM PCI/ISA BIOS (ZASIAE11) CMOS SETUP UTILITY AWARD SOFTWARE, INC.

Figure 4-7. Load BIOS Defaults Screen

In the event of a loss in memory on the configuration SETUP, the user can restore the information on the BIOS by loading its default values. Loading the BIOS defaults provides safe booting of the system.

Important: This option may not be able to configure all the values within the SETUP program according to the installed equipments (i.e., floppy drives A: & B:, hard disk drives C: & D:).

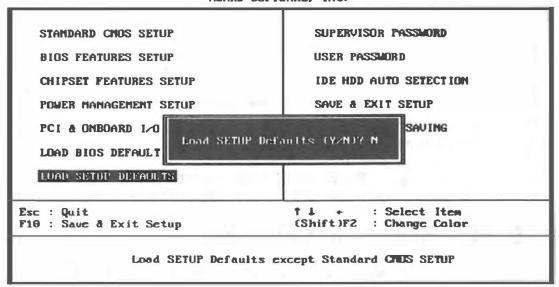

### 4.8 Load SETUP Defaults

ROM PCI/ISA BIOS (2A51AE11)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC.

Figure 4-8. Load SETUP Screen

SETUP defaults are considered default values with which the system will be enabled to perform better. This is due to the enabling of some options within the SETUP program. However, if problems are encountered after loading the SETUP defaults, reboot the system and load the BIOS defaults instead.

## 4.9 Supervisor & User Password

The Pass word Setting utility allows you to set, change, and disable the password stored in the BIOS. To change the password setting, press <Enter> on the Password Setting option of the main menu and type the new password when the following screen is displayed.

The password can be at most 6 characters long. The program will require you to confirm the new password before it exits and enables the utility. To disable the password setting, press the <F1> once the program asks you to enter the new password.

STANDARD CHOS SETUP SUPERVISOR PASSWORD BIOS FEATURES SETUP USER PASSWORD CHIPSET FEATURES SETUP IDE HDD AUTO SETECTION SAVE & EXIT SETUP POWER MANAGEMENT SETUP PCI & UNBUARD I/O S Enter Password: UT SAVING LOAD BIOS DEFAULTS LOAD SETUP DEFAULTS Esc : Quit Select Item F10 : Save & Exit Setup (Shift)F2 : Change Color Change/Set/Disable Password

ROM PCI/ISA BIOS (2A5IAE11)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC.

Figure 4-9. Supervisor & User Password Screen

Note:

Configure the Security Option within the BIOS Features Setup corresponding to the setting in this utility.

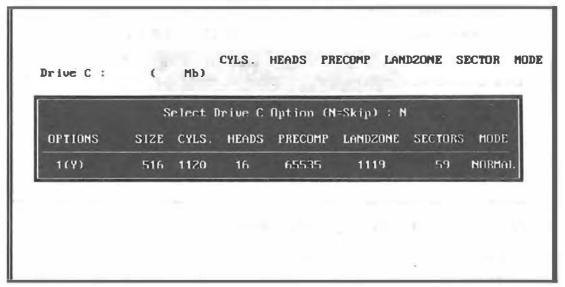

#### 4.10 IDE HDD Auto Detection

The IDE HDD Auto Detection provides auto configuration of the hard drive installed in the system. It supports LBA, Large, and Normal modes. If the system's hard disk drive has a capacity of over 528MB and supports LBA functions, you may enable either the LBA mode or the Large mode. On the other hand, if the hard disk drive's capacity is over 528MB but does support LBA functions, you may enable the Large mode in order to use over 528MB.

Note:

a. The LBA and Large modes will only appear on the screen when the installed hard disk drive is specified to support the LBA mode.

b.In the case when a hard disk drive's cylinder specification exceeds 1024, and does not support the LBA functions, only the Large mode will be displayed on the screen.

c. With a hard disk drive supporting cylinders below 1024, only the Normal mode will appear on the screen. The Normal mode will also be shown on the screen under conditions a & b above.

d. Hard disk drives with less than 528MB total capacity must be set to **Normal** mode when combined with either old BIOS versions or the Award BIOS.

#### Warning:

LBA and Large modes are new specifications which may not be fully supported by all operating systems. An example of which is the current version of UNIX System (R3.2.4) which is still unable to support the LBA function. Therefore, determine the specifications of your hard disk drive and operating system before selecting the drive's mode.

After pressing the <Enter> key on this item of the main menu, the display screen will show the following screen.

ROM PCI/ISA BIOS (2A5IAE11)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC.

Figure 4-10. IDE HDD Auto Detection Screen

Once the program detects the type of hard disk installed, it will display the relative information such as the type, cylinders, heads, write pre-compensation, landing zone, number of sectors per track, size and mode. A message asking you to accept the IDE HDD detected will also be flashed on the screen.

## 4.11 Quitting SETUP

After making all modifications in the SETUP program, go to the option "Save & Exit SETUP" then press the <Enter> key. The program will display the following screen.

ROM PCI/ISA BIOS (2A5IAE11)

CMOS SETUP UTILITY

AWARD SOFTWARE, INC. STANDARD CHOS SETUP SUPERUISOR PASSMORD BIOS FEATURES SETUP USER PASSWORD CHIPSET FEATURES SETUP IDE HDD AUTO DETECTION POWER NANAGEMENT SETUP SAUE & EXIT SETUP PCI & ONBOARD I/O VING SAVE to CMUS and EXIT (Y/N)? N LOAD BIOS DEFAULT LOAD SETUP DEFAULTS Esc : Quit : Select Item F10 : Save & Exit Setup (Shift)F2 : Change Color Save Data to CMOS & Exit SETUP

Figure 4-11. Save & Exit SETUP Screen

Press <Y> to confirm the changes made, and the <N> or the <ESC> keys if further modifications are still necessary before exiting the SETUP program. Once the <Y> key is pressed, the system will automatically exit the program and reboot. However, if you want to cancel all changes made under the SETUP program, go to the option "Exit Without Saving". The system will display the following screen.

#### ROM PCI/ISA BIOS (ZASIAE11) CMOS SETUP UTILITY AWARD SOFTWARE, INC.

| STANDARD CMOS SETUP BIOS FEATURES SETUP CHIPSET FEATURES SETUP   | SUPERVISOR PASSWORD USER PASSWORD IDE HDD AUTO DETECTION |  |  |

|------------------------------------------------------------------|----------------------------------------------------------|--|--|

| POWER MANAGEMENT SETUP SAVE & EXIT SETUP                         |                                                          |  |  |

| PCI & ONBOARD I/O Quit Without Saving (Y/N)? N LOAD BIOS DEFAULT |                                                          |  |  |

| LOAD SETUP DEFAULTS                                              |                                                          |  |  |

| Esc : Quit<br>F10 : Save & Exit Setup                            | † + : Select Item<br>(Shift)FZ : Change Color            |  |  |

| Abandon all Datas & Exit SETUP                                   |                                                          |  |  |

Figure 4-12. Exit Without Saving Screen

Press <Y> and the system will exit the SETUP program then reboot without saving any of the changes made.

**Note:**

You may also use the <F10> key to save the new settings.

## Appendix A

## **Setting the System Speed**

There is two methods in changing the system processing speed of your SI54P AIO. The first method is implemented through the hardware connector designated as J16. The second method is done with the simultaneous pressing of several special keys on the keyboard known as hot-keys. You may change the speed during normal operation while working with your application program.

#### Note:

Hot-Key for changing System Speed Procedure:

- a. Short 2-3 for the jumper setting of JP12.

- b. Set the L1 Cache Update Mode into (WT) Write Through within the BIOS Chipset Features SETUP.

- c. After finishing steps a & b, the S/W hot-key will function normally but the Turbo LED will not turn on/off, no matter system in Turbo/De-turbo mode.

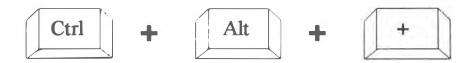

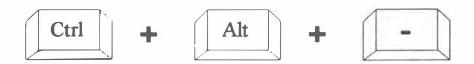

The hot-key combinations for setting the system speed on your SI54P AIO are shown on the following diagrams.

#### High Speed

### Lew Speed

40-012-819120 Version 1.2