## IBM CORPORATION 486SLC2 VESA

Processor 486SLC2

Processor Speed 50(internal)/66(internal)MHz

Chip SetUnidentifiedVideo Chip SetNoneMaximum Onboard Memory16MBMaximum Video MemoryNone

**Cache** 64/128/256KB

**BIOS** Award

**Dimensions** 254mm x 218mm

I/O Options 32-bit VESA local bus slots (3)

NPU Options 80387SX

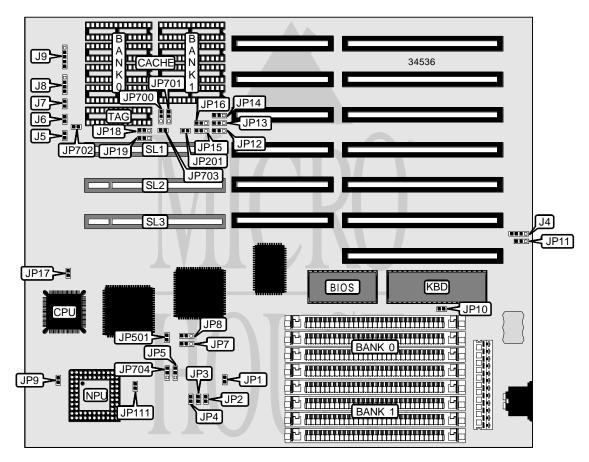

| CONNECTIONS      |          |                             |           |

|------------------|----------|-----------------------------|-----------|

| Purpose          | Location | Purpose                     | Location  |

| External battery | J4       | Speaker                     | J8        |

| Turbo LED        | J5       | Power LED & keylock         | J9        |

| Turbo switch     | J6       | Chassis fan power           | JP9       |

| Reset switch     | J7       | 32-bit VESA local bus slots | SL1 – SL3 |

## IBM CORPORATION 486SLC2 VESA

. . . continued from previous page

|   | USER CONFIGURABLE SETTINGS           |       |                   |  |  |

|---|--------------------------------------|-------|-------------------|--|--|

|   | Function                             | Label | Position          |  |  |

| í | Monitor type select color/EGA/VGA    | JP10  | Closed            |  |  |

|   | Monitor type select monochrome       | JP10  | Open              |  |  |

|   | Battery type select internal         | JP11  | Pins 2 & 3 closed |  |  |

|   | Battery type select external         | JP11  | Pins 1 & 2 closed |  |  |

| í | CPU memory read/write delay enabled  | JP700 | Pins 1 & 2 closed |  |  |

|   | CPU memory read/write delay disabled | JP700 | Pins 2 & 3 closed |  |  |

| SIMM CONFIGURATION |              |              |  |

|--------------------|--------------|--------------|--|

| Size               | Bank 0       | Bank 1       |  |

| 1MB                | (4) 256K x 9 | None         |  |

| 2MB                | (4) 256K x 9 | (4) 256K x 9 |  |

| 4MB                | (4) 1M x 9   | None         |  |

| 8MB                | (4) 1M x 9   | (4) 1M x 9   |  |

| 16MB               | (4) 4M x 9   | None         |  |

| CACHE CONFIGURATION |             |             |             |

|---------------------|-------------|-------------|-------------|

| Size                | Bank 0      | Bank 1      | TAG         |

| 64KB                | (4) 8K x 8  | (4) 8K x 8  | (1) 8K x 8  |

| 128KB               | (4) 32K x 8 | None        | (1) 32K x 8 |

| 256KB               | (4) 32K x 8 | (4) 32K x 8 | (1) 32K x 8 |

| CACHE JUMPER CONFIGURATION                              |       |       |       |       |       |

|---------------------------------------------------------|-------|-------|-------|-------|-------|

| Size                                                    | JP12  | JP13  | JP14  | JP15  | JP16  |

| 64KB                                                    | 2 & 3 | 2 & 3 | 2 & 3 | 2 & 3 | 2 & 3 |

| 128KB                                                   | 1 & 2 | 1 & 2 | 1 & 2 | 1 & 2 | 1 & 2 |

| 256KB                                                   | 2 & 3 | 2 & 3 | 2 & 3 | 2 & 3 | 2 & 3 |

| Note: Pins designated should be in the closed position. |       |       |       |       |       |

| CACHE JUMPER CONFIGURATION (CON'T) |        |        |        |        |

|------------------------------------|--------|--------|--------|--------|

| Size                               | JP11   | JP17   | JP702  | JP703  |

| 64KB                               | Open   | Open   | Open   | Open   |

| 128KB                              | Closed | Open   | Closed | Closed |

| 256KB                              | Open   | Closed | Closed | Closed |

| CPU SPEED SELECTION                                     |                                            |      |      |        |       |       |

|---------------------------------------------------------|--------------------------------------------|------|------|--------|-------|-------|

| Speed                                                   | JP1                                        | JP2  | JP3  | JP4    | JP5   | JP704 |

| 50iMHz                                                  | Closed                                     | Open | Open | Closed | 2 & 3 | 1 & 2 |

| 66iMHz                                                  | 66iMHz Closed Closed Open Open 2 & 3 1 & 2 |      |      |        |       |       |

| Note: Pins designated should be in the closed position. |                                            |      |      |        |       |       |

## IBM CORPORATION 486SLC2 VESA

. . . continued from previous page

| CPU ADS DELAY SELECTION |        |                   |  |  |

|-------------------------|--------|-------------------|--|--|

| Setting                 | JP201  | JP701             |  |  |

| íEnabled                | Closed | Pins 1 & 2 closed |  |  |

| Disabled                | Open   | Pins 2 & 3 closed |  |  |

| VL BUS WAIT STATE SELECTION |                   |  |

|-----------------------------|-------------------|--|

| Setting JP18                |                   |  |

| í O                         | Pins 1 & 2 closed |  |

| 1                           | Pins 2 & 3 closed |  |

| VL BUS SPEED SELECTION |                   |  |

|------------------------|-------------------|--|

| Speed                  | JP19              |  |

| <= 33MHz               | Pins 1 & 2 closed |  |

| >33 MHz                | Pins 2 & 3 closed |  |

| LOCAL BUS CLOCK DELAY SELECTION |                   |                   |  |  |

|---------------------------------|-------------------|-------------------|--|--|

| Setting                         | JP7               | JP8               |  |  |

| í No delay                      | Pins 1 & 2 closed | Pins 1 & 2 closed |  |  |

| One gate delay                  | Pins 2 & 3 closed | Pins 2 & 3 closed |  |  |