## UNIDENTIFIED 450L2 CACHE

**Processor** 80486SX/80487SX/80486DX/ODP486SX/80486DX2 20/25/33/50 (Internal)/50/66 (Internal)MHz **Processor Speed**

OPTI **Chip Set** Max. onboard DRAM 32MB

Cache 64/128/256KB

**BIOS** AMI

**Dimensions** 330mm x 218mm I/O Options 32-bit local bus slots (2)

**NPU Options** None

| CONNECTIONS                                                         |          |                       |          |  |

|---------------------------------------------------------------------|----------|-----------------------|----------|--|

| Purpose                                                             | Location | Purpose               | Location |  |

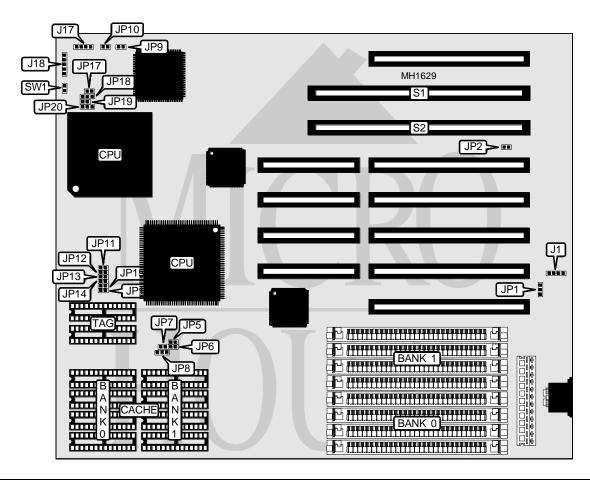

| External battery                                                    | J1       | Turbo LED             | JP10     |  |

| Speaker                                                             | J17      | 32-bit local bus slot | S1       |  |

| Power LED & keylock                                                 | J18      |                       | S2       |  |

| Turbo switch                                                        | JP9      | Reset                 | SW1      |  |

| Note: The exact locations of local bus slots S1 and S2 are unknown. |          |                       |          |  |

Continued on next page . . .

## UNIDENTIFIED 450L2 CACHE

. . . continued from previous page

| USER CONFIGURABLE SETTINGS                            |           |                   |  |

|-------------------------------------------------------|-----------|-------------------|--|

| Function                                              | Jumper    | Position          |  |

| í CMOS memory normal operation                        | JP1       | pins 2 & 3 closed |  |

| CMOS memory clear                                     | JP1       | pins 1 & 2 closed |  |

| í Monitor type select color                           | JP2       | Closed            |  |

| Monitor type select monochrome                        | JP2       | Open              |  |

| í Ready signal select ISA                             | JP3 & JP4 | pins 1 & 2 closed |  |

| Ready signal select Local bus                         | JP3 & JP4 | pins 2 & 3 closed |  |

| í CPU upgrade (486PQFP to 486PGA) enabled JP17 Closed |           |                   |  |

| CPU upgrade (486PQFP to 486PGA) disabled JP17 Open    |           |                   |  |

| Note: The location of jumpers JP3 and JP4 is unknown. |           |                   |  |

|      | DRAM CONFIGURATION |              |

|------|--------------------|--------------|

| Size | Bank 0             | Bank 1       |

| 1MB  | (4) 256K x 9       | NONE         |

| 2MB  | (4) 256K x 9       | (4) 256K x 9 |

| 4MB  | (4) 1M x 9         | NONE         |

| 5MB  | (4) 1M x 9         | (4) 256K x 9 |

| 8MB  | (4) 1M x 9         | (4) 1M x 9   |

| 16MB | (4) 4M x 9         | NONE         |

| 20MB | (4) 1M x 9         | (4) 4M x 9   |

| 32MB | (4) 4M x 9         | (4) 4M x 9   |

|       |             | CACHE CONFIGURATION | N          |            |

|-------|-------------|---------------------|------------|------------|

| Size  | Bank 0      | Bank 1              | TAG (U39)  | TAG (U40)  |

| 64KB  | (4) 8K x 8  | (4) 8K x 8          | (1) 8K x 8 | NONE       |

| 128KB | (4) 32K x 8 | NONE                | (1) 8K x 8 | NONE       |

| 256KB | (4) 32K x 8 | (4) 32K x 8         | (1) 8K x 8 | (1) 8K x 8 |

|                                | CACHE JUMPER CONFIGURATION |        |        |            |        |        |

|--------------------------------|----------------------------|--------|--------|------------|--------|--------|

| Size JP5 JP6 JP7 JP8 JP15 JP16 |                            |        |        |            |        | JP16   |

| 64KB                           | Open                       | Open   | Open   | pins 2 & 3 | Open   | Open   |

| 128KB                          | Closed                     | Open   | Closed | pins 1 & 2 | Open   | Closed |

| 256KB                          | Closed                     | Closed | Closed | pins 2 & 3 | Closed | Closed |

Continued on next page . . .

## UNIDENTIFIED 450L2 CACHE

$\dots$  continued from previous page

| CPU SPEED CONFIGURATION |        |        |        |        |

|-------------------------|--------|--------|--------|--------|

| Speed                   | JP11   | JP12   | JP13   | JP14   |

| 20MHz                   | Closed | Closed | Open   | Open   |

| 25MHz                   | Open   | Closed | Open   | Closed |

| 33MHz                   | Open   | Open   | Closed | Closed |

| 50i MHz                 | Open   | Closed | Open   | Closed |

| 50MHz                   | Open   | Open   | Closed | Open   |

| 66MHz                   | Open   | Open   | Closed | Closed |

| CPU TYPE CONFIGURATION |                   |        |                   |  |

|------------------------|-------------------|--------|-------------------|--|

| Type                   | JP18              | JP19   | JP20              |  |

| 80486SX PQFP           | Open              | Closed | pins 2 & 3 closed |  |

| 80486SX PGA            | Open              | Open   | pins 2 & 3 closed |  |

| 80487SX                | pins 2 & 3 closed | Closed | pins 1 & 2 closed |  |

| 80486DX                | pins 1 & 2 closed | Closed | pins 1 & 2 closed |  |

| ODP486SX               | Open              | Open   | pins 2 & 3 closed |  |

| 80486DX2               | pins 1 & 2 closed | Closed | pins 1 & 2 closed |  |