## CACHE COMPUTERS, INC.

## SX 386-20 (MODEL 308)

80386SX **Processor Processor Speed** 16/20MHz **Chip Set** VIA Max. Onboard DRAM 8MB Cache None

AMI/Award/Phoenix/Quadtel **BIOS**

330mm x 218mm **Dimensions**

I/O Options None **NPU Options** 80387SX

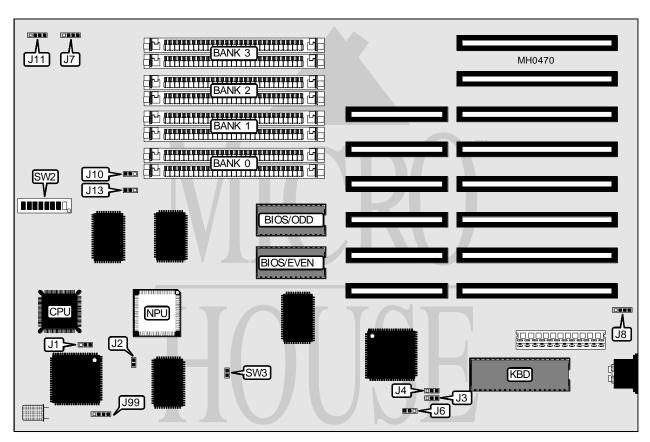

| CONNECTIONS                                                |          |                  |          |  |

|------------------------------------------------------------|----------|------------------|----------|--|

| Purpose                                                    | Location | Purpose          | Location |  |

| Turbo switch                                               | J3       | External battery | 18       |  |

| Turbo LED                                                  | J6       | Speaker          | J11      |  |

| Power LED & keylock J7                                     |          | Reset switch     | SW3      |  |

| Note: The location of the expansion slots is unidentified. |          |                  |          |  |

Continued on next page . . .

## CACHE COMPUTERS, INC.

## SX 386-20 (MODEL 308)

. . . continued from previous page

| USER CONFIGURABLE SETTINGS            |               |                   |  |  |

|---------------------------------------|---------------|-------------------|--|--|

| Function                              | Jumper/Switch | Position          |  |  |

| í CPU speed select 20MHz              | J1            | Open              |  |  |

| CPU speed select 16MHz                | J1            | Closed            |  |  |

| í NPU disabled                        | J2            | Closed            |  |  |

| NPU enabled                           | J2            | Open              |  |  |

| í Monitor type select monochrome      | J4            | Open              |  |  |

| Monitor type select color             | J4            | Closed            |  |  |

| í DMA speed select 8/10MHz            | J99           | pins 2 & 3 closed |  |  |

| DMA speed select 4MHz                 | J99           | Closed            |  |  |

| DMA speed select synchronous with CPU | J99           | pins 1 & 2 closed |  |  |

| í Factory configured - do not alter   | SW2/5         | Off               |  |  |

| í Factory configured - do not alter   | SW2/6         | Off               |  |  |

|       |              | DRAM CONFIGURATION | J            |              |

|-------|--------------|--------------------|--------------|--------------|

| Size  | Bank 0       | Bank 1             | Bank 2       | Bank 3       |

| 512KB | (2) 256K x 9 | NONE               | NONE         | NONE         |

| 1MB   | (2) 256K x 9 | (2) 256K x 9       | NONE         | NONE         |

| 1.5MB | (2) 256K x 9 | (2) 256K x 9       | (2) 256K x 9 | NONE         |

| 2MB   | (2) 256K x 9 | (2) 256K x 9       | (2) 256K x 9 | (2) 256K x 9 |

| 2MB   | (2) 1M x 9   | NONE               | NONE         | NONE         |

| 3MB   | (2) 256K x 9 | (2) 256K x 9       | (2) 1M x 9   | NONE         |

| 4MB   | (2) 1M x 9   | (2) 1M x 9         | NONE         | NONE         |

| 5MB   | (2) 256K x 9 | (2) 256K x 9       | (2) 1M x 9   | (2) 1M x 9   |

| 6MB   | (2) 1M x 9   | (2) 1M x 9         | (2) 1M x 9   | NONE         |

| 8MB   | (2) 1M x 9   | (2) 1M x 9         | (2) 1M x 9   | (2) 1M x 9   |

| DRAM JUMPER/SWITCH CONFIGURATION                        |       |       |       |       |       |       |

|---------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| Size                                                    | J10   | J13   | SW2/1 | SW2/2 | SW2/3 | SW2/4 |

| 512KB                                                   | 2 & 3 | 2 & 3 | Off   | Off   | Off   | Off   |

| 1MB                                                     | 2 & 3 | 2 & 3 | On    | Off   | Off   | Off   |

| 1.5MB                                                   | 2 & 3 | 2 & 3 | Off   | On    | Off   | Off   |

| 2MB                                                     | 2 & 3 | 2 & 3 | On    | On    | Off   | Off   |

| 2MB                                                     | 1 & 2 | 1 & 2 | Off   | Off   | On    | On    |

| 3MB                                                     | 2 & 3 | 1 & 2 | Off   | On    | On    | Off   |

| 4MB                                                     | 1 & 2 | 1 & 2 | On    | Off   | On    | On    |

| 5MB                                                     | 2 & 3 | 1 & 2 | On    | On    | On    | Off   |

| 6MB                                                     | 1 & 2 | 1 & 2 | Off   | On    | On    | On    |

| 8MB                                                     | 1 & 2 | 1 & 2 | On    | On    | On    | On    |

| Note: Pins designated should be in the closed position. |       |       |       |       |       |       |

| DRAM WAIT STATE CONFIGURATION |                             |     |       |  |  |

|-------------------------------|-----------------------------|-----|-------|--|--|

| Read States                   | Read States Write States SW |     | SW2/8 |  |  |

| NONE                          | NONE                        | Off | On    |  |  |

| 1                             | 1                           | Off | Off   |  |  |

| 1                             | 2                           | On  | Off   |  |  |

| 2                             | 2                           | On  | On    |  |  |