Description:

The PB is a single-chip host-to-PCI Bridge. A rich set of CPU-to-PCI and PCI-to-CPU bus transaction translations optimize bus bandwidth and improve system performance. All ISA and EISA regions are supported. Three programmable memory gaps can be created-a PCI Frame Buffer Region with specialized frame buffer attributes and two general-purpose memory gaps (called the Memory Gap Region and the High Memory Gap Region).

The PB takes advantage of the Pentium Pro processor ratio clocking scheme to assure modularity now and upgradability in the future. The PB has a synchronous interface to the Pentium Pro processor bus and supports a derived clock for the synchronous PCI interface. The PB derives either a 30 or 33 MHz PCI clock output from the Pentium Pro processor bus clock. The PB PCI Signals are 5-volt tolerant and can be used with either 5-volt or 3.3-volt PCI devices.

Features:

- Supports the Pentium® Pro Processor at 60 MHz and 66 MHz Bus Speeds

- PCI Specification 2.0 Compliant

- 64-Bit Data Bus and 36-Bit Address Bus

- Parity Protection on Control Signals

- Up to Eight Deep In-Order Queue

- Four Deep Outbound Request Queue

- Dual-Processor Support

- Four Cache Line Size Read and Write Buffers

- GTL+ Host Bus Interface

- Synchronous PCI Interface

- 32-bit Address/Data PCI Bus (64-bit Dual Cycle Address Support)

- Parity Protection on All PCI Bus Signals

- Four Deep Inbound Request Queue

- Data Collection/Write Assembly of Line Bursts

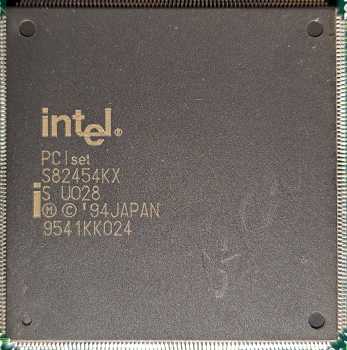

- Single Chip: Combined Controller and Data Path in a 304-Pin QFP or 352 BGA

- Support for 3.3V and 5V PCI Devices

- On-Chip Digital PLL (DPLL)

- Component and In-System Connectivity Test Support (JTAG)

Disclaimer

The info found in this page might not be entirely correct. Check out this guide to learn how you can improve it.

Image 1 of 1 (limsup)

Image 1 of 1 (limsup)