# VT82C570M

**APOLLO MASTER**

Green Pentium/P54C PCI/ISA System with Plug and Play and Master Mode PCI-IDE

DATE : June, 1995

**VIA TECHNOLOGIES, INC.**

The material in this document supersedes all previous documentation issued for any of the products included herein. Please contact VIA Technologies for the latest documentation.

# **Copyright Notice:**

Copyright © 1995, Via Technologies Incorporated. Printed in Taiwan. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of Via Technologies Incorporated.

The VT82C570M, VT82C575M, VT82C576M, VT82C577M and VT82C416 may only be used to identify products of VIA Technologies.

PS/2<sup>™</sup> is a registered trademark of International Business Machines Corp.

Pentium<sup>™</sup> and P54C<sup>™</sup> are registered trademarks of Intel Corp.

M1<sup>™</sup> is registered trademarks of Cyrix Corp.

K86<sup>™</sup> (K5) is a registered trademark of American Micro Devices Corp.

Windows 95<sup>™</sup> and Plug and Play<sup>™</sup> are registered trademarks of Microsoft Corp.

PCI<sup>™</sup> is a registered trademark of the PCI Special Interest Group.

All trademarks are the properties of their respective owners.

# **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

# **Offices:**

5020 Brandin Court Fremont, CA 94538 USA Tel: (510) 683-3300 Fax: (510) 683-3301 8th Floor, No. 533 Chung-Cheng Rd., Hsin-Tien Taipei, Taiwan ROC

Tel: (886-2) 218-5452 Fax: (886-2) 218-5453

# **REVISION HISTORY**

| Document<br>Release | Revision        | Date    |

|---------------------|-----------------|---------|

|                     | Initial Release | 6/22/95 |

# **Table of Contents**

| FEATURES1                                      |

|------------------------------------------------|

| OVERVIEW4                                      |

| FUNCTIONAL DESCRIPTION6                        |

| 1. Clock Logic                                 |

| 2. CPU Interface                               |

| 3. Advanced Cache Controller7                  |

| 3.1. Burst Synchronous and Asynchronous SRAMs7 |

| 3.2. Multiple Tag Options7                     |

| 3.3. Cache Timing7                             |

| 3.4. DRAM Post Write Buffers8                  |

| 3.5. Concurrent DRAM Writeback9                |

| 3.6. Cacheable Region9                         |

| 4. Enhanced DRAM Controller9                   |

| 4.1. Standard Page Mode DRAM9                  |

| 4.2. EDO and Burst EDO DRAM10                  |

| 4.3. Other DRAM Parameters10                   |

| 5. Shadow RAM and ROM Decoding11               |

| 6. Intelligent PCI Bus Controller12            |

| 6.1. CPU to PCI Operation13                    |

| 6.2. PCI to Memory Operation14                 |

| 6.2.1. Snoop Ahead 14                          |

| 6.2.2. Concurrent CPU and Master Operations 14 |

| 6.3. PCI Arbitration and Interrupt Steering15  |

| 6.4. PCI Configuration15                       |

| 7. Master Mode Enhanced IDE Controller16         |

|--------------------------------------------------|

| 7.1. IDE Drive Interface Configuration16         |

| 7.2. Prefetch and Post Write Buffers17           |

| 7.3. Operation Mode Selection17                  |

| 7.4. Scatter and Gather and Bus Master Operation |

| 8. Plug and Play Controller18                    |

| 9. ISA Bus Controller19                          |

| 10. Power Management Unit20                      |

| 10.1. Idle Timers20                              |

| 10.2. Handling of Secondary Events21             |

| 10.3. General Purpose and Peripheral Timers      |

| 10.4. System Management Interrupt21              |

| 10.5. Conserve Mode22                            |

| 11. Multi-function X-Bus Peripherals22           |

| 11.1. Scan Logic22                               |

| 11.2. The XD to SD buffer:23                     |

| 11.3. Multi-clock generator:23                   |

| 11.4. Keyboard controller24                      |

| 11.5. Real time clock24                          |

| 11.6. General Purpose Chipselect24               |

| 11.7. Programmable Output Port24                 |

| 12.Configuration Registers24                     |

| VT82C575M Pin Description25                      |

| VT82C575M Pin Out in Numerical Order             |

| VT82C575M Pin Diagram                            |

| VT82C576M Pin Description                        |

| VT82C576M Pin Out in Numerical Order             |

| VT82C576M Pin Diagram35                    | ;  |

|--------------------------------------------|----|

| VT82C577M Pin Description36                | 5  |

| VT82C577M Pin Out in Numerical Order37     | ,  |

| VT82C577M Pin Diagram38                    | \$ |

| VT82C416 Pin Description39                 | )  |

| VT82C416 Pin Out in Numerical Order41      | L  |

| VT82C416 Pin Diagram42                     | 2  |

| Electrical Characteristics43               | 5  |

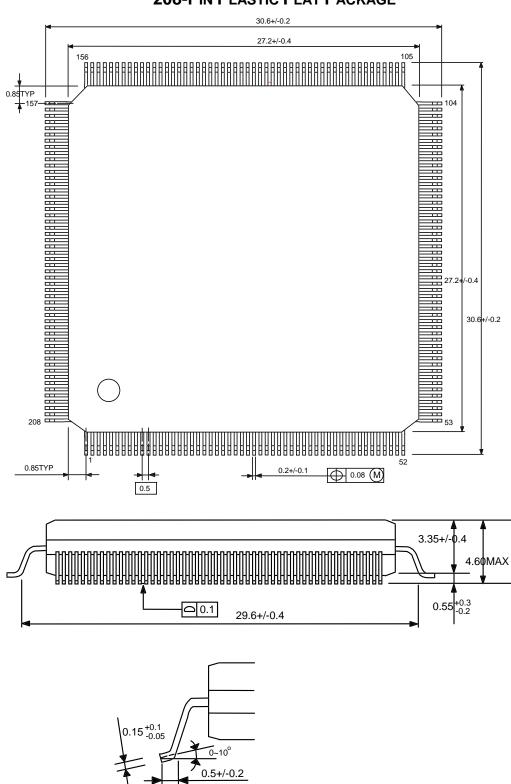

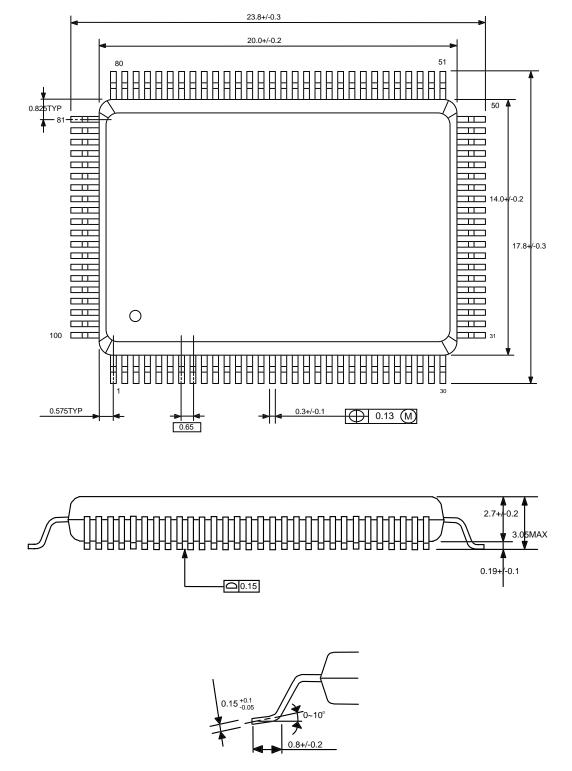

| 208-Pin Plastic Flat Package44             | ļ  |

| 100-Pin Plastic Rectangular Flat Package45 | 5  |

# VIA VT82C570M APOLLO MASTER PENTIUM/P54C PCI/ISA GREEN PC SYSTEMS WITH PLUG AND PLAY AND MASTER MODE PCI-IDE CONTROLLER

# **FEATURES**

- \* PCI/ISA Green PC Ready

- \* High Integration

- VT82C575M system controller

- VT82C576M PCI bus controller

- Two instances of the **VT82C577M** data buffers

- Glueless interface to the VT82C416 integrated clock generator, real time clock with extended CMOS, plug and play control and keyboard controller with PS/2<sup>TM</sup> mouse support

- Ten TTLs for a complete main board implementation

# \* Flexible CPU Interface

- − 64-bit P54C<sup>TM</sup>, Pentium<sup>TM</sup>, K5<sup>TM</sup> and M1<sup>TM</sup> CPU interface

- 3.3v or 5v CPU and cache interface

- CPU external bus speed up to 66Mhz (internal 150Mhz and above)

- Supports CPU internal write-back cache

- Concurrent CPU/cache and PCI/DRAM operation

- System management interrupt, memory remap and STPCLK mechanism

- Cyrix M1 linear burst support

- CPU NA#/Address pipeline capability

# \* Advanced Cache Controller

- Direct map write back or write through secondary cache

- Burst Synchronous (Pipelined or non-pipelined), asynchronous SRAM and Cache Module support

- Eight-pin CWE# and GWE# control options

- Flexible cache size: 0K/128K/256K/512K/1M/2MB

- 32 byte line size to match the primary cache

- Integrated 10-bit tag comparator

- Interleaved SRAM access

- 3-1-1-1 read/write timing for Burst Synchronous SRAM access at 66Mhz

- 3-2-2-2 (read) and 4-2-2-2 (write) timing for interleaved asynchronous SRAM access at 66Mhz

- Data streaming for simultaneous primary and secondary cache line fill

- System and video BIOS cacheable and write-protect

- Programmable cacheable region and cache timing

- Optional combined tag and alter bit SRAM for write-back scheme

# \* Fast DRAM Controller

- Concurrent DRAM Writeback

- Four levels of CPU/cache to DRAM write buffer

- Standard Page Mode/EDO/Burst EDO-DRAM support in a flexible/mixed combination

- EDO-DRAM auto-detect

- Mixed 256K/512K/1M/2M/4M/8M/16MxN DRAMs

- 8 banks up to 512MB DRAMs

- Flexible row and column addresses

- 64 bit or 32 bit data width

- Burst read and write operation

- Programmable DRAM timing

- BIOS shadow at 16KB increment

- System management memory remapping

- Decoupled and burst DRAM refresh with staggered RAS timing

- CAS-before-RAS refresh timing

#### \* Intelligent PCI Bus Controller

- 32 bit PCI interface

- PCI Master snoop ahead and snoop filtering

- Concurrent PCI master/CPU/IDE operations

- Synchronous Bus to CPU clock with divide-by-two from the CPU clock

- Multiple accelerated schemes for high bus throughput

- Automatic detection of data streaming burst cycles from CPU to the PCI bus

- Four level of CPU to PCI posted write buffers

- Byte merging in the write buffers to reduce the number of PCI cycles and to create further PCI bursting possibilities

- PCI to system memory data streaming up to 110Mbyte/sec

- Four level of post write buffers from PCI masters to DRAM

- Four level of prefetch buffers from DRAM for access by PCI masters

- Zero wait state PCI master and slave burst transfer rate

- Complete steerable PCI interrupts

- IDE and ISA bus through peer PCI bus to avoid slower traffic blocking the regular PCI bus

- PCI-2.1 compliant

# \* Enhanced Master Mode PCI IDE Controller

- Dual channel master mode PCI supports four Enhanced IDE devices

- Mode 4 and Mode 5 transfer rate up to 22MB/sec

- Sixteen doubleword of prefetch and write buffers

- Interlaced commands between two channels

- Separate IDE data bus and control signals from the PCI and ISA bus to reduce loading and to enhance performance

- Bus master programming interface for ATA controllers SFF-8038 rev.1.0 compliant

- Full scatter and gather capability

- Support ATAPI compliant devices

- Support PCI native and ATA compatibility modes

- Complete software driver support

#### \* Plug and Play Controller

- Dual interrupt and DMA signal steering with plug and play control

- Two programmable chip selects

- Microsoft Windows 95<sup>TM</sup> and plug and play BIOS compliant

# \* Sophisticated Power Management Unit

- Normal, doze, sleep, suspend and conserve modes

- System event monitoring with two event classes

- One idle timer, one peripheral timer and one general purpose timer

- More than ten general purpose Input/Output ports

- Six external event input ports with programmable SMI condition

- Complete leakage control when external component is in power off state

- Primary and secondary interrupt differentiation for individual channels

- Clock stretching, clock throttling and clock stop control

- Multiple internal and external SMI sources for flexible power management models

- APM 1.1 compliant

### \* Synchronous ISA Bus Controller

- Synchronous ISA bus clock

- Programmable wait state, command delay and IO recovery time

- Bus conversion and data alignment

- Hardware and software de-turbo control

- Fast reset and Gate A20 operation

- Integrated 82C206 peripheral controller

- Edge trigger or level sensitive interrupt

- Flash EPROM and combined BIOS support

- \* Built-in nand-tree pin scan test capability

- \* 0.6um mixed voltage, high speed and low power CMOS process

- \* 208 pin PQFP for VT82C575M

- \* 208 pin PQFP for VT82C576M

- \* 100 pin PQFP for VT82C577M

- \* 100 pin PQFP for VT82C416

# **OVERVIEW**

The VT82C570M *Apollo Master* is a high performance, cost-effective and energy efficient chip set for the implementation of PCI/ISA desktop and notebook personal computer systems based on the 64-bit P54C/Pentium/K5/M1 super-scalar processors. Either 3.3v or 5v CPU and cache interface is supported up to 66Mhz CPU external bus speed (with CPU internal speed up to 150Mhz and above). In either case, DRAM, PCI and ISA bus runs at 5v voltage level.

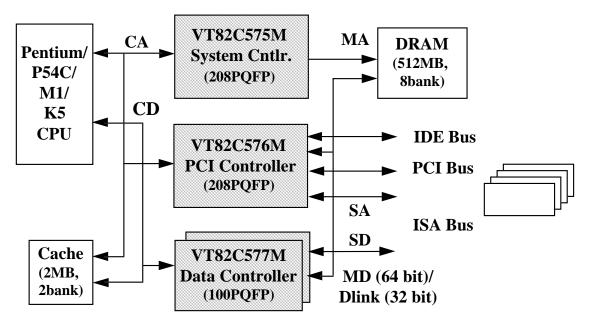

The VT82C570M chip set consists of the VT82C575M system controller, the VT82C576M PCI bus controller with integrated master mode Enhanced-IDE controller, and two instances of the VT82C577M data buffers. The CPU bus is minimally loaded with only the CPU, secondary cache and the chip set. The VT82C577M data buffers isolate the CPU bus from the DRAM, PCI and ISA bus so that CPU and cache operation may run reliably at the high frequencies demanded by today's processors. The chip set also interfaces directly with the VT82C416 integrated clock generator, real time clock with extended CMOS (128 byte) and keyboard controller with PS2 mouse support. A complete main board can be implemented with only ten TTLs. Please refer to Figure 1 for the system block diagram.

The VT82C570M supports eight banks of DRAMs up to 512MB. The DRAM controller supports Standard Page Mode DRAM, EDO-DRAM and Burst EDO-DRAM in a flexible mixed/match manner. The eight banks of DRAM are grouped into four pairs with an arbitrary mixture of 256K/512K/1M/2M/4M/8M/16MxN DRAMs. Zero, one or both banks may be populated in each pair with either 32bit or 64bit data width.

The secondary (L2) cache is based on Burst Synchronous (Pipelined or non-pipelined) SRAM, asynchronous SRAM or cache module from 128KB to 2MB. For burst synchronous SRAMs, 3-1-1-1 timing can be achieved for both read and write transactions at 66Mhz. For standard SRAMs, 3-2-2-2 and 4-2-2-2 timing can be achieved for interleaved read and write transactions at 66Mhz. Four levels of CPU/cache to DRAM write buffers with concurrent write-back capability are included in the VT82C577M data buffer chips to speed up the cache read and write miss cycles. For primary cache fill cycles that result in secondary cache misses, the primary and secondary caches are filled up concurrently to further enhance the performance.

Figure 1. VT82C570M System Block Diagram

The VT82C570M supports the shadowing of the system, video and other BIOS to speed up the access. The video and system BIOS can also be write-protected and made cacheable. The unused portion of the DRAM can be relocated to increase the size of the overall system memory. Access cycles to either E or C segment can be programmed to be an on-board EPROM cycle to allow the combination of system and video BIOS for an all-in-one system board implementation. The VT82C570M can also be programmed to recognize write cycles as EPROM cycles to support field upgradability of flash EPROM BIOS.

The VT82C570M supports 32-bit PCI bus with 64-bit to 32-bit data conversion. Four levels of post write buffers are included to allow for concurrent CPU and PCI operation. Consecutive CPU addresses are converted into burst PCI cycles with byte merging capability for optimal CPU to PCI throughput. A 32-bit fast data link is established between the two VT82C577M data units and the VT82C576M PCI bus controller so that the address, data and command information for CPU to PCI bus transactions is contained in the same chip. This arrangement, unique to the VT82C570M chip set is crucial in achieving zero wait state buffer movement and implementing sophisticated and upgradable buffer management schemes such as the byte merging. For PCI master operation, four levels of post write buffers and four levels of prefetch buffers are included for concurrent PCI bus and DRAM/cache accesses. Snoop Ahead and Snoop Filtering mechanisms are implemented to allow PCI bus master transfer rates greater than 110MB/s for typical applications. Furthermore, the ISA and IDE bus are steered through a peer PCI bus so that the slower traffic does not block the normal traffic of the regular PCI bus. The VT82C570M is PCI 2.1 compliant.

The integrated master mode IDE controller supports a dual channel/four device enhanced IDE bus with sixteen levels of double-word prefetch and write buffers. The data bus, control signals, write buffers and prefetch buffers are separated from those of the PCI bus so that performance and electrical loading are optimized. The command and recovery time of each IDE device can be individually programmed in units of PCI bus clock to achieve optimal speed of the device up to >22MB/s. Other features of the IDE controller include interlaced dual channel commands, full scatter and gather capability, bus master programming interface for ATA controllers SFF-8038 compliant and complete software driver support.

The VT82C570M provides two plug and play ports for converting non plug and play devices into plug and play devices on the main board. The configuration mechanism is compliant with the plug and play BIOS and the Microsoft Windows  $95^{TM}$  operating system.

The integrated power management unit offers the following modes: normal, doze, sleep, suspend and conserve. To determine the power management mode, the power management unit monitors IO events, interrupt, DMA and PCI master request signals to detect the status of system activity. Each event can be turned off or assigned to one of two event classes tracked by an idle timers, a peripheral timer and a general purpose timer. The system management interrupt (SMI) may be triggered by multiple sources including time-out of individual timers, occurrence of system activities, external input and software programming for flexible applications. Clock speed switching (or throttling), IO and power control are functions performed by the SMI routine. The power management unit is APM 1.1 compliant.

The VT82C577M data buffers separate the CPU/cache and PCI/DRAM bus so that the two busses may run concurrently. At the CPU side, the CPUs access cache without interfering with the PCI/DRAM bus unless a cache miss or non-cacheable cycle is encountered, in which case the write buffers with concurrent write back capability minimize the interface overhead. At the PCI/DRAM side, the PCI master devices access DRAM without interfering with the CPU/cache data bus unless a snoop hit occurs.

The VT82C570M is ideal for high performance, high quality, high energy efficient and high integration desktop and notebook PCI/ISA computer systems.

# **FUNCTIONAL DESCRIPTION**

# 1. Clock Logic

The VT82C570M supports 3.3v and 5v Pentium and compatible processors up to 66Mhz CPU external bus speed. The CPU interface, cache and DRAM controller runs at the same clock frequency as the CPU bus clock which may be fraction of the CPU internal frequency. Since the PCI bus runs at half the frequency of the CPU bus, the VT82C570M requires two clock inputs: one of the CPU frequency (CCLK) and the other of half the speed (PCLK). The companion VT82C416 supports both clocks, the frequency of which is controlled by bit 3-0 of internal register RX56h (CCLK).

| 0000 - 16Mhz | 1000 - 8Mhz  | 0001 - 40Mhz  | 1001 - 20Mhz |

|--------------|--------------|---------------|--------------|

| 0010 - 50Mhz | 1010 - 25Mhz | 0011 - 80Mhz  | 1011 - 40Mhz |

| 0100 - 66Mhz | 1100 - 33Mhz | 0101 - 100Mhz | 1101 - 50Mhz |

| 0110 - 8Mhz  | 1110 - 4Mhz  | 0111 - 60Mhz  | 1111 - 30Mhz |

At power on reset, the target CPU frequency is read in from the jumper setting of pins RAS#3-0. The frequency can be changed during CPU operation (with or without asserting STPCLK#) for power management purposes. The clock generator in the VT82C416 guarantees smooth frequency changes if the original and target frequencies fall in the same bank (same bit 3 of RX56h). The STPCLK# signal can be used for clock throttling to reduce the CPU power consumption.

The ISA bus clock can either be derived from the CCLK or be asynchronous according to the setting of bit 3-0 of RX11h.

| 0 CCLK/8       | 1000 - CCLK/3  | 1001 - CCLK/2               |

|----------------|----------------|-----------------------------|

| 1010 - CCLK/4  | 1011 - CCLK/6  | 1100 - CCLK/5               |

| 1101 - CCLK/10 | 1110 - CCLK/12 | 1111 - OSC/2 (asynchronous) |

# 2. CPU Interface

The VT82C570M responds to CPU generated bus cycles and activates the cache, DRAM, PCI and ISA state machines according to the command type and address range. The CACHE# input from the CPU is monitored to determine burst cycles and KEN# is returned to inform the CPU of the cacheability of the data. For memory cycles with inactive CACHE# signaling, the line is normally not cached into the secondary cache unless bit 2 of RX40h is set. The coherency of the CPU primary cache with the rest of the system is maintained by the KEN#, EADS# and HITM# pins. KEN# is normally active for a memory read cycle. If the CPU address lies outside the cacheable region, KEN# becomes inactive before the completion of the first burst transfer so that the data is not cached inside the CPU.

For DMA cycles, the CPU address is driven from the integrated DMA controller of the VT82C575M. For PCI or ISA master cycles, the CPU address is driven from the PCI or ISA bus through the integrated buffer inside the VT82C576M. The EADS# pin is asserted during DMA and master cycles to snoop the internal cache. If the HITM# signal is driven active by the CPU, then an altered internal cache line needs to be written back to the system before the intended memory access is performed. Snoop filtering and snoop ahead mechanism is implemented to minimize the snooping overhead during master accesses.

# 3. Advanced Cache Controller

### 3.1. Burst Synchronous and Asynchronous SRAMs

The VT82C570M supports direct-mapped cache systems with data size ranging from 128KB to 2MB. Burst synchronous, burst pipeline synchronous and asynchronous data SRAMs are supported to allow flexible system tradeoffs between cost and performance. The SRAM type is indicated in the following registers:

| RX51h bit4 | RX50h bit2 |                                      |

|------------|------------|--------------------------------------|

| 1          | -          | Asynchronous SRAM                    |

| 0          | 0          | Non-pipelined Burst Synchronous SRAM |

| 0          | 1          | Pipelined Burst Synchronous SRAM     |

The VT82C570M also supports eight CWE# pins for each byte in addition to the global GWE# option (RX48h bit 6) which allows glueless interfacing with either discrete cache chips or cache modules.

# 3.2. Multiple Tag Options

The VT82C570M supports both write-back and write-through schemes with maximum flexibility in selecting the number of tag and alter bits (from eight to eleven bits). No valid bit is required in all cases since system data are maintained valid all the time after initialization.

The minimum number of tag plus alter bits is eight to fit the standard x8 SRAMs. Three schemes are supported under this configuration: write-through, write-back with alter bit and write-back without alter bit. To allow a larger cacheable region, more than one x8 SRAMs are required for wider combined tag plus alter bits. The VT82C570M supports tag bits up to ten in addition to the alter bit for the write-back scheme. Note that the alter bit cannot be used as the eleventh tag bit even if the alter bit is not used. Three register bits are used to distinguish different cache schemes as indicated in Table 1.

| RX5Eh<br>bit 6 | RX50h<br>bit 4 | RX50h<br>bit 3 | write-thru/<br>write-back | tag-<br>bits | alter-<br>bit | total<br>bits |

|----------------|----------------|----------------|---------------------------|--------------|---------------|---------------|

| 0              | 0              | 0              | write-back                | 8            | 0             | 8             |

| 0              | 0              | 1              | write-back                | 7            | 1             | 8             |

| 0              | 1              | 0              | write-back                | 8            | 1             | 9             |

| 0              | 1              | 1              | write-back                | 10           | 1             | 11            |

| 1              | -              | 0              | write-thru                | 8            | -             | 8             |

| 1              | 0              | 1              | write-thru                | 7            | -             | N/A           |

| 1              | 1              | 1              | write-thru                | 10           | -             | 10            |

Table 1. Cache Schemes and Number of Tag/Alter Bits

#### 3.3. Cache Timing

Cache read and write hit timing is 3-1-1-1 for burst (pipelined or standard) synchronous SRAMs. For asynchronous SRAMs, cache hit timing can be programmed to be either zero, one or two wait states in RX51h. The first read cycle, other read cycle (second to fourth cycle in a burst transfer), first write cycle and other write cycle can be programmed independently. The following table indicates the speed requirement of the tag and data SRAM for different CPU bus clock frequencies.

| CPU Clock | Tag  | Sync. | Read/write     | Async. | Read/write      |

|-----------|------|-------|----------------|--------|-----------------|

|           | SRAM | SRAM  | Timing (sync.) | SRAM   | Timing (async.) |

| 50Mhz | -20 | -20 | 3-1-1-1/3-1-1-1 | -20 | 3-2-2-2/3-2-2-2 |

|-------|-----|-----|-----------------|-----|-----------------|

| 60Mhz | -15 | -15 | 3-1-1-1/3-1-1-1 | -20 | 3-2-2-2/4-2-2-2 |

| 66Mhz | -12 | -12 | 3-1-1-1/3-1-1-1 | -15 | 3-2-2-2/4-2-2-2 |

The following internal registers are associated with the cache controller:

RX50h: Cache access mode

| – bit 7-6: cache mode. 0x: disabled.                                                            |

|-------------------------------------------------------------------------------------------------|

| 10: enabled 11: initialization                                                                  |

| <ul> <li>bit 5: Cyrix CPU linear burst order: 0: disable</li> </ul>                             |

| 1: enable                                                                                       |

| <ul> <li>bit 4-3: number of tag plus alter bits (see Table 1)</li> </ul>                        |

| <ul> <li>bit 2: data synchronous SRAM type (if bit 4 of RX51h is 0):</li> </ul>                 |

| 0: standard synchronous SRAM                                                                    |

| 1: pipelined burst synchronous SRAM                                                             |

| <ul> <li>bit 1: cache read wait state for PCI masters (PCI clock)</li> </ul>                    |

| 0: zero wait state (2-1-1-1)                                                                    |

| 1: one wait state (3-2-2-2)                                                                     |

| <ul> <li>bit 0: cache write wait state for PCI masters (PCI clock)</li> </ul>                   |

| 0: zero wait state (2-1-1-1)                                                                    |

| 1: one wait state (3-2-2-2)                                                                     |

| RX51h: cache timing control                                                                     |

| <ul> <li>bit 4: data SRAM type</li> <li>0: synchronous SRAM (refer to bit2 of RX50h)</li> </ul> |

| 1: asynchronous SRAM                                                                            |

| – bit 7: read hit timing for the first cycle (CPU clock) for asynchronous SRAM:                 |

| 0: 1 wait state (3-x-x-x)                                                                       |

| 1: 2 wait state (4-x-x-x)                                                                       |

| <ul> <li>bit 6: write hit timing for the first cycle for asynchronous SRAM:</li> </ul>          |

| 0: 1 wait state (3-x-x-x)                                                                       |

| 1: 2 wait state (4-x-x-x)                                                                       |

| - bit 5: read hit timing for the second-fourth burst cycle for asynchronous SRAM:               |

| 0: 1 wait state (x-2-2-2)                                                                       |

| 1: 2 wait state (x-3-3-3)                                                                       |

| * write hit timing is always 1 wait state (x-2-2-2) for asynchronous SRAM                       |

| * read hit and write hit timing is always 3-1-1-1 for synchronous SRAM                          |

| – bit 3: bank of data SRAM: 0: 1 bank 1: 2 banks                                                |

| – bit 2-0: cache size 000: no cache 001: N/A                                                    |

| 010: N/A 011: 128KB                                                                             |

| 100: 256KB 101: 512KB                                                                           |

| 110: 1MB 111: 2MB                                                                               |

|                                                                                                 |

# 3.4. DRAM Post Write Buffers

The VT82C570M includes a four level DRAM post write buffer to optimize the performance of the L2 cache write miss and non-cacheable write operations. In this buffered arrangement, the fast CPU writes the data to the fast buffer and then terminates the cycle without any wait states. Once the cycle is terminated, the CPU may start a new operation and the DRAM controller concurrently writes the data from the buffer to the DRAM.

#### 3.5. Concurrent DRAM Writeback

In order to bypass the performance penalty imposed by the DRAM during writeback operations, the VT82C570M supports Concurrent DRAM Writeback operation. During a cache read miss with

dirty line replacement, there are two operations necessary: the dirty line in the L2 cache must be written back to the DRAM first and then current data must be filled to the L2 cache. The Concurrent DRAM Writeback mechanism involves the use of two fast zero-wait FIFO data buffers. While the dirty line is read into the first FIFO, the new DRAM data is read into the second FIFO concurrently. After the end of the L2 to FIFO fill, the CPU then reads the data from the second FIFO along the L2 cache fill. Concurrently, the data in the first FIFO is written to the DRAM. Once the first data is read into CPU, the CPU can continue its operation without waiting for the completion of the L2 cache fill and the dirty line DRAM fill.

# 3.6. Cacheable Region

Only on-board DRAM can be made cacheable. The cacheable region is determined by the following factors:

- the cache size,

- the tag size,

- the on-board DRAM size,

- the setting of the programmable non-cacheable region (RX41h and RX42h), and

- the cacheability of video and system BIOS as determined by the setting of RX40h.

The normal cacheable region is the minimum of the on-board DRAM size and 256 (1024 if there are 10 tag bits) times the cache size. The decoding of the normal cacheable region is built inside the chip so that no register setting is required.

The upper memory region (A0000h to FFFFFh) is an exception to the normal case. Since this region corresponds to memory-mapped IO ports, it is defaulted to be non-cacheable. However, the video (C0000h to C7FFFh) and system (E0000h to EFFFFh and F0000h to FFFFFh) BIOS can be made cacheable and write-protect by programming RX40h.

One other memory region inside the normal cacheable space can be made non-cacheable by programming the internal register RX41h and RX42h. The size of the region is from 64KB to 4MB. The base address of the region must be an integral multiple of the size of the region.

The cacheable region is consistent between the primary and the secondary cache through the use of the KEN# and EADS# pins to the CPU.

# 4. Enhanced DRAM Controller

The VT82C570M supports eight banks of DRAMs up to 512MB. The eight banks are grouped into four pairs and each bank can be independently made of 256K, 512K 1M, 2M, 4M, 8M and 16MxN DRAMs. Zero, one or both banks of DRAMs may be populated in each pair. The DRAM controller can support standard page mode, EDO and Burst-EDO DRAMs with either 64bit or 32bit in flexible mixed combinations.

#### 4.1. Standard Page Mode DRAM

The DRAM memory address generation is a function of the CPU and DRAM type. DRAM row and column addresses are multiplexed onto the same MA bus. When operating in non-page mode or on page misses, a row address followed by a column address is generated during the DRAM access. On page-hits, only a column address is generated during the DRAM access.

DRAM cycles normally operate in page mode. Each RAS# is held active after a DRAM access has finished and is precharged only when subsequent cycle to the same bank does not access the same DRAM page, or if an asynchronous event such as a RAS time-out.

For all CPU accesses, DRAM cycles are generated synchronously with the CPU clock. Critical DRAM timing parameters are individually programmable in RX22h to allow optimal matching between the DRAM and the CPU speed. The parameters include:

- bit 7-6: RAS# precharge time: 2-8 cycles,

- bit 5-4: RAS# pulse width: 4-10 cycles,

- bit 3-2: Read cycle CAS# pulse width: 1-4 cycles,

- bit 1: Write cycle CAS# pulse width: 1-2 cycles, and

- bit 0: RAS# to column address/column address to CAS#: 1-2 cycles.

The VT82C570M supports decoupled DRAM refresh (bit 0 of RX03h set) to allow on-board DRAM operation to continue before the slower ISA refresh is complete. Furthermore, CAS-to-RAS refresh (bit 3 of RX40h set) and slow refresh (bit 2 of RX5Eh set) are also supported to conserve power consumption and to allow more flexibility in selecting DRAMs with different refresh address requirement. In all cases, the RAS timing is staggered during refresh to minimize the power supply noise.

#### 4.2. EDO and Burst EDO DRAM

The DRAM controller of VT82C575M supports both EDO and Burst EDO DRAMs in addition to standard page mode DRAMs. This feature enhances the DRAM read performance in comparison with a standard DRAM device by one and two CPU clocks, respectively. The composition of the eight bank DRAM can be of mixed EDO with standard DRAM modules in the bank bases. The DRAM controller will generate EDO, Burst EDO or standard cycle according to the type of DRAM in each bank.

A software/firmware mechanism that can automatically detect EDO DRAM device can be integrated into the BIOS so that user configuration effort may be reduced. Register RX47h indicates the DRAM type of each bank.

RX47: DRAM type -default (0)

| 7,3: | Bank 3 | DRAM type      |

|------|--------|----------------|

|      | 00:    | Standard DRAM  |

|      | 01:    | Burst EDO DRAM |

|      | 10:    | EDO DRAM       |

|      | 11:    | Illegal        |

| 6,2: | Bank 2 |                |

| 5,1: | Bank 1 |                |

| 4,0: | Bank 0 |                |

#### 4.3. Other DRAM Parameters

The DRAM type, size and single/double bank information is indicated in the following registers:

RX43h: pair 0/1 DRAM size and configuration - bit 7-5: bank-pair 0 DRAM size (x2 if double bank): 000: 1MB 001: 2MB 010: 4MB 011: 8MB 100: 16MB 101: 32MB 110: 64MB 111: 128MB bit 4: number of banks of pair 0 0:1 bank 1: 2 banks (zero bank if bit 7-5 or RX20h is 0) bit 3-1: bank-pair 1 DRAM size bit 0: number of banks of pair 1 (zero bank if bit 3-1 of RX20h is 0)

| - bit 7-5:<br>- bit 4: nu<br>- bit 3-1: | bank-pair 3 DRAM                                                                                                                               | size<br>air 2 (zero bank if bit 7-5 or RX21h is 0)                                                                                                                               |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| – bit 7-5:<br>– bit 4: pa               | ow/column address<br>number of column<br>000: disabled<br>010: 10 bit<br>100: 12 bit<br>age mode operation<br>0: disable<br>number of column a | address for pair 0<br>001: 9 bit<br>011: 11 bit<br>others: illegal<br>1: enable                                                                                                  |

| – bit 0: D                              | RAM bus width:<br>0: 32 bit                                                                                                                    | 1: 64 bit                                                                                                                                                                        |

| – bit 7-5:<br>– bit 4: re               | number of column                                                                                                                               | address for pair 2                                                                                                                                                               |

| - bit7-4: r<br>- bit3-0: s              |                                                                                                                                                | t for each bank<br>h DRAM operation<br>1: 64 bit<br>;all banks are 32bit<br>;64bit operation for the corresponding DRAM bank<br>;32bit operation for the corresponding DRAM bank |

|                                         |                                                                                                                                                |                                                                                                                                                                                  |

# 5. Shadow RAM and ROM Decoding

The VT82C570M supports shadowing of system, video and other BIOS to speed up the access. The granularity is 16KB in address range C0000h to DFFFFh and 64KB in address range E0000h to FFFFFh. Read and write shadowing can be enabled or disabled independently in each region. Furthermore, read access to address range C0000h-C7FFFh and E0000h-FFFFFh can be programmed to be cacheable and write protected to further enhance the performance of video and system BIOS access.

If shadow RAM is not enabled, memory range A0000h to FFFFFh can be relocated to the top of the local DRAM so that the memory size is increased by 384KB. If only C (C0000h-CFFFFh) and/or F segments are used for shadowing, then the memory size is increased by 256KB. No DRAM can be relocated if either D or E segment is used as shadow memory. If the SMI capability is enabled, the memory range A0000h to BFFFFh is reserved for SM memory remap (RX5Bh bit 4 set) and cannot be relocated again. Therefore, the size of the increased memory reduces to 256KB and 128KB, respectively.

Accesses to either E or C segment can be programmed to be on-board ROM cycles. The E segment is used when the size of the system BIOS exceeds 64KB. The C segment is used when the video and system BIOS are combined into one single EPROM in an all-in-one system board implementation. A memory write cycle is typically not considered as a ROM cycle even if the address is decoded as such. To support flash EPROM which allows on-line modification of the memory content, the VT82C570M can be programmed to recognize such memory write cycles as ROM cycles (bit 6 of RX11h).

Furthermore, memory address range 15MB to 16MB can be programmed to be ISA cycles (instead of normal on-board DRAM cycles) if bit 2 of RX32h is set.

The following internal registers are associated with the shadow RAM and ROM decoding:

RX30h: C0000h-CFFFFh shadow control

- bit 7: CC000h-CFFFFh read shadow

- 1- enable 0-disable

- bit 6: CC000h-CFFFFh write shadow

- bit 5-4: C8000h-CBFFFh read/write shadow

- bit 3-2: C4000h-C7FFFh read/write shadow

- bit 1-0: C0000h-C3FFFh read/write shadow

RX31h: D0000h-DFFFFh shadow control

- bit 7-6: DC000h-DFFFFh read/write shadow

- bit 5-4: D8000h-DBFFFh read/write shadow

- bit 3-2: D4000h-D7FFFh read/write shadow

- bit 1-0: D0000h-D3FFFh read/write shadow

RX32h: E0000h-FFFFFh shadow control

- bit 7-6: E0000h-EFFFFh read/write shadow

- bit 5-4: F0000h-FFFFFh read/write shadow

- bit 3: other usage

- bit 2: memory range F00000h-FFFFFh always decoded as ISA cycle

- bit 1-0: other usage

RX33h: ROM decoding and memory relocation

- bit 7: C8000h-CFFFFh decoded as ROM cycle

- 1 enable 0 disable

- bit 6: C0000h-C7FFFh decoded as ROM cycle

- bit 5: E8000h-EFFFFh decoded as ROM cycle

- bit 4: E0000h-E7FFFh decoded as ROM cycle

- bit 3-2: relocation 00 disable (

- 00 disable 01 illegal 10 - 256K relocation 11 - 384K relocation

- bit 1-0: other

RX40h: ROM cacheable control

- bit 7: C0000h-C7FFFh cacheable and write-protect

- 1 enable 0 disable

- bit 6: F0000h-FFFFFh cacheable and write-protect

- bit 5: E0000h-EFFFFh cacheable and write-protect

- bit 4-3: other usage

- bit 2: secondary cache fill for CACHE# inactive memory cycles

# 6. Intelligent PCI Bus Controller

The VT82C570M supports the 32-bit PCI bus synchronously at half the CPU frequency. The 64bit to 32-bit data conversion and command regeneration are performed by the VT82C575M with minimum overhead. Four levels of post write buffers are included between the CPU and the PCI bus to allow for concurrent CPU and PCI operation. Consecutive CPU addresses are converted into burst PCI cycles with byte merging capability for optimal CPU to PCI throughput. A 32-bit fast data link is established between the two VT82C577M data units and the VT82C576M PCI bus controller so that the address, data and command information for CPU to PCI bus transactions is contained in the same chip. This arrangement, unique to the VT82C570M chip set, is crucial in achieving zero wait state buffer movement and also in implementing sophisticated and upgradable buffer management schemes such as the byte merging. For PCI master operation, four levels of post write buffers and four level of prefetch buffers are included for concurrent PCI bus and DRAM/cache accesses. 2-1-1-1 cache hit and 2-1-2-1 cache miss timing is performed to achieve greater than 110MB/s PCI bus master transfer rate for typical applications. Furthermore, the ISA and IDE bus are steered through a peer PCI bus so that the slower traffic does not block the normal traffic of the regular PCI bus. The VT82C570M is PCI 2.1 compliant.

# 6.1. CPU to PCI Operation

The PCI bus controller contains four levels of post write buffers between the CPU and PCI bus. If the write-buffer is not full and the cycle belongs to the PCI bus, the cycle can be pushed into the write buffer. Note that both data and address information of the buffered cycles are contained in the same chip (VT82C576M) to achieve optimal buffer management. The PCI bus controller converts consecutive CPU accesses into burst cycles on the PCI bus. The controller also monitors address and byte enable signals and performs byte merge (when the situation permits) between the two consecutive CPU write cycles in the write buffers. Therefore, it reduces the number of PCI cycles and creates further bursting possibilities.

A single 64-bit cycle, if spread over both higher and lower double words is converted into two consecutive commands for the PCI bus controller with two PADS#. The CPU data is latched inside the VT82C577M data units and re-aligned to the 32-bit PCI bus controller.

The following registers control the operation of the PCI bus interface:

RX82h: buffer control

- bit 7: 1/0 = CPU to PCI write buffer enable/disable

- bit 6: 1/0 = PCI to memory write buffer enable/disable

- bit 5: reserved

- bit 4: 1/0 = PCI accessing memory prefetch buffer enable/disable

- bit 3: 1/0 = PCI accelerated decoding enable/disable

- bit 2: reserved

- bit 1: 1/0 = on-board memory burst write enable/disable

- bit 0: 1/0 = on-board memory burst read enable/disable

RX83h: data link control

- bit 7: 1/0 = data link write cycle at 0/1 wait state

- bit 6-4: reserved

- bit 3: 1/0 = on-board memory detection point for PCI master at

- first data phase/address phase

- bit 2-1: reserved

- bit 0: must be 0

RX84h: PCI interface timing

- bit 7: 1/0 = slave mode lock function enable/disable

- bit 6: 1/0 = retry count at 64 times/16 times

- bit 5: 1/0 = retry deadlock error reporting enable/disable

- bit 4: 1/0 = retry status occurred/not occurred (write 1 to reset)

- bit 3: 1/0 = CPU to PCI fast back to back enable/disable

- bit 2: 1/0 = fast FRAME# generation enable/disable

- bit 1-0: 11/10/01/00: DEVSEL# decoding is subtractive/slow/medium/fast

# 6.2. PCI to Memory Operation

The PCI bus controller contains four level of PCI to memory write buffers and four level of PCI from memory prefetch buffers to streamline the PCI and memory bus operation. On the memory bus side, the VT82C576M PCI bus controller requests the ownership of the memory bus to the VT82C575M system controller through the PREQ# pin. The PGNT# is granted to the PCI bus controller after arbitration with the CPU request. The address generated by the PCI bus controller is passed to the CPU bus to snoop the primary and secondary cache. If the address hits an altered line of

the primary cache, the altered line will be written back to the system (either DRAM or secondary cache) before the intended access can continue.

#### 6.2.1. Snoop Ahead

CPUs with internal writeback cache systems need snoop operations to detect and compare the validity of the data in the cache in order to determine whether a writeback operation is required. The VT82C570M offers a snoop ahead feature to avoid the performance penalty of a normal snoop operation. The snoop ahead applies to the cycles of PCI master burst access to system memory or the L2 cache.

In a normal snoop operation, the DRAM/cache controller will discontinue burst operations when the master burst mode crosses the cache line. Then the controller will generate a snoop address to the CPU and wait one clock cycle for the CPU's response. If the CPU detects a non-coherence state between the L1 and system memory, the CPU would issue a HITM# signal. The HITM# signal instructs the PCI master to perform two operations: 1) back off from the memory bus and 2) initiate a L1 writeback cycle. If the CPU detects coherence between L1 and system memory, then the DRAM/cache controller would resume burst operations. In this normal snoop operation, the performance penalty is incurred when the controller waits one cycle for the CPU response.

In the VT82C570M snoop ahead feature, the main difference is that after the controller generates a snoop, the controller may continue burst operations without waiting one clock cycle for the CPU response. Since the cache line is sequentially incremented in the burst mode, the timing for the next cache line access can be predicted and the snoop address can be sent before the actual access. Consequently, by the time the physical access actually starts, the snoop address and the HITM# signal would already have been processed and the controller would not have to wait for the CPU response.

#### 6.2.2. Concurrent CPU and PCI Master Operations

In typical systems, the operation of PCI master access to the bus is a bottleneck. When the PCI master issues a REQ# signal for control of the PCI bus, 1) the REQ# signal is sent to the PCI Arbitrator, 2) the PCI Arbitrator then sends a PREQ# signal to the CPU Arbitrator, 3) the CPU Arbitrator sends a HOLD signal to the CPU, 4) after the CPU completes its current cycle, it responds back to the CPU Arbitrator with a HLDA signal and allows the PCI master to see the CPU bus, 5) upon receiving HLDA, the CPU Arbitrator sends the PGNT# signal to the PCI Arbitrator, and 6) the PCI Arbitrator then sends a GNT# signal to the PCI master. Only after the PCI master receives the GNT# signal can the PCI master access the bus. Consequently, the long critical path of the signals imposes a large performance penalty whenever the PCI master tries to access the bus in typical systems.

This performance bottleneck is bypassed in the VT82C570M through the use of concurrent operations techniques. The PCI Arbitrator in the VT82C570M acts as a gate separating the CPU and PCI Master operations. When the PCI master issues a REQ# signal, the PCI Arbitrator will follow the PCI bus arbitration protocol and immediately grant the bus to the PCI master. The PCI Master can then access the slave device on the PCI bus and perform PCI master operations. During this time, the CPU and the CPU bus has not been interfered with. Consequently, the CPU and the CPU bus is left free to process other operations concurrently with the PCI master operations and the bottleneck is bypassed. However, if the PCI master needs to access an on-board device such as system memory or the L2 cache, then the PCI Arbitrator "gate" opens and a PREQ# signal is sent to the CPU Arbitrator (Note that PREQ# signal occurs after the PCI bus is granted to the PCI master).

#### 6.3. PCI Arbitration and Interrupt Steering

The VT82C576M PCI bus controller arbitrates the ownership of the PCI bus between the four PCI masters and the controller itself. The arbitration is of rotational priority and provides the following register control in order to fine tune to specific application environments.

RX85h: PCI arbitration

- bit 7: 1/0 = fairness between CPU and PCI bus/priority on PCI bus

- bit 6: 1/0 = FRAME# based/REQ# based

- bit 5-4: 11/10/01/00 = CPU time slot in unit of 32/16/8/4 PCI clocks

- bit 3-0: PCI master bus time out 0000: disable 0001: 1 x 32 PCI clock

- 0010: 2 x 32 PCI clocks

- 0010. 2 x 32 1 01 0

- 1111: 15 x 32 PCI clocks

The interrupts signals from the PCI bus (INTA#-D#) along with those from the ISA bus and the two plug and play ports are completely steerable to the two 8259A compatible interrupt controllers inside the VT82C575M. Please refer to the "Plug and Play Controller" section for details.

#### 6.4. PCI Configuration

The VT82C570M supports the standard PCI configuration mechanism #1 and #2 (determined by bit 7 of internal register RX86h, defaulted as mechanism #1). Under mechanism #1, IO address CF8h is used as the configuration address port and CFCh as the configuration data port. Both ports are 32-bit wide. If the VT82C570M detects a full double word write at address CF8h, the chip latches the value into it. Any other types of accesses to this address are treated as a normal IO access. The format of the configuration address is as follows:

- bit 31: configuration enable (this bit needs to be set to translate a configuration data access into a configuration cycle).

- bit 30-24: reserved

- bit 23-16: bus number (must be 0 to enable the configuration)

- bit 15-11: device number (00000 access the PCI bus controller internal registers, other values access other PCI devices)

- bit 10-8: function number (don't care for internal registers, but pass through to PCI bus for other PCI devices)

- bit 7-2: register number

- bit 1-0: always 00 (only type 0 format is supported)

Under mechanism #2, CPU IO read and write cycles to the C000-CFFFh address range are translated into PCI configuration read and write cycles, if configuration space enable register at address CF8h is enabled. The translation method carries the least significant 8 bits of the CPU address to the least significant 8 bits of the PCI address to select one of the 256 8-bit IO location in the PCI configuration space. Bits 8 to 11 of the CPU address are mapped to one of the 16 devices' IDSEL# input. These IDSEL# inputs of the PCI devices have to be hard-wired to one of the AD16-31 signals on the PCI bus. CA<11:8> being 0 accesses the internal configuration register of the VT82C570M and AD17-31 are available for other PCI devices.

Bus controller has both internal register and PCI configuration register. The internal configuration registers (RX80h to RXFFh) will not be able to access through either of the PCI configuration mechanism. It can be accessed through I/O ports A8 and A9 only.

The following PCI configuration registers are defined:

- Configuration Register: Mandatory header field (or IDX00 and IDX04 based on the 32-bit IO port convention)

- IDX00<15:0> Vendor ID = 1106h (read only)

- IDX00<31:16> Device ID = 0576h (read only)

- IDX04<15:0> Command register

- bit 0: IO space = 1 (read only)

- bit 1: memory space = 1 (read only)

- bit 2: bus master = 1 (read only)

- bit 3: special cycle monitoring = 0 (read only)

- bit 4: memory write and invalid command = 0 (read only)

bit 5: VGA palette snoop = 0 (read only)

- bit 6: parity error response (read/write, default=0)

- bit 7: address/data stepping = 0 (read only)

- bit 8: SERR# enable (read/write, default=0)

- bit 9: fast back-to-back cycle enable (read/write, default=0)

- bit 15-10: reserved

- IDX04<31:16> Status register (or IDX06<15:0>)

bit 0-6: reserved

bit 7: fast back-to-back: reserved

bit 8: data parity detected: reserved

bit 9-10: DEVSEL# timing: reserved

bit 11: signaled target abort: reserved

bit 12: received target abort (read only, write one to clear)

bit 13: signaled master abort: reserved

bit 14: signaled system error: reserved

bit 15: detected parity error (write only, write one to clear)

# 7. Master Mode Enhanced IDE Controller

The VT82C570M has integrated a Master Mode IDE controller that supports dual channel/four device Enhanced-IDE bus (Enhanced-IDE specification such as mode-3 and mode-4 transfer rate and CD-ROM). The IDE controller has sixteen levels of double word prefetch and write buffers for the two channels to allow concurrent PCI bus and IDE drive operation. The data bus, control signals, write buffers and prefetch buffers are embedded in the VT82C570M and separated from those of the PCI and ISA bus so that performance is optimized and electrical loading is minimized. The command and recovery time of each IDE device can be individually programmed in units of PCI bus clock to achieve optimal speed of the device up to >22MB/s.

# 7.1. IDE Drive Interface Configuration

The IDE controller includes a variety of configuration registers for controlling the timing of individual IDE drives and different type of I/O access cycles. The format of configuration registers are compatible with the PCI configuration space specification and should be programmed by PCI configuration protocol.

Configuration register 4F/4E defined read/write command active pulse width and recovery time of non-1F0h port access for primary and secondary channels, respectively. One of sixteen selections, from one to sixteen PCI bus clocks, can be selected for each of the parameters. Register 4B/4Ah define the read and write access timing to the 1F0h port for the master and slave drives of the primary channel, respectively. Similarly, register 49/48h are used to control the master and slave drives of the secondary channel, respectively.

Register 4Ch determines the address setup time of for the 1F0h port access. For non-1F0h port access, the address setup time is always set to be 4 PCI bus cycles.

# 7.2. Prefetch and Post Write Buffers

The IDE controller supports sixteen levels of prefetch and write buffers for each of the two channels. These buffers provide concurrent operation for the IDE drives while the PCI bus may be performing other tasks.

Prefetch option may start after the following conditions are met:

- 1) the prefetch buffers are enabled;

- 2) the host has issued a Read\_sector, or Read\_multiple command into 1F7h command register; (Read-long in excluded)

- 3) a read to 1F0h data port is detected.

The IDE controller will read the subsequent 1F0h data after the first 1F0h data word is read from the IDE drive. Such a prefetch operation will be terminated when the 512th byte of the 1F0h data is read. Therefore, to avoid reading the incorrect data of the next sector which may be ready for host access, the prefetch operation does not continue through the sector boundary. The IDE controller also supports non-512th byte reading (e.g. 2352 for CD-ROM) according to the setting of internal registers (61/60h for the primary channel and 69/68h for the secondary channel).

If the post write buffer is enabled, the IDE controller will perform post-write operation for the host 1F0h write cycles. The CBE#3:0 status of the PCI bus command is latched to determine the active bytes for the drive interface. The IDE controller will terminate the bus cycle once the data is latched into the write buffer.

# 7.3. Operation Mode Selection

The IDE Controller can support both ATA compatible mode and PCI relocation mode for I/O port address configuration. Mode control is determined by PCI configuration register 42 bit <7..6>.

| bit 7 0/1 ATA mode/PCI mode for 1st channel | bit 7 | 0/1 | ATA mode/PCI mode for 1st channel |

|---------------------------------------------|-------|-----|-----------------------------------|

|---------------------------------------------|-------|-----|-----------------------------------|

bit 6 0/1 ATA Mode/PCI mode for 2nd channel

**ATA Mode:** The controller registers are hardwired to fixed IRQs and IO space as indicated in the following table:

| Channel   | Command Block Registers | Control Block Registers |

|-----------|-------------------------|-------------------------|

| Primary   | 1F0h - 1F7h             | 3F6h                    |

| Secondary | 170h - 177h             | 376h                    |

**PCI Mode:** The registers of the IDE channels are completely relocatable in IO space. Base Address registers at offset 10h, 14h, 18h and 1Ch in the VT82C576M's configuration space registers are used to map the IDE registers into IO space. Specific base address registers are used to map the different register blocks as defined in the following table:

| Channel   | Command Block Registers    | Control Block Registers    |

|-----------|----------------------------|----------------------------|

| Primary   | Base Address at offset 10h | Base Address at offset 14h |

| Secondary | Base Address at offset 18h | Base Address at offset 1Ch |

Base registers used to map Command Block registers must ask for 8 bytes of IO space. Base registers used to map Control Block registers must ask for 4 bytes of IO space. In this four byte allocation the byte at offset 02h is where the alternate status/device control byte is located. Other bytes in the four byte allocation (bytes at offsets 0,1 and 3) are unused.

# 7.4. Scatter and Gather and Bus Master Operation

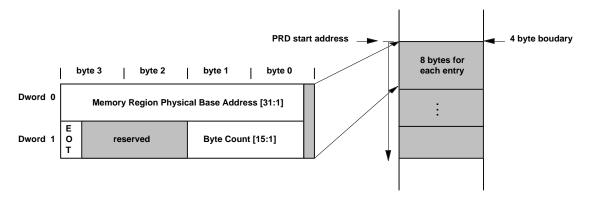

The VT82C570M is compliant with the bus master programming interface for IDE ATA controllers SFF-8038 rev.1.0. Before the controller starts a master transfer, the IDE controller is given a pointer to a physical region descriptor (PRD) table (refer to Figure 2). This table contains some number of PRDs which describe areas of memory that are involved in the data transfer. Each PRD entry is 8 bytes in length. The first 4 bytes specify the byte address of a physical memory region. The next two bytes specify the count of the region in bytes. A value of zero indicates a 64KB size. Bit 7 of the last byte indicates the end of the table; bus master operation terminates when the last descriptor has been retired.

Figure 2: Physical Region Descriptor Table

The Scatter and Gather mechanism allows for larger transfer blocks to be scattered to or gathered from memory. This operation minimizes interrupts and CPU intervention. To initiate a bus master transfer between the system memory and the IDE device, the following steps are required:

- 1) Software prepares a PRD table in system memory.

- 2) Software determines the starting address on the PRD table by loading the PRD Table Pointer Register. The direction of the data transfer is determined by the Read/Write Control bit. Clear the Interrupt bit and Error bit in the Status register.

- 3) Software issues the appropriate DMA command to the IDE device.

- 4) Write "1" to the Start bit in the Bus Master IDE Command Register for the appropriate channel to engage bus master function.

- 5) The controller transfers data to/from memory responding to DMA requests from the IDE device.

- 6) At the end of the transfer the IDE device signals an interrupt.

- 7) In response to the interrupt, software resets the start/stop bit in the command register and reads the controller status and then the drive status to determine the success of the transfer.

# 8. Plug and Play Controller

The VT82C570M provides two plug and play ports for converting non plug and play devices into plug and play devices on the main board. Interrupts from the PCI bus (INTA# to INTD#), ISA bus and the plug and play ports can be directed to the individual channels of the two 8259A compatible interrupt controller under program control. Similarly, the DMA control signals from the ISA and the plug and play ports can be directed to the individual channels of the two 82C37A compatible DMA controller under program control. The configuration mechanism is compliant with the plug and play BIOS and the Microsoft Windows 95<sup>TM</sup> operating system. The VT82C570M also provides two general purpose programmable chip selects for reconfiguring IO address or for controlling non-intelligent IO devices. The following registers control the functionality of the plug and play ports:

RXFBh: Plug and play DRQ routing

|   | r nag unia praj Driv | i o u u u g       |              |           |

|---|----------------------|-------------------|--------------|-----------|

| - | bit 7-6: reserved    |                   |              |           |

| - | bit 5-3: PDRQ1 ro    | uting             |              |           |

|   | 000: DRQ0            | 001: DRQ1         | 010: DRQ2    | 011: DRQ3 |

|   | 100: reserved        | 101: DRQ5         | 110: DRQ6    | 111: DRQ7 |

| - | bit 2-0: PDRQ0 ro    | uting: same as Pl | DRQ1 routing |           |

|   |                      |                   |              |           |

RXFCh: PCI interrupt polarity

- bit 7-4: reserved

- bit 3 = 1/0: INTA# invert (edge)/non-invert (level)

- bit 2 = 1/0: INTB# invert (edge)/non-invert (level)

- bit 1 = 1/0: INTC# invert (edge)/non-invert (level)

- bit 0 = 1/0: INTD# invert (edge)/non-invert (level)

RXFDh: Plug and play IRQ routing

bit 7-4: INTD# routing

|                     | 0              |                |             |

|---------------------|----------------|----------------|-------------|

| 0000: reserved      | 0001: IRQ1     | 0010: reserved | 0011: IRQ3  |

| 0100: IRQ4          | 0101: IRQ5     | 0110: IRQ6     | 0111: IRQ7  |

| 1000: IRQ8          | 1001: IRQ9     | 1010: IRQ10    | 1011: IRQ11 |

| 1100: IRQ12         | 1101: reserved | 1110: IRQ14    | 1111: IRQ15 |

| hit 2 0. DIDOO rous | ting           |                |             |

bit 3-0: PIRQ0 routing

RXFEh: PCI IRQ routing

- bit 7-4: INTA# routing: same as INTD# routing

- bit 3-0: INTB# routing: same as INTD# routing

#### RXFFh: PCI IRQ routing

- bit 7-4: INTC# routing: same as INTD# routing

- bit 3-0: PIRQ1 routing: same as INTD# routing

The routed IRQ and DRQ channels for the PCI and plug and play ports cannot be reused by the ISA bus (under plug and play BIOS or operating system control). The IRQ and DRQ channels of the two plug and play ports cannot overlap but the four PCI interrupts are level sensitive and thus can be shared.

# 9. ISA Bus Controller

The ISA bus state machine is included in the VT82C575M which controls and monitors all the ISA bus signals. To coordinate the bus operation with the VT82C576M PCI bus controller, the ISAREQ# signal is used. In particular, ISAREQ# is activated by the VT82C576M for CPU cycles that do not hit on-board memory and PCI devices to activate the ISA state machine. The ISA bus data is isolated form the CPU/cache and DRAM bus as a separate port form the VT82C577M data units.

The VT82C575M includes two 82C37A compatible DMA controllers, two 82C59A compatible interrupt controller, one 82C54 compatible timer and port B logic. The integrated DMA controller runs either at the same or half the speed of the ISA clock (bit 6 of RX10h). The DRQ and IRQ from the PCI bus, ISA bus and the two plug and play ports are steered and combined before delivering to the DMA and interrupt controllers. The integrated interrupt controller is extended to support level sensitive interrupts in addition to the 8259A compatible edge trigger interrupts (RX63-64h).

# **10.** Power Management Unit

The integrated power management unit monitors IO events, interrupt, DMA and PCI master request signals to detect the status of system activity. Each event can be turned off or assigned to one of two event classes tracked by two independent idle timers. Two additional reloadable timers are provided for house-keeping or mode switching purposes. One of the timers can also be used to keep track the activity of specific peripheral devices. The system management interrupt (SMI) may be triggered by multiple sources including time-out of individual timers, occurrence of system activities, external input and software programming for flexible applications. The SMI routine checks the status and takes appropriate actions including clock speed switching (or throttling) and IO and power control. The power management unit is sophisticated enough to implement any power management model including the APM mechanism.

#### 10.1.Idle Timers

The VT82C570M includes two idle timers to monitor primary and secondary system events. In addition to interrupts, the primary events are classified into the following eight categories (RX52h, RX53h):

- bit 7: keyboard access (IO port 60h),

- bit 6: serial port access (IO port 3F8h-3FFh, 2F8h-2FFh, 3E8h-3EFh, 2E8h-2EFh),

- bit 5: parallel port access (IO port 378h-37Fh, 278h-27Fh),

- bit 4: video access (IO port 3B0h-3DFh and memory A/B segments),

- bit 3: hard disk and floppy access (IO port 1F0h-1F7h and 3F5h),

- bit 2: IO port 100h-3FFh,

- bit 1: external input (Turbo pin scanned in through VT82C416),

- bit 0: DRQ/LREQ: DMA and local bus master requests.

Each category can be enabled as primary activities by setting the corresponding bit of RX52h to 1. Each occurrence of a primary activity reloads the idle timer with a value determined by bit 3-1 of RX59h.

| 000 - disable | 001 - 1 sec  | 010 - 8 sec   | 011 - 32 sec  |

|---------------|--------------|---------------|---------------|

| 100 - 1 min.  | 101 - 8 min. | 110 - 16 min. | 111 - 32 min. |

The cause of the timer reload is recorded in the corresponding bit of RX53h while the timer is reloaded. If no primary activity occurs during the time period, the idle timer will time out and the VT82C570M can be programmed to trigger an SMI to switch the system to a power down mode.

The idle timer distinguishes between two kinds of interrupt requests as far as power management is concerned: the primary and secondary interrupts. Like other primary activities, the occurrence of a primary interrupt demands the system to return to its full processing capability. Secondary interrupts, however are typically used for house keeping tasks in the background and are unnoticeable to the user. The VT82C570M allows each channel of interrupt request to be declared as either primary or secondary in RX60h and RX61h.

| - | RX61h 1 - primary interrupt 0 - secondary interrupt |              |              |              |  |  |

|---|-----------------------------------------------------|--------------|--------------|--------------|--|--|

|   | bit 7: IRQ15                                        | bit 6: IRQ14 | bit 5: IRQ13 | bit 4: IRQ12 |  |  |

|   | bit 3: IRQ11                                        | bit 2: IRQ10 | bit 1: IRQ9  | bit 0: IRQ8  |  |  |

| _ | RX60h                                               |              |              |              |  |  |

|   | bit 7: IRQ7                                         | bit 6: IRQ6  | bit 5: IRQ5  | bit 4: IRQ4  |  |  |

|   | bit 3: IRQ3                                         | bit 2: IRQ1  | bit 1: IRQ0  |              |  |  |

#### **10.2. Handling of Secondary Events**

If secondary IRQs occur and if the secondary events handler enable is defined in bit 1 of RX5fh (set to 1), then the secondary IRQ triggers the secondary events handler and services the interrupt request. After the interrupt is serviced (EOI, or "End of Interrupt") or after the secondary events counter runs out, the secondary events handler generates a SMI which will return the system back to the original mode. The EOI is defined in bit 1 of RX5Fh (set to 0) and the timer is found in bit 3-2 of RX5Fh:

00 - 2 ms 01 - 16 ms 10 - 64 ms 11 - EOI + .125ms

#### **10.3. General Purpose and Peripheral Timers**

The VT82C570M includes two reloadable timers to support various house keeping tasks. The two timers can be loaded by writing an 8-bit value into RX58h and RX67h, respectively. The time base for the two timers is determined by bit 7-6 of RX59h and bit 3-2 of RX66h, respectively:

00- disable 01 - 32.768Khz 10- 1 sec 11 - 1 min.

The time out of either timer can be programmed to trigger an SMI for proper system response. In addition to the house keeping function, the second reloadable timer also covers the functionality of a peripheral timer to monitor any combination of the following peripheral events (bit7-0 of RX65h):

– bit 7: keyboard access

- bit 3: parallel port access

- bit 1: speaker access

- bit 6: serial port access

- bit 2: reserved

- bit 0: reserved

- bit 5: video access

- bit 4: hard disk and floppy access.

# 10.4.System Management Interrupt

There are eight possible sources for triggering an SMI (RX54h and RX55h):

- bit 7: primary idle timer time-out,

- bit 6: general purpose timer (1st reloadable timer of 10.3) time-out,

- bit 5: primary activity occurrence,

- bit 4: primary interrupt occurrence,

- bit 3: external pin (Turbo) toggle,

- bit 2: DRQ/PREQ occurrence,

- bit 1: peripheral timer or secondary idle timer time-out,

- bit 0: software SMI.

The SMI action includes clock speed changing, clock throttling control and power/peripheral control by programming the following registers:

a. CPU clock frequency (bit 3-0 of RX56h)

| 0000 - 16Mhz | 1000 - 8Mhz  | 0001 - 40Mhz  | 1001 - 20Mhz |

|--------------|--------------|---------------|--------------|

| 0010 - 50Mhz | 1010 - 25Mhz | 0011 - 80Mhz  | 1011 - 40Mhz |

| 0100 - 66Mhz | 1100 - 33Mhz | 0101 - 100Mhz | 1101 - 50Mhz |

| 0110 - 8Mhz  | 1110 - 4Mhz  | 0111 - 60Mhz  | 1111 - 30Mhz |

The clock generator in the VT82C416 guarantees smooth frequency changes if the original and target frequencies fall in the same bank (same bit 3 of RX56h).

- b. Clock throttling (bit 0 of RX5Bh): set the bit to 1 enables clock throttling. The STPCLK# period and duty cycle is controlled in RX02h.

- bit 4: STPCLK# throttling period: 1-1.7ms \* 16 0-3.35us \* 16,

bit 3-0: duty cycle for STPCLK# 1/16 15/16.

- c. Power/peripheral control (bit 7-4 of RX5Ah): More than ten general purpose output ports. Some of the ports are only available in notebook mode (eight CWE# pin reused as GPIO ports) and other ports need to be latched using external logic.

The setting of the above registers depends on the power management model and the cause of the SMI. Through this basic mechanism, the VT82C570M is capable of supporting many different power management models. For instance, BIOS routines are ready made to support the standard APM (Advanced Power Management protocols) for a cooperative power management among the application software, operating system, BIOS and the hardware. To illustrate the capability and flexibility of the VT82C570M, take a simple model that supports full-on, doze and sleep modes.

Bit 7 and bit 3 of RX54h are set and bit 5, 4 and 2 are not set during the full-on mode. Any occurrence of a primary activity reloads the idle timer without triggering an SMI so that no processing overhead is involved and the system performance is not degraded at all. The first SMI triggering happens when the idle timer is timed out or when the external pin is pushed by the user to force the

system into sleep. The SMI routine slows down the CPU clock and puts the system into the doze mode. Bit 7 of RX54h is now turned off and bit 2, 4, 5 are turned on to monitor the occurrence of a primary activity which will trigger an SMI to put the system back into the full-on mode.

By setting bit 6 of RX54h to 1, the time out of the general purpose timer will trigger an SMI which can switch the system from the doze mode to the sleep mode. If a primary activity occurs before the time-out of the general purpose timer, the system goes into the full-on mode and bit 6 of RX54h is turned off and the time-out of the general purpose timer will be ignored.

#### 10.5.Conserve Mode

The conserve mode is a relatively straight-forward mode that monitor primary events and primary IRQs. The conserve mode is enabled by bit 5 of RX5Fh. The conserve mode generates no SMIs and it does not use a time base counter. Instead, the conserve mode offers two methods to conserve: clock throttling and clock division.

# **11. Multi-function X-Bus Peripherals**

# 11.1.Scan Logic

The scan-in and scan-out logic uses the SCANIN and SCANOUT pins to communicate between the VT82C570M and the VT82C416. The signals to be scanned in to the VT82C570M from the VT82C416 through the SCANIN pin are indicated in Table 2:

| scan order | signal name | scan order | signal name | scan order | signal name |

|------------|-------------|------------|-------------|------------|-------------|

| 0          | DRQ0        | 8          | IRQ4        | 16         | IRQ14       |

| 1          | DRQ1        | 9          | IRQ5        | 17         | IRQ15       |

| 2          | DRQ2        | 10         | IRQ6        | 18         | IRQ1        |

| 3          | DRQ3        | 11         | IRQ7        | 19         | IRQ12       |

| 4          | DRQ5        | 12         | IRQ#8       | 20         | A20 Gate    |

| 5          | DRQ6        | 13         | IRQ9        | 21         | KBRC#       |

| 6          | DRQ7        | 14         | IRQ10       | 22         | Turbo       |

| 7          | IRQ3        | 15         | IRQ11       | 23         | IOCHK#      |

#### Table 2. Scan-in Signal Sequence

On the other hand, the signals to be scanned out from the VT82C570M to the VT82C416 through the SCANOUT pin are listed in Table 3:

| scan order | signal name | scan order | signal name |

|------------|-------------|------------|-------------|

| 0          | ClkSel0     | 5          | MouseLock   |

| 1          | ClkSel1     | 6          | RP13        |

| 2          | ClkSel2     | 7          | RP14        |

| 3          | ClkSel3     | 8          | RP15        |

| 4          | RPS2        | 9          | RP16        |

#### Table 3. Scan-out Signal Sequence

Clksel0-3 reflect bit 3-0 of RX56h for the CCLK frequency. RP13-16 are the jumper setting of MA0-3 at power on reset. These four bits are transmitted to the keyboard controller inside the VT82C416. These four bits can also be read from bit 3-0 of RX64h.

There are twenty-four scan-in signals and ten scan-out signals. Both the VT82C570M and the VT82C416 use both edges of the OSC clock as the scan clock. After system reset, the two chips are initialized to the same scan order and the communication between the two chips runs forever.

#### 11.2.The XD to SD buffer:

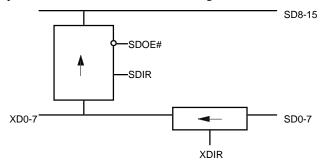

The available external pins are XD0-7, SD0-7, SD8-15, SDIR, SDOE# and XDIR. If the XDIR pin is high, the data flows from the SD0-7 to the XD0-7 bus. If the SDIR pin is high, the data flows from the XD0-7 to SD8-15. If the SDIR pin is low, then the data flows from SD8-15 to XD0-7. If SDOE# is low, it enables the internal data transfer between XD0-7 to the SD8-15 buffer. If the XDIR pin is low, the data flows from the XD0-7 to the SD0-7 bus. During the internal keyboard controller and RTC read cycles, the XD0-7 bus is driven by the VT82C416 independent of the XDIR value. If the XDIR pin is low, the data is also driven to the SD0-7 bus; otherwise, the SD0-7 bus is not driven by the chip. During the internal keyboard controller and RTC write cycles of even address bytes, the XDIR pin must be driven low for the XD0-7 bus to write into the internal peripherals write cycle of odd address byte, the SDIR and XDIR pin must be driven low for transferring SD8-15 to SD0-7.

Figure 3. The XD to SD Block Diagram

#### 11.3. Multi-clock generator: