# 82C556M/82C557M/82C558M

# Viper-M (Multimedia) Chipset

# **Preliminary Data Book**

Revision: 1.0 912-2000-010 April 1995

M 9004196 0000899 038 MM

#### Copyright

Copyright © 1995, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 2525 Walsh Avenue, Santa Clara, CA 95051.

#### Disclaimer

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### Trademarks

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

OPTi Inc.

2525 Walsh Avenue Santa Clara, CA 95051 Tel: (408) 980-8178 Fax: (408) 980-8860 BBS: (408) 980-9774

ii

#### 9004196 000090068T 🎟

# **Table of Contents**

| 1.0 | ) Fea | Features1 |                                            |     |  |  |

|-----|-------|-----------|--------------------------------------------|-----|--|--|

| 2.0 | Ονε   | erview    |                                            | 2   |  |  |

|     | 2.1   | 82C55     | 6M (DBC) Data Buffer Controller            | 3   |  |  |

|     | 2.2   | 82C55     | 7M (SYSC) System Controller                | 3   |  |  |

|     | 2.3   |           | 8M (IPC) Integrated Peripherals Controller |     |  |  |

| 3.0 | Sig   | nal Def   | finitions                                  | 6   |  |  |

|     | 3.1   | Signal    | I Description Definitions                  | 6   |  |  |

|     | 3.2   | 82C55     | 6M Signal Descriptions                     | 11  |  |  |

|     |       | 3.2.1     | CPU Bus Interface Signals                  | 11  |  |  |

|     |       | 3.2.2     | 82C557M Interface Signals                  |     |  |  |

|     |       | 3.2.3     | DRAM Interface Signals                     |     |  |  |

|     |       | 3.2.4     | Power and Ground Pins                      | 12  |  |  |

|     | 3.3   | 82C55     | 7M Signal Descriptions                     | 19  |  |  |

|     |       | 3.3.1     | Reset and Clock Signals                    |     |  |  |

|     |       | 3.3.2     | CPU Bus Interface Signals                  | 19  |  |  |

|     |       | 3.3.3     | Cache Control Interface Signals            | 21  |  |  |

|     |       | 3.3.4     | DRAM Interface Signals                     | 22  |  |  |

|     |       | 3.3.5     | AT Bus Interface Signals                   | 23  |  |  |

|     |       | 3.3.6     | Bus Arbiter Interface Signals              | 24  |  |  |

|     |       | 3.3.7     | PCI/VL Bus Interface Signals               | 25  |  |  |

|     |       | 3.3.8     | 82C556M/82C558M Interface Signals          | 26  |  |  |

|     |       | 3.3.9     | Power and Ground Pins                      | 27  |  |  |

|     | 3.4   | 82C55     | 8M Signal Descriptions                     | 35  |  |  |

|     |       | 3.4.1     | Reset and Clock Signals                    |     |  |  |

|     |       | 3.4.2     | IDE Interface Signals                      |     |  |  |

|     |       | 3.4.3     | 82C557M and 82C556M Interface Signals      |     |  |  |

|     |       | 3.4.4     | PCI Bus Interface Signals                  |     |  |  |

|     |       | 3.4.5     | CPU Interface Signals                      | 40  |  |  |

|     |       | 3.4.6     | ISA Bus Interface Signals                  | 41  |  |  |

|     |       |           |                                            |     |  |  |

|     |       |           |                                            | DTI |  |  |

Page iii

🔳 9004196 0000901 516 🔳

912-2000-010

|     |     | 3.4.7   | ISA DMA   | Arbiter Signals                                                  | 43 |

|-----|-----|---------|-----------|------------------------------------------------------------------|----|

|     |     | 3.4.8   | Interrupt | Control Signals                                                  | 45 |

|     |     | 3.4.9   | RTC and   | Timer Signals                                                    | 46 |

|     |     | 3.4.10  | Miscellan | eous Signals                                                     | 47 |

|     |     | 3.4.11  |           | d Ground Pins                                                    |    |

|     | _   |         |           |                                                                  | 50 |

| 4.0 | Fun |         | -         | tion                                                             |    |

|     | 4.1 | Reset L | _ogic     |                                                                  | 52 |

|     | 4.2 | System  | n Clocks  |                                                                  | 52 |

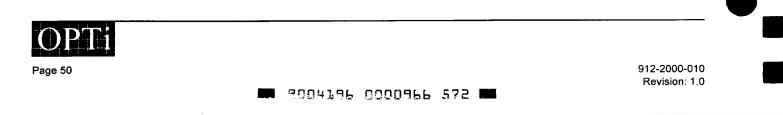

|     |     | 4.2.1   | CPU and   | 82C557M Clocks                                                   | 52 |

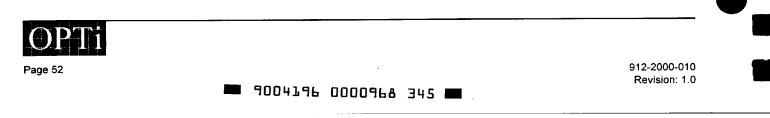

|     |     | 4.2.2   | PCI and V | VL Bus Clocks                                                    | 53 |

|     |     | 4.2.3   | AT Bus C  | locks                                                            | 53 |

|     | 4.3 | Cache   | Subsyster | n                                                                | 54 |

|     |     | 4.3.1   | -         | st Mode Control                                                  |    |

|     |     |         |           | Cyrix Linear Burst Mode Support                                  |    |

|     |     | 4.3.2   | Cache Cy  | ycle Types                                                       | 54 |

|     |     | 4.3.3   | Cache O   | peration                                                         | 55 |

|     |     |         | 4.3.3.1   | L2 Cache Read Hit                                                | 55 |

|     |     |         | 4.3.3.2   | L2 Cache Write Hit Cycle                                         |    |

|     |     |         | 4.3.3.3   | L2 Cache Read Miss                                               |    |

|     |     |         | 4.3.3.4   | L2 Cache Write Miss                                              |    |

|     |     |         | 4.3.3.5   | Adaptive Write-Back Policy                                       |    |

|     |     |         |           | 4.3.3.5.1 Write-Through on Page Hit and RAS# Active (AWB Mode 1) |    |

|     |     |         |           | 4.3.3.5.2 Write-Through on Page Hit (AWB Mode 2)                 |    |

|     |     |         | 4.3.3.6   | Tag Compare Table                                                |    |

|     |     |         | 4.3.3.7   | Tag and Dirty RAM implementations                                |    |

|     |     |         |           | 4.3.3.7.1 Separate Tag/Dirty RAM Implementation                  |    |

|     |     |         |           | 4.3.3.7.2 Combined Tag/Dirty RAM Implementation                  |    |

|     |     |         | 4.3.3.8   | Cache Initialization                                             |    |

|     |     |         | 4.3.3.9   | Write Back Cache with DMA/ISA Master/PCI Master Operation        |    |

|     |     |         |           | Cacheability and Write Protection                                |    |

|     |     | 4.3.4   | Synchror  | nous SRAM Support                                                | 77 |

|     |     |         | 4.3.4.1   | Pipelined Synchronous SRAM support                               |    |

|     |     |         | 4.3.4.2   | SONY SONIC-2WP (Cache Module) Support                            | 77 |

|     |     | 4.3.5   | SRAM R    | equirements                                                      | 77 |

|     |     |         |           |                                                                  |    |

Page iv

🔳 9004196 0000902 452 💻

| 4.4  | DRAM    | Controller                 |                          | 80 |

|------|---------|----------------------------|--------------------------|----|

|      | 4.4.1   | EDO Support                |                          |    |

|      | 4.4.2   | Programming the DRAM Pa    | arameters                |    |

|      |         |                            | 1 banks                  |    |

|      |         |                            | ations                   |    |

|      |         | 4.4.2.3 Timing Parameter   | rs                       |    |

|      |         | 4.4.2.4 Drive Strengths    |                          | 81 |

|      | 4.4.3   | -                          |                          |    |

|      |         |                            | le                       |    |

|      |         |                            | le                       |    |

|      |         |                            | neration/Detection Logic |    |

|      |         |                            | ogic                     |    |

|      | 4.4.4   | -                          |                          |    |

|      | 4.4.5   | DRAM DMA/Master Cycles     | S                        |    |

| 4.5  | PCI Bu  | s Interface                |                          |    |

|      | 4.5.1   | PCI Master Cycles          |                          |    |

|      |         | 4.5.1.1 System Memory A    | Access                   |    |

|      |         |                            | ry Access                |    |

|      |         |                            | noop                     |    |

|      | 4.5.2   |                            |                          |    |

|      |         |                            | es                       |    |

|      |         | -                          | lerge                    |    |

|      |         | 4.5.2.3 ISA Master Cycles  | S                        |    |

| 4.6  | VL Bus  | Interface                  |                          | 88 |

| 4.7  | AT Bus  | Interface                  |                          |    |

| 4.8  | XD Bu:  | Interface                  |                          |    |

| 4.9  | Bus Ar  | pitration Logic            |                          |    |

| 4.10 | Data B  | is Conversion/Data Path Ce | control Logic            |    |

| 4.11 | Interna | Integrated 82C206          |                          |    |

|      | 4.11.1  | Top Level Decoder and Cor  | nfiguration Register     |    |

|      | 4.11.2  |                            | • • •                    |    |

|      |         | •                          |                          |    |

|      |         | -                          | Mode                     |    |

|      |         |                            | ram Mode                 |    |

|      |         | 4.11.2.1.3 Active          | e Mode                   |    |

|      |         |                            |                          |    |

|      |         |                            |                          |    |

912-2000-010

**# 9004196 0000903 399 #**

|        | 4.11.2.2             | DMA Transfer Modes                                                                                 |                                                      | 102 |

|--------|----------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|

|        |                      | 4.11.2.2.1 Single Transi                                                                           | fer Mode                                             |     |

|        |                      | 4.11.2.2.2 Block Transfe                                                                           | er Mode                                              |     |

|        |                      | 4.11.2.2.3 Demand Trai                                                                             | nsfer Mode                                           |     |

|        |                      | 4.11.2.2.4 Cascade Mo                                                                              | de                                                   |     |

|        | 4.11.2.3             | Transfer Types                                                                                     |                                                      | 103 |

|        |                      | 4.11.2.3.1 Auto-initializa                                                                         | ation                                                | 104 |

|        |                      | 4.11.2.3.2 DREQ Priorit                                                                            | ty                                                   | 104 |

|        |                      | 4.11.2.3.3 Address Gen                                                                             | eration                                              | 104 |

|        |                      | 4.11.2.3.4 Compressed                                                                              | Timing                                               | 105 |

| 4.11.3 | DMA Re               | ister Descriptions                                                                                 |                                                      | 105 |

|        |                      |                                                                                                    | r                                                    |     |

|        |                      |                                                                                                    | ister                                                |     |

|        |                      |                                                                                                    |                                                      |     |

|        |                      |                                                                                                    | er                                                   |     |

|        |                      |                                                                                                    |                                                      |     |

|        |                      |                                                                                                    |                                                      |     |

|        |                      |                                                                                                    |                                                      |     |

|        |                      |                                                                                                    |                                                      |     |

|        |                      |                                                                                                    |                                                      |     |

|        |                      |                                                                                                    |                                                      |     |

| 4.11.4 | Special (            | commands                                                                                           |                                                      | 106 |

| 4.11.5 | Interrupt            | Controller Subsystem                                                                               |                                                      |     |

|        |                      |                                                                                                    | ystem Overview                                       |     |

|        |                      |                                                                                                    | ation                                                |     |

|        |                      |                                                                                                    |                                                      |     |

|        |                      |                                                                                                    |                                                      |     |

|        | 4.11.5.5             | Priority Assignment                                                                                |                                                      | 109 |

|        |                      |                                                                                                    | / Mode                                               |     |

|        |                      | 4.11.5.5.2 Specific Rota                                                                           | ation Mode                                           | 109 |

|        |                      | 4.11.5.5.3 Automatic Re                                                                            | otation Mode                                         |     |

|        | 4.11.5.6             | Programming the Interrup                                                                           | pt Controller                                        | 110 |

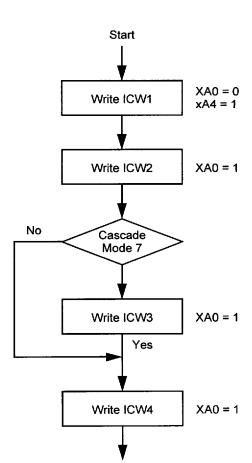

|        |                      | 4.11.5.6.1 Initialization                                                                          | Command Words (ICWs)                                 | 110 |

|        |                      |                                                                                                    | Command Words (OCWs)                                 |     |

|        |                      | 4.11.5.6.3 IRR, ISR, &                                                                             | Poll Vector                                          | 111 |

|        |                      |                                                                                                    |                                                      |     |

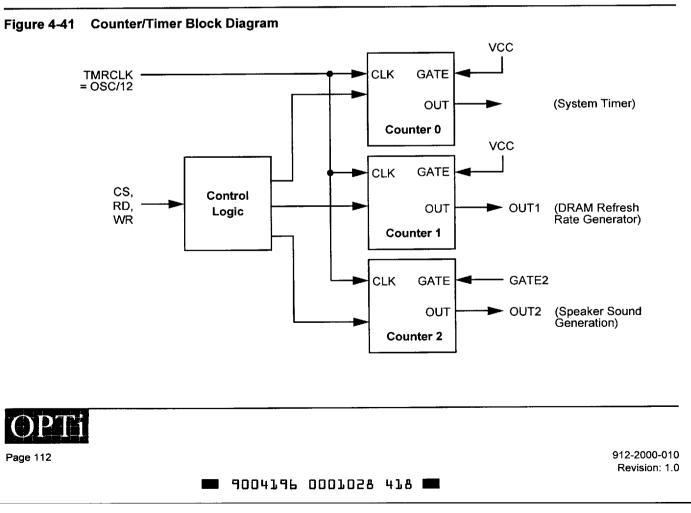

| 4.11.6 | Counter              | Timer Subsystem                                                                                    |                                                      |     |

| 4.11.6 | Counter,<br>4.11.6.1 | Timer Subsystem                                                                                    |                                                      |     |

| 4.11.6 | Counter,<br>4.11.6.1 | Counter Description<br>4.11.6.1.1 Programming                                                      | g the Counter/Timer                                  |     |

| 4.11.6 | Counter,<br>4.11.6.1 | Counter Description<br>4.11.6.1.1 Programmin<br>4.11.6.1.2 Read/Write (                            | g the Counter/Timer<br>Counter Command               |     |

| 4.11.6 | Counter,<br>4.11.6.1 | Counter Description<br>4.11.6.1.1 Programmin<br>4.11.6.1.2 Read/Write 0<br>4.11.6.1.3 Counter Late | g the Counter/Timer<br>Counter Command<br>ch Command |     |

| 4.11.6 | Counter,<br>4.11.6.1 | Counter Description<br>4.11.6.1.1 Programmin<br>4.11.6.1.2 Read/Write 0<br>4.11.6.1.3 Counter Late | g the Counter/Timer<br>Counter Command               |     |

Page vi

912-2000-010

**9**004196 0000904 225 **9**

OP

Page vii

### Table of Contents (cont.)

|                      |                                                                        | 4.11.6.2 Counter Operation                                                                                                                                                                                                                                      |                   |

|----------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                      |                                                                        | 4.11.6.2.1 Mode 0 - Interrupt on Terminal Count                                                                                                                                                                                                                 |                   |

|                      |                                                                        | 4.11.6.2.2 Mode 1 - Hardware Retriggerable One-Shot                                                                                                                                                                                                             |                   |

|                      |                                                                        | 4.11.6.2.3 Mode 2 - Rate Generator                                                                                                                                                                                                                              |                   |

|                      |                                                                        | 4.11.6.2.4 Mode 3 - Square Wave Generator                                                                                                                                                                                                                       |                   |

|                      |                                                                        | 4.11.6.2.5 Mode 4 - Software Triggered Strobe                                                                                                                                                                                                                   |                   |

|                      |                                                                        | 4.11.6.2.6 Mode 5 - Hardware Triggered Strobe<br>4.11.6.2.7 GATE2                                                                                                                                                                                               |                   |

| 4 4 2                | Bowor                                                                  | Management                                                                                                                                                                                                                                                      |                   |

| 4.12                 |                                                                        | -                                                                                                                                                                                                                                                               |                   |

|                      | 4.12.1                                                                 | Definition of Power Management Modes                                                                                                                                                                                                                            |                   |

|                      |                                                                        | 4.12.1.1 Normal Mode                                                                                                                                                                                                                                            |                   |

|                      |                                                                        | 4.12.1.3 SMI_GREEN Mode                                                                                                                                                                                                                                         |                   |

|                      | 4.12.2                                                                 | System Activity Detection                                                                                                                                                                                                                                       |                   |

|                      | 7.12.2                                                                 | 4.12.2.1 GREEN Events                                                                                                                                                                                                                                           |                   |

|                      |                                                                        | 4.12.2.2 Reload GET/Wake-up Events                                                                                                                                                                                                                              |                   |

|                      | 4.12.3                                                                 | System Management Interrupt (SMI)                                                                                                                                                                                                                               |                   |

|                      |                                                                        | 4.12.3.1 SMI Implementation                                                                                                                                                                                                                                     | 117               |

|                      |                                                                        |                                                                                                                                                                                                                                                                 |                   |

|                      | 4.12.4                                                                 | Hardware Power Management Support without an External Latch                                                                                                                                                                                                     | 117               |

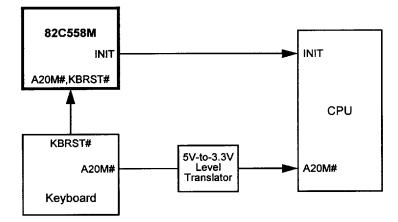

| 4.13                 |                                                                        | Hardware Power Management Support without an External Latch                                                                                                                                                                                                     |                   |

|                      | Fast G                                                                 |                                                                                                                                                                                                                                                                 | 118               |

| 4.14                 | Fast G/<br>Shadov                                                      | ATEA20 and Reset Emulation                                                                                                                                                                                                                                      | 118               |

| 4.14<br>4.15         | Fast G/<br>Shadov<br>Scatter                                           | ATEA20 and Reset Emulation<br>w ROM & BIOS Cacheability                                                                                                                                                                                                         | 118<br>119<br>119 |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F                                 | ATEA20 and Reset Emulation<br>w ROM & BIOS Cacheability                                                                                                                                                                                                         | 118<br>           |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F                                 | ATEA20 and Reset Emulation<br>w ROM & BIOS Cacheability<br>r/Gather<br>DMA                                                                                                                                                                                      | 118<br>119<br>    |

| 4.14                 | Fast G/<br>Shadov<br>Scatter<br>Type F<br>IDE Inte                     | ATEA20 and Reset Emulation<br>w ROM & BIOS Cacheability<br>r/Gather<br>DMA<br>erface                                                                                                                                                                            |                   |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F<br>IDE Inte<br>4.17.1           | ATEA20 and Reset Emulation<br>w ROM & BIOS Cacheability<br>r/Gather<br>DMA<br>erface<br>Overview                                                                                                                                                                |                   |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F<br>IDE Inte<br>4.17.1           | ATEA20 and Reset Emulation                                                                                                                                                                                                                                      |                   |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F<br>IDE Inte<br>4.17.1           | ATEA20 and Reset Emulation                                                                                                                                                                                                                                      |                   |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F<br>IDE Inte<br>4.17.1           | ATEA20 and Reset Emulation                                                                                                                                                                                                                                      |                   |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F<br>IDE Inte<br>4.17.1           | ATEA20 and Reset Emulation                                                                                                                                                                                                                                      |                   |

| 4.14<br>4.15<br>4.16 | Fast G/<br>Shadov<br>Scatter<br>Type F<br>IDE Inte<br>4.17.1<br>4.17.2 | ATEA20 and Reset Emulation<br>w ROM & BIOS Cacheability<br>r/Gather<br>DMA<br>erface<br>Overview<br>MIDE Register Descriptions<br>4.17.2.1 MIDE Configuration Registers<br>4.17.2.2 I/O Registers for Primary IDE<br>4.17.2.2.1 I/O Registers for Secondary IDE |                   |

912-2000-010

#### 9004196 0000905 161 🗰

|     |      | 4.17.4   | Programming the MIDE Module Registers                               | 136         |

|-----|------|----------|---------------------------------------------------------------------|-------------|

|     |      |          | 4.17.4.1 Standard Programming Sequence for Bus Mastering Operations |             |

|     |      |          | 4.17.4.2 Programming the IDE Mode Timing                            |             |

|     |      |          | 4.17.4.3 Programming the IDE Interrupt Routing                      | 136         |

|     | 4.18 | Special  | Cycles                                                              | 141         |

|     |      | 4.18.1   | System ROM BIOS Cycles                                              | <b>1</b> 41 |

|     |      | 4.18.2   | System Shutdown/Halt Cycles                                         | 141         |

| 5.0 | Regi | ister De | escriptions                                                         | 142         |

|     | 5.1  | 82C557   | M Register Space                                                    | 143         |

|     |      | 5.1.1    | 82C557M PCI Configuration Register Space                            | 143         |

|     |      | 5.1.2    | 82C557M System Control Register Space                               |             |

|     |      | 5.1.3    | 82C557M I/O Registers                                               | 166         |

|     | 5.2  | 82C558   | M Register Space                                                    |             |

|     |      | 5.2.1    | 82C558M PCI Configuration Register Space                            | 167         |

|     |      | 5.2.2    | 82C558M System Control Register Space                               | 170         |

|     |      | 5.2.3    | 82C558M I/O Registers                                               | 182         |

|     |      | 5.2.4    | 82C558M Internal Integrated 82C206 Register Descriptions            |             |

|     |      |          | 5.2.4.1 DMA Subsystem Registers                                     |             |

|     |      |          | 5.2.4.2 Interrupt Controller Subsystem                              |             |

|     |      |          | 5.2.4.3 Counter/Timer Subsystem                                     |             |

|     |      | 5.2.5    | 82C558M Power Management Registers                                  |             |

| 6.0 | Max  | imum F   | Ratings                                                             | 211         |

|     | 6.1  | Absolu   | te Maximum Ratings                                                  | 211         |

|     | 6.2  | DC Cha   | tracteristics: 5.0 Volt (VCC = 5.0V ±5%, TA = 0°C to +70°C)         | 211         |

|     | 6.3  | DC Cha   | rracteristics: 3.3 Volt (VDD = 3.3V ±5%, TA = 0°C to +70°C)         | 211         |

|     | 6.4  | 82C556   | M AC Characteristics (66MHz - Preliminary)                          | 212         |

|     | 6.5  | 82C557   | M AC Characteristics (66MHz - Preliminary)                          | 213         |

|     | 6.6  | 82C558   | M AC Characteristics (66MHz - Preliminary)                          | 215         |

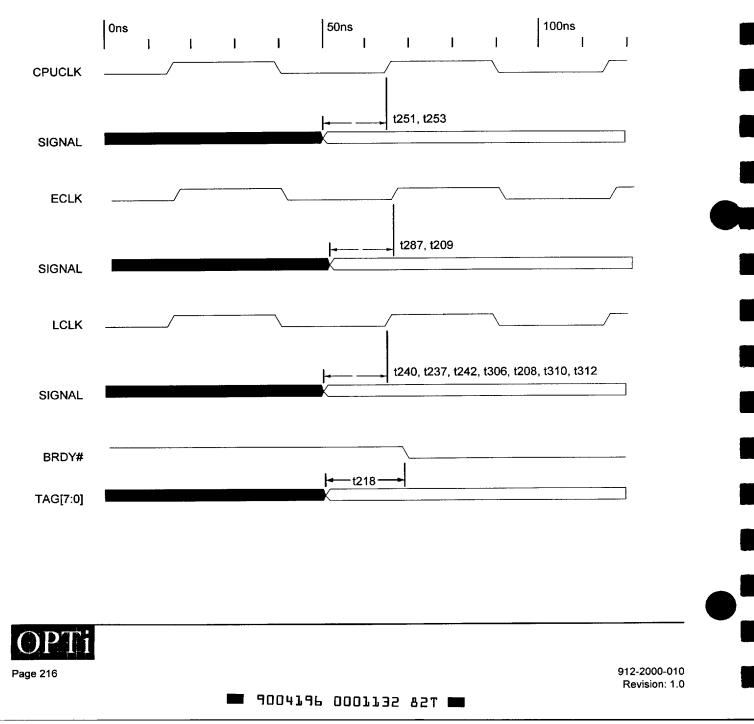

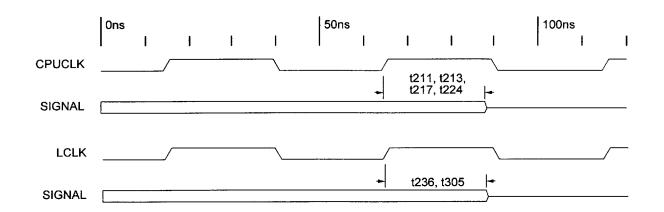

|     | 6.7  | AC Tim   | ing Diagrams                                                        | 216         |

Page viii

912-2000-010

90041960000906 OTA 🔳

| 7.0 | Tes | t Mode  | Information                                    | 219 |

|-----|-----|---------|------------------------------------------------|-----|

|     | 7.1 | 82C55   | 6M Testability                                 | 219 |

|     |     | 7.1.1   | 82C556M NAND Tree Test (Test Mode 1)           | 219 |

|     | 7.2 | 82C55   | 7M Testability                                 | 219 |

|     |     | 7.2.1   | 82C557M NAND Tree Test (Test Mode 1)           | 219 |

|     | 7.3 | 82C55   | 8M Testability                                 |     |

|     |     | 7.3.1   | 82C558M NAND Tree Test (Test Mode 1)           |     |

|     |     | 7.3.2   | Drive High/Drive Low Test (Test Modes 2 and 3) | 222 |

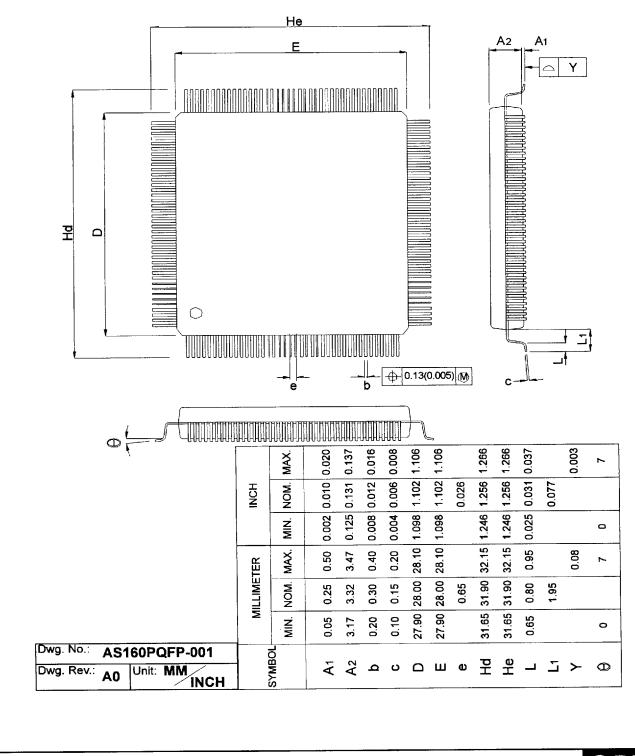

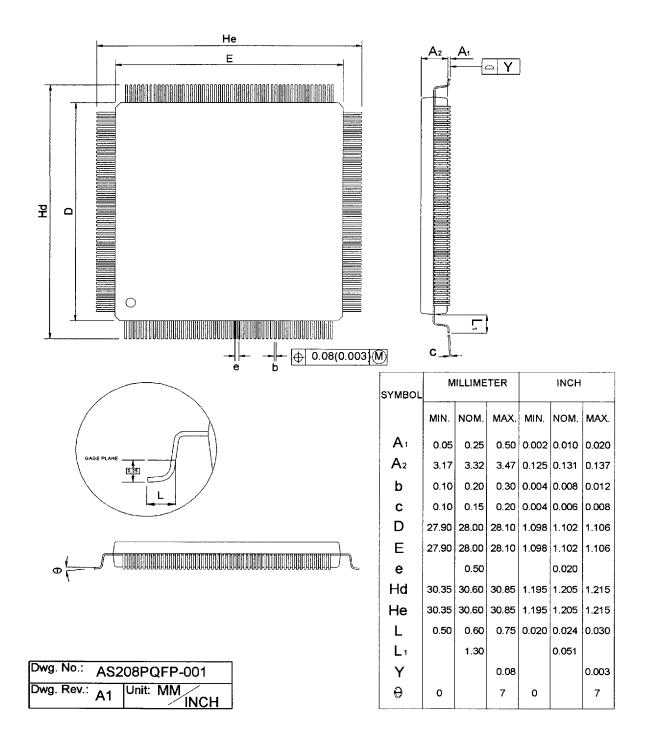

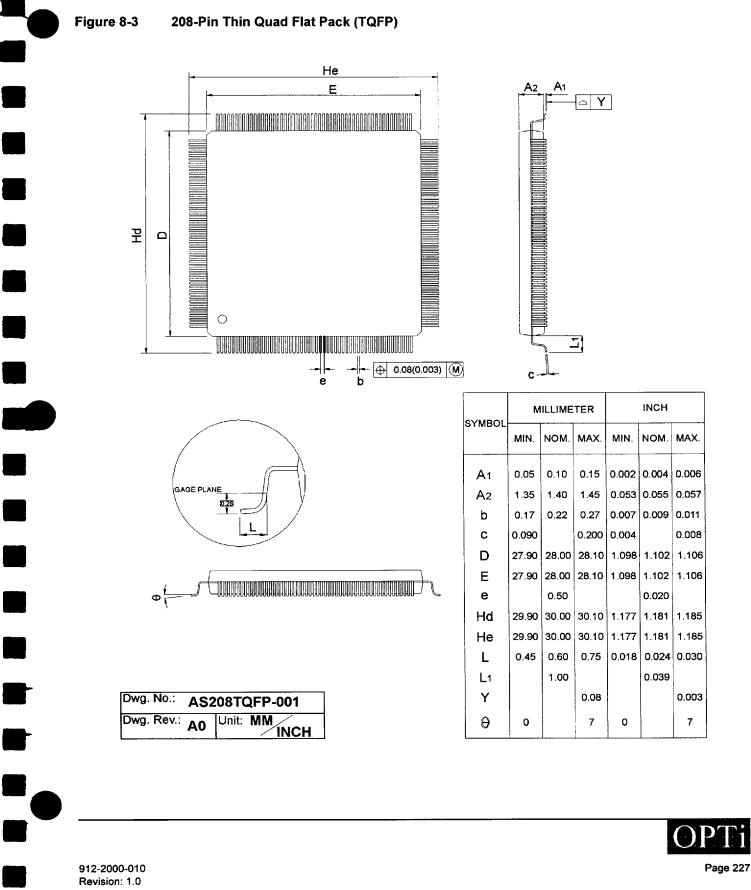

| 8.0 | Mec | chanica | al Package Outlines                            | 225 |

| A.0 | Acc | essing  | the BBS                                        | 229 |

|     | A.1 | Paging  | g the SYSOP                                    | 229 |

|     | A.2 | System  | m Requirements                                 | 229 |

|     | A.3 | Calling | g In/Hours of Operation                        | 229 |

|     | A.4 | Loggir  | ng On for the First Time                       | 229 |

|     | A.5 | Log Oi  | n Rules and Regulations                        | 229 |

|     | A.6 | Using   | the BBS                                        | 229 |

|     |     | A.6.2   | Sending/Receiving Messages                     | 230 |

|     |     | A.6.3   | Finding Information                            | 230 |

|     |     | A.6.4   | Downloading Files From OPTi                    | 230 |

|     |     | A.6.5   | Uploading Files To OPTi                        | 230 |

|     |     | A.6.6   | Logging Off                                    | 230 |

|     |     | A.6.7   | Logging Back on Again                          | 230 |

|     | A.7 | The M   | enus                                           | 230 |

|     |     | A.7.1   | Menu Selections                                | 231 |

|     |     |         |                                                |     |

912-2000-010 912-2000-010 Раде іх

# **List of Figures**

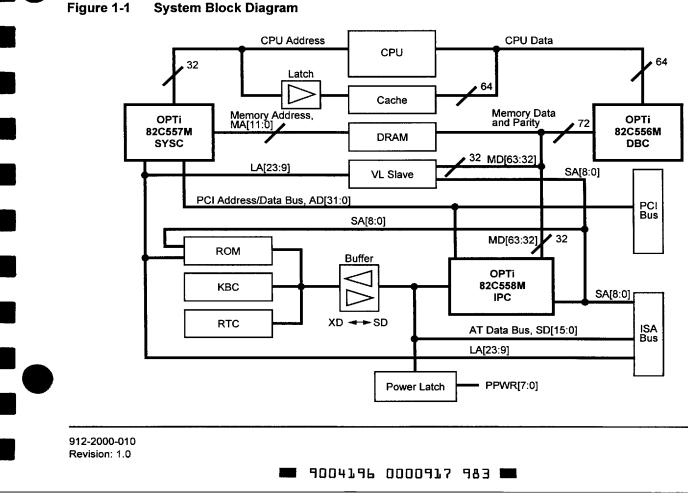

| Figure 1-1  | System Block Diagram                                                            | 1  |

|-------------|---------------------------------------------------------------------------------|----|

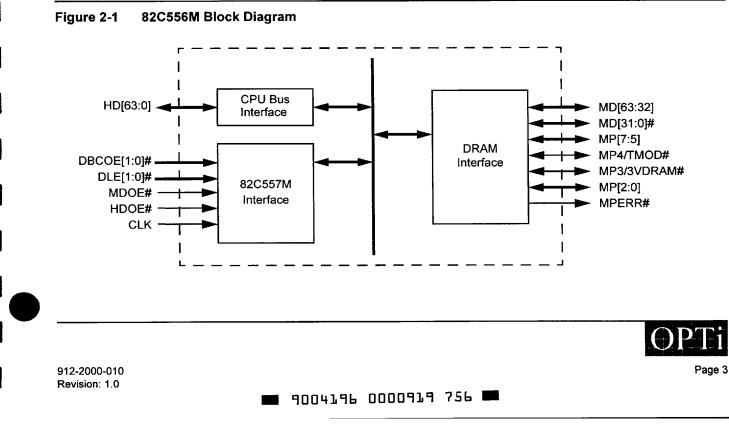

| Figure 2-1  | 82C556M Block Diagram                                                           | 3  |

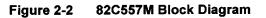

| Figure 2-2  | 82C557M Block Diagram                                                           | 4  |

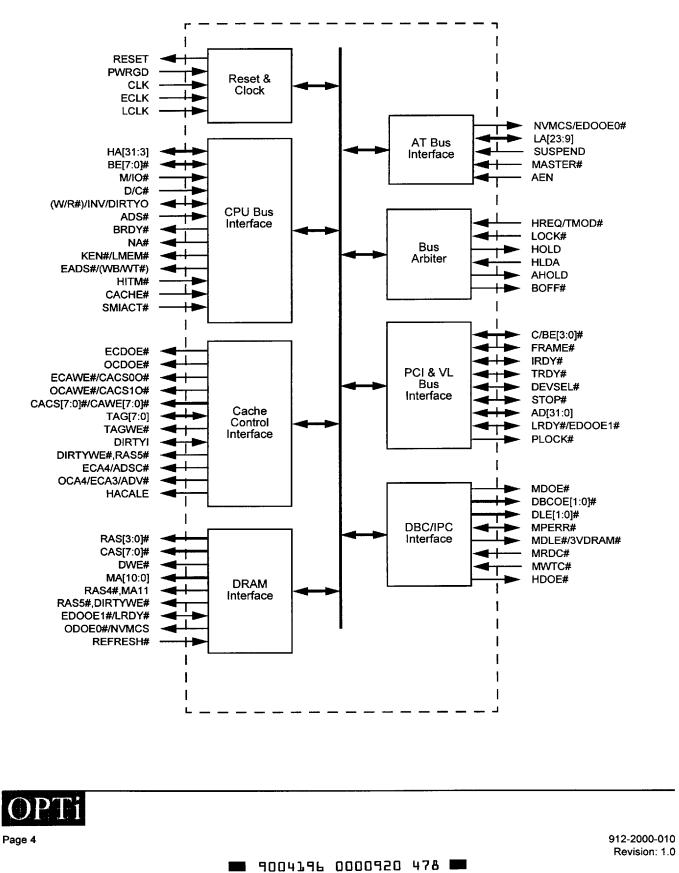

| Figure 2-3  | 82C558M Block Diagram                                                           | 5  |

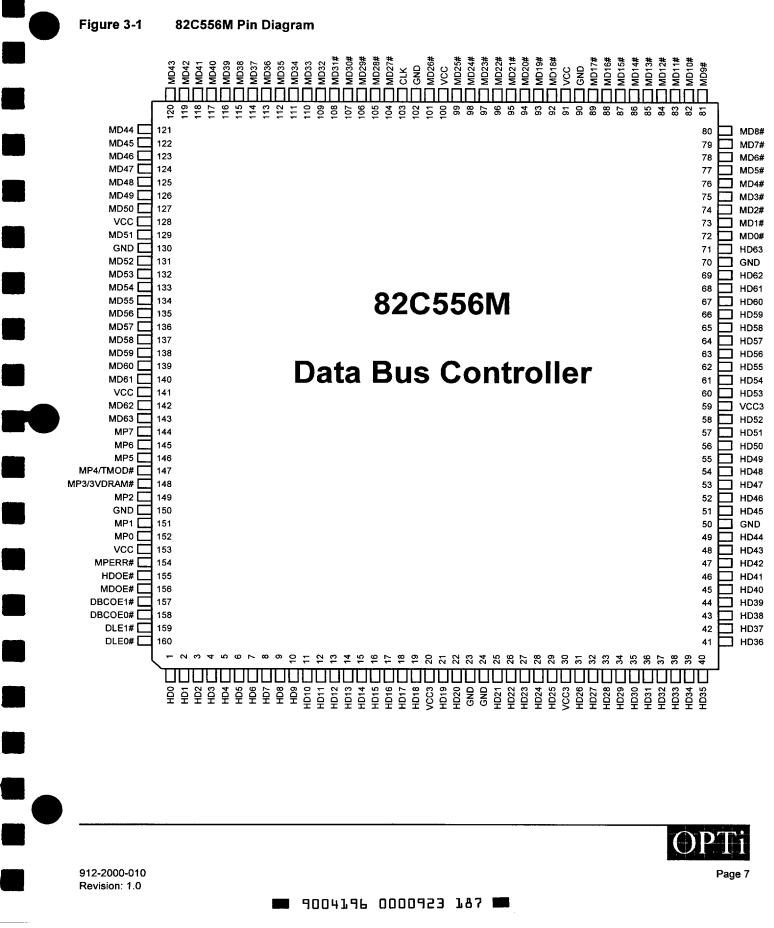

| Figure 3-1  | 82C556M Pin Diagram                                                             | 7  |

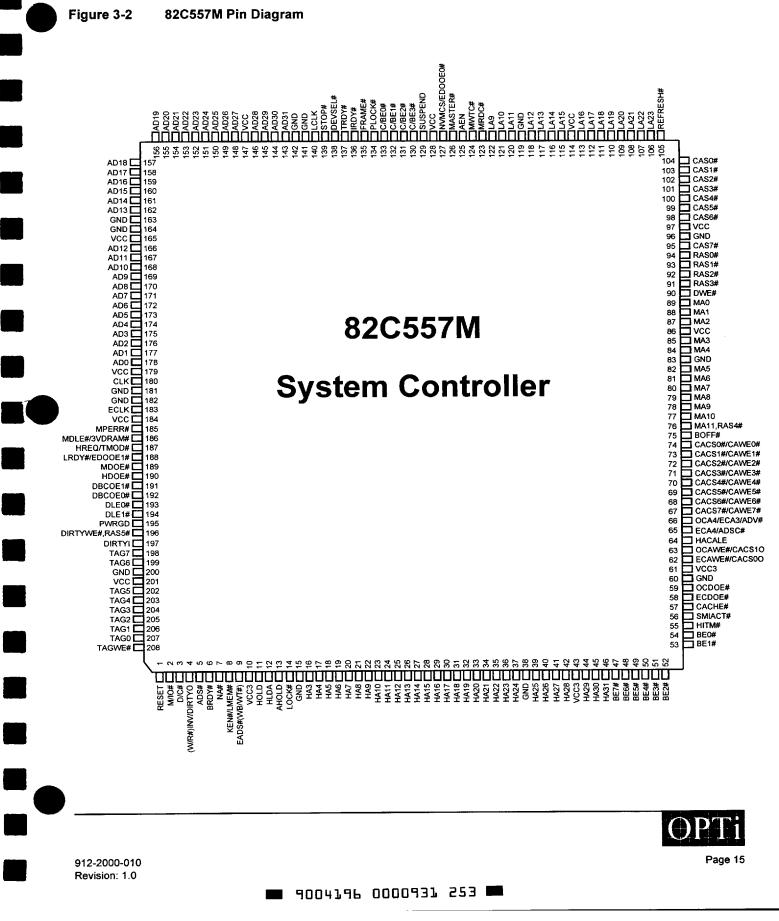

| Figure 3-2  | 82C557M Pin Diagram                                                             |    |

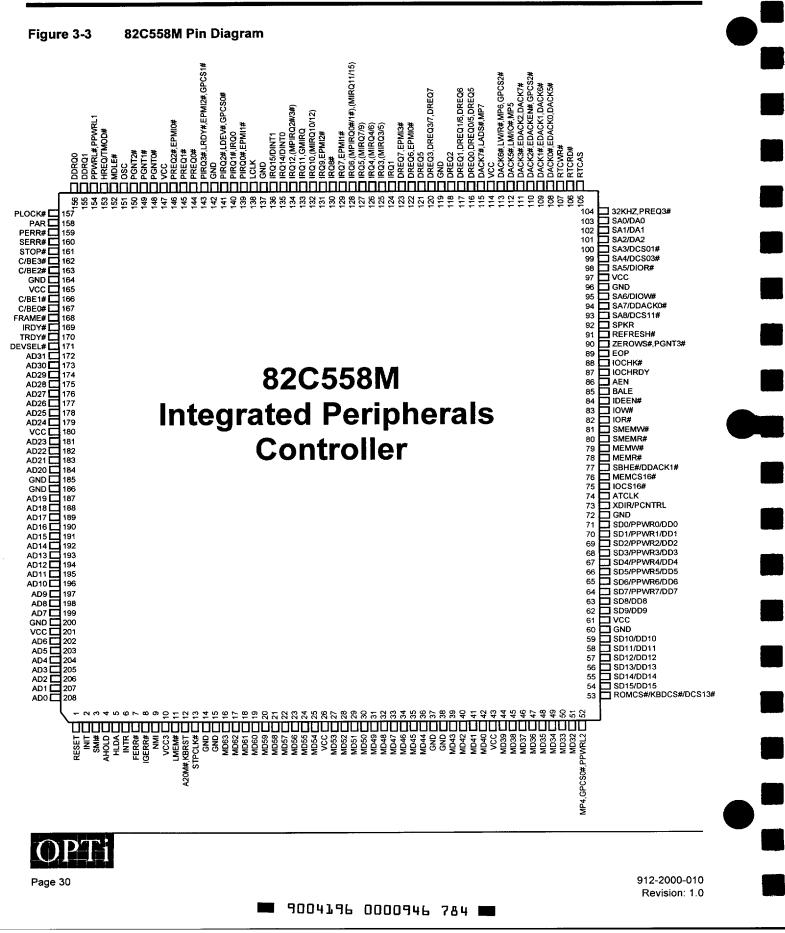

| Figure 3-3  | 82C558M Pin Diagram                                                             |    |

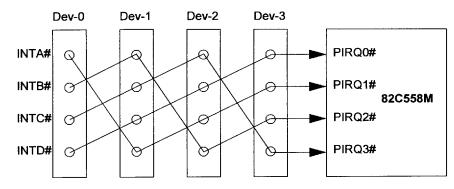

| Figure 3-4  | PCI Interrupts Mapping Matrix                                                   |    |

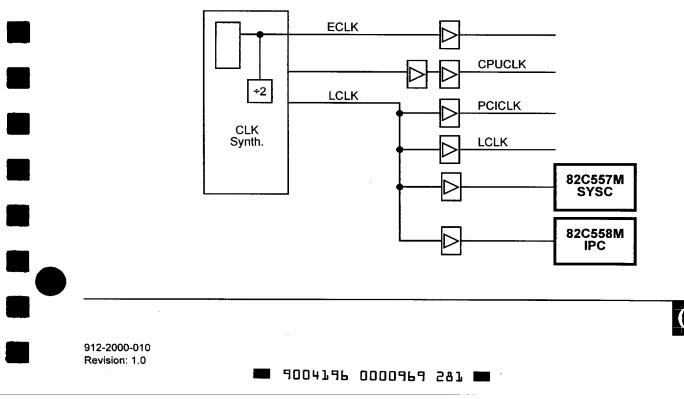

| Figure 4-1  | CPU and 82C557M Clock Distribution                                              |    |

| Figure 4-2  | Clock Distribution Method for VL Bus and PCI Connectors (Async. PCI and VL Bus) |    |

| Figure 4-3  | Clock Distribution Method for VL Bus and PCI Connectors (Sync. PCI and VL Bus)  |    |

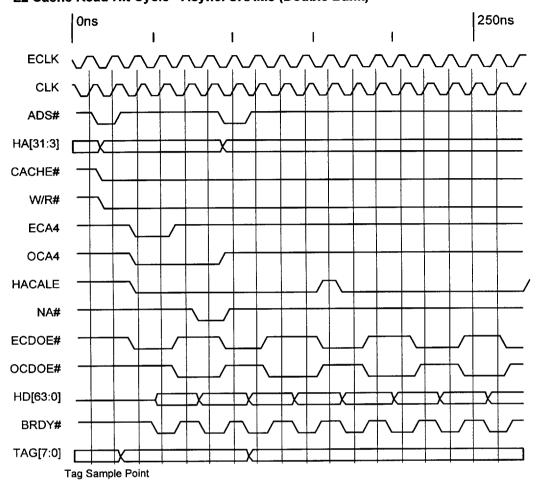

| Figure 4-4  | L2 Cache Read Hit Cycle - Async. SRAMs (Double Bank)                            |    |

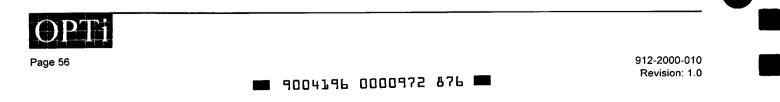

| Figure 4-5  | L2 Cache Read Hit Cycle - Sync. SRAMs                                           |    |

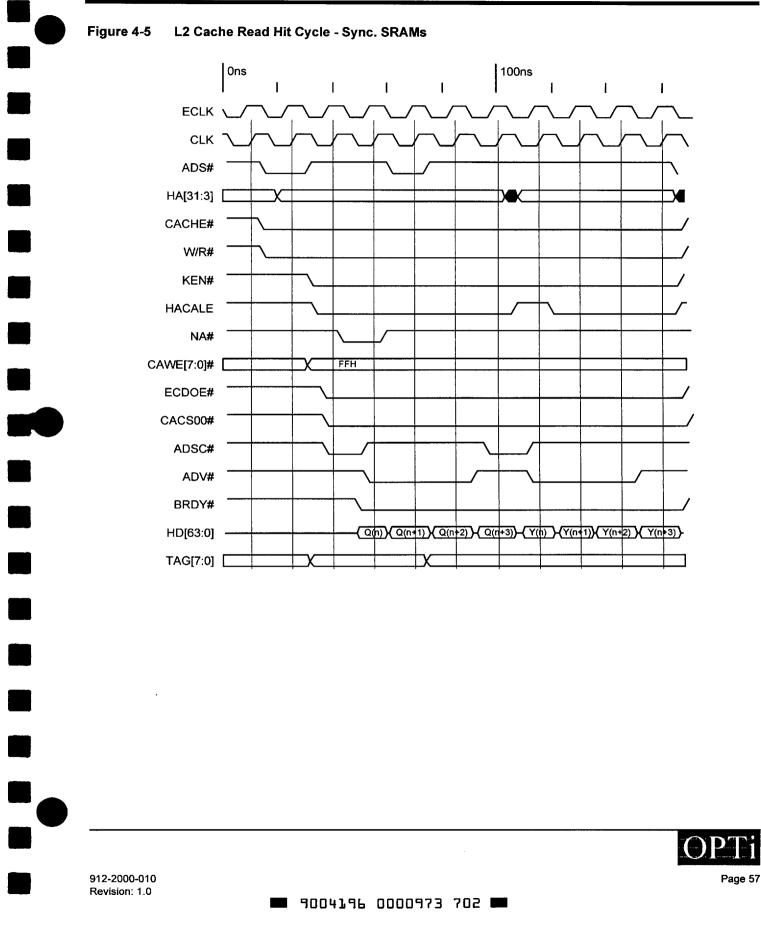

| Figure 4-6  | L2 Cache Read Hit Cycle Async. SRAMs (Single Bank)                              |    |

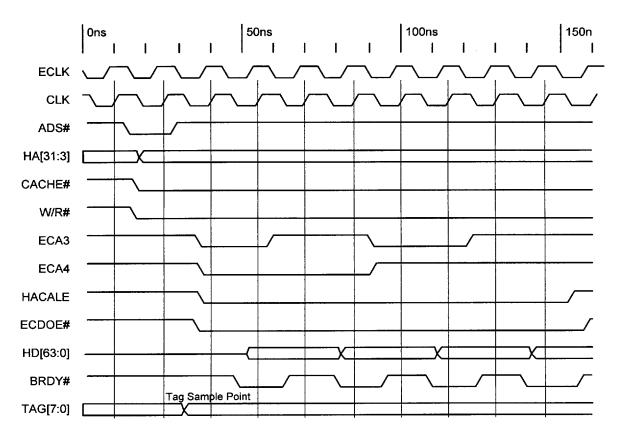

| Figure 4-7  | Write Hit Burst Cycle for Write-Back Mode - Async. SRAM (Double Bank)           |    |

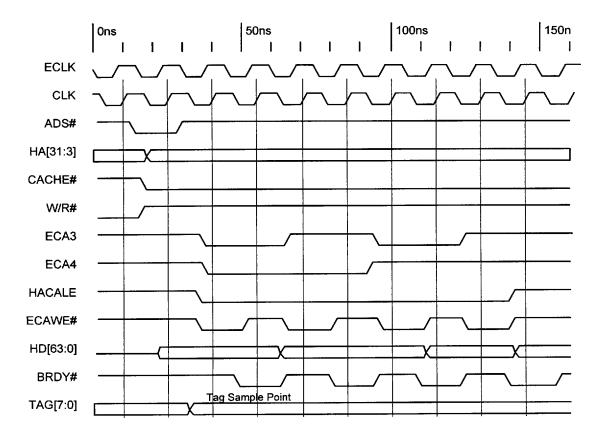

| Figure 4-8  | Write Hit Burst Cycle for Write-Back Mode (Single Bank) - Async. SRAM           | 60 |

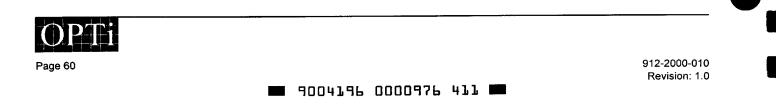

| Figure 4-9  | Write Hit Burst Cycle for Write-Back Mode - Sync. SRAM                          | 61 |

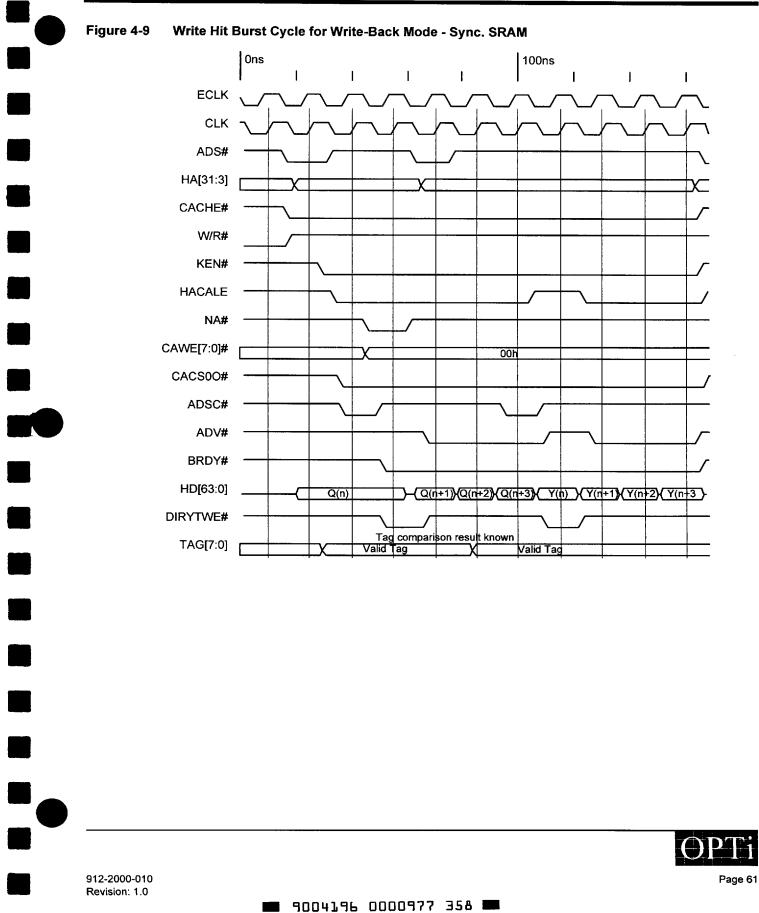

| Figure 4-10 | L2 Cache Read Miss Clean Burst of 8-3-3-3 (Linefill Cycle) - Async. SRAMs       | 63 |

| Figure 4-11 | L2 Cache Read Miss Clean Burst of 8-3-3-3 (Linefill Cycle) - Sync. SRAMs        | 64 |

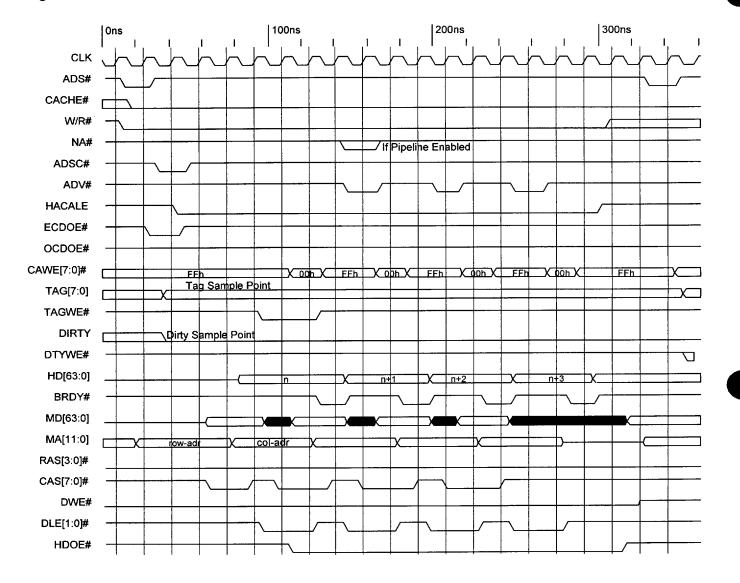

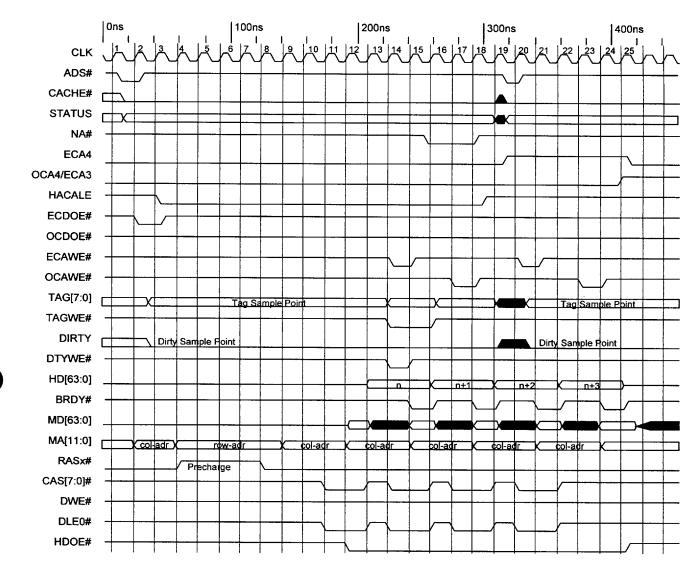

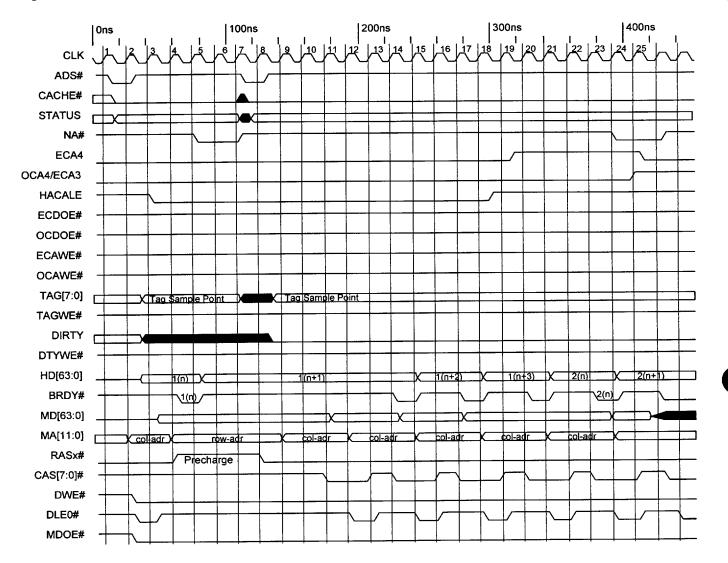

| Figure 4-12 | L2 Cache Read Miss Dirty Cycle - Async. SRAMs                                   | 65 |

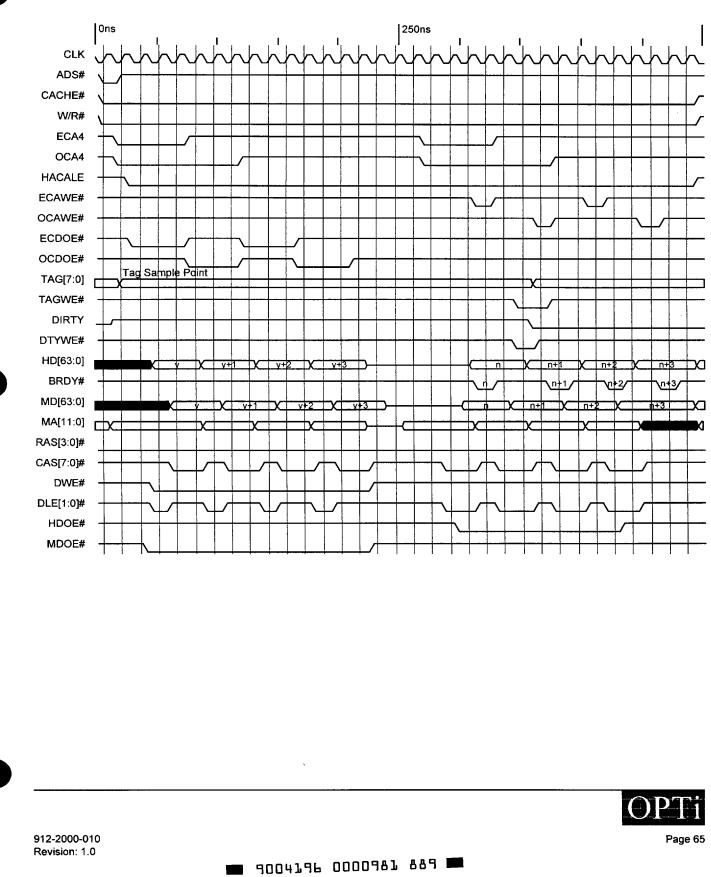

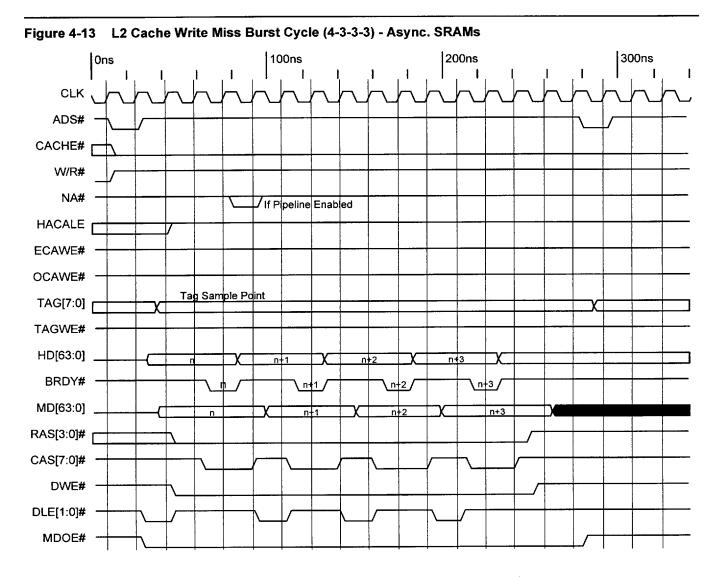

| Figure 4-13 | L2 Cache Write Miss Burst Cycle (4-3-3-3) - Async. SRAMs                        | 66 |

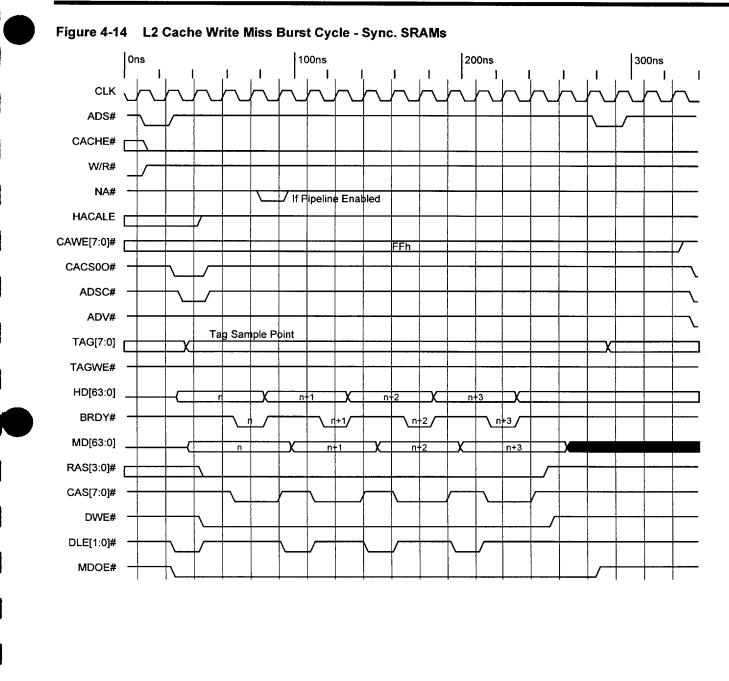

| Figure 4-14 | L2 Cache Write Miss Burst Cycle - Sync. SRAMs                                   | 67 |

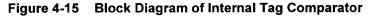

| Figure 4-15 | Block Diagram of Internal Tag Comparator                                        | 68 |

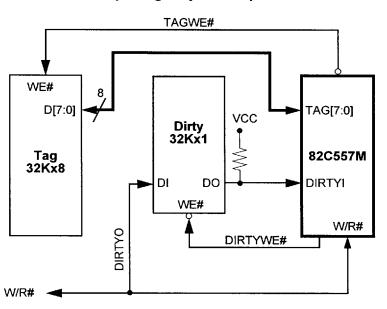

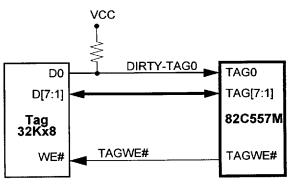

| Figure 4-16 | Separate 32Kx8 and 32Kx1 Split Tag/Dirty RAM Implementation                     | 69 |

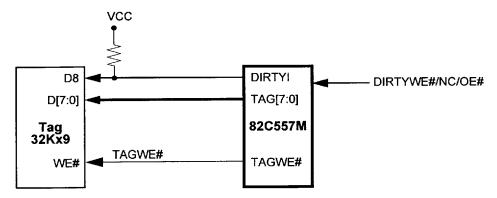

| Figure 4-17 | 32Kx9 Combined Tag/Dirty RAM Implementation                                     | 70 |

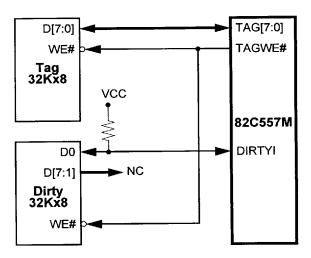

| Figure 4-18 | 32Kx8 Combined Tag/Dirty RAM Implementation                                     | 70 |

| Figure 4-19 | 32Kx8 and 32Kx8 Combined Tag/Dirty RAM Implementation (Separate Devices)        | 70 |

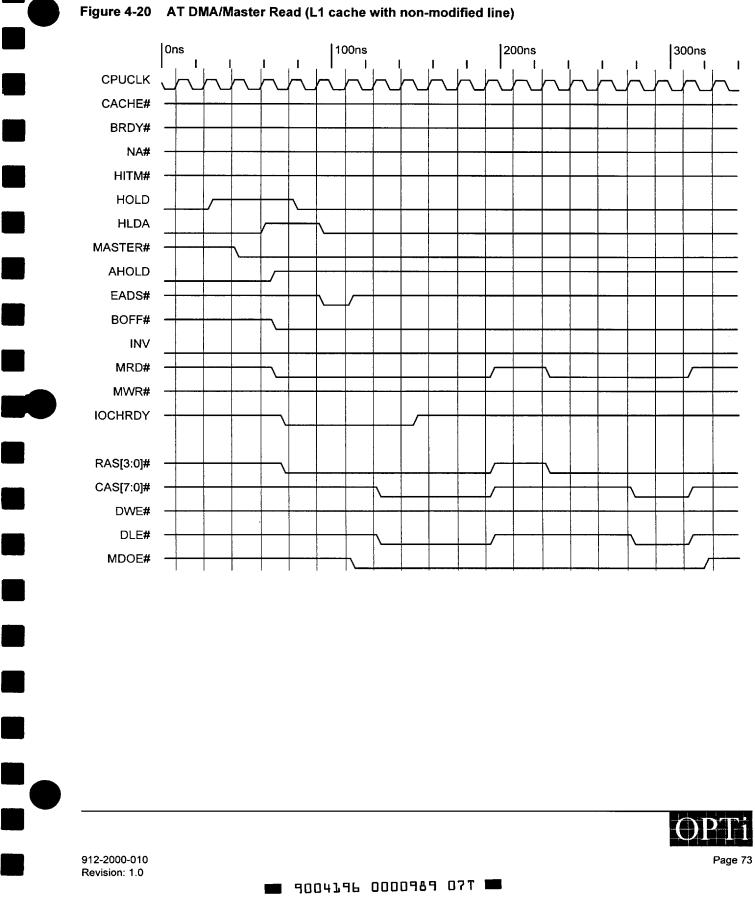

| Figure 4-20 | AT DMA/Master Read (L1 cache with non-modified line)                            | 73 |

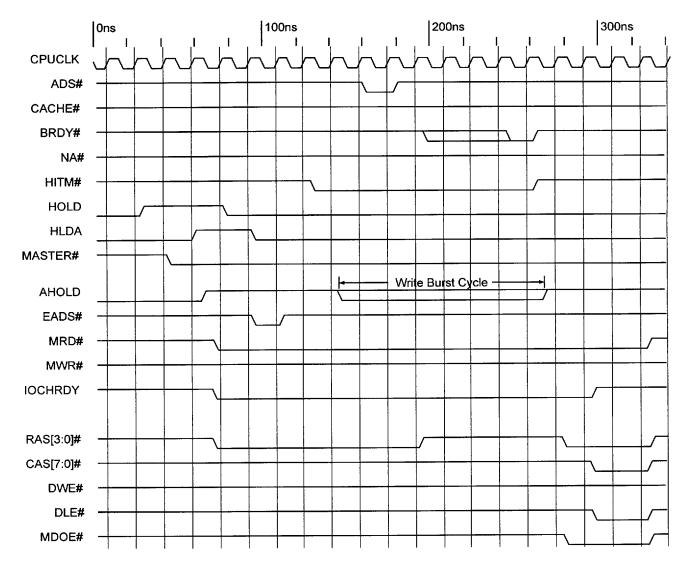

| Figure 4-21 | AT DMA/Master Read (L1 cache with modified line)                                | 74 |

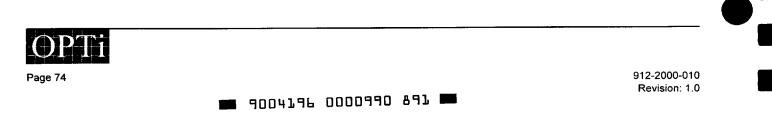

| Figure 4-22 | AT DMA/Master Write (L1 cache with modified line)                               | 75 |

| Figure 4-23 | DRAM Read Page Miss with RAS Active Read Cycle                                  | 83 |

| Figure 4-24 | DRAM Page Miss with RAS Active Write Cycle                                      |    |

|             |                                                                                 |    |

912-2000-010

#### 9004196 0000908 970 🔳

OP

Page xi

# List of Figures (cont.)

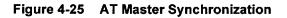

| Figure 4-25 | AT Master Synchronization                             |     |

|-------------|-------------------------------------------------------|-----|

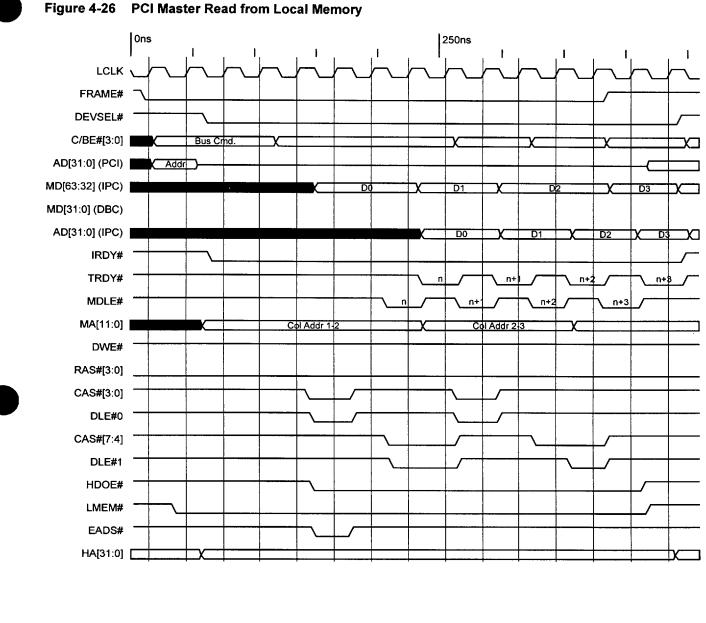

| Figure 4-26 | PCI Master Read from Local Memory                     |     |

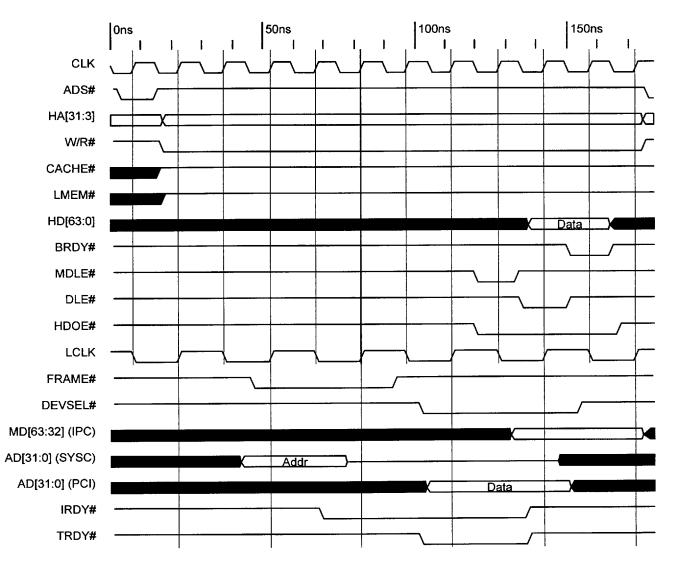

| Figure 4-27 | CPU Read from PCI, 32 Bits                            |     |

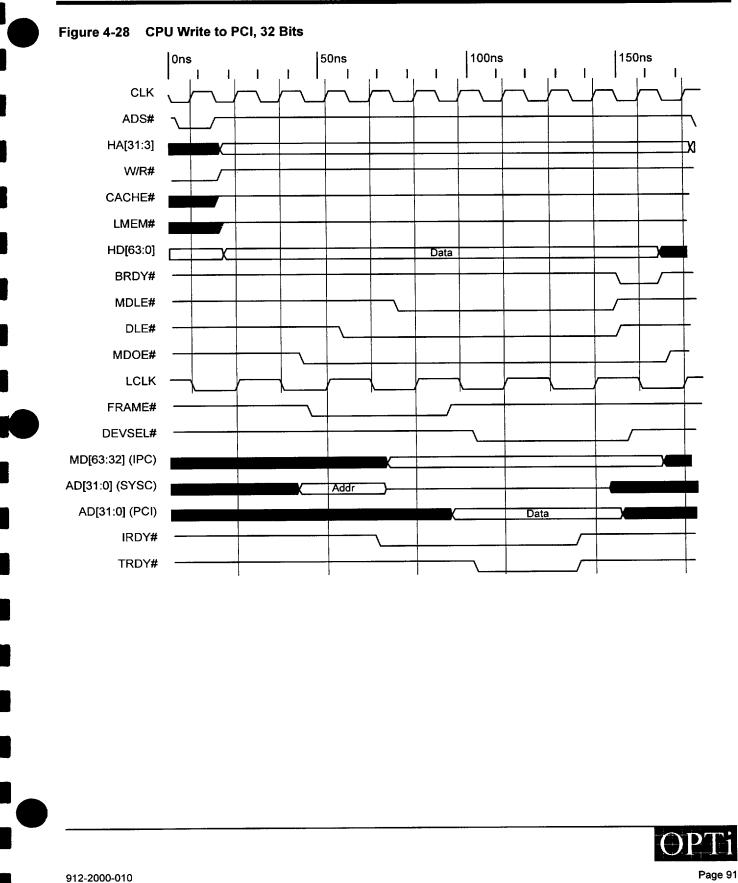

| Figure 4-28 | CPU Write to PCI, 32 Bits                             | 91  |

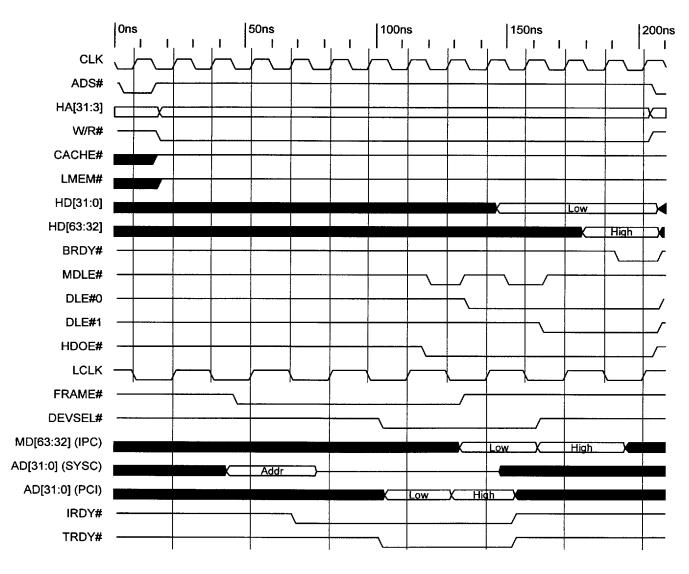

| Figure 4-29 | CPU Read from PCI, 64 Bits                            | 92  |

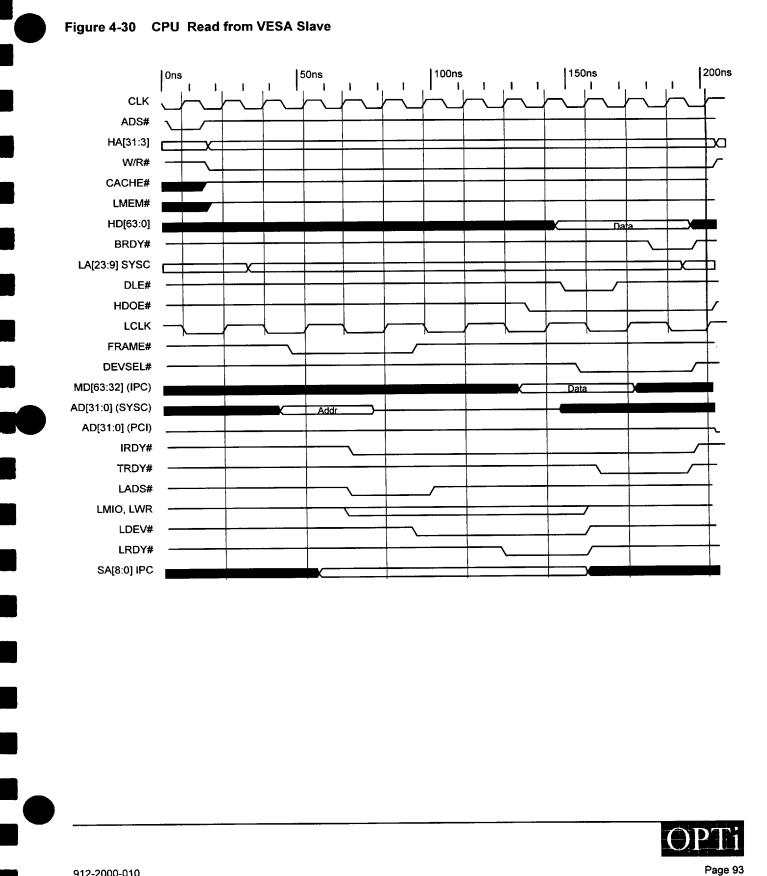

| Figure 4-30 | CPU Read from VESA Slave                              |     |

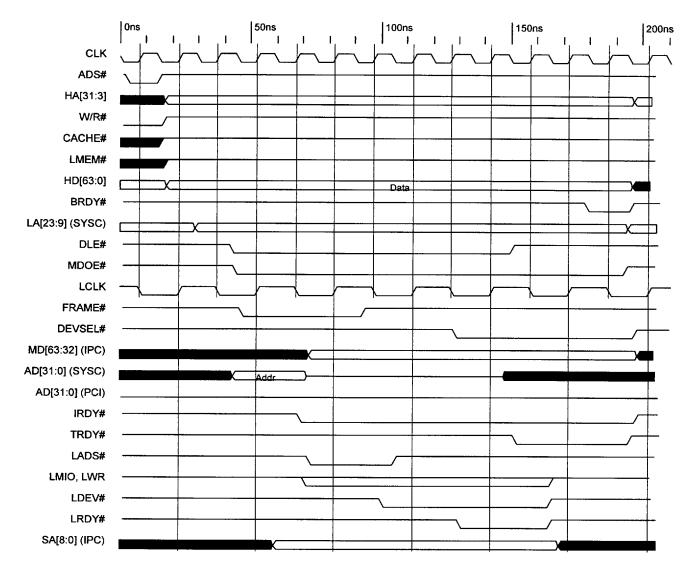

| Figure 4-31 | CPU Write to VESA Slave                               | 94  |

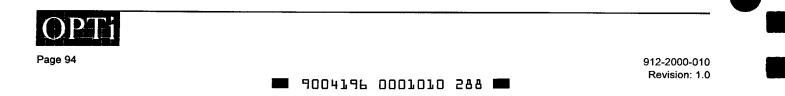

| Figure 4-32 | ISA Master Read from PCI                              |     |

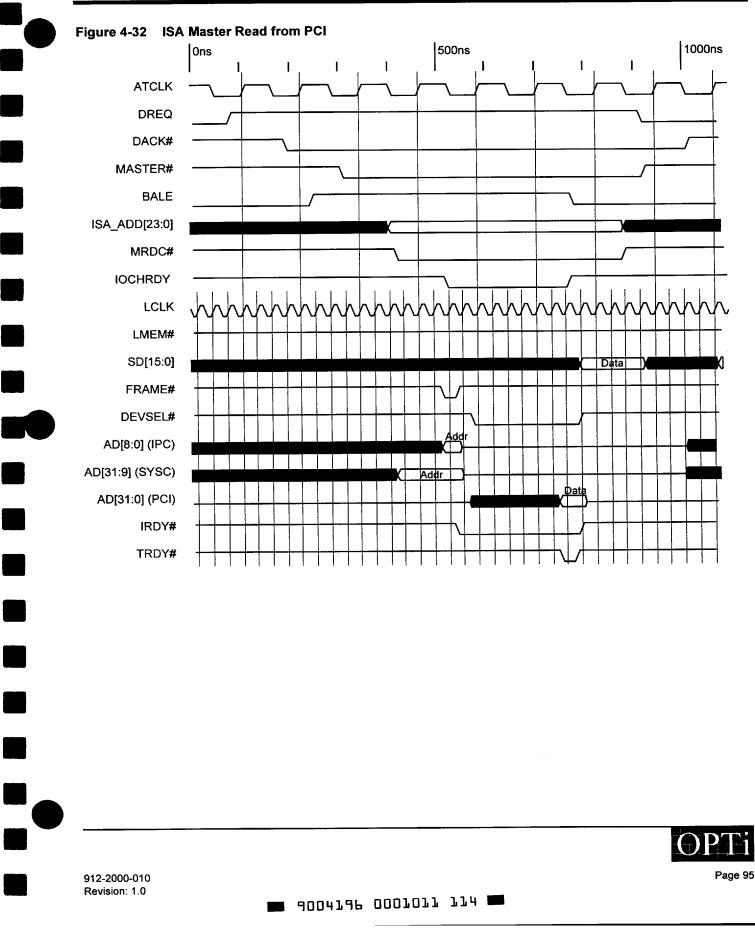

| Figure 4-33 | ISA Master Write to PCI                               |     |

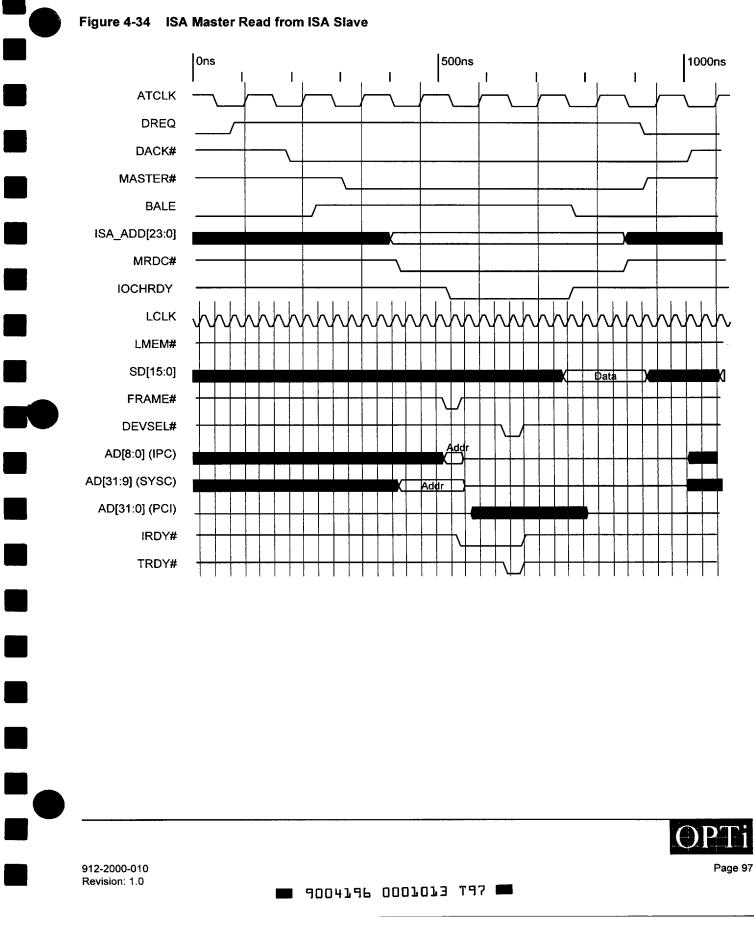

| Figure 4-34 | ISA Master Read from ISA Slave                        | 97  |

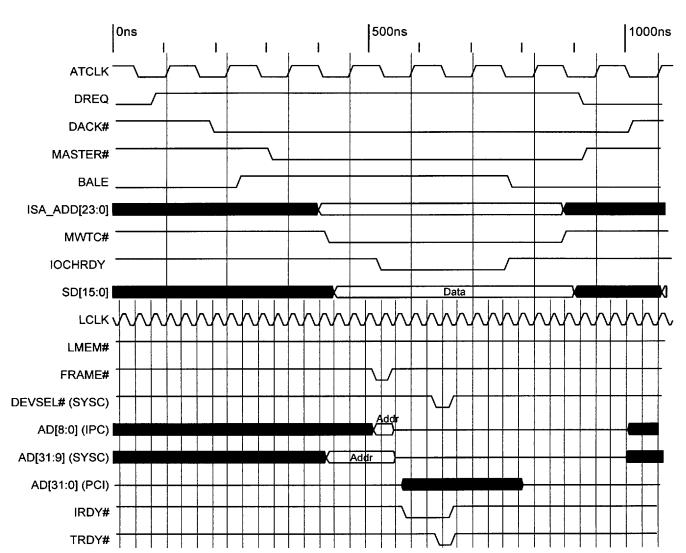

| Figure 4-35 | ISA Master Write to ISA Slave                         |     |

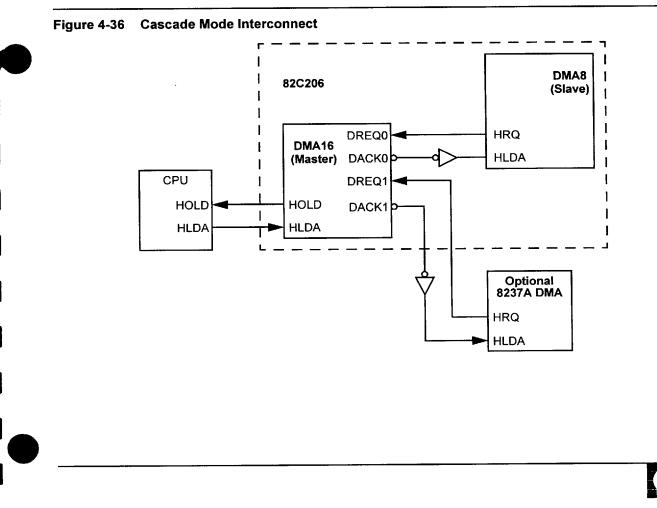

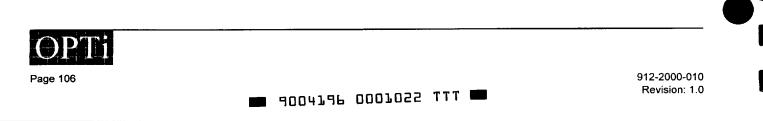

| Figure 4-36 | Cascade Mode Interconnect                             |     |

| Figure 4-37 | Internal Cascade Interconnect                         |     |

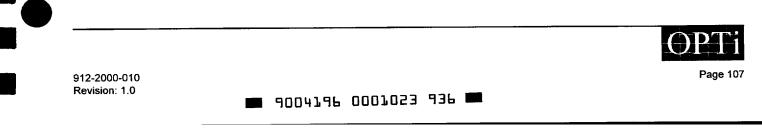

| Figure 4-38 | Interrupt Controller Block Diagram                    |     |

| Figure 4-39 | Interrupt Sequence                                    |     |

| Figure 4-40 | Initialization Sequence                               |     |

| Figure 4-41 | Counter/Timer Block Diagram                           | 112 |

| Figure 4-42 | Connections with Keyboard Emulation disabled          | 118 |

| Figure 4-43 | MIDE Interface Primary Channel Programming Flow Chart | 140 |

| Figure 6-1  | Setup Timing Waveform                                 | 216 |

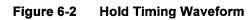

| Figure 6-2  | Hold Timing Waveform                                  | 217 |

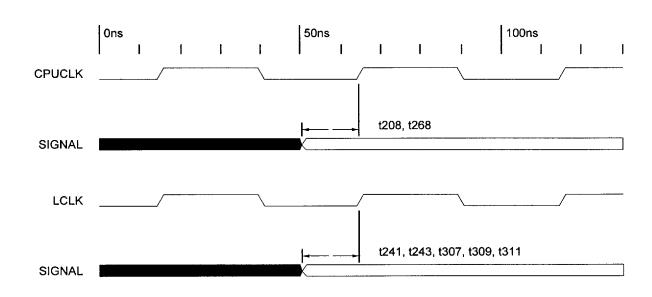

| Figure 6-3  | Output Delay Timing Waveform                          | 217 |

| Figure 6-4  | Float Delay Timing Waveform                           | 218 |

| Figure 8-1  | 160-Pin Plastic Quad Flat Pack (PQFP)                 | 225 |

| Figure 8-2  | 208-Pin Plastic Quad Flat Package (PQFP)              | 226 |

| Figure 8-3  | 208-Pin Thin Quad Flat Pack (TQFP)                    | 227 |

| Figure A-1  | The Main Menu                                         | 230 |

| Figure A-2  | The Bulletin Menu                                     |     |

| Figure A-3  | The File Menu                                         |     |

| Figure A-4  | The Message Menu                                      | 231 |

# **List of Tables**

| Table 3-1  | 82C556M 160-Pin Numerical Pin Cross-Reference List       | 8  |

|------------|----------------------------------------------------------|----|

| Table 3-2  | 82C556M 160-Pin Alphabetical Cross-Reference List        |    |

| Table 3-3  | 82C556M Strap Pin Mapping Functions                      |    |

| Table 3-4  | 82C556M Operating Voltage Groups                         | 13 |

| Table 3-5  | 82C556M Encoded Commands                                 | 14 |

| Table 3-6  | 82C557M Numerical Pin Cross-Reference List               | 16 |

| Table 3-7  | 82C557M Alphabetical Pin Cross-Reference List            | 18 |

| Table 3-8  | 82C557M Multiplexed Function Pins                        |    |

| Table 3-9  | 82C557M Strap Function Pins                              |    |

| Table 3-10 | 82C557M System Operating Voltage Groups                  | 29 |

| Table 3-11 | 82C558M Numerical Pin Cross-Reference List               | 31 |

| Table 3-12 | 82C558M Alphabetical Pin Cross-Reference List            | 34 |

| Table 3-13 | 82C558M Strap Function Pins                              |    |

| Table 3-14 | 82C558M Multiplexed Function Pins                        | 49 |

| Table 3-15 | 82C558M Programmable Functions Pins                      | 50 |

| Table 3-16 | 82C558M Operating Voltage Groups                         |    |

| Table 4-1  | Burst Modes                                              | 54 |

| Table 4-2  | Tag Compare Table                                        | 68 |

| Table 4-3  | DMA/Master Read Cycle Summary                            | 72 |

| Table 4-4  | DMA/Master Write Cycle Summary                           | 72 |

| Table 4-5  | Cacheability Methods                                     | 76 |

| Table 4-6  | SRAM Requirements                                        | 77 |

| Table 4-7  | Signal Functionality for Synchronous SRAM Implementation | 77 |

| Table 4-8  | Data SRAM Asynchronous Configurations                    |    |

| Table 4-9  | Data SRAM (Asynchronous) and Tag SRAM Speed Requirements |    |

| Table 4-10 | Data SRAM (Synchronous) Configurations                   |    |

| Table 4-11 | Data SRAM (Synchronous) Speed Requirements               |    |

| Table 4-12 | Tag SRAM Speed Requirements for Synchronous SRAMs        |    |

| Table 4-13 | SRAM Comparisons                                         | 79 |

| Table 4-14 | DRAM Programmable Control                                |    |

| Table 4-15 | DRAM Timing Mode Summary                                 |    |

| Table 4-16 | DRAM Row/Column MA to Address Bit Map                    |    |

|            |                                                          |    |

912-2000-010

**9**004196 0000910 529 **55**

Page xiii

### List of Tables (cont.)

| Table 4-17 | DMA I/O Address Map                                           |     |

|------------|---------------------------------------------------------------|-----|

| Table 4-18 | Rotating Priority Scheme                                      | 104 |

| Table 4-19 | DMA Page Register I/O Address Map                             | 105 |

| Table 4-20 | Interrupt Request Source                                      | 107 |

| Table 4-21 | Interrupt Vector Byte                                         |     |

| Table 4-22 | Counter/Timer I/O Address Map                                 | 113 |

| Table 4-23 | GATE2 Pin Function                                            |     |

| Table 4-24 | Vendor ID Register - 01h-00h                                  |     |

| Table 4-25 | Device ID Register - 03h-02h                                  |     |

| Table 4-26 | Command Register - 05h-04h                                    |     |

| Table 4-27 | Status Register - 07h-06h                                     | 121 |

| Table 4-28 | Revision ID Register - 08h                                    |     |

| Table 4-29 | Class Code Register - 0Bh-09h                                 |     |

| Table 4-30 | Reserved Register - 0Dh-0Ch                                   |     |

| Table 4-31 | Header Type Register - 0Eh                                    |     |

| Table 4-32 | Built-In Self-Test Register - 0Fh                             |     |

| Table 4-33 | Command Block Base Address Register - 13h-10h (Primary IDE)   |     |

| Table 4-34 | Control Block Base Address Register - 17h-14h (Primary IDE)   |     |

| Table 4-35 | Command Block Base Address Register - 1Bh-18h (Secondary IDE) |     |

| Table 4-36 | Control Block Base Address Register - 1Fh-1Ch (Secondary IDE) |     |

| Table 4-37 | Bus Master IDE Base Address Register - 23h-20h                |     |

| Table 4-38 | Interrupt Line Register - 3Ch                                 |     |

| Table 4-39 | Interrupt Pin Register - 3Dh                                  |     |

| Table 4-40 | IDE Initialization Control Register - 42h-40h                 |     |

| Table 4-41 | IDE Enhanced Mode Register - 43h                              |     |

| Table 4-42 | Internal ID Register - 1F2h                                   |     |

| Table 4-43 | Read Cycle Timing Register-A - 1F0h, Index-0                  |     |

| Table 4-44 | Read Cycle Timing Register-B - 1F0h, Index-1                  |     |

| Table 4-45 | Write Cycle Timing Register-A - 1F1h, Index-0                 |     |

| Table 4-46 | Write Cycle Timing Register-B - 1F1h, Index-1                 |     |

| Table 4-47 | Control Register - 1F3h                                       |     |

| Table 4-48 | Strap Register - 1F5h                                         |     |

|            |                                                               |     |

Page xiv

912-2000-010

9004196 0000911465 📟

### List of Tables (cont.)

| Table 4-49 | Miscellaneous Register - 1F6h                                            |     |

|------------|--------------------------------------------------------------------------|-----|

| Table 4-50 | Internal ID Register - 172h                                              |     |

| Table 4-51 | Read Cycle Timing Register-A - 170h, Index-0                             |     |

| Table 4-52 | Read Cycle Timing Register-B - 170h, Index-1                             | 129 |

| Table 4-53 | Write Cycle Timing Register-A - 171h, Index-0                            |     |

| Table 4-54 | Write Cycle Timing Register-B - 171h, Index-1                            |     |

| Table 4-55 | Control Register - 173h                                                  |     |

| Table 4-56 | Strap Register - 175h                                                    |     |

| Table 4-57 | Miscellaneous Register - 176h                                            |     |

| Table 4-58 | Physical Region Descriptor Table Entry                                   |     |

| Table 4-59 | Bus Master IDE Registers                                                 |     |

| Table 4-60 | Bus Master IDE Command Register for Primary IDE - Base Address + 00h     |     |

| Table 4-61 | Bus Master IDE Status Register for Primary IDE - Base Address + 02h      |     |

| Table 4-62 | Descriptor Table Pointer Register for Primary IDE - Base Address + 04h   |     |

| Table 4-63 | Bus Master IDE Command Register for Secondary IDE - Base Address + 08h   |     |

| Table 4-64 | Bus Master IDE Status Register for Secondary IDE - Base Address + 0Ah    |     |

| Table 4-65 | Descriptor Table Pointer Register for Secondary IDE - Base Address + 0Ch | 135 |

| Table 4-66 | REGTIMx Programming Options                                              | 136 |

| Table 4-67 | 16-Bit Timing Parameters with PCI Bus @ 33MHz                            |     |

| Table 4-68 | 16-Bit Timing Parameters with PCI Bus @ 25MHz                            |     |

| Table 4-69 | IDE Interrupt Routing Chart                                              |     |

| Table 5-1  | Register Locations and Access Mechanisms Summary                         | 142 |

| Table 5-2  | 57VIN, 82C557M Vendor Identification Register - Address Offset 01h-00h   |     |

| Table 5-3  | 57DID, 82C557M Device Identification Register - Address Offset 03h-02h   | 143 |

| Table 5-4  | 57COM, 82C557M Command Register - Address Offset 05h-04h                 | 143 |

| Table 5-5  | 57STAT, 82C557M Status Register - Address Offset 07h-06h                 | 144 |

| Table 5-6  | 57REV, 82C557M Revision Identification Register - Address Offset 08h     |     |

| Table 5-7  | 57CLASS, 82C557M Class Code Register - Address Offset 0Bh-09h            |     |

| Table 5-8  | 57RESV1, 82C557M Reserved Register 1 - Address Offset 0Ch                |     |

| Table 5-9  | 57MLTMR, 82C557M Master Latency Timer Register - Address Offset 0Dh      |     |

| Table 5-10 | 57HEAD, 82C557M Header Type Register - Address Offset 0Eh                |     |

| Table 5-11 | 57BIST, 82C557M Built-In Self-Test Register, Address Offset 0Fh          |     |

| Table 5-12 | 57RESV2, 82C557M Reserved Register 2 - Address Offset 3Fh-10h            | 145 |

|            |                                                                          |     |

912-2000-010

🔳 9004196 0000912 3TI 🔳

Page xv

# List of Tables (cont.)

| Table 5-13 | 57MEMCTL, 82C557M Memory Control Register - Address Offset 43h-40h             | 145 |

|------------|--------------------------------------------------------------------------------|-----|

| Table 5-14 | 57DRCCTL, 82C557M DRAM Data Latching Control Register - Address Offset 47h-44h |     |

| Table 5-15 | Index 00h                                                                      |     |

| Table 5-16 | 57DRMCTL, 82C557M DRAM Control Register 1 - Index 01h                          |     |

| Table 5-17 | 57CHCTL1, 82C557M Cache Control Register 1 - Index 02h                         |     |

| Table 5-18 | 57CHCTL2, 82C557M Cache Control Register 2 - Index 03h                         |     |

| Table 5-19 | 57SHCTL1, 82C557M Shadow RAM Control Register 1 - Index 04h                    |     |

| Table 5-20 | 57SHCTL2, 82C557M Shadow RAM Control Register 2 - Index 05h                    |     |

| Table 5-21 | 57SHCTL3, 82C557M Shadow RAM Control Register 3 - Index 06h                    |     |

| Table 5-22 | 57TAGTST, 82C557M Tag Test Register - Index 07h                                |     |

| Table 5-23 | 57CPUCH, 82C557M CPU Cache Control Register - Index 08h                        |     |

| Table 5-24 | 57SYSMEM, 82C557M System Memory Function Register - Index 09h                  |     |

| Table 5-25 | 57DRAMA, 82C557M DRAM Hole A Address Decode Register 1 - Index 0Ah             |     |

| Table 5-26 | 57DRAMB, 82C557M DRAM Hole B Address Decode Register 2 - Index 0Bh             | 151 |

| Table 5-27 | 57EDMA, 82C557M Extended DMA Register - Index 0Ch                              | 151 |

| Table 5-28 | 57CLKCTL, 82C557M Clock Control Register - Index 0Dh                           | 152 |

| Table 5-29 | 57CYCTL1, 82C557M Cycle Control Register 1 - Index 0Eh                         |     |

| Table 5-30 | 57CYCTL2, 82C557M Cycle Control Register 2 - Index 0Fh                         | 153 |

| Table 5-31 | 57MISC1, 82C557M Miscellaneous Control Register 1 - Index 10h                  | 154 |

| Table 5-32 | 57MISC2, 82C557M Miscellaneous Control Register 2 - Index 11h                  | 155 |

| Table 5-33 | 57REFCTL - 82C557M Refresh Control Register - Index 12h                        | 156 |

| Table 5-34 | 57MEMDC1, 82C557M Memory Decode Control Register 1 - Index 13h                 | 156 |

| Table 5-35 | 57MEMDC2, 82C557M Memory Decode Control Register 2 - Index 14h                 | 157 |

| Table 5-36 | DRAM Configurations                                                            | 158 |

| Table 5-37 | 57PCICY1, 82C557M PCI Cycle Control Register 1 - Index 15h                     |     |

| Table 5-38 | 57DRTY - 82C557M Dirty/Tag RAM Control Register - Index 16h                    | 160 |

| Table 5-39 | 57PCICY2, 82C557M PCI Cycle Control Register 2 - Index 17h                     |     |

| Table 5-40 | 57TRICTL, 82C557M Tristate Control Register - Index 18h                        | 162 |

| Table 5-41 | 57MEMDC3, 82C557M Memory Decode Control Register 3 - Index 19h                 |     |

| Table 5-42 | 57SGCTL1, 82C557M Memory Shadow Control Register 1 - Index 1Ah                 |     |

| Table 5-43 | 57SGCTL2, 82C557M Memory Shadow Control Register 2 - Index 1Bh                 |     |

| Table 5-44 | 57EDOCTL, 82C557M EDO DRAM Control Register - Index 1Ch                        |     |

| Table 5-45 | 57RESV3, 82C557M Reserved Register 3 - Index 1Dh                               |     |

| Table 5-46 | 57BOFF, 82C557M BOFF# Control Register - Index 1Eh                             | 165 |

|            |                                                                                |     |

Page xvi

912-2000-010

#### 🖬 9004196 0000913 238 🖿

### List of Tables (cont.)

| Table 5-48       57         Table 5-49       58         Table 5-50       58         Table 5-51       58 | <ul> <li><sup>7</sup>RSVD1, 82C557M Reserved Register - Index 1Fh</li></ul>                                                                                                                                                                                                                                                        | 166<br>167<br>167<br>167<br>168<br>168 |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Table 5-49       58         Table 5-50       58         Table 5-51       58                             | BVIN, 82C558M Vendor Identification Register - Address Offset 01h-00h         BDID, 82C558M Device Identification Register - Address Offset 03h-02h         BCOM, 82C558M Command Register - Address Offset 05h-04h         BSTAT, 82C558M Status Register - Address Offset 07h-06h                                                | 167<br>167<br>167<br>168<br>168        |

| Table 5-50         58           Table 5-51         58                                                   | BDID, 82C558M Device Identification Register - Address Offset 03h-02h<br>BCOM, 82C558M Command Register - Address Offset 05h-04h<br>BSTAT, 82C558M Status Register - Address Offset 07h-06h<br>BREV, 82C558M Revision Identification Register - Address Offset 08h<br>BCLASS, 82C558M Class Code Register - Address Offset 08h-09h | 167<br>167<br>168<br>168               |

| Table 5-51 58                                                                                           | COM, 82C558M Command Register - Address Offset 05h-04h<br>STAT, 82C558M Status Register - Address Offset 07h-06h<br>REV, 82C558M Revision Identification Register - Address Offset 08h<br>CLASS, 82C558M Class Code Register - Address Offset 0Bh-09h                                                                              | 167<br>168<br>168                      |

| Table 5-52 58                                                                                           | BREV, 82C558M Revision Identification Register - Address Offset 08h<br>BCLASS, 82C558M Class Code Register - Address Offset 0Bh-09h                                                                                                                                                                                                | 168                                    |

|                                                                                                         | CLASS, 82C558M Class Code Register - Address Offset 0Bh-09h                                                                                                                                                                                                                                                                        |                                        |

| Table 5-53 58                                                                                           | -                                                                                                                                                                                                                                                                                                                                  | 168                                    |

| Table 5-54 58                                                                                           | RESV1_82C558M Reserved Register 1 - Address Offset 0Ch                                                                                                                                                                                                                                                                             |                                        |

| Table 5-55 58                                                                                           |                                                                                                                                                                                                                                                                                                                                    | 168                                    |

| Table 5-56 58                                                                                           | MLTMR, 82C558M Master Latency Timer Register - Address Offset 0Dh                                                                                                                                                                                                                                                                  | 168                                    |

| Table 5-57 58                                                                                           | 3HEAD, 82C558M Header Type Register - Address Offset 0Eh                                                                                                                                                                                                                                                                           | 169                                    |

| Table 5-58 58                                                                                           | BIST, 82C558M Built-In Self-Test Register - Address Offset 0Fh                                                                                                                                                                                                                                                                     | 169                                    |

| Table 5-59 58                                                                                           | RESV2, 82C558M Reserved Register 2- Address Offset 3Fh-10h                                                                                                                                                                                                                                                                         | 169                                    |

| Table 5-60 58                                                                                           | KBDCTL, 82C558M Keyboard Control Register - Address Offset 41h-40h                                                                                                                                                                                                                                                                 | 170                                    |

| Table 5-61 58                                                                                           | MISC1, 82C558M Miscellaneous Control Register 1 - Address Offset 43h-42h                                                                                                                                                                                                                                                           | 171                                    |

| Table 5-62 58                                                                                           | PINFU1, 82C558M Pin Functionality Register 1 - Address Offset 45h-44h                                                                                                                                                                                                                                                              | 172                                    |

| Table 5-63 58                                                                                           | CYCTL1, 82C558M Cycle Control Register 1 - Address Offset 47h-46h                                                                                                                                                                                                                                                                  | 174                                    |

| Table 5-64 58                                                                                           | PINFU2, 82C558M Pin Functionality Register 2 - Address Offset 49h-48h                                                                                                                                                                                                                                                              | 175                                    |

| Table 5-65 58                                                                                           | ROMCS, 82C558M ROMCS# Range Control Register - Address Offset 4Bh-4Ah                                                                                                                                                                                                                                                              | 176                                    |

| Table 5-66 58                                                                                           | RESV3, 82C558M Reserved Register 3 - Address Offset 4Dh-4Ch                                                                                                                                                                                                                                                                        | 176                                    |

| Table 5-67 58                                                                                           | MISC2, 82C558M Miscellaneous Control Register 2 - Address Offset 4Fh-4Eh                                                                                                                                                                                                                                                           | 177                                    |

| Table 5-68 58                                                                                           | 3TRIG, 82C558M Trigger Control Register - Address Offset 51h-50h                                                                                                                                                                                                                                                                   | 178                                    |

| Table 5-69 58                                                                                           | 3INTMCL, 82C558M Interrupt Multiplexing Control Register - Address Offset 53h-52h                                                                                                                                                                                                                                                  | 179                                    |

| Table 5-70 58                                                                                           | BDMACTL, 82C558M DMA Control Register - Address Offset 55h-54h                                                                                                                                                                                                                                                                     | 180                                    |

| Table 5-71 Pi                                                                                           | n Multiplexing Chart 1                                                                                                                                                                                                                                                                                                             | 180                                    |

| Table 5-72 Pi                                                                                           | n Multiplexing Chart 2                                                                                                                                                                                                                                                                                                             | 181                                    |

| Table 5-73 Pi                                                                                           | n Multiplexing Chart 3                                                                                                                                                                                                                                                                                                             | 181                                    |

| Table 5-74 Po                                                                                           | ort B Register - I/O Port 61h                                                                                                                                                                                                                                                                                                      | 182                                    |

| Table 5-75 PS                                                                                           | S/2 Reset Control - Port 92h                                                                                                                                                                                                                                                                                                       | 182                                    |

| Table 5-76 DI                                                                                           | MA System I/O Register - Address 40Bh                                                                                                                                                                                                                                                                                              | 183                                    |

| Table 5-77 DI                                                                                           | MA System I/O Register - Address 483h-481h                                                                                                                                                                                                                                                                                         | 183                                    |

| Table 5-78 DI                                                                                           | MA System I/O Register - Address 48Bh-487h                                                                                                                                                                                                                                                                                         | 183                                    |

| Table 5-79 DI                                                                                           | MA System I/O Register - Address 4D6h                                                                                                                                                                                                                                                                                              | 183                                    |

| Table 5-80 Co                                                                                           | onfiguration Register (Index Port 022h, Data Port 023h) - Index: 01h                                                                                                                                                                                                                                                               | 184                                    |

🛲 9004196 0000914 174 🎟

Page xvii

### List of Tables (cont.)

| Table 5-81  | Command Register                                                | 185 |

|-------------|-----------------------------------------------------------------|-----|

| Table 5-82  | Mode Register                                                   | 185 |

| Table 5-83  | Request Register Write Format                                   |     |

| Table 5-84  | Request Register Read Format                                    |     |

| Table 5-85  | Request Mask Register Set/Reset Format                          | 186 |

| Table 5-86  | Request Mask Register Read/Write Format                         |     |

| Table 5-87  | Status Register                                                 |     |

| Table 5-88  | ICW1 Register - Address 020h (0A0h)                             |     |

| Table 5-89  | ICW2 Register - Address 021h (0A1h)                             |     |

| Table 5-90  | ICW3 Register - Format for INTC1 - Address 021h                 |     |

| Table 5-91  | ICW3 Register - Format for INCT1 - Address 0A1h                 |     |

| Table 5-92  | ICW4 Register - Address 021h (0A1h)                             | 188 |

| Table 5-93  | OCW1 Register - Address 021h (0A1h)                             | 188 |

| Table 5-94  | OCW2 Register - Address 020h (0A0h)                             |     |

| Table 5-95  | OCW3 Register - Address 020h (0A0h)                             | 189 |

| Table 5-96  | IIR Register - Address 020h (0A0h)                              | 189 |

| Table 5-97  | ISR Register - Address 020h (0A0h)                              | 189 |

| Table 5-98  | Poll Vector - Address 20h (0A0h)                                |     |

| Table 5-99  | Interrupt Controller Subsystem Shadow Registers                 |     |

| Table 5-100 | Control Word Format (Write Only) - Address 043h                 | 191 |

| Table 5-101 | Counter Latch Command Format (Write Only) - Address 043h        |     |

| Table 5-102 | Read-Back Command Format (Write Only) - Address 043h            |     |

| Table 5-103 | Status Format - Address 043h                                    | 192 |

| Table 5-104 | Counter 0 Count Value - Address 40h                             | 192 |

| Table 5-105 | Counter 1 Count Value - Address 41h                             | 192 |

| Table 5-106 | Counter 2 Count Value - Address 42h                             | 192 |

| Table 5-107 | Counter/Timer Subsystem Shadow Registers                        |     |

| Table 5-108 | 58GRNCTL, GREEN Mode Control/Enable Status - Index E0h          | 194 |

| Table 5-109 | 58GETCTL, EPMI Control / GREEN Event Timer - Index E1h Register |     |

| Table 5-110 | 58COUNT, GREEN Event Timer Initial Count Register - Index E2h   | 196 |

| Table 5-111 | 58IRQ1, IRQ Event Enable Register 1 - Index E3h                 | 196 |

| Table 5-112 | 58IRQ2, IRQ Event Enable Register 2 - Index E4h                 | 196 |

| Table 5-113 | 58DREQ, DREQ Event Enable Register - Index E5h                  | 196 |

| Table 5-114 | 58ACCDET, Device Cycle Monitor Enable Register - Index E6h      | 197 |

|             |                                                                 |     |

Page xviii

912-2000-010

🔳 9004196 0000915 000 🎟

OP

Page xix

## List of Tables (cont.)

| Table E 11E |                                                                              |     |