intel®

# 82350 EISA Chip Set

September 1992

# 82350 EISA CHIP SET CONTENTS PAGE EISA TERMINOLOGY 1-565 EISA System Introduction 1-565 82350 EISA Chip Set Highlights 1-565 EISA System Block Diagrams 1-566 MECHANICAL DATA 1-568 Package Information 1-568 Introduction 1-568

Package Thermal Specification ...... 1-571

#### **EISA TERMINOLOGY**

**ISA BUS—** The bus used in Industry Standard Architecture compatible computers. In the context of an EISA system, it refers to the ISA subset of the EISA bus.

**EISA BUS—** Extended ISA bus, a superset of the ISA bus. It includes all ISA bus features, along with extensions to enhance performance and capabilities.

**HOST CPU**— The main system processor, located on a separate Host Bus. This uses the EBC and other system board facilities to interface to the EISA bus.

CPU CYCLE— 386 CPU and/or the 82385 subsystem, or 80486 CPU is the master running the cycle.

**EISA MASTER**— A 16-bit or 32-bit bus master that uses the EISA signal set to generate memory or I/O cycles. The bus controller will convert the EISA control signals to ISA signals, when necessary.

ISA MASTER—A 16-bit bus master that uses the ISA subset of the EISA bus for generation of memory or I/O cycles. This device must understand 8-bit or 16-bit ISA slaves, and route data to the appropriate byte lanes. It is not required to handle any of the signals associated with the extended portion of the EISA bus.

**EISA SLAVE—** An 8-bit, 16-bit or 32-bit memory or I/O slave device that uses the extended signal set of the EISA bus to accept cycles from various masters. It returns information about its type and width using extended and ISA signals.

**ISA SLAVE**— A 16-bit or 8-bit slave that uses the ISA subset of the EISA bus to accept cycles from various masters. It returns ISA signals to indicate its type and width.

**DMA SLAVE—** An I/O device that uses the DMA signals (DREQ, DACK#) of the system board ISP to perform a direct memory access.

**ISACMD—** The ISA command signals (IORC#, IOWC#, MRDC#, MWTC#)

ASSEMBLY/DISASSEMBLY— This occurs when the master/slave data bus size are mismatched. The EBC runs multiple cycles to route bytes to the appropriate byte lanes (byte swapping). For example, if the 32-bit CPU is accessing an 8-bit slave, the EBC

will need to run four cycles to the 8-bit slave and route the bytes to appropriate byte lanes.

**CYCLE TRANSLATION**— This is performed by the EBC when the master and slave are on different busses (Host/EISA/ISA). The EBC will translate the master protocol to the slave protocol (Host master accessing EISA slave).

# **EISA System Introduction**

Extended Industry Standard Architecture (EISA) is a high performance 32-bit architecture based upon the Industry Standard Architecture (ISA) (PC AT\*). The wide acceptance of the 32-bit 386 microprocessor family has led to this interest in extending ISA to 32-bits. EISA's advanced capabilities and 32-bit architecture can unleash the full potential of the 386 and i486TM CPUs.

The EISA consortium has defined the EISA bus in response to the demand for a 32-bit high performance ISA compatible system. The open industry standard allows for industry wide participation, compatibility, and differentiation.

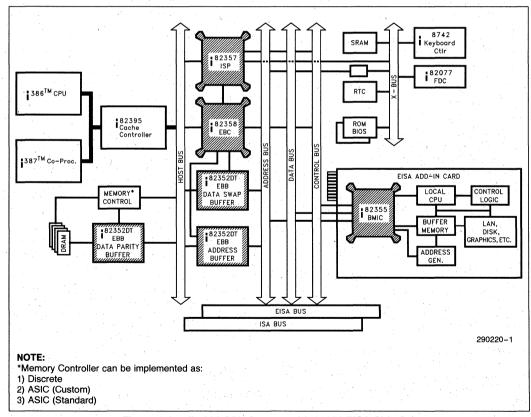

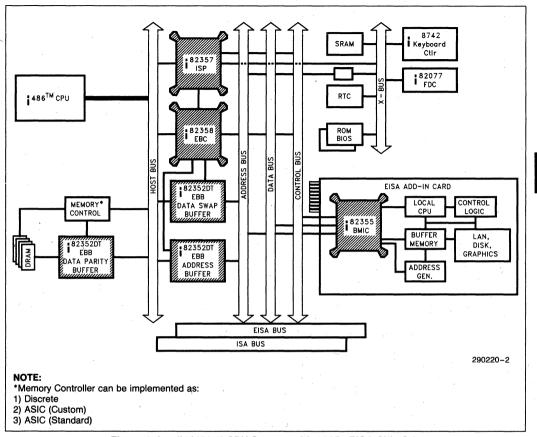

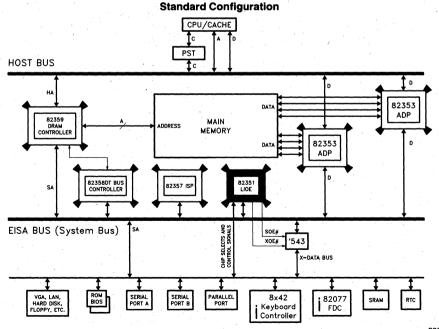

EISA brings advances in performance and convenience to the user. It provides 32-bit memory addressing and data transfers for CPU, DMA and bus masters allowing 33 Mbyte/second transfer rate for DMA and bus masters on the EISA bus. EISA provides a specification for auto-configuration of add-in cards that will eliminate the need for jumpers and switches on EISA cards. Interrupts are shareable and programmable. Figure 1 and 2 show the types of busses in an EISA system. A new bus-arbitration makes possible a new generation of intelligent bus master add-in cards that bring advanced applications to PCs.

Since the EISA system is 100% compatible with the ISA 8-bit and 16-bit expansion boards and software, ISA cards can be plugged into the EISA connector slots. The EISA slots can be defined as ISA or EISA for ease of compatibility during configuration. The EISA connector is a superset of the ISA connector maintaining full compatibility with ISA expansion cards and software. Simultaneous use of EISA and ISA add-in boards is available with automatic system and expansion board configuration.

# 82350 EISA Chip Set Highlights

The Intel 82350 EISA chip set is the industry's first 100% EISA/ISA compatible chip set. The 82350

Intel486 is a trademark of Intel Corporation.

\*PC AT is a trademark of International Business Machines Corporation.

EISA chip set supports the 33 MHz and 25 MHz 386 CPU or i486 CPU, 82385 Cache Controller, and optional 80387 numerics coprocessor. The EISA chip set includes three chips:

82352DT EISA Bus Buffers (EBB) (Optional)

82357 Integrated System Peripheral (ISP)

82358 EISA Bus Controller (EBC)

Information on the 82352DT EBB device is located in a separate data sheet.

The ISP performs the DMA functions of the system and is fully compatible with ISA functions. It integrates seven 32-bit DMA channels, five 16-bit timer/counters, two eight channel interrupt controllers, and provides for multiple NMI control and generation. It provides refresh address generation and keeps track of pending refresh requests when the bus is unavailable. The ISP supports multiple EISA bus masters while offering intelligent system arbiter services which grant the bus on a rotational basis.

The EBC is the EISA "engine". It is an intelligent bus controller that controls 8, 16 and 32-bit bus masters and slaves. It provides the state machine interface to Host, ISA and EISA busses and other IC's in the chip set. It offers a simple interface to the 386/i486 CPU and EISA bus. The EBC services as a bridge between the EISA and ISA devices. Data bus size mismatches are handled automatically by the EBC (including byte assembly and disassembly). It also guarantees cache operation on the Host, EISA, and ISA busses.

More information on EBC and ISP devices can be found in the data sheets in this document.

The 82355 Bus Master Interface Chip (BMIC) is a new device for add-in cards that takes advantage of the EISA bus master capabilities. Information on the 82355 BMIC is located in a separate data sheet.

Figure 1. Intel's 386 CPU System with 82350 EISA Chip Set

Figure 2. Intel's i486™ CPU System with 82350 EISA Chip Set

## **MECHANICAL DATA**

# **PACKAGING INFORMATION**

(See Packaging Spec. Order # 231369)

## Introduction

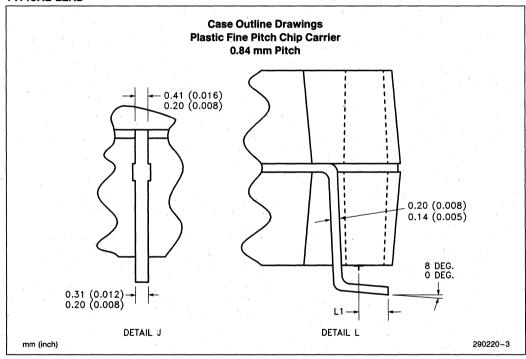

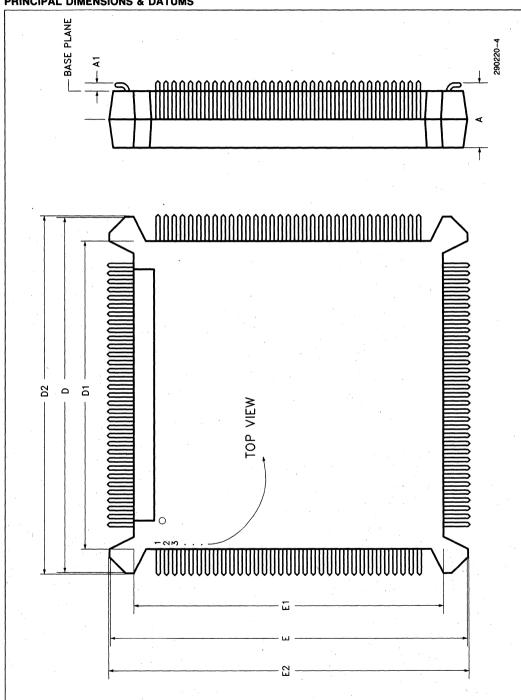

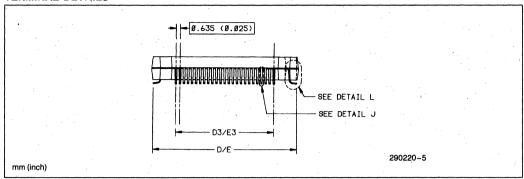

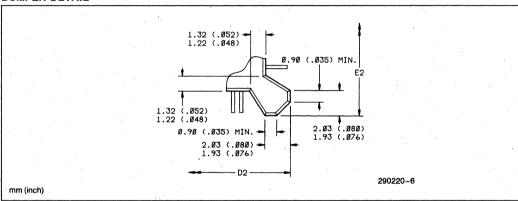

The individual components of Intel's EISA Chip Set come in JEDEC standard Gull Wing packages (25 MIL pitch), with "bumpers" on the corners for ease of handling. Please refer to the accompanying table for the package associated with each device, and to the individual component specifications for pinouts. (Note that the individual pinouts are numbered consistently with the numbering scheme depicted in the accompanying figures).

#### TYPICAL LEAD

| Symbol   | Description        | ir        | nch   | mm        |       |  |

|----------|--------------------|-----------|-------|-----------|-------|--|

| - Symbol | Description        | Min       | Max   | Min       | Max   |  |

| N        | Lead Count         | 132       |       | 132       |       |  |

| Α        | Package Height     | 0.160     | 0.170 | 4.06      | 4.32  |  |

| A1       | Standoff           | 0.020     | 0.030 | 0.51      | 0.76  |  |

| D, E     | Terminal Dimension | 1.075     | 1.085 | 27.31     | 27.56 |  |

| D1, E1   | Package Body       | 0.947     | 0.953 | 24.05     | 24.21 |  |

| D2, E2   | Bumper Distance    | 1.097     | 1.103 | 27.86     | 28.02 |  |

| D3, E3   | Lead Dimension     | 0.800 Ref |       | 20.32 Ref |       |  |

| L1       | Foot Length        | 0.020     | 0.030 | 0.51      | 0.76  |  |

## PRINCIPAL DIMENSIONS & DATUMS

# **TERMINAL DETAILS**

# **BUMPER DETAIL**

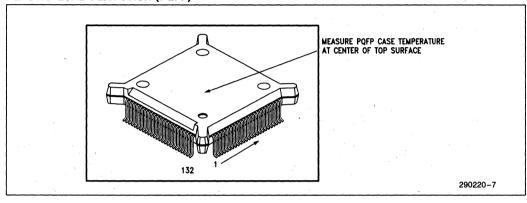

# **Package Thermal Specification**

The 82357 ISP and 82358 EBC are specified for operation when the case temperature is within the range of 0°C to 85°C. The case temperature may be measured in any environment, to determine whether the device is within the specified operating range.

The PQFP case temperature should be measured at the center of the top surface opposite the pins, as shown in the figure below.

#### PLASTIC QUAD FLAT PACK (PQFP)

Table 2. 82357 ISP and 82358 DT EBC PQFP Package Thermal Characteristics

| Thermal Resistance— °C/Watt |                        |    |      |      |      |     |     |  |  |  |

|-----------------------------|------------------------|----|------|------|------|-----|-----|--|--|--|

| Parameter                   | Air Flow Rate (ft/min) |    |      |      |      |     |     |  |  |  |

| , arameter                  | 0                      | 50 | 100  | 200  | 400  | 600 | 800 |  |  |  |

| heta Junction—Case          | 7                      | 7  | 7    | 7    | 7    | . 7 | 7   |  |  |  |

| $\theta$ Case to Ambient    | 22                     | 21 | 19.5 | 17.5 | 14.5 | 12  | 10  |  |  |  |

#### NOTES:

1. Table 2 applies to the PQFP device plugged into a socket or soldered directly into the board. 2.  $\theta_{JA} = \theta_{JC} + \theta_{CA}$ .

# PROCESS NAME:

1.2µ CHMOS III P-well

## ICC AT HOT WITH NO RESISTIVE LOADS:

150 mA Max at 85°C.

# 82351 LOCAL I/O EISA SUPPORT PERIPHERAL (LIO.E)

- EISA and PC/AT System Fully Compatible Local I/O Controller

- Integrates:

- Local I/O Address Decoder

- EISA System Configuration Registers

- Fast CPU Reset and A20 Gate Port (92h)

- Two External Serial I/O Controller Interfaces with Four Assignable Interrupts Generation

- External Real Time Clock Interface

- External EISA Configuration RAM Interface

- Parallel Port Interface

- i486 and 386 CPU Compatible Numeric Co-Processor Interface

- External Floppy Disk Controller Interface

- External Keyboard (8x42) Controller Interface including Interrupt Generation

- EISA System ID Register

- Fast A20GATE, CPU RESET, and FLUSH# Generation by Snooping Keyboard Controller Commands

- Four Programmable General Purpose Chip Selects for Additional Local I/O Devices

- Provides I/O Address Decode and Commands

- Provides I/O Data Bus Buffer Control

- EPROM or FLASH EPROM BIOS ROM Interface (BIOS ROM Address is Externally Decoded)

- Edge or Level Sensitive Triggered Interrupt Generation Selection

- 132 Pin PQFP Package

(See Packaging Specification Order Number 240800, Package Type KD)

Figure 1-1. System Block Diagram

290386-1

The complete document for this product is available on Intel's "Data-on-Demand" CD-ROM system. To obtain a copy, contact your local Intel field sales office, Intel technical distributor or call 1-800-548-4725.

# 82352DT EISA BUS BUFFER (EBB)

- Designed Specifically for EISA Bus Requirements

- **■** Provides Three Modes of Operation

- Data Latch and Swap Functions

Allow Swapping and Assembly of

Data between the Host and EISA/ISA

Buses on a Byte by Byte Basis

(Mode 0)

- Provides a Buffered Path with Parity Generation/Check between the Host Data Bus and DRAM (Mode 1)

- Address Latch Functions Provide Latching between the Host and EISA/ISA Buses (LA and SA Addresses) (Mode 3)

■ 120-Pin Quad Flat Pack (QFP)

EISA System

- Similar in Function to Discrete Implementation Using 74F543s/544, 74180s, and 74ALS245s

- Replaces 19 Discrete Components

Three 82352DTs are Used Per 82350

- The 82352DT Interfaces Easily to the System

- Buffer Control for the 32-Bit Mode

W/O Parity and the EISA Address

Mode is Provided by the 82358 (EISA Bus Controller)

(See Packaging Specification Order Number 240800, Package Type S)

The 82352DT design allows it to replace the multiple address and data latch-buffer/driver ICs used in EISA applications. The EBB provides three modes of operation: a 32-bit mode without parity to replace the EISA data swap buffers, a 32-bit mode with parity to replace the EISA DRAM data parity buffers, and an EISA address mode to replace the host to EISA/ISA address buffers. Mode 2 on the EBB is reserved. The same chip is strapped in three different ways to obtain the three configurations.

82352DT is manufactured and tested for Intel by LSI Logic in accordance with their internal standards.

The complete document for this product is available on Intel's "Data-on-Demand" CD-ROM system. To obtain a copy, contact your local Intel field sales office, Intel technical distributor or call 1-800-548-4725.

October 1993 Order Number: 290254-007

# 82357 **INTEGRATED SYSTEM PERIPHERAL (ISP)**

- **Provides Enhanced DMA Functions**

- ISA/EISA DMA Compatible Cycles

- All Transfers are Fly-By Transfers

- 32-Bit Addressability

- Seven Independently Programmable Channels

- Provides Timing Control for 8-, 16-, and 32-Bit DMA Data Transfers

- Provides Timing Control for Compatible, Type "A", Type "B", and Type "C" (Burst) Cycle Types

- 33 Mbytes/sec Maximum Data **Transfer Rate**

- Provides Refresh Address Generation

- Supports Data Communication **Devices and Other Devices That** Work from a Ring Buffer in Memory

- Incorporates the Functionality of Two 82C37A DMA Controllers

- Provides High Performance Arbitration

- For CPU, EISA/ISA Bus Masters. **DMA Channels, and Refresh**

- Incorporates the Functionality of Two 82C59A Interrupt Controllers

- 14 Independently Programmable Channels for Level-or-Edge **Triagered Interrupts**

- Five Programmable 16-Bit Counter/ **Timers**

- Generates Refresh Request Signal

- System Timer Interrupt

- Speaker Tone Output

- Fail-Safe Timer

- Periodic CPU Speed Control

- 82C54 Programmable Interval Timer Compatible

- Provides Logic for Generation/Control of Non-Maskable Interrupts

- Parity Errors for System and **Expansion Board Memory**

- 8 µs and 32 µs Bus Timeout

- Immediate NMI Interrupt via Software Control

- Fail-Safe Timer

- 132-Pin PQFP Package

(See Packaging Specifications: Order Number 240800. Package Type NG)

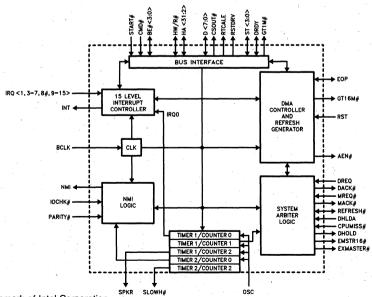

# 82357 Internal Block Diagram

Intel486 is a trademark of Intel Corporation.

290253-78

The complete document for this product is available on Intel's "Data-on-Demand" CD-ROM system. To obtain a copy, contact your local Intel field sales office, Intel technical distributor or call 1-800-548-4725.

October 1992

Order Number: 290253-006

# 82358DT EISA BUS CONTROLLER

- Supports 82350 and 82350DT Chip Set Based Systems

- Mode Selectable for Either 82350 or 82350DT Based Systems

- Mode Defaults to 82350 Based Systems

- Socket Compatible with the 82358 (EISA Bus Controller)

- Provides EISA/ISA Bus Cycle Compatibility

- EISA/ISA Standard Memory or I/O Cycles

- EISA/ISA Wait State Cycles

- ISA No Wait State Cycles

- EISA Burst Cycles

- Supports Intel386™ & Intel486™ Microprocessors

- Translates Host (CPU) and 82359 (DRAM Controller) Cycles to EISA/ISA Bus Cycles

- Generates ISA Signals for EISA Masters

- Generates EISA Signals for ISA Masters

- Supports 8-, 16-, or 32-bit DMA Cycles

Type A, B, or C (Burst) Cycles

Compatible Cycles

- Supports Host and EISA/ISA Refresh Cycles

- Generates Control Signals for Address and Data Buffers

- 82353 (ADP) and 82352 (EBB)

- Supports Byte Assembly/Disassembly for 8-, 16-, or 32-Bit Transfers

- Selectable Host (CPU) Posted Memory Write Support to EISA/ISA Bus

- Cache Controller (82385, 82395)

Interface to Maximize Performance for 386 Based Systems

- Supports I/O Recovery Mechanism

- Generates CPU, 82385, and System Software Resets

- 132-Pin PQFP Package

- Low Power CHMOS Technology

(See Packaging Specification Order #240800, Package Type

The 82358DT EISA Bus Controller is part of Intel's 82350 and 82350DT chip sets. There are five mode or function select pins which allow the 82358DT to be programmed for use in either 82350 or 82350DT based systems. The mode pins also provide support for posted memory write cycles to the EISA/ISA bus and Intel486<sup>TM</sup> burst support. The 82358DT defaults to 82350 mode and is 100% socket compatible with the 82358 (EBC).

The 82358DT interfaces the 386 and Intel486 microprocessors to the Extended Industry Standard Architecture (EISA) bus. It is used to facilitate bus cycles between the Host (CPU) bus and the EISA/ISA bus. In an 82350 system, the 82358DT interfaces to the cycle address and control signals of the Host bus. In an 82350DT system, the 82358DT interfaces to the cycle address and control signals of the 82359 DRAM controller. The 82358DT generates the appropriate data conversion and alignment control signals to implement an external byte assembly/disassembly mechanism for transferring data of different widths between the Host, EISA, and Industry Standard Architecture (ISA) buses. It also provides the cycle translation between the Host, EISA, and ISA buses.

The 82358DT is tightly coupled with the 82357 DMA controller (ISP) to run 8-. 16-, or 32-Bit EISA/ISA DMA transfers.

The 82358DT features hardware enforced I/O recovery logic to provide I/O recovery time between back-to-back I/O cycles.

The 82358DT provides special cache hardware interface signals to implement a high performance 386 based system with an 82385 or 82395 cache controller.

The 82358DT also provides resets to the Intel486, 80386, 82385, and other devices in the system to provide an integrated synchronous system reset.

Intel486 is a trademark of Intel Corporation.

The complete document for this product is available on Intel's "Data-on-Demand" CD-ROM system. To obtain a copy, contact your local Intel field sales office, Intel technical distributor or call 1-800-548-4725.

October 1992

1-575