T.52-33-21

**HTK340**

# <u>Headland</u>

### Technology

### Features

#### General

- Support for 486SX/DX/DX2 CPU

- 2 184 pin PQFP devices

- Local bus interface

- 16, 20, 25 and 33MHz CPU speeds

- Fully static operation

- Weitek 4167 supported

- System and Video BIOS on single ROM

- Uses 0.7 Micron HCMOS process

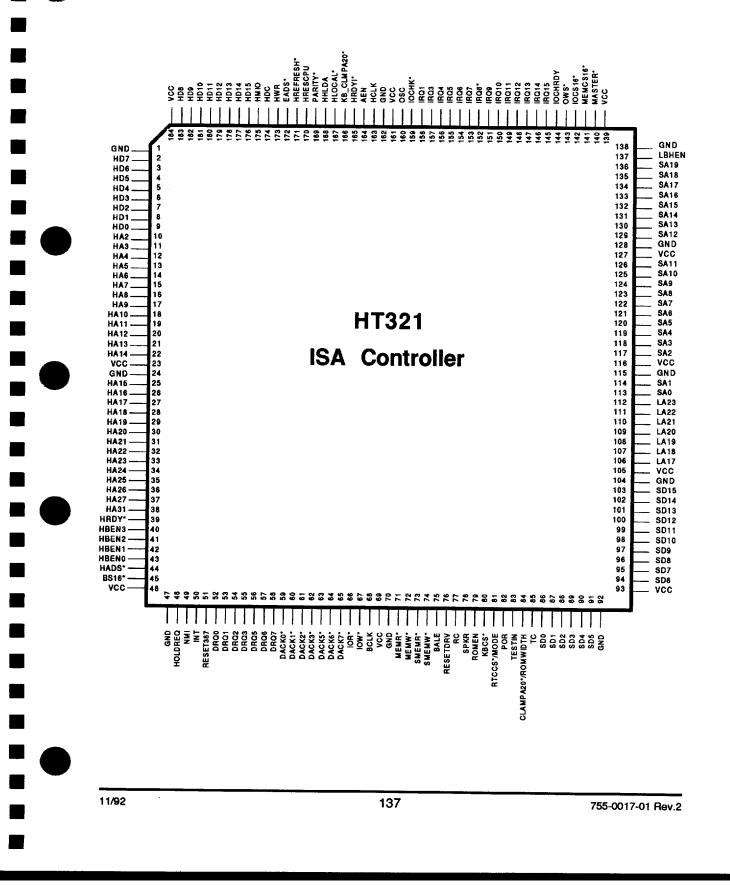

ISA Controller

- AT Compatible

- Syncronized 8MHz ISA bus

- Posted backplane memory writes

- 10 or 16 bit I/O mapping

- Integrated 8237s, 8259s and 8254 functionality

- Fast gate A20/Fast reset

# Shasta 486 Chip Set

#### Write Buffer

- 4 deep on-chip buffer

- Byte gathering

- Out of order operation

- Full or partial write buffer hits

#### **DRAM Controller**

- Line burst capability from DRAM to 80486

- 256K/1M/4M/16M DRAMs

- Mixed memory types

- EMS 4.0

- Hidden refresh operation

- 256MB Maximum system memory

- Staggered refresh

- Shadowing in 16KB increments between 640KB and 1MB

- Remapping

- Fast paging

- 2 or 4 way interleaving

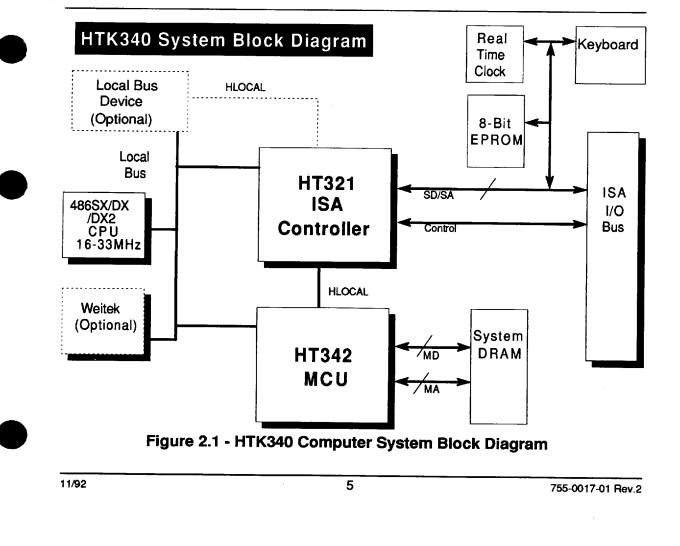

### **General Description**

The HTK340 chip set is a two chip, high performance, cost-effective solution for the  $80486SX^{TM} DX$ ,  $^{TM}$  and  $DX2^{TM}$  processing environments. In its minimum configuration, this highly integrated chip set requires only four external TTL devices to implement a fully compatible IBM PC/AT<sup>TM</sup> system at speeds up to 33MHz.

The HTK340 is based upon Headland's HTK320 Bus Architecture and consists of the HT321-ISA Bus Controller and the HT342-Memory Control Unit (MCU). Both chips are packaged in 184 pin plastic quad flat packs.

The HTK340 is unique in that it provides performance approximating that of large secondary cache systems, including the highest performance write back cache architectures, without any external cache. Secondary cache solutions should be considered in applications that make use of multi-tasking and large model operating systems. The Headland HT44 secondary cache was designed to meet the cost and performance objectives for these applications. The key to this level of performance is the 4-level deep write buffer, which includes byte gathering for up to 32-bit DRAM writes.

Due to the effectiveness of the primary cache internal to the  $80486^{TM}$ , most of the bus activity in a PC/AT compatible environment consists of writes. Indeed, this write activity consists almost exclusively of writes of either bytes or words (16 bit entities). In addition, much of this write activity is into sequential memory locations. The byte gathering feature of the buffer has the effect of reducing the number of memory accesses required. Since the 80486 can always write into the buffer with zero wait states (assuming the buffer is not full), and the buffer can empty faster than it can be filled for most write activity, the net effect is that the writes from the CPU never cause a wait state.

#### **General Description**

The HTK340 can support Peripheral Devices such as VGA or SCSI on the local processor bus, or any other devices that are designed to work within the 80486 bus protocol and timing. By eliminating the ISA backplane bottleneck, system designers can greatly improve the performance of functions such as graphics generation and disk access.

The HTK340 supports up to 4 banks of DRAM, configurable as 1-4 banks. This flexible memory architecture allows for any memory type, from 256K to 16M devices, in any bank. Maximum system performance is achieved from the DRAM banks through various means, including interleaving of memory banks and/or paging, and CAS before RAS refresh. The memory can also be tuned to maximum potential through the use of extensive DRAM timing control registers. These controls include: precharge time, access time on reads, active time on writes, as well as CAS and RAS delays. In addition, further system performance is gained by separate timing parameters on the read and write cycles which allow system designers to take maximum advantage of the pipelined structure of the chip set.

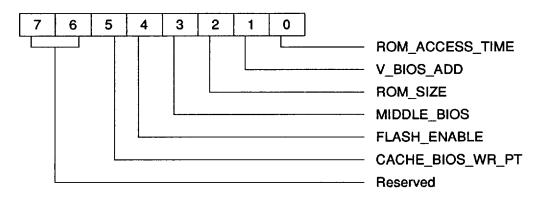

The HTK340 also supports extensive mapping registers, which allow system designers to take maximum advantage of system memory. The chip set supports Shadow/Remap in 16K blocks between the 640K and 1M boundaries, and eliminates the requirement for external decoding logic by supporting 26 programmable non-cache regions. Devices which meet HTK340 local bus requirements may be implemented without external TTL. The mapping structure of the HTK340 provides for a single 8-bit EPROM to be used for both the System and Video BIOS, further reducing system chip count and cost.

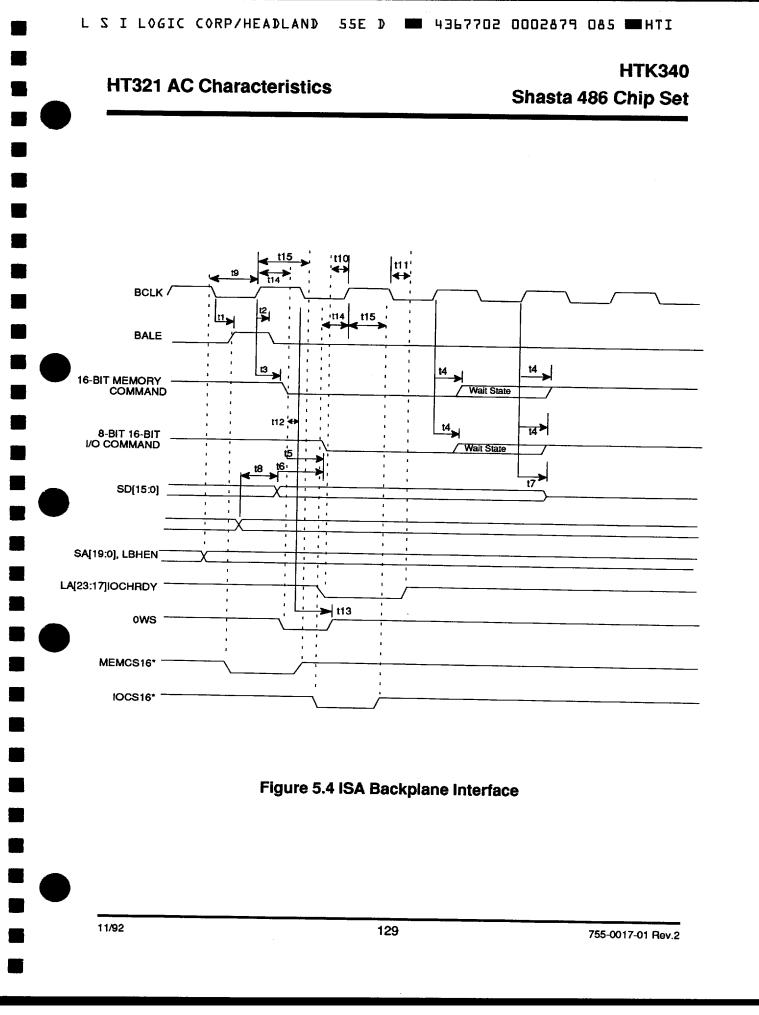

This section provides the functional description of the HT321 within the Shasta Chip Set environment. The main duty of the HT321 is to interface the 8-MHz ISA backplane with the high speed Shasta Local Bus. The HT321 provides all the functional blocks necessary for AT Compatible backplane timing, Address/Data Buffering and Latching, as well as circuit equivalents of two Intel 8237's in cascade mode, two 8259's in cascade mode, and an 8254. The HT321 is designed for '486 systems that operate between 16 and 40MHz.

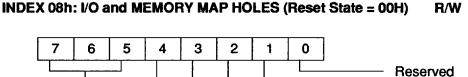

In the Shasta chip set architecture, the HT321 is the default device for CPU generated cycles, meaning that if no other LOCAL BUS device responds to the current cycle, then the HT321 will be selected to respond and terminate the cycle. The HLOCAL\* input provides the information necessary for the HT321 to determine whether or not to respond to the current cycle. Alternatively, if a Local Device cannot support the "HLOCAL\*" feature, the HT321 can be programmed for a "decode hole" within its I/O and/or MEMORY map so that when any address matches the Programmed Hole, the HT321 will ignore the cycle allowing another device to respond. One I/O and MEMORY hole may be programmed within the HT321 at any given time.

The HT321 becomes the Master Device in the System during DMA cycles, whereby the HT321 will generate all the address and control information necessary for the Shasta local bus, just as the CPU does for regular cycles. As Master during DMA cycles, the HT321 provides cycle information to both the Shasta Local Bus and the Backplane. If a Local Bus Device does not respond to this cycle, then the HT321 will assume the DMA cycle is for a backplane device and adjust accordingly.

Oulined below are the major features of the HT321:

- 184 PQFP package.

# HTK340 Shasta 486 Chip Set

- Up to 33 MHz operation.

- Fully AT-compatible 8 MHz ISA bus interface.

- Posted backplane memory writes.

- Interfaces to 8 or 16-bit ROM's.

- Ability to map video BIOS into same physical device as system BIOS.

- Internal DMA Page Registers

- Extended DMA Page Registers.

- Port\_92 functionality.

- 1 micron technology.

- Shasta architecture compatible.

- Performs all ISA bus address and data buffering.

- Built-in Intel<sup>™</sup> equivalents for:

i) 8237 DMA controllers.

ii) 8259 PIC's (interrupt controllers).

iii) 8254 PIT (timer).

- Chip-select outputs for Real Time Clock and Keyboard interfacing.

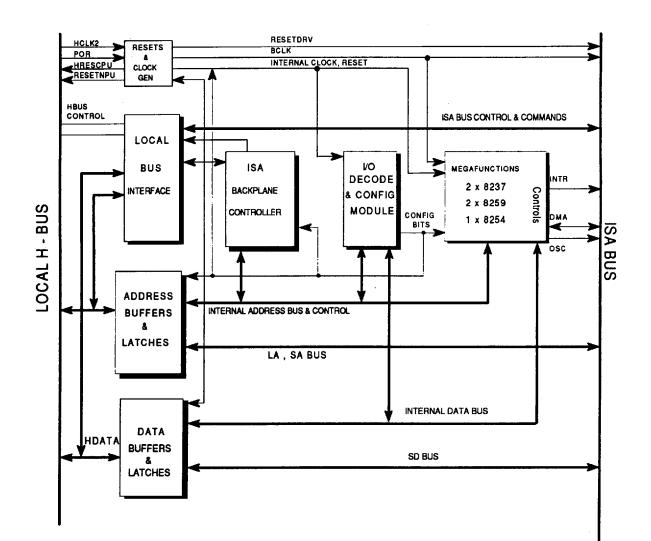

Within the HT321 there are seven (7) major functional blocks (see Figure 2.2). These blocks include:

- 1. RESETS & CLOCK\_GEN

- 2. LOCAL\_BUS INTERFACE

- 3. ADDRESS BUFFERS & LATCHES

- 4. DATA BUFFERS & LATCHES

- 5. ISA BACKPLANE CONTROLLER

- 6. I/O DECODE & CONFIGURATION MODULE

- 7. MEGAFUNCTIONS

7

A Functional Description for each of these blocks follows.

11/92

755-0017-01 Rev.2

# **HT321 Functional Description**

755-0017-01 Rev.2

8

#### 1. Resets & Clock Generation

This module is responsible for generating all the Internal or External Resets and Backplane Clocks required by the Shasta HT321. The output signal pins directly affected by this module include BCLK (P68), HRESCPU (P170), RESETNPU (P51) and RESET-DRV (P76).

#### **Clock Generation:**

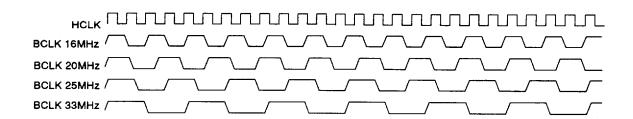

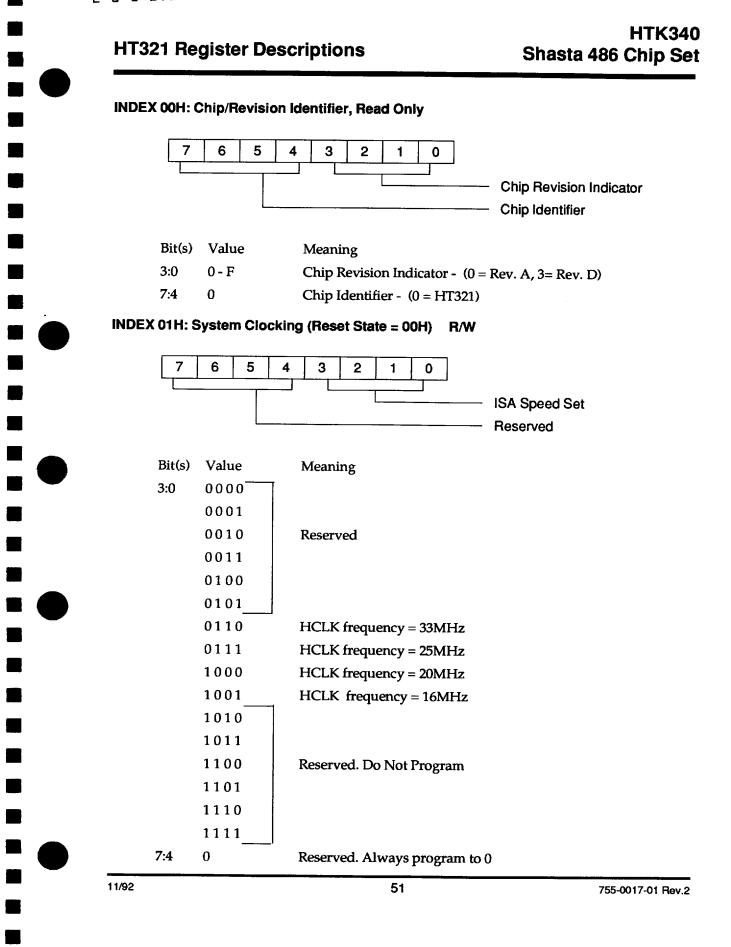

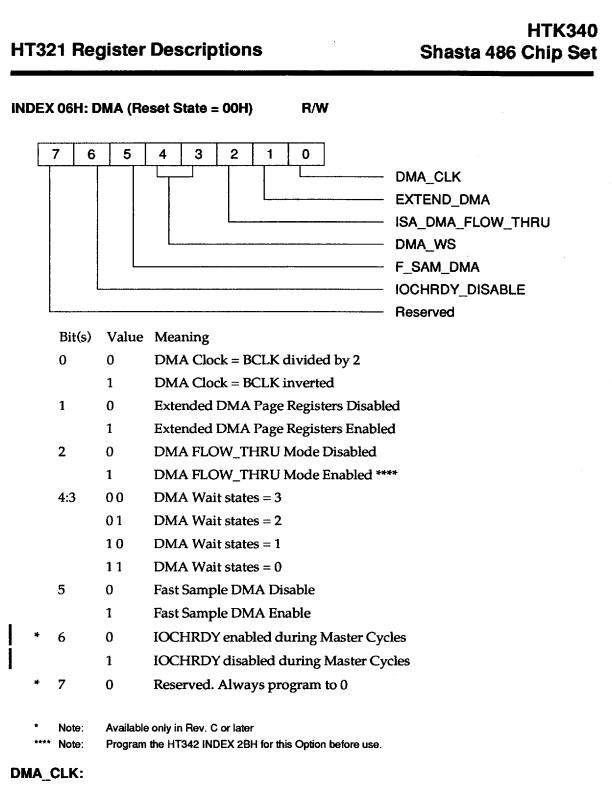

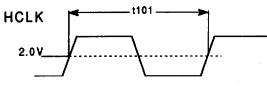

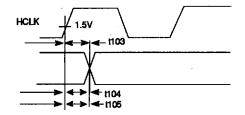

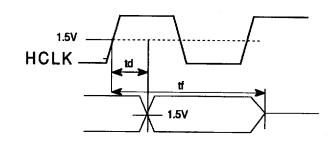

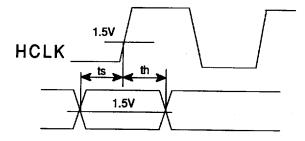

The primary incoming reference clock signal is HCLK, which is used to derive BCLK and INTERNAL\_CLK. INTERNAL\_CLK is a buffered version of the HCLK signal and is used to clock all the internal state machines of the HT321, whereas BCLK is produced by division of the HCLK signal by Programmable Ratios of 2, 3, 4, 5, 6, or 8. This Divide Ratio is selected via INDEX 01 of the HT321, where the system bus speed can be programmed to produce a 50% duty cycle 8.0-8.33 MHz BCLK signal that is then available to the ISA Backplane. Figure 2.3 shows the timing relationships between HCLK and BCLK for different settings of INDEX 01. The BCLK signal is further made available to clock the internally cascaded Intel 8237 DMA Controller equivalents. The user has the choice of supplying the internal 8237's with the 8 MHz BCLK signal directly or dividing this BCLK signal in half to supply the AT standard 4MHz clock to the 8237 DMA functions. Frequency selection for the 8237 clock is programmed via INDEX 06 of the HT321.

The AT Backplane signal, OSC, which is a 14.318 MHz Color Burst Frequency is used within this module to produce the Internal Clock of the Intel equivalent 8254 Timer function. This clock is simply the OSC input divided by 12 to produce the required 1.19MHz clock signal.

# HTK340 Shasta 486 Chip Set

#### **Resets:**

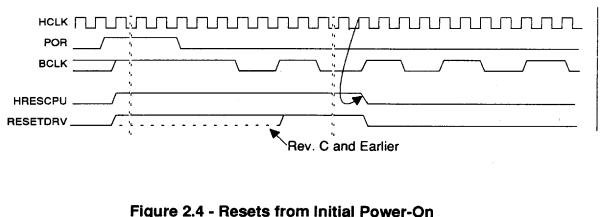

POR is the primary reset signal input. It indicates either a POWER-ON or HARD RESET situation. Once this signal goes active (high), all internal circuits are reset to their initial default state and the HRESCPU, RESETNPU and RESETDRV signals are asserted to initialize all external system devices.

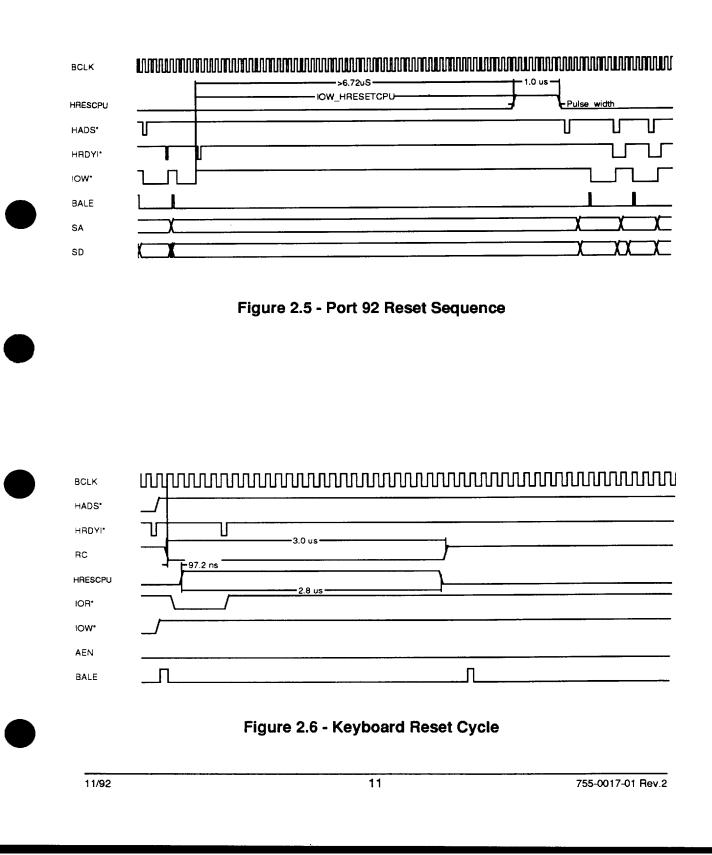

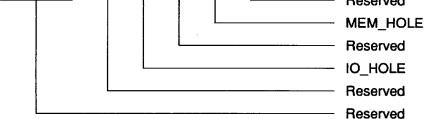

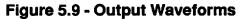

HRESCPU is the reset required by the 486 processor (CLREXPTION) to reset it to its initial state. This signal is produced synchronously using the HCLK input. Figure 2.4 shows the basic timing relationship between HCLK and HRESCPU. See the AC Timing Specifications Section for detailed timing of this signal. HRESCPU will also be generated for a keyboard initiated reset sequence via the RC(P77) input or the PORT\_92 FAST\_RC programmable function.

RESETNPU is the signal required to initialize the optional system Co-processor. The timing of this signal is identical to the HRESCPU and is only generated as a result of POR or by an I/O write cycle to 0F1H. An I/O write to 0F1H, which produces a RESETNPU pulse, defaults to Enabled at Power-on.

RESETDRV is the ISA Backplane reset signal. This Reset signal is Synchronized to the BCLK clock and is produced only during the POR sequence. RESETDRV is driven active high after the falling edge of POR for more than 80 HCLKs in Rev. C or earlier. For Rev. D or later, RESETDRV is active during POR as well. See Fig. 2.4 for details.

Figures 2.4, 2.5, and 2.6, show the timing relationships between HCLK and the Reset signals described.

11/92

755-0017-01 Rev.2

**HT321 Functional Description**

Figure 2.3 - Backplane Clocking (BCLK)

Figure 2.4 - Resets from Initial Power-On

HTK340 Shasta 486 Chip Set

#### 2. Local Bus Interface

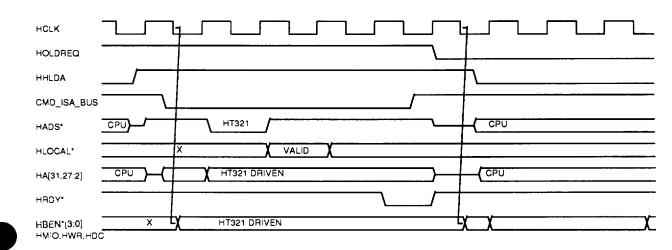

The LOCAL BUS INTERFACE module interfaces the HT321 with the Shasta Local Bus Control Signals. These signals include HA(P38-25,22-10), HBEN\*(P40-43), HHLDA (P168), HADS\*(P44), HRDY\*(P39), HRDYI\*(P165), HMIO(P175), HDC (P174), HWR(P173) and HLOCAL\*(P167). For CPU initiated transfers, this module must synchronize Shasta cycles with the ISA Backplane cycles and, during DMA transfers, this module is responsible for generating all the Shasta Bus Control Signals.

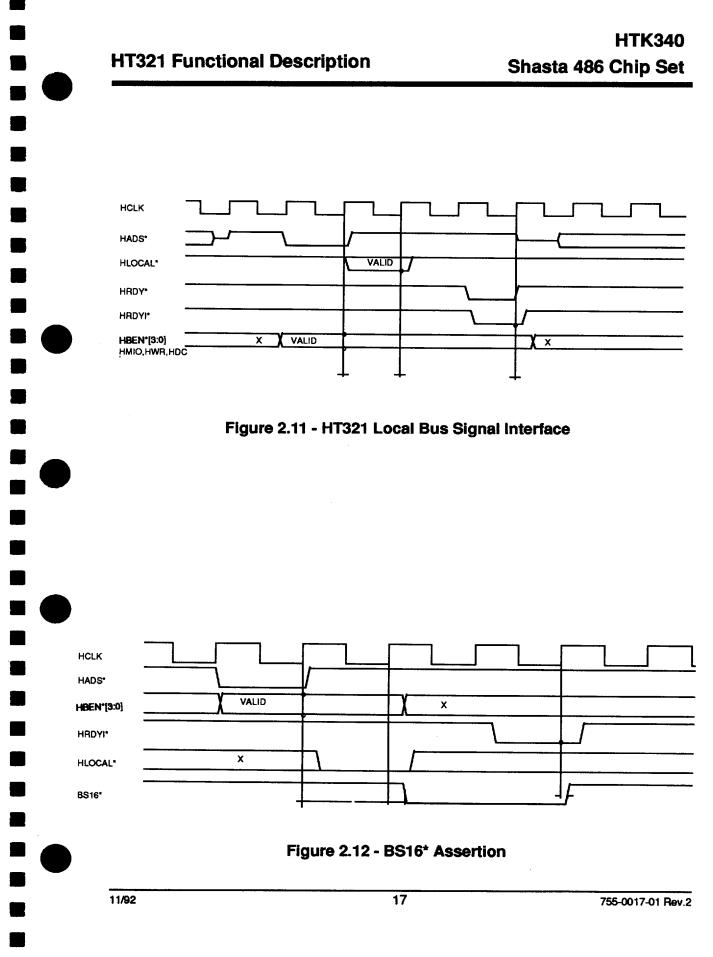

The LOCAL\_BUS\_INTERFACE module must monitor the Shasta Bus to determine when a HT321 cycle is required. HADS\* is the Control Signal in a '486 system which indicates Start-of-Cycle to all Local Bus devices. One HCLK2 after HADS\* initiates Start-of-Cycle, the HLOCAL\* signal is sampled to determine if another Local Device has responded to the cycle. If at this time the HLOCAL\* signal is true (low), the HT321 performs no action for the cycle. However, if the HLOCAL\* is false (high), the HT321 must respond to the cycle, and the LOCAL\_BUS\_INTERFACE module will pass the request on to the ISA BACKPLANE CON-TROLLER section of the chip. Signals including HA[31, 27:2], HBEN\*[3:0], HMIO, HDC and HWR are sampled and gated to the rest of the ISA chip. At the conclusion of the ISA cycle, the ISA BACKPLANE CONTROLLER section indicates completion by issuing a READY pulse to the LOCAL\_BUS\_INTER-FACE module. This READY appears on the Shasta Local Bus as HRDY\* from the HT321. When HRDYI\* is returned to the HT321 chip, the real end-of-cycle occurs and the HT321 returns to monitoring the Shasta Local Bus for further ISA cycles. Figure 2.11 shows the fundamental timing relationships between HCLK and Shasta Local Bus signals attached to the HT321. This diagram specifically shows timing for CPU initiated cycles.

### **HT321 Functional Description**

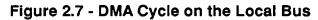

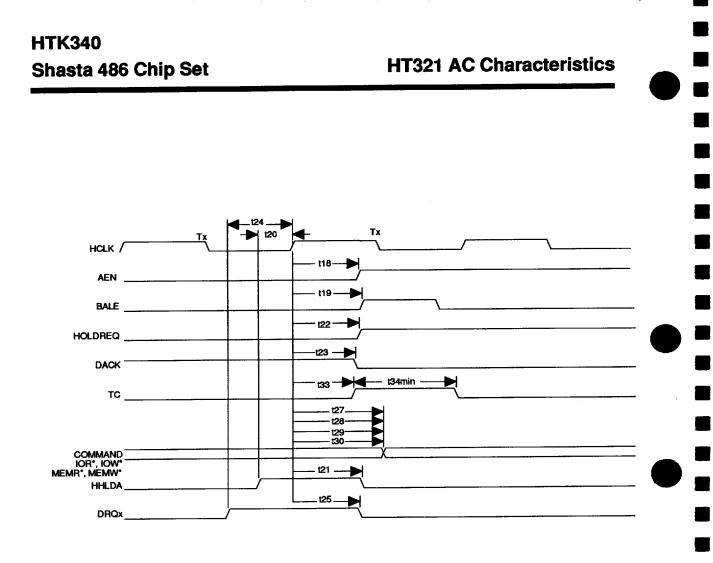

For DMA initiated cycles, the '486 CPU enters a Hold State in response to the HOLDREQ Signal of the HT321. When the CPU has completed its current tasks and can relinquish the Shasta bus, it will assert the HHLDA signal, this is gated to the Cycle Arbiter of the LOCAL\_BUS\_INTERFACE module. Only when activity is determined complete on the Shasta Bus and ISA Backplane Bus is the HHLDA signal gated to the rest of the ISA Chip. For regular DMA cycles, the internal DMA Controller of the ISA Chip will assert the ISA Backplane Command combinations (IOR\*/MEMW\*, MEMR\*/IOW\*) which are detected by the LOCAL BUS INTERFACE. DMA to/from Local Memory is the only non-MASTER Mode activity supported by the Shasta architecture; when a MEMR\* or MEMW\* Command is detected, the LOCAL\_BUS\_INTERFACE module asserts an HADS\* pulse on the Shasta bus, the cycle status information (HMIO, HDC, HWR) is decoded and asserted on the Shasta Bus at this time, where it remains valid until the Backplane Commands are de-asserted. HLOCAL\* is sampled one HCLK after HADS\* to determine if the cycle initiated is for a Shasta Local Bus device. In this manner, all cycles on the Shasta Local Bus look identical, whether they are initiated by DMA or '486 CPU. Figure 2.7 shows the timing of HT321 initiated Shasta cycles during DMA transfers.

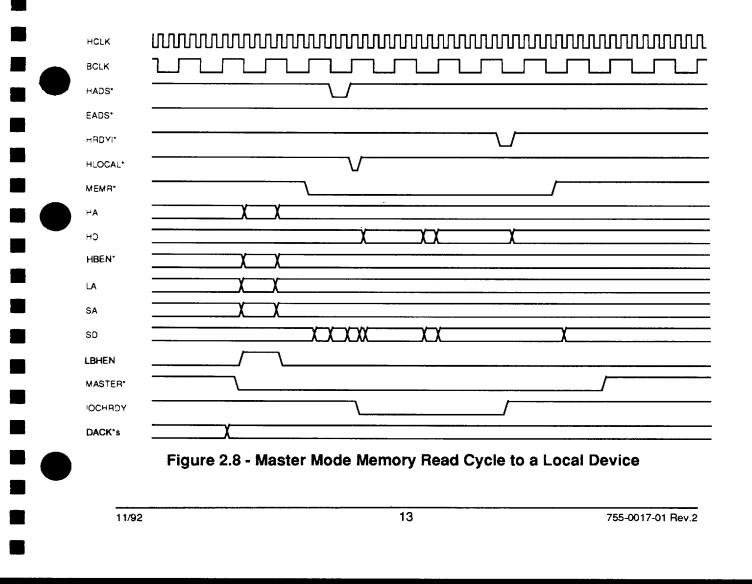

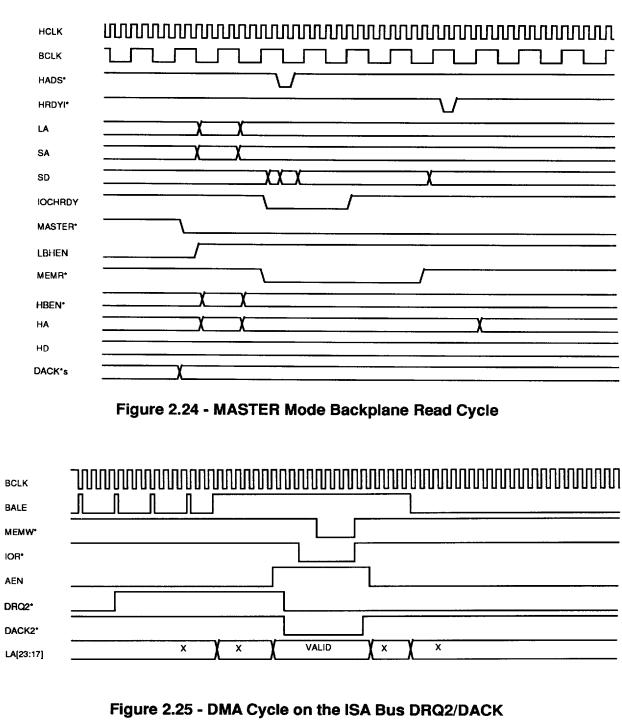

For DMA MASTER mode cycles, events follow the sequence described above, but Backplane MASTER mode devices may have access to I/O as well as Memory locations on the Shasta Local Bus. Therefore, during MASTER mode Cycles, when any Backplane command is detected by the LOCAL\_BUS\_INTERFACE module, a HADS\* pulse will be generated for the Shasta Bus (Reference HT321 Index 06H). Figure 2.9 shows a MASTER Mode Memory Write Cycle to Shasta local memory, whereas Figure 2.8 shows the timing relationships for a MASTER Mode Read Cycle from local memory.

HTK340

Shasta 486 Chip Set

| HCLK    |     |

|---------|-----|

| BCLK    |     |

| HADS*   |     |

| EADS*   |     |

| HRDYI*  |     |

| HLOCAL" | V   |

| MEMW    |     |

| HA      | X_X |

| HD      |     |

| HBEN*   |     |

| LA      |     |

| SA      |     |

| SD      |     |

| LBHEN   |     |

| MASTER. |     |

| OCHRDY  |     |

| DACK*s  | X   |

#### **3. ADDRESS BUFFERS & LATCHES**

This module is responsible for providing the necessary ISA Backplane SA[19:0] (P136-129,126-117,114-113), LBHEN\*(P137) and LA[23:17](P112-106) Address Signals during ISA Cycles initiated by the CPU. During DMA cycles, this module will provide the HA [31, 27:2] and HBEN\*[3:0] Shasta Local Bus signals.

For CPU initiated cycles, the SA[19:2] lines are produced from the incoming HA[19:2] signals and gated to the ISA backplane when BALE is true(high). On the falling edge of BALE, ISA Compatible Backplane devices may latch the SA address signals since they are then stable and will remain stable for the entire cycle or until another BALE is generated. Shasta Local bus signals HBEN\*[3:0] generate SA1, SA0 and LBHEN\*. The significance of these SA address lines depends on the number of bytes requested by the system and whether the target data is located at an odd address. The ISA Backplane LA[23:17] address lines are asserted 1 HCLK after HADS\* is sampled true, by the HT321. These Signals are equivalent to the HA[23:17] input address signals. These LA address lines remain valid until HRDYI\* is returned to the HT321 signifying the end of the current cycle.

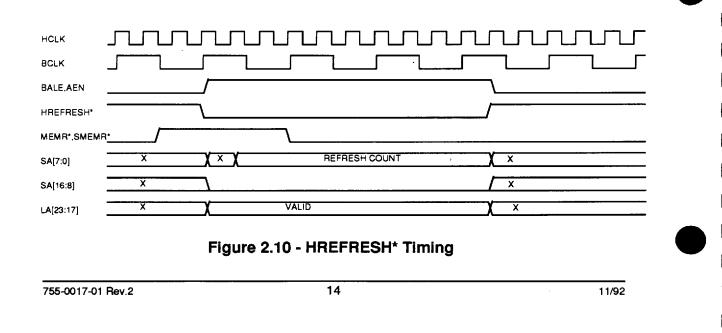

During REFRESH\* cycles, SA[7:0] are driven by the internal refresh counter of the HT321 and contain the Refresh Address. SA[15:8] are asserted to logic 0. SA[19:16] and LA[23:17] are controlled by the current programmed value of the Internal DMA PAGE Register at location 8FH. Typically, this register is set to 00 in an AT system. HA address lines are not driven by the HT321 during REFRESH\* cycles. The Backplane signal BALE is true(high) for the duration of the cycle. The sequence of a REFRESH\* cycle is shown in Figure 2.10.

# HTK340 Shasta 486 Chip Set

During DMA cycles, SA[15:0] and LBHEN\* signals are generated by the Internal Intel 8237 equivalent that has control for the cycle. The significance of SA[19:16] and LA[23:17] signals is controlled by the DMA PAGE register (I/O location 80-8FH) of the acknowledged DMA channel. The value is programmed by application software or BIOS. BALE is always true(high) for the duration of a DMA cycle. A typical DMA transfer cycle, as seen on the ISA Backplane, is shown in Figure 2.25. In this diagram, the DMA clock is set to BCLK/2 (INDEX 06H). A MASTER mode transfer cycle from an ISA Backplane memory device is shown in Figure 2.24. In this case, the HLOCAL\* was not generated by any Shasta Local device. Therefore, the whole transfer takes place on the ISA Backplane.

HA[23:2] and HBEN\*[3:0] lines are asserted by the HT321 during DMA cycles and are the equivalent of the Backplane SA and LA signals. To provide DMA access to the full Local Memory range of a Shasta System, Extended DMA PAGE REGISTERS located at I/O address 480-48FH are implemented in the HT321. These registers are controlled via INDEX 06 of the HT321 Registers. When enabled, they contain the HA[31:24] Address values required for the Extended DMA transfer. The Extended DMA Page Registers provide for DMA access to/from any location within the Shasta system local memory map. The timing of the HA and HBEN\* signals produced during DMA cycles is equivalent to '486 processor timing; that is, the addresses are valid when HADS\* is generated by the HT321 and remain valid until HRDYI\* is returned by the System to terminate the cycle in progress.

11/92

#### 4. DATA BUFFERS & LATCHES

This module is responsible for routing Data to and from the ISA Backplane SD[15:0] and the Shasta Local Data Bus HD[15:0]. If Data Bridging is required during the current cycle, this module will provide it. For ISA Backplane requests which require more than one cycle to access the data required by the CPU, temporary storage exists within this module to hold the gathered data until all the data is processed.

The HT321 is limited to a 16 bit transfer of data for any given cycle. To signal this fact to the CPU, BS16\* is generated by the HT321 for any CPU cycle requesting data transfer on the upper half of the CPU data bus HD[31:16]. Figure 2.12 shows the timing for the generation of the BS16\* signal by the HT321 chip.

For CPU initiated WRITE cycles to the ISA Backplane, data is placed on the HD[15:0] inputs of the HT321 and then routed through the chip to the SD[15:0] of the Backplane Bus. For 16-bit devices on the backplane, no Data bridging is required in the HT321 Chip. For 8-Bit ISA Compatible devices, the incoming data is routed automatically to the lower half of the SD bus (SD[7:0]). MEMCS16\* and IOCS16\* are the backplane signals monitored by the HT321 to determine whether the ISA Backplane device responding is 16- or 8-Bit. For CPU WRITES of 16-bits of data to an 8-Bit Backplane device, the incoming HD[15:0] bus is latched at the start of the first WRITE cycle. A second WRITE cycle is generated by the HT321 to transfer the next 8 bits of data to the Backplane device.

For CPU initiated READ cycles from the ISA Backplane, data is applied to the SD[15:0] Backplane Bus by the responding device and routed through the ISA chip to the HD[15:0] bus so that the '486 CPU can aquire the data. The HBEN\*[1:0] Shasta Local Bus signals, generated by the CPU in this case, are used to determine which way to route the backplane

### **HT321 Functional Description**

data through the HT321. Again, MEMCS16\* and IOCS16\* are monitored to see what data size will be transferred by the Backplane device. For CPU requests of 16-bits of data from an 8-bit Backplane device, the incoming SD[7:0] bus is latched at the end of the first cycle, and then another cycle is generated by the HT321 to acquire the next 8 bits of data from the Backplane device. During the second cycle of this transfer, both sets of 8-bit data are applied to the HD[15:0] pins to complete the request.

For DMA WRITE and Backplane MASTER mode READ Transfers to/from the Shasta Local Bus, the HT321 uses the SA0, SA1 and LBHEN\* signals to determine the Shasta HBEN\*[3:0] lines. These signals now indicate to the Local Memory device where to expect Valid Data on the HD[15:0] bus. When DMA transfers of data to the upper half of the Shasta data bus (HD[31:16]) occur, the HT321 will issue HBEN\*[3:2] correctly; Local Memory Devices must accept this data on HD[15:0] and bridge the Data to the correct location.

For DMA READ and Backplane MASTER mode WRITE Transfer cycles to/from the Shasta Local Bus, the HT321 again asserts the HBEN\*[3:0] signals but requires a responding Local Memory Device to provide Valid Data only to the HD[15:0] lines.The Memory Device must bridge the data on the HD[15:0] bus as required. No more than two bytes of data will be transferred by the HT321 during a DMA cycle.

755-0017-01 Rev.2

#### 5. ISA BACKPLANE CONTROLLER

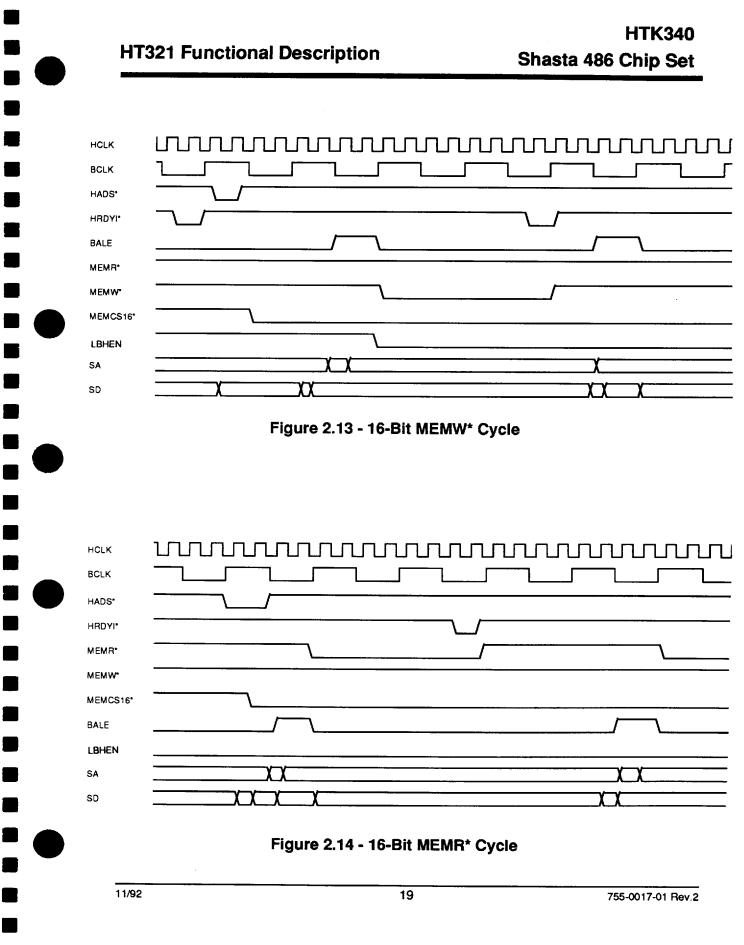

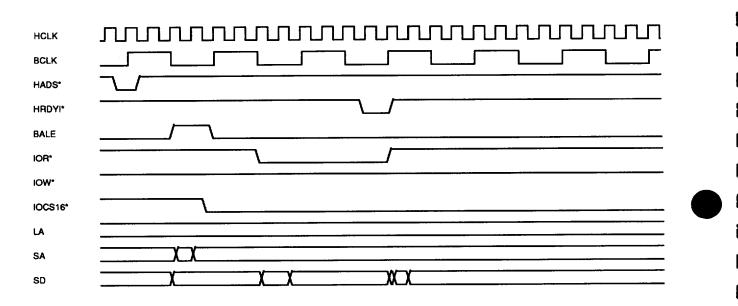

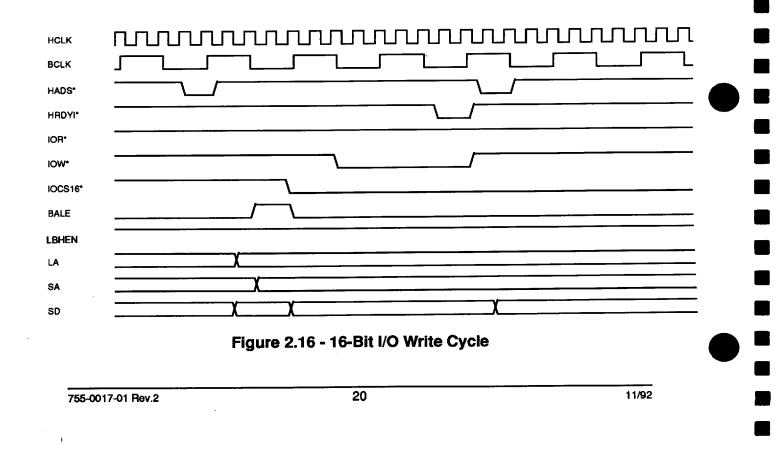

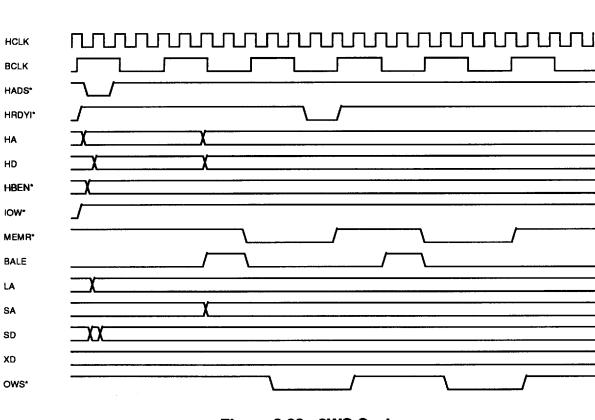

This module is responsible for producing ISA Compatible timing for the Backplane control signals. These signals include IOW\*, IOR\*, (S)MEMW\*, (S)MEMR\*, BALE and are synchronized to BCLK edges. In order to accomplish this, the ISA BACKPLANE CON-TROLLER module monitors backplane signals MEMCS16\*, IOCS16\*, IOCHRDY, and OWS to determine the timing required by the current cycle. INDEX 02H may be programmed to set the Default Timing of any backplane access. The AT Compatible setting is of 6 BCLK cycle duration. The options exist to set default as low as 3 BCLK cycles duration for a Backplane cycle. The duration of a Backplane cycle is measured from 1/2 BCLK before the assertion of BALE to the end of the Command asserted for the cycle.

Backplane cycles begin within the HT321 once it is determined that the current Local Bus cycle is for the ISA Controller. This happens one HCLK2 after HADS\* is sampled,

### **HT321 Functional Description**

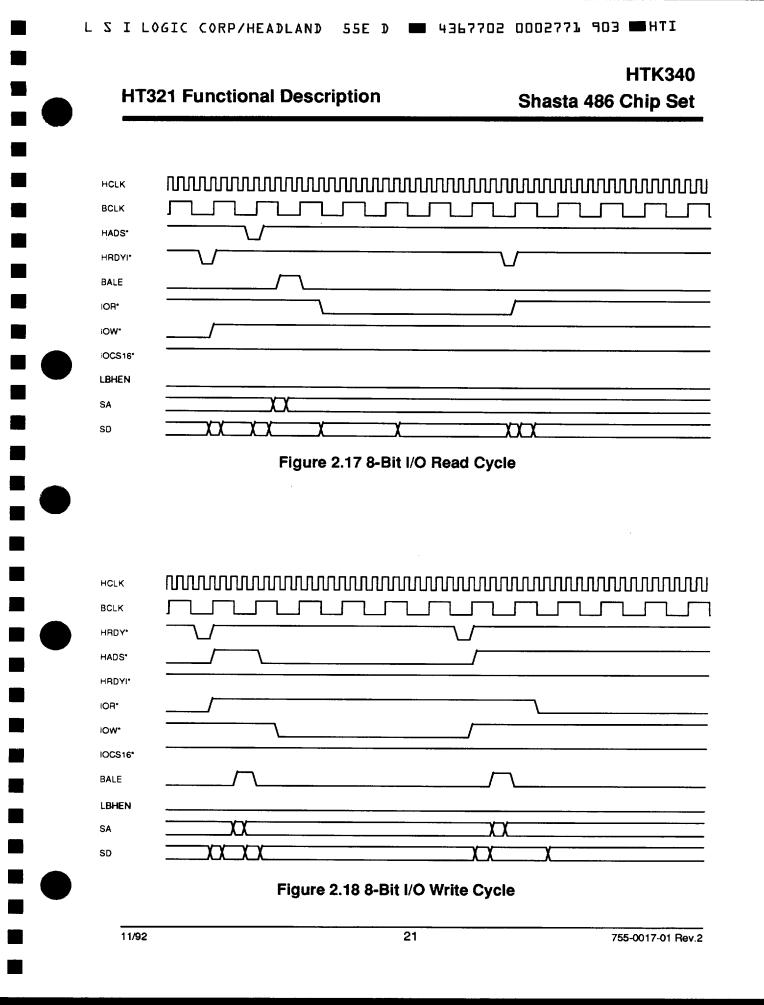

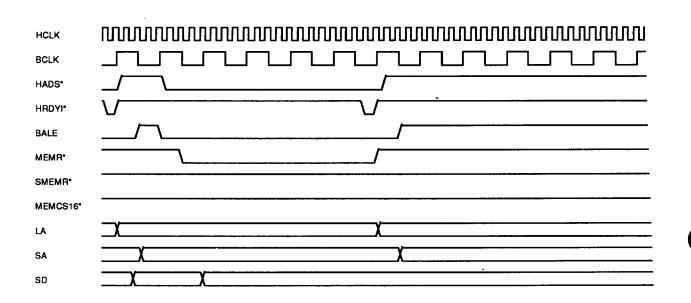

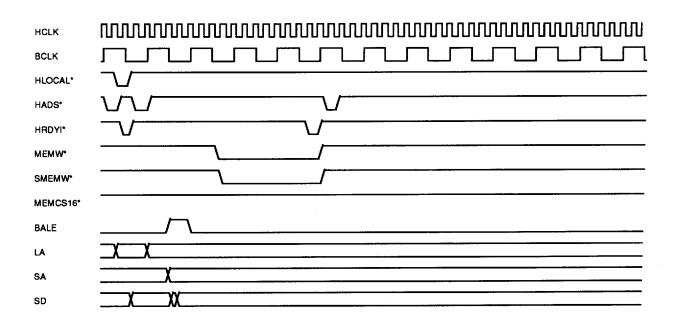

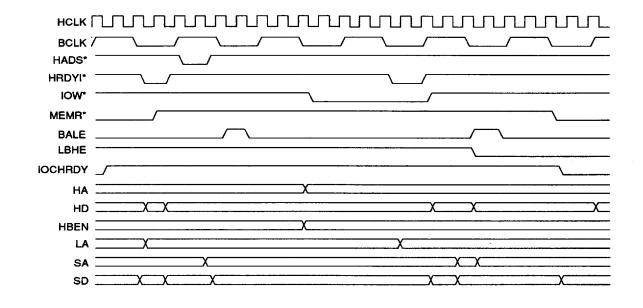

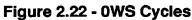

indicating the start of cycle. At this point, the ISA BACKPLANE CONTROLLER module will synchronize to the BCLK signal and begin the sequence by asserting a BALE pulse at the correct phase of BCLK. Depending on the type of cycle requested and the state of the incoming backplane cycle Moderator Signals, the proper Command(s) will be determined. At the completion of the Command, HRDY\* will be issued by the HT321 to the Shasta Local Bus indicating the cycle is complete. When HRDYI\* is returned to the HT321 the cycle actually completes. For more detail see Figures 5.11 and 5.12 in the AC Timing Section of this Data Sheet. A number of typical ISA Backplane cycles are shown in the following figures, 2.13, 2.14, 2.15, 2.16, 2.17, 2.18, 2.19, 2.20, 2.21, 2.22.

For DMA/MASTER MODE operation, the BACKPLANE CONTROLLER section of the ISA Chip is disabled, since the Commands will be asserted by the MASTER device. BALE is normally set true(high) for the duration of a DMA cycle, allowing address flowthru to/from the backplane.

755-0017-01 Rev.2

**HT321 Functional Description**

**HT321 Functional Description**

#### Figure 2.19 - 8-Bit MEMR\* Cycle

### Figure 2.20 - 8-Bit MEMW\* Cycle

Figure 2.21 - IOCHRDY Wait States

11/92

HTI 4367702 0002774 612 HTI

# **HTK340** Shasta 486 Chip Set

**HT321 Functional Description**

# HTK340 Shasta 486 Chip Set

DMACLK = 4MHz DMA Wait State = 1 (AT Standard)

11/92

755-0017-01 Rev.2

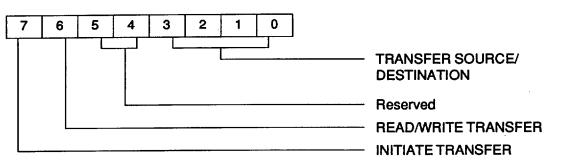

#### 6. I/O DECODE & CONFIGURATION

This module contains all the Internal Registers of the HT321 as well as Decodes for Internal and some External Devices. The HT321 provides "Chip Select" signals for two External Devices commonly used in AT Compatible Motherboard systems: Real Time Clock Chip Select (RTCCS\* P81) and Keyboard Chips Select (KBCS\* P80). The tables below chart the internal I/O decode information of the HT321.

The Configuration Module contains all the INDEX Registers which provide the HT321 Programmable Configuration Controls. The HT321 has a total of 32 mapped Index locations but only those containing programmable bits are implemented and accessible. These ISA Configuration Registers are mapped into INDEX 00 - 1Fh. Most of these registers are Read/Write, but only the bits indicated should be altered. All Unused or Reserved Registers

## **HT321 Functional Description**

and Bits must be left at Default or Masked off during Configuration to maintain future compatibility.

The ISA Chip is also responsible for maintaining the current Configuration INDEX Pointer Value. Therefore, access to I/O location 028H will be terminated by the HT321. Data Read from I/O location 028H is made available to the CPU via HD[15:0].

The Configuration INDEX Register Bits of the HT321 are described in detail in the Register Description Section of this Data Sheet. Please refer to this section for detail of the Registers, Control Functions and program access to the Registers.

#### I/O Decode

The following table shows the I/O Decode range for Internal Ports of the HT321.

| A15-<br>A12 | A11                                                                                      | A10 | <b>A</b> 9 | <b>A</b> 8 | A7 | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | A3 | A2 | <b>A</b> 1 | AO | Address<br>Range(Hex) | Selected Device |

|-------------|------------------------------------------------------------------------------------------|-----|------------|------------|----|------------|------------|------------|----|----|------------|----|-----------------------|-----------------|

| 0           | 0                                                                                        | 0   | 0          | 0          | 0  | 0          | 0          | Х          | X  | Х  | х          | х  | 000 -01F              | DMA1            |

| 0           | 0                                                                                        | 0   | 0          | 0          | 0  | 0          | 1          | 0          | 0  | 0  | 0          | х  | 020 - 021             | PIC1            |

| 0           | 0                                                                                        | 0   | 0          | 0          | 0  | 0          | 1          | 0          | 0  | 1  | 0          | 0  | 024                   | Config Data     |

| 0           | 0                                                                                        | 0   | 0          | 0          | 0  | 0          | 1          | 0          | 1  | 0  | 0          | 0  | 028                   | Config Address  |

| 0           | 0                                                                                        | 0   | 0          | 0          | 0  | 1          | 0          | X          | Х  | X  | Х          | х  | 040 - 05F             | PTC             |

| 0           | 0                                                                                        | 0   | 0          | 0          | 0  | 1          | 1          | 0          | х  | x  | х          | 0  | 060 -<br>06E(even)    | KBC, Port B     |

| 0           | 0                                                                                        | 0   | 0          | 0          | 0  | 1          | 1          | 1          | х  | х  | Х          | Х  | 070 - 071             | RTC, NMI        |

| 0           | 0                                                                                        | 0   | 0          | 0          | 1  | 0          | 0          | 0          | Х  | X  | X          | Х  | 080 - 08F             | DMA Page        |

| 0           | 0                                                                                        | 0   | 0          | 0          | 1  | 0          | 0          | 1          | 0  | 0  | 1          | 0  | 092                   | Sys Ctrl Port   |

| 0           | 0                                                                                        | 0   | 0          | 0          | 1  | 0          | 1          | X          | X  | х  | Х          | х  | 0A0 - 0BF             | PIC2            |

| 0           | 0                                                                                        | 0   | 0          | 0          | 1  | 1          | 0          | х          | x  | х  | Х          | х  | 0C0-0DF               | DMA2            |

| 0           | 0                                                                                        | 0   | 0          | 0          | 1  | 1          | 1          | 1          | х  | Х  | Х          | 1  | 0F1                   | RESETNPU        |

| 0           | 0                                                                                        | 1   | 0          | 0          | 1  | 0          | 0          | 0          | Х  | х  | Х          | х  | 480 - 48F             | Ext. DMA Page   |

| 60-6        | 60-64 is KBC if A0=0, and Port B if A0=1, 070-071 is RTC if A0=1 and RTC and NMI if A0=0 |     |            |            |    |            |            |            |    |    |            |    |                       |                 |

All other address ranges are available to devices on the ISA bus.

# HTK340 Shasta 486 Chip Set

#### I/O Address Map

The following table describes the I/O ports supported by the HT321. The table is numerically ordered by HEX Address from zero.

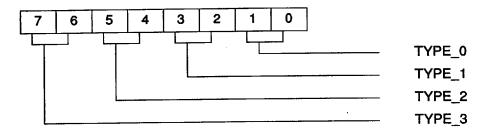

#### I/O TYPE

| Addr<br>Port          | Read/<br>Write   | Description                      |

|-----------------------|------------------|----------------------------------|

| DMA Controller #1     |                  |                                  |

| 0000H                 | R/W              | Channel 0 current address        |

| 0001H                 | R/W              | Channel 0 current word count     |

| 0002H                 | R/W              | Channel 1 current address        |

| 0003H                 | R/W              | Channel 1 current word count     |

| 0004H                 | R/W              | Channel 2 current address        |

| 0005H                 | R/W              | Channel 2 current word count     |

| 0006H                 | R/W              | Channel 3 current address        |

| 0007H                 | R/W              | Channel 3 current word count     |

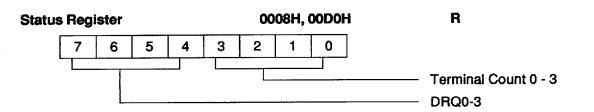

| 0008H                 | R/W              | Command/Status Register          |

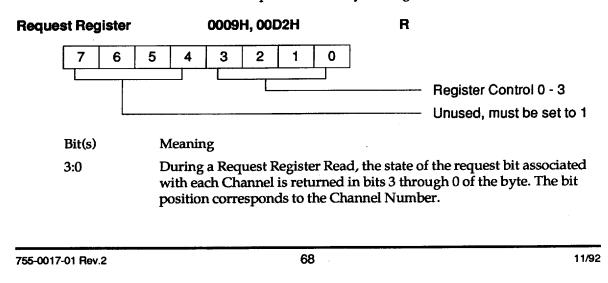

| 0009H                 | R/W              | Request Register                 |

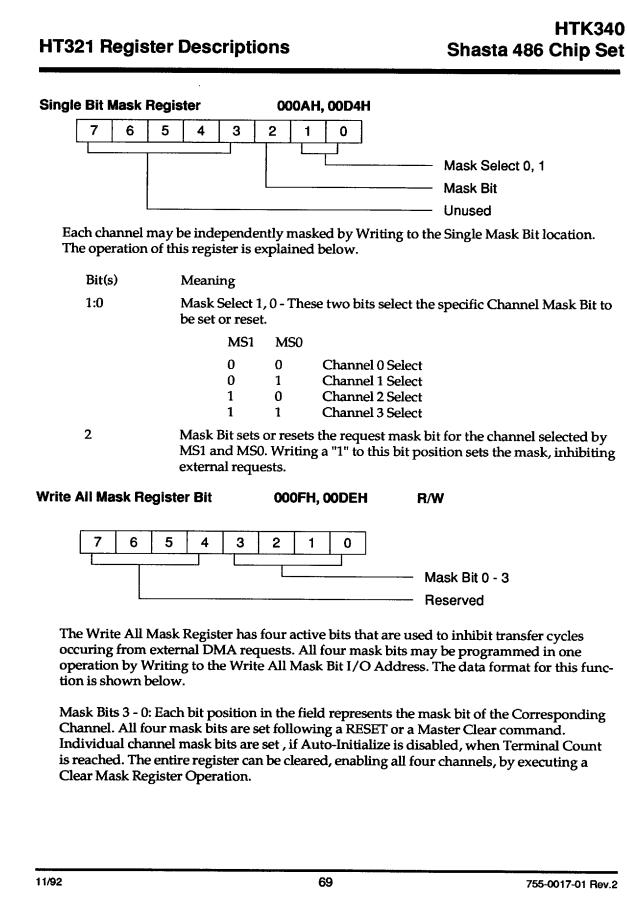

| 000AH                 | R/W              | Single Bit Mask Register         |

| 000BH                 | R/W              | Mode Register                    |

| 000CH                 | R/W              | Clear Byte Pointer               |

| 000DH                 | R/W              | Master Clear                     |

| 000EH                 | R/W              | Clear Mask Register              |

| 000FH                 | R/W              | Write All Mask Register Bit      |

| Programmable Interrup | ot Controller #1 |                                  |

| 0020H                 | W                | ICW1                             |

|                       | W                | OCW2                             |

|                       | W                | OCW3                             |

|                       | R                | Interrupt Request Register (IRR) |

|                       | R                | In-Service Register (ISR)        |

|                       | R                | Polling Data Byte                |

|                       |                  |                                  |

# **HT321 Functional Description**

| Addr             | Read/     | Description                        |

|------------------|-----------|------------------------------------|

| Port             | Write     | •                                  |

| 0021H            | W         | ICW2                               |

|                  | W         | ICW3                               |

|                  | W         | ICW4                               |

|                  | W         | OCW1                               |

|                  | R         | Interrupt Mask Register (IMR)      |

| 0023H            |           | Reserved                           |

| 0024H            | R/W       | Configuration Data Port            |

| 0028H            | R/W       | Configuration Address Port         |

| 0029H - 003FH    |           | Reserved                           |

| Timer/Counter    |           |                                    |

| 0040H            | R/W       | Timer 0 Count Load/Read            |

| 0041H            | R/W       | Timer 1 Count Load/Read            |

| 0042H            | R/W       | Timer 2 Count Load/Read            |

| 0043H            | W         | Timer Control Word                 |

| 0044H - 005FH    |           | Reserved                           |

| Write Keyboard C | ontroller |                                    |

| 0060H            | R/W       | Keyboard Data                      |

| 0062H - 0063H    |           | Reserved                           |

| 0064H            | R/W       | Keyboard Control/Status            |

| Port B           |           |                                    |

| 0061H            | R/W       | Port B Status Port                 |

| Real Time Clock  |           |                                    |

| 0070H            | W         | Real-Time Clock Index and NMI Mask |

| 0071H            | R/W       | Real-Time Clock Data Port          |

| DMA Page Regist  | ers       |                                    |

| 0080H            | R/W       | Not Used                           |

| 0081H            | R/W       | Channel 2 Page Register            |

| 0082H            | R/W       | Channel 3 Page Register            |

| 0083H            | R/W       | Channel 1 Page Register            |

| 0087H            | R/W       | Channel 0 Page Register            |

| 0089H            | R/W       | Channel 6 Page Register            |

|                  |           |                                    |

| 321 Functional   | Description         | H<br>Shasta 486 Ch              |

|------------------|---------------------|---------------------------------|

| Addr<br>Port     | Read/<br>Write      | Description                     |

| 008AH            | R/W                 | Channel 7 Page Register         |

| 008BH            | R/W                 | Channel 5 Page Register         |

| System Control P |                     |                                 |

| 0090H - 0091H    |                     | Reserved                        |

| 0092H            | R/W                 | System Control Port             |

| 0093H - 009FH    |                     | Reserved                        |

| Programmable Int | errupt Controller # | 2                               |

| 00A0H            | W                   | ICW1                            |

|                  | W                   | OCW2                            |

|                  | W                   | OCW3                            |

|                  | R                   | Interrupt Request Register (IRR |

|                  | R                   | In-Service Register (ISR)       |

|                  | R                   | Polling Data Byte               |

| 00A1H            | W                   | ICW2                            |

|                  | W                   | ICW3                            |

|                  | W                   | ICW4                            |

|                  | W                   | OCW1                            |

|                  | R                   | Interrupt Mask Register (IMR)   |

| DMA Controller # | 2                   |                                 |

| 00C0H            | R/W                 | Channel 0 current address       |

| 00C2H            | R/W                 | Channel 0 current word count    |

| 00C4H            | R/W                 | Channel 1 current address       |

| 00C6H            | R/W                 | Channel 1 current word count    |

| 00C8H            | R/W                 | Channel 2 current address       |

| 00CAH            | R/W                 | Channel 2 current word count    |

| 00CCH            | R/W                 | Channel 3 current address       |

|                  |                     |                                 |

R/W

R/W

R/W

R/W

R/W

# **HTK340** asta 486 Chip Set

755-0017-01 Rev.2

Channel 3 current word count

Command/Status

**Request Register**

Mode Register

Single Bit Mask Register

00CEH

00D0H

00D2H

00D4H

00D6H

| HTK340              |  |

|---------------------|--|

| Shasta 486 Chip Set |  |

| Addr<br>Port  | Read/<br>Write   | Description                      |

|---------------|------------------|----------------------------------|

| 00D8H         | R/W              | Clear Byte Pointer               |

| 00DAH         | R/W              | Master Clear                     |

| 00DCH         | R/W              | Clear Mask Register              |

| 00DEH         | R/W              | Write All Mask Register Bit      |

| 00DFH - 00EFH |                  | Reserved                         |

| Extended DMA  | A Page Registers |                                  |

| 0480H         | R/W              | Not Used                         |

| 0481H         | R/W              | Channel 2 Extended Page Register |

| 0482H         | R/W              | Channel 3 Extended Page Register |

| 0483H         | R/W              | Channel 1 Extended Page Register |

| 0487H         | R/W              | Channel 0 Extended Page Register |

| 0489H         | R/W              | Channel 6 Extended Page Register |

| 048AH         | R/W              | Channel 7 Extended Page Register |

| 048BH         | R/W              | Channel 5 Extended Page Register |

755-0017-01 Rev.2

30

#### 7. MEGAFUNCTIONS

This block of the HT321 contains the standard AT Compatible Megafunctions necessary for the implementation of an AT-Compatible system and ISA bus. Within this module are the equivalents of two Intel 8237 DMA Controllers, two 8259 Intel Interrupt Controllers and one Intel 8254 Programmable Interval Timer. All the support logic necessary to implement and clock these devices is also included. Below is a brief description of each of the Megafunctions in this block. This information, together with the detailed Register Description for these devices located in the **REGISTER DESCRIPTION section of this** data sheet, should provide the user with enough information to properly program and use these devices. If further information is required, please examine the IBM AT Technical Reference manual or the Intel Data Sheet for the particular device in question.

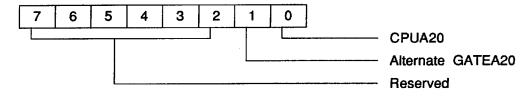

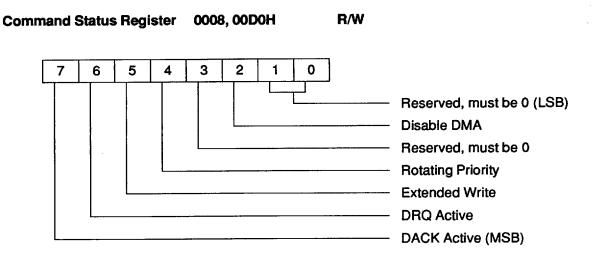

#### **DMA** Controller

The HT321 contains two DMA controllers that are compatible with an Intel 8237. Each controller is a four-channel DMA device that can generate the Control Signals and Memory Addresses necessary to transfer information between a Peripheral Device and Memory. The DMA controllers are internally cascaded to provide four DMA channels for transfers to 8-bit peripherals (DMA1) and three channels for transfers to 16-bit peripherals (DMA2). DMA2 Channel 0 provides the cascade interconnection for the two DMA devices.

This arrangement is used to maintain IBM PC AT bus compatibility as documented by the IEEE P996 specification. The DMA functions are arbitrated by internal logic and will gain control of the Local Bus as a Temporary Bus master. To facilitate this operation, the HT321 utilizes the HOLD/HLDA protocol of the microprocessor.

# HTK340 Shasta 486 Chip Set

The DMA Controller is clocked via one of two sources:

i) for AT-Compatibility, the DMA Controllers can be clocked with BCLK/2 (4 MHz),

or

ii) for systems requiring greater DMA performance, the DMA Controller can be clocked by BCLK (8 MHz).

The clock for the DMA Controllers is selected via INDEX 06 of the HT321. INDEX 06 also controls the DMA Wait States. The option ranges from 0 to 3 additional Wait States inserted into any DMA cycle generated. For AT-Compatibility, the setting should be at 1 Wait State.

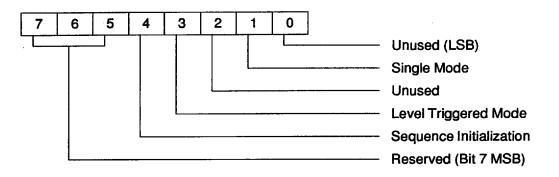

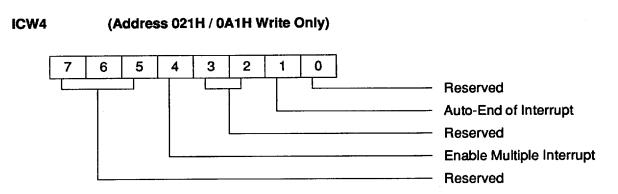

#### Interrupt Controller

The HT321 incorporates two programmable Interrupt Controllers that are functionally compatible to an Intel 8259A. The controllers accept Interrupt Requests from Peripherals, resolve Priority between pending interrupts and interrupts in service, issue an interrupt request to the CPU and supply a vector which is used as an index by the CPU to select the service routine to execute.

A variety of Priority Assignment Modes is provided, which may be changed at any time during system operation to allow the complete interrupt subsystem to be restructured based on the Operating System requirements. The controllers are cascaded in a fashion compatible with the IBM PC AT and the IEEE AT Bus P996 Specification.

The table below shows typical interrupt levels assigned for an AT-compatible I/O bus.

The two devices are coupled in chain fashion by connecting the interrupt output of Programmable Interrupt Controller 2

(PIC2) to the interrupt request input 2 of PIC1. To ensure that all 16 interrupt channels operate correctly in this arrangement, all channels must be programmed to operate in Cascade Mode. PIC1 is located at addresses 020H-021H and is configured for Master operation in Cascade Mode. PIC2 is a Slave device and is located at addresses 0A0H - 0A1H(see definitions below). The address location and Cascade interconnection provides compatibility with the IEEE AT Bus P996 Specification.

Two additional connections are made to the interrupt request inputs of PICs 1 and 2. The output of Timer 0 in the Counter/Timer Megafunction is connected directly to the input of Channel 0 (IRQ) of PIC1 and does not have an external connection. In a standard AT system implementation, IRQ1 is reserved exclusively for the Keyboard Output Buffer Full Flag. Therefore, the input pin for this interrupt has been named OPTBUFUL, or Output Buffer Full, and should only be used as an input from a Keyboard Controller. IRQ8 differs from the other IRQ's in that it has an inverter between the input pin and PIC2.

### **HT321 Functional Description**

| Interrupt | System<br>Functions                                         | I/O Bus       |  |  |

|-----------|-------------------------------------------------------------|---------------|--|--|

| NMI       | Parity Check                                                | I/OCHCK       |  |  |

| IRQ0      | Timer                                                       | Not Available |  |  |

| IRQ1      | Keyboard                                                    | Not Available |  |  |

| IRQ3      | Serial Port 2                                               | Available     |  |  |

| IRQ4      | Serial Port 1                                               | Available     |  |  |

| IRQ5      | Parallel Port 2                                             | Available     |  |  |

| IRQ6      | Floppy Disk                                                 | Available     |  |  |

| IRQ7      | Parallel Port 1                                             | Available     |  |  |

| IRQ8      | Real Time Clk                                               | Not Available |  |  |

| IRQ9      | Not Used                                                    | Available     |  |  |

| IRQ10     | Not Used                                                    | Available     |  |  |

| IRQ11     | Not Used                                                    | Available     |  |  |

|           | Typical System Interrupts and AT-<br>compatible I/O Channel |               |  |  |

#### **Programmable Interval Timer**

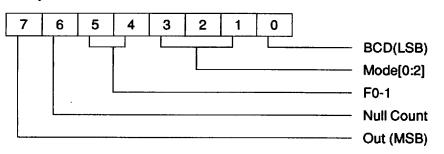

The HT321 integrates a Programmable Interval Timer (PIT), which is functionally equivalent to an Intel 8254 Programmable Interval Timer/Counter. The PIT is programmable through internal I/O ports located at 0040H through 0043H.

The Clock inputs of the three channels are driven by a 1.19 MHz clock, which is internally generated by dividing the oscillator input (OSC P160 14.31818 MHz) by 12. The outputs of the three channels are as follows:

Channel 0 is a general purpose and software interrupt timer. The output of this channel is connected directly to the IRQ0 pin of the integral Programmable Interrupt Controller (PIC1). (see

755-0017-01 Rev.2

the Interrupt Controller Functional Description)

- The output of Channel 1 is used internally by the HT321 to generate refresh requests.

- The output of Channel 2 provides for tone generation for a speaker. The HT321 presents this signal as SPeaKeR (SPKR P78).

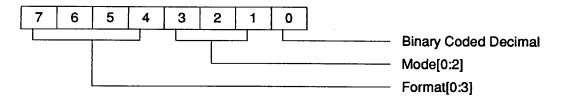

#### **Programmable Timer Control**

The Programmable Interval Timer (PIT) in the HT321 is general purpose and can be used to generate accurate time delays under software control. The PIT contains three 16bit counters (Counter[0:2]) which may be programmed as Binary or Binary Code Decimal (BCD) counters. Each counter operates independently of the other two and each can operate as a Timer or Counter.

# HTK340 Shasta 486 Chip Set

The counters have common control logic that decodes control information written to the PIT and has the necessary controls to load, read, configure and direct each counter. Counter 0 and Counter 1 can be programmed for all six modes, but Mode 1 and Mode 5 have limited usefulness due to the lack of an external hardware trigger signal. Counter 2 can be operated in any of six modes listed below.

- Mode 0 Interrupt on terminal count

- Mode 1 Hardware re-triggerable one-shot

- Mode 2 Rate generator

- Mode 3 Square wave generator

- Mode 4 Software triggered strobe

- Mode 5 Hardware re-triggerable strobe

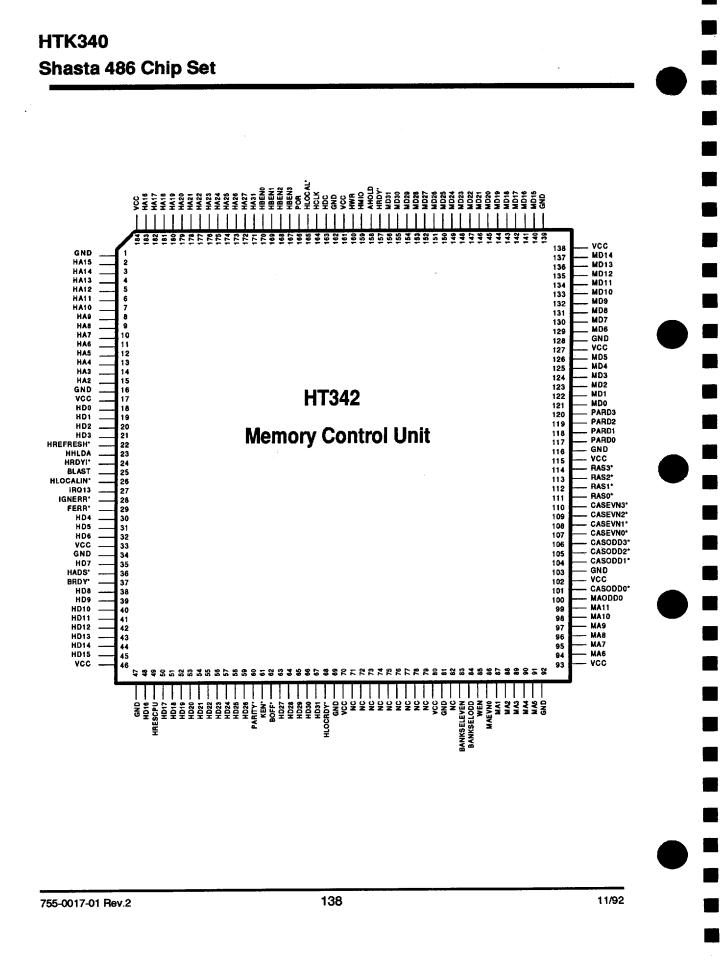

#### Introduction

The HT342 is a high performance, pipelined DRAM controller and Write Buffer. The Controller interfaces to '486 Systems with minimum support logic. The Controller conforms to the Local Bus Specification.

The primary purpose of the HT342 Memory Control Unit (MCU) is to provide the interface to DRAM for the Shasta system. Two other non-memory related functions have also been assigned to the chip: the AT-compatible numerical error reporting and 16-bit cycle data bridging.

A 4-level write buffer facilitates 0 wait state write cycles as long as the write buffers are not full. A superior set of DRAM control algorithms have been defined that effectively utilize pipelined techniques and optimize zero wait state performance, even during write cycles on a page hit at maximum operating frequencies. This, combined with write buffering, effectively make all write cycles 0 wait state.

At lower operating frequencies the DRAM control section of the HT342 allows a 3-1-1-1 486 burst read cycle sequence during DRAM page hits in a CAS interleaved paging configuration. When the clock rate is higher, and the DRAM access times do not meet the 3-1-1-1 burst cycle timing requirements, a special data pipe can be activated relaxing the DRAM access time constraints. In this case 4-1-1-1 burst cycle can be achieved and save 3 wait states over 4-2-2-2 burst cycle timing.

Because of the 486 CPU bus specification, 16-bit cycles on the Local Bus require data bridging. The HT342 MCU controller provides the necessary circuitry. No extra logic is necessary for 16-bit device support. This is especially important because the HT321 ISA controller and some local bus VGA controllers (like the HT216) are 16-bit devices. The HT342 MCU allows these

### **HT342 Functional Description**

devices to be connnected to the Local Bus with no external bridging buffers.

Outlined below are the major features of the controller:

- One 184 pin PQFP package.

- 1 micron HCMOS Technology.

- Fully static operation: 0-33MHz CPU speeds.

- Shasta architecture compatible.

- LIM EMS 4.0 support.

- Separate Data Bus for DRAMs and Local Bus.

- Parity generation, detection and reporting.

- 256K, 1MB, 4MB, 16MB DRAM type support.

- Up to 256MB total addressability (4 banks of 16Mb DRAMs).

- Shadowing in 16KB increments between 640KB and 1MB.

- Up to 384KB of memory, from 640KB to 1MB, may be remapped above the main memory limit. Re-mapping coexists with Shadowing, meaning any remaining unshadowed DRAM may be re-mapped above the main memory limits.

- 1, 2, 4-way CAS interleave with fast paging.

- Middle BIOS support enable/disable.

- Programmable 26 Non-Cacheable regions.

- Refresh hidden from the system.

- CAS before RAS or RAS only Refresh.

- RAS staggering during Refresh.

- Programmable Timing Parameters for DRAM access.

- Read and Write Cycle Timing independently programmable.

755-0017-01 Rev.2

#### HTK340

Shasta 486 Chip Set

- 3-1-1-1 486 burst rate during DRAM page hits while interleaving.

- Data pipe relaxing DRAM timing constraints at higher clock rates, potential saving of 3 wait states with a 4-1-1-1 burst cycle.

- 4 deep double-word write buffering.

- Byte gathering support.

- Out of order operation (reads propagate ahead of writes if there is no hit in the write buffers).

- Ability to respond from within the write buffer for a Write Buffer Read Hit.

- AT-compatible floating point error reporting.

### Architecture

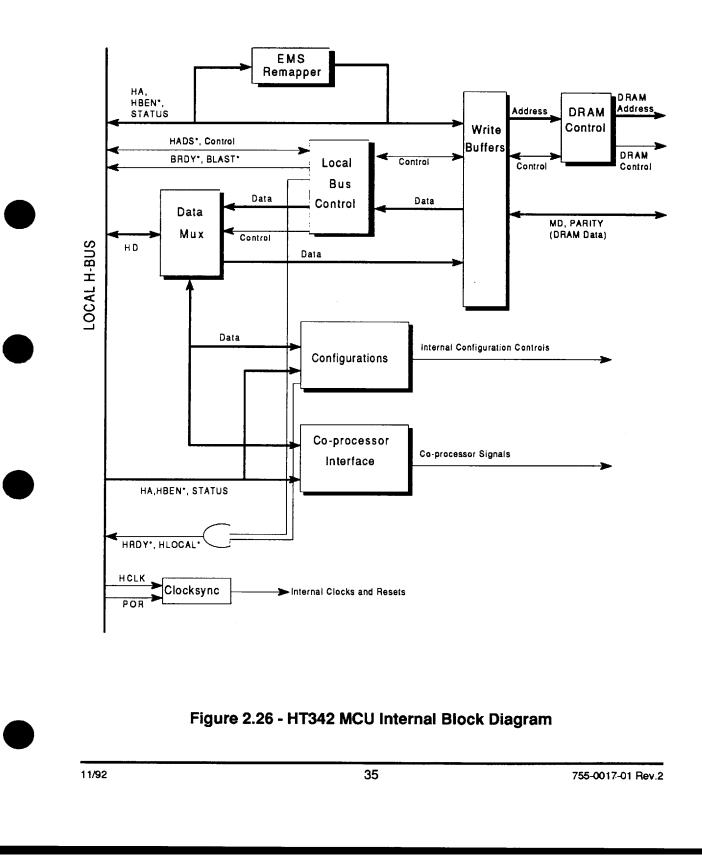

The HT342 has three major operational sections: Local Bus Controller, Write Buffers and a DRAM Controller implementing complete DRAM Control functions. These three major modules, which are shown in the Block Diagram on Page 34, are called L O C A L \_ B U S \_ C O N T R O L L E R, WRITE\_BUFFERS and DRAM\_CONTROL-LER respectively. The LOCAL\_BUS\_CON-TROLLER provides DRAM cycle recognition, EMS and Remap cycle handling, 16-bit data bridging and burst read data pipe.

The WRITE\_BUFFERS and DRAM\_CON-TROLLER are organized in a pipelined fashion. The WRITE\_BUFFERS module generates cycles for the DRAM\_CONTROL-LER module as a stage of the pipeline. These mega-modules are distinct and independent entities. Their functions are described below.

#### **Local Bus Controller**

The first task of this module is to qualify cycles. The module samples decodes from the DRAM\_DECODER module, and the HLOCALI\* input. The following cycles are

### **HT342 Functional Description**

qualified by the module as the HT342 MCU cycles:

- regular memory DRAM cycles. These cycles are passed immediately by the LOCAL\_BUS\_CONTROLLER to the WRITE\_BUFFERS module.

- two of the 486 special cycles : flush and write back. These cycles are terminated by the LOCAL\_BUS\_CONTROLLER.

The following cycles require special attention and are described in detail:

- non-DRAM and non-special CPU read cycles for which HLOCALI\* is sampled de-asserted and HBEN1\* and HBEN0\* are BOTH negated;

- non-DRAM and non-special CPU write cycles, for which HLOCALI\* is sampled de-asserted, and HBEN1\* and HBEN0\* are BOTH negated.

These cycles are assumed by the HT342 to be directed toward 16-bit devices. The read cycles are not terminated by the HT342 MCU controller, but the read bridging is performed. The bridging during the read cycles is necessary, because the 486 processor expects the read data on the data bus lines (HD[31:0] bus) associated with the byte enables (HBEN\*[3:0]) activated during the cycle. This occurs regardless of the bus sizing information supplied with the BS16 signal. Although the CPU knows that a 16-bit device does not have the upper 16 bit data bus connected, it still expects to see the data there. Therefore the bridging is necessary for all memory and I/O read cycles directed to 16bit devices, when the HBEN1\* and HBEN0\* signals are negated. When any one of the signals is asserted, and the cycle is directed to a 16-bit device, the CPU reads the data associated with the HBEN1\* and/or HBEN0\* first, and then repeats the cycle (if necessary) with the HBEN1\* and HBEN0\* negated. This second, repeated cycle requires bridging of

755-0017-01 Rev.2

the data returned by the 16-bit device. The HT342 MCU controller reads the data on the lower part of the data bus (HD[15:0]), and mirrors it on the upper one (HD31:16).

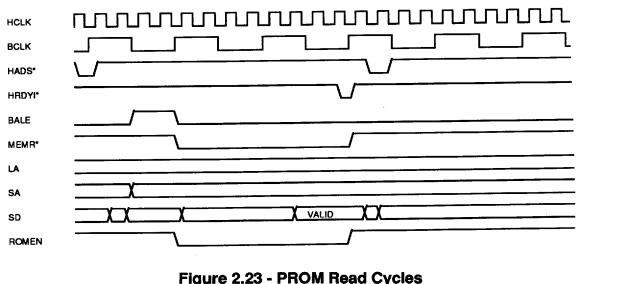

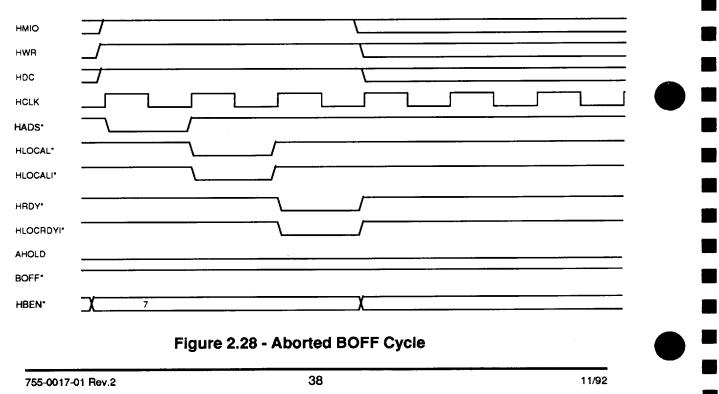

An even more complicated process takes place during write cycles to 16-bit devices. The 486 CPU does not mirror the upper 16 bits of the data bus on the lower 16 bits, when performing a write cycle with both HBEN\*1 and HBEN\*0 signals negated. Therefore a 16bit device cannot read the data, since it does not have access to the upper 16 bits of the data bus. What makes things even worse, the 486 CPU still drives the lower 16 bits of the data bus with some invalid data. A complex set of data buffers would be needed to bridge the data during these cycles. The HT342 MCU controller takes care of the problem in an unusual way. The controller samples the write bridging condition and determines if the cycle is directed to a 16-bit device by sampling the HLOCALI\* one clock after the HADS\*. If the HLOCALI\* is asserted, the cycle is assumed to be directed to a 32-bit local device and no action is taken. Otherwise the cycle is taken over by the MCU controller by asserting the HLOCAL\* signal, and a BOFF\* cycle is requested. At the same time the address and the write data from the CPU is stored internally and the cycle is terminated. One clock after the BOFF\* is asserted, the CPU releases the entire Local Bus. The HT342 starts driving the bus one clock later and it repeats the stored cycle with the HD[31:16] lines mirrored on HD[15:0] lines. In this way the HT342 acts as a local bus master and emulates the behavior of the 386 CPU for the write cycles directed toward 16bit devices. The overhead involved is minimum. There is a 6 clock penalty for these cycles. These cycles are usually much slower anyway (most of them are backplane cycles). The LOCAL\_BUS\_CONTROLLER is the module controlling BOFF cycles. Fig. 2.27 illustrates a BOFF\* cycle. The AHOLD and BOFF\* signals are used to take control of the Shasta Local Bus. The second cycle is generated by the HT342 MCU controller and

# HTK340 Shasta 486 Chip Set

the HD[31:16] part of the data bus is duplicated on the HD[15:0]. Fig. 2.28 shows an aborted BOFF\* cycle. The HT342 does not initiate a BOFF\* cycle after HLOCALI\* is asserted.

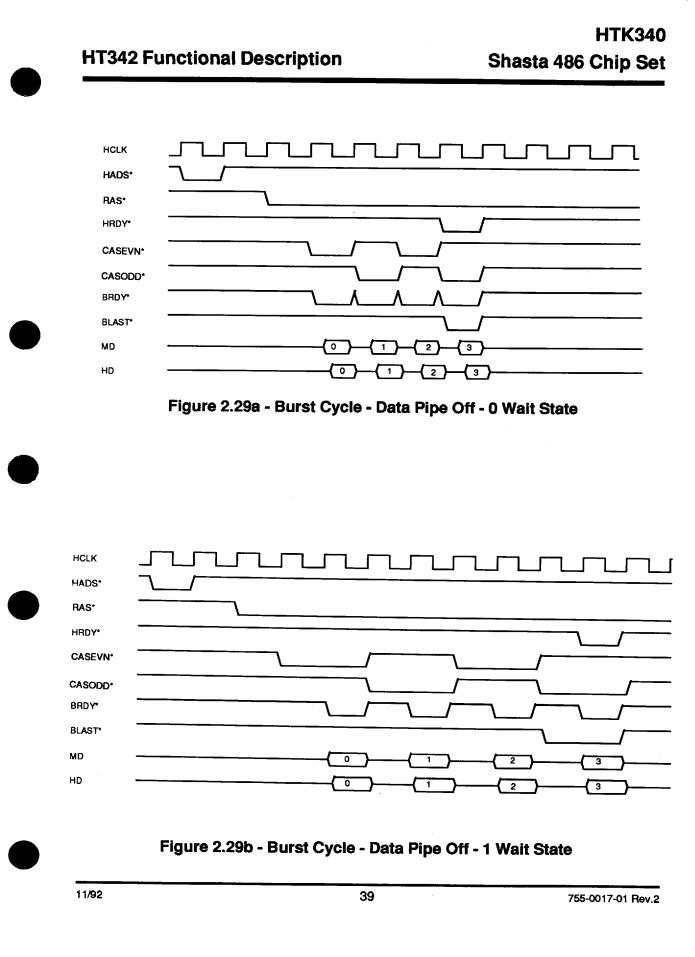

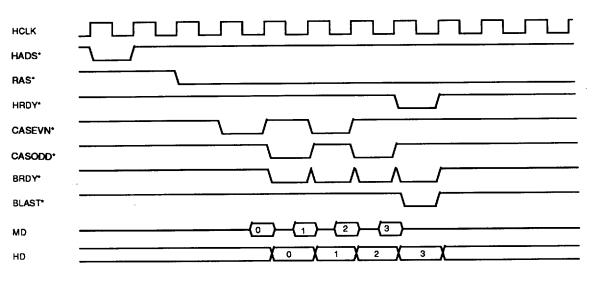

Another function of the LOCAL BUS CON-TROLLER is the control of burst DRAM cycles. The HT342 MCU controller always bursts cacheable DRAM read cycles. BRDY\* is generated while bursting and HRDY\* terminates the last cycle in the burst sequence. Fig. 2.29a shows a fastest possible sequence of a read burst cycle. This sequence occurs on a DRAM page hit, with the CAS active time during read set to 1 HCLK, and interleave option turned on, no CAS delays, no bus recoveries, etc.. The data pipe is not enabled. A 3-1-1-1 burst is performed. Fig. 2.29b shows the same cycle with 1 wait state added to every CAS cycle. The CAS active time has been set to 2 HCLK. This happens usually at higher operating frequencies, when the CAS access time of 1 HCLK is too short. In this case a 4-2-2-2 burst is performed. Possible advantages of the data pipe are shown by Figure 2.30. When the pipe is disabled, the data coming back from the DRAM has to go through the HT342 MCU controller, heavily loaded Local Bus, and then meet the CPU setup requirements. By enabling the pipe, the only requirement the DRAM data has to meet is setup on the MD bus of the HT342. This relaxes the timing significantly, especially at higher operating frequencies. The 4-2-2-2 burst sequence shown in Fig. 2.29b can be shrunk down to 4-1-1-1, when the data pipe is enabled as shown by Fig. 2.30.

The last function of the LOCAL\_BUS\_CON-TROLLER is to control the DRAM cycles in the EMS and Remap cases. Whenever an EMS or Remap translation is required, a wait state is added to the cycle in order to allow time for MA lines calculation.

# HTK340

**HT342 Functional Description**

# Shasta 486 Chip Set

| ю        | X VALID     | VALID Repeated                 |

|----------|-------------|--------------------------------|

| R        |             |                                |

| <b>c</b> | VALID X     | X VALID Repeated               |

| ĸ        |             |                                |

| DS*      | <b>\</b>    |                                |

| CAL.     |             |                                |

| CALI*    |             |                                |

| 31:16    | X AA55      | X AA55                         |

| 15:0     | X xxxx X    | X AA55                         |

| )Y•      |             | //                             |

| DLD      | /           |                                |

| ·F·      |             |                                |

| IN*      | <b>X</b> 7  | 7 Repeated                     |

|          | X ADDRESS X | ADDRESS Repeated               |

|          | 80486 CYCLE | HT342 16-Bit Data Bridge CYCLE |

### Figure 2.27 - BOFF Data Bridge Cycle

# HTK340

Shasta 486 Chip Set

**HT342 Functional Description**

Figure 2.30 - Burst Cycle - Data Pipe On - 0 Wait State

#### Write Buffers

One of the major functions of the HT342 is buffering of write data. The module WRITE\_BUFFERS controls cycles on the DRAM\_CONTROLLER local bus.

Whenever one of the write buffers fills, the WRITE\_BUFFERS module starts its unload sequence by generating cycles on the DRAM\_CONTROLLER local bus. Write cycles from the module are always FIFO.

An important feature of the WRITE\_BUF-FERS module is byte gathering. This feature checks if data being written to the WRITE\_BUFFERS happens to be a 'Write Buffer Write Hit' (an address match for the data of the cycle occurs for data already in the WRITE\_BUFFERS, queued for unload) then the data will be directed to the write buffer where the match occurred. Multiple hits are impossible. This aligns with the 16-bit nature of current software written for '286 machines to be run on Shasta '486 Systems.

Another feature of the WRITE\_BUFFERS module is out of order operation. Any read

cycle will be processed before any write unload cycle, eliminating slow down by the collision of cache read miss cycles with latency of the write buffer unloads. This feature is tightly coupled with another feature of the WRITE\_BUFFERS, which is an ability to respond from its buffers to a Write Buffer Read Hit. Typically, for Write Buffer Read Hits only a part of the data requested is present in the write buffer; the remainder is fetched from the DRAM.

# **HT342 Functional Description**

#### DRAM\_CONTROLLER

The third major unit of the HT342 is the DRAM\_CONTROLLER. This unit provides all DRAM control algorithms.

The DRAM\_CONTROLLER supports up to 4 banks of DRAM memory of 256KB, 1MB, 4MB and 16MB types. Any combination of these types of DRAM memory may be used, meaning it is possible to install any type of DRAM in any bank. From one to four banks may be used. This provides for unlimited flexibility of system upgrade. The DRAM\_CONTROLLER supports programmable 2-way or 4-way CAS interleave. It is possible to select 2-way interleaving between two lower banks and between two upper

#### A. No Interleave

# HTK340 Shasta 486 Chip Set

banks, or between lower and upper banks. For 4-way interleave, all 4 banks must be installed. The interleaved banks must be populated by the same type of DRAMs. The HA2 address line determines 2-way CAS interleave. HA2 and HA3 are used for 4-way interleave.

Fast paging is also supported by the DRAM\_-CONTROLLER. Internal Pipelined Local Buses between the WRITE\_BUFFERS and DRAM\_CONTROLLER have bursting capability.This technique along, with the CAS interleaved scheme of DRAM control, provides faster burst cycles.

The tables below describe mapping of the HA to MA lines :

| MA          | 0   | 1   | 2   | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   |

|-------------|-----|-----|-----|------|------|------|------|------|------|------|------|------|

| CAS Address | HA2 | НАЗ | HA4 | HA5  | HA6  | HA7  | HA8  | HA9  | HA10 | HA11 | HA12 | HA13 |

| RAS Address | x   | Υ   | z   | HA14 | HA15 | HA16 | HA17 | HA18 | HA19 | HA20 | HA21 | HA22 |

| where: | X    | Y    | z    |                |

|--------|------|------|------|----------------|

|        | HA11 | HA12 | HA13 | for 256K DRAMs |

|        | HA12 | HA13 | HA21 | for 1M DRAMs   |

|        | HA13 | HA22 | HA23 | for 4M DRAMs   |

|        | HA23 | HA24 | HA25 | for 16M DRAMs  |

# HTK340

# Shasta 486 Chip Set

**HT342 Functional Description**

# **B. 2-way Interleave**

| MA          | 0   | 1   | 2   | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   |

|-------------|-----|-----|-----|------|------|------|------|------|------|------|------|------|

| CAS Address | НАЗ | HA4 | HA5 | HA6  | HA7  | HA8  | HA9  | HA10 | HA11 | HA12 | HA13 | HA14 |

| RAS Address | x   | Y   | z   | HA15 | HA16 | HA17 | HA18 | HA19 | HA20 | HA21 | HA22 | HA23 |

| where: | x    | Y    | z    |                |

|--------|------|------|------|----------------|

|        | HA12 | HA13 | HA14 | for 256K DRAMs |

|        | HA13 | HA14 | HA22 | for 1M DRAMs   |

|        | HA14 | HA23 | HA24 | for 4M DRAMs   |

|        | HA24 | HA25 | HA26 | for 16M DRAMs  |

# C. 4-way Interleave

| МА          | 0   | 1   | 2   | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   |

|-------------|-----|-----|-----|------|------|------|------|------|------|------|------|------|

| CAS Address | HA4 | HA5 | HA6 | HA7  | HA8  | HA9  | HA10 | HA11 | HA12 | HA13 | HA14 | HA15 |

| RAS Address | x   | Y   | z   | HA16 | HA17 | HA18 | HA19 | HA20 | HA21 | HA22 | HA23 | HA24 |

| where: | x    | Y    | z    |                |

|--------|------|------|------|----------------|

|        | HA13 | HA14 | HA15 | for 256K DRAMs |

|        | HA14 | HA15 | HA23 | for 1M DRAMs   |

|        | HA15 | HA24 | HA25 | for 4M DRAMs   |

|        | HA25 | HA26 | HA27 | for 16M DRAMs  |

755-0017-01 Rev.2

11/92

# **HT342 Functional Description**

RAS only or CAS before RAS Refresh methods are supported. Internal refresh counters generate refresh addresses during RAS only refresh. The RAS signals during refresh can be staggered.

A powerful set of Timing Options has been implemented, allowing the user to adjust timing to suit specific system and DRAM speeds:

a) RAS delay - 0 or 1 HCLK (Index 27H, Bit 7)

Selects MA setup time on RAS. For zero RAS delay setup time becomes 1 HCLK +/-system and internal delays. For 1 RAS delay the setup time is 1 HCLK longer.

b) CAS delay - 1 or 2 HCLK (Index 26H, Writes Bit 4, Reads Bit 3)

This parameter defines RAS to CAS delay. Switching MA lines from RAS to CAS Address always occurs in the middle of the delay. This parameter controls MA setup time to CAS, and MA hold time for RAS.

Separate CAS delay for read and write may be defined. This is possible because while paging write cycles are pipelined, the setup time for MA to CAS during a page hit is improved significantly compared to read cycles.

c) RAS Active time on Reads 2 to 9 HCLK in one clock increments. (Index 27H, Bits 4-2)

> This parameter is determined by DRAM Specification of Read access time from RAS.

d) RAS Active time for Writes 2, 3, 4 or 5 HCLK. (Index27H, Bits 6-5)

This parameter is determined by DRAM minimum RAS width specification.

# HTK340 Shasta 486 Chip Set

- e) RAS precharge time 1 to 4 HCLK (Index 27H, Bits 1-0)

- f) CAS active time on reads-1 to 4 HCLK (Index 26H, Bits 1-0)

Determined by DRAM specification of read access time from CAS.

g) CAS active time on writes-1 to 2 HCLK (Index 26H, Bit 2)

Determined by DRAM specification of minimum CAS width and CAS data hold time on CAS.

- h) CAS precharge 0.5 or 1 HCLK (Index 26H, Bit 6)

- i) Bus Recovery time 0, 0.5 or 1 HCLK (Index 2DH, Bits 1-0)

This parameter affects back to back CAS signals switched to alternate banks when interleaving is enabled. If there is no Recovery time specified the CAS signals will happen back to back while bursting. Specifying a Recovery time creates the inactive delay required for all CAS signals between consecutive Dword fetches.

j) First CAS burst read delay - 0 or 1 HCLK (Index 26H, Bit 5)

> One more wait state will be inserted during the first cycle of a burst during a page hit on a read miss cycle. This parameter is determined by the DRAM specification of address access time during a page hit.

k) CAS Hold on RAS - 1 or 2 HCLK (Index 26H, Bit 7)

> Applies to CAS before RAS Refresh timing. Sets the delay between the RAS being activated and CAS deactivated during the cycle.

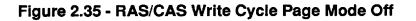

Figures 2.34 and 2.35 illustrate basic RAS/CAS Read and Write Cycles with paging disabled. The differences are: WEN is not activated during a Read Cycle and the

# **HTK340**

# Shasta 486 Chip Set

timing control parameters are from separate configuration registers. tRAR/tRAW parameters refer to RAS active time on Reads/Writes (respectively), tCDR/tCDW to CAS delay on Reads/Writes, tCAR/tCAW to CAS active time on Reads/Writes, and TRP to RAS precharge.

Figure 2.31 illustrates the basic RAS/CAS Cycle with paging and no interleave. The TCP parameter refers to CAS precharge. BANKSELEVN (BANKSELODD) signals are stable throughout the cycle.

Figure 2.32 illustrates the basic RAS/CAS Cycle with Paging and 2-way Interleave. BANKSELEVN and BANKSELODD are stable throughout the cycle. The figure shows consecutive dwords accessed in an interleaved fashion with the HA2 Address line as the Interleave control. TBR refers to the Bus Recovery parameter described above.

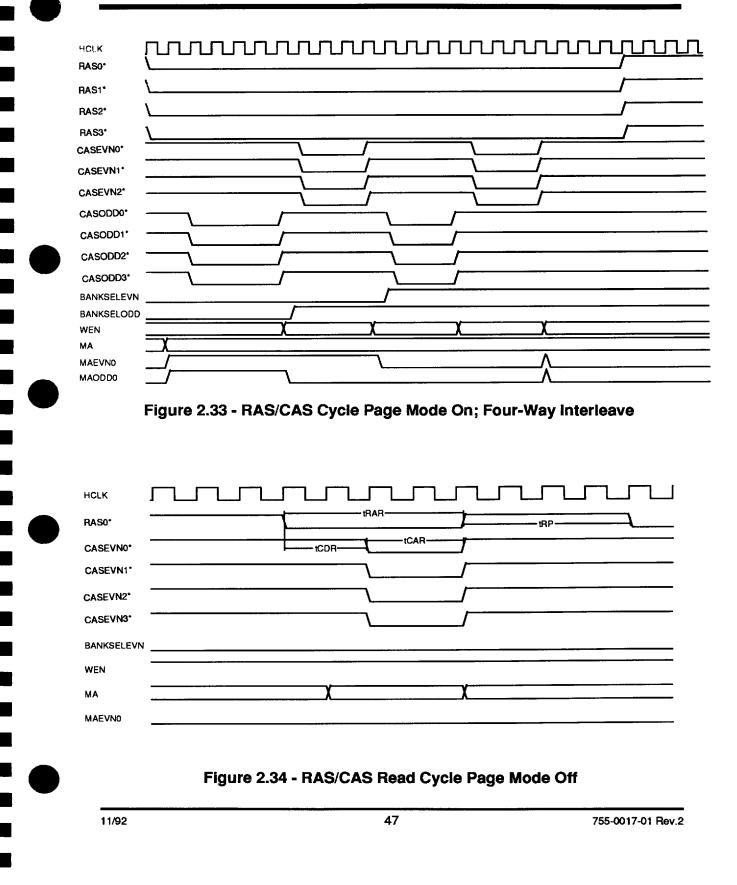

Figure 2.33 illustrates the basic CAS/RAS cycle with Paging and 4-way Interleave. BANKSELEVN and BANKSELODD are controlling CAS activation. There is always at least a half HCLK Setup and Hold time provided when switching CASEVN\* and CASODD\* between banks. The figure shows consecutive Dwords accessed in an interleaved fashion with HA2/HA3 as the interleave controls.

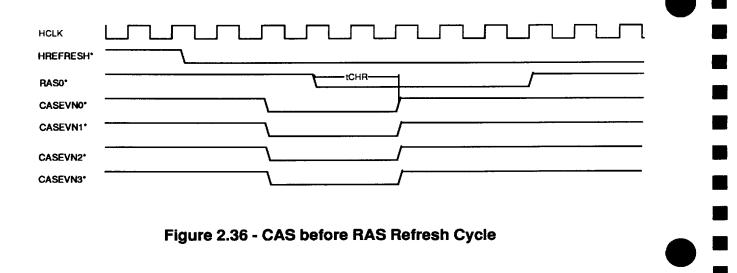

Figure 2.36 illustrates the CAS before RAS Refresh Cycle. tCHR refers to the minimum timing parameter of CAS Hold on RAS described above, while figure 2.37 illustrates the RAS-only Refresh Cycle. The width of the RAS signal during refresh cycles is determined by tRAW. The width of the CAS signals during CAS before RAS refresh is determined by tCHR and tCAW.

# **HT342 Functional Description**

#### **Co-processor Interface**

This module implements the AT compatible numerical error reporting. Fig. 2.38 illustrates the timing. Upon sampling the FERR\* line asserted, the IRQ13 interrupt is generated. An I/O write to F0h clears the IRQ13 request. At the same time IGNERR\* signal is asserted and remains active until FERR\* line is negated.

#### **Clock Sync**

This module generates internal clocks and resets for the HT342.

#### **DRAM Decoder**

The purpose of this module is to generate an internal signal called DRAM\_SPACE. This signal determines whether a cycle is targeted at the DRAM subsystem controlled by the HT342. It is exclusively resolved when HADS\* is sampled as asserted.

#### Data Mux

This module provides multiplexing of the output data. The multiplexing occurs between data being read from configuration registers and data from the DRAM memory. The module also bridges data bytes during DMA cycles, if the necessity arises. (This occurs because the HT321 is a 16-bit device and it is the only source of DMA cycles). The bridging appears between lower (HD[0:15]) and upper (HD[16:31]) data bits. The bridging occurs also during cycles targeted to a 16-bit device. The bridging is controlled by the LOCAL\_BUS\_CONTROLLER.

755-0017-01 Rev.2

44

# **HT342 Functional Description**

#### Ems Remapper

EMS\_REMAPPER is an address translator which changes the current host's Local Bus addresses (HA lines) into physical DRAM subsystem addresses. These addresses reflect the remapping and EMS support schemes. Essentially, the DRAM subsystem is viewed as a contiguous memory. During remapping (if the remap function is enabled) the EMS\_REMAPPER changes the host request at some high address above DRAM space to one of the EMS pages (16K memory chunks between 640KB and 1MB address space). For the EMS support, an EMS page address is changed to a high memory (but existing in the DRAM subsystem) address according to an offset loaded by the user in the configuration registers.

#### Configurations

This module combines all configuration registers which provide the programmability of the HT342. These registers are defined in the HT342 Register descriptions in this data book.

11/92

HTK340 Shasta 486 Chip Set

| K340<br>asta 486 Chip Set | HT342 Functional Description       |

|---------------------------|------------------------------------|

|                           |                                    |

|                           |                                    |

|                           |                                    |

| Figure 2.31 - RAS/CAS     | Cycle Page Mode On; Interleave Off |

|                           |                                    |

|                           |                                    |

|                           |                                    |

|                           |                                    |

|                           |                                    |

|                           |                                    |

# HTK340

Shasta 486 Chip Set

CASEVN1\* CASEVN2\* CASEVN3\*

BANKSELEVN

WEN MA MAEVNO

755-0017-01 Rev.2

# HTK340 Shasta 486 Chip Set HT342 Functional Description

11/92

48

| LS | I | LOGIC | CORP/HEADLAND | 55E | D |  | 4367702 | 0002799 | T92 | HTI |

|----|---|-------|---------------|-----|---|--|---------|---------|-----|-----|

|----|---|-------|---------------|-----|---|--|---------|---------|-----|-----|

| HCLK<br>HREI<br>RASC<br>CASE<br>CASE<br>CASE<br>CASE<br>MA<br>MAEV | -RESH* \         |          |                                                                                                                                                                                                                                                                                            |             |  |

|--------------------------------------------------------------------|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| CASE<br>MA                                                         | VN3.             |          |                                                                                                                                                                                                                                                                                            |             |  |

|                                                                    | N0               | XX       |                                                                                                                                                                                                                                                                                            |             |  |

|                                                                    |                  | Figure 2 | .37 - RAS-only Re                                                                                                                                                                                                                                                                          | fresh Cycle |  |

|                                                                    |                  |          |                                                                                                                                                                                                                                                                                            |             |  |

|                                                                    | HCLK<br>FERR*    |          | <b>[</b> ] -)( <b>[_</b> )()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()()(_)( |             |  |

|                                                                    | IRQ13<br>IGNERR* |          |                                                                                                                                                                                                                                                                                            |             |  |

|                                                                    |                  | Figure   | e 2.38 - AT Error F                                                                                                                                                                                                                                                                        | leporting   |  |

# **HT321 Register Descriptions**

# **HT321 Register Descriptions**

The HT321 chip has a total of 32 INDEX locations mapped into INDEX 00 - 1FH. Only the bits mentioned in this text should be programmed. All unused register bits should be left at default to maintain future compatibility.

The HT321 chip is also responsible for holding the current INDEX Pointer Value even when the Target Value is external to the HT321. Any access to I/O location 28H (CNFGASLO) is therefore terminated by the HT321. The data read at this location is made available to the CPU.

To program the INDEX registers, one must execute the following procedure:

- i) Write I/O Location 28H with Value = INDEX (00 1FH for HT321)

- ii) Write to I/O Location 24H with Control Value for the selected INDEX

To Read INDEX registers, execute the following procedure:

- i) I/O Write Location 28H with Value = INDEX (00 1FH for HT321)

- ii) I/O READ Location 24H Control Value of selected INDEX is presented

To read the INDEX pointer value, one must execute the following procedure:

i) I/O READ Location 28H - INDEX ADDRESS (lower byte) presented

When an INDEX pointer is written to I/O location 28H, the pointer remains until another I/O write to 28H. This allows multiple DATA accesses at the INDEXed register.

At POR the INDEX pointer will default to INDEX 00H.

The remaining Indices are organized in the following fashion:

# **HT321 Register Descriptions**

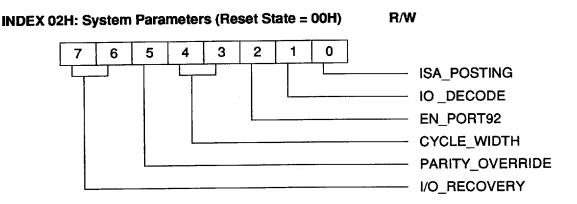

|   | Bit(s) | Value     | Meaning                 |                      |

|---|--------|-----------|-------------------------|----------------------|

|   | 0      | 0         | POSTED Backplane M      | EMWN cycles disabled |

|   |        | 1         | POSTED Backplane M      | EMWN cycles enabled  |

|   | 1      | 0         | 10-Bit I/O decoding er  | nabled               |

|   |        | 1         | 16-Bit I/O decoding er  | nabled               |

|   | 2      | 0         | PORT 92 Functionality   | disabled             |

|   |        | 1         | PORT 92 Functionality   | enabled              |

|   | 4:3    | 00        | Backplane Cycle Time    | = 6 BCLK's           |

|   |        | 01        | Backplane Cycle Time    | = 5 BCLK's           |

|   |        | 10        | Backplane Cycle Time    | = 4 BCLK's           |

|   |        | 11        | Backplane Cycle Time    | = 3 BCLK's           |

|   | 5      | 0         | Parity Error Override   | OFF                  |

|   |        | 1         | Parity Error Override   | ON                   |

| * | 7:6    | 00        | I/O Recovery =          | 0 additional BCLK's  |

|   |        | 01        |                         | 1 additional BCLK's  |

|   |        | 10        |                         | 3 additional BCLK's  |

|   |        | 11        |                         | 7 additional BCLK's  |

| ٠ | Note:  | Available | only in Rev. D or later |                      |