# Part I

# 1. SiS85C496/497 Overview

# SiS85C496PCI & CPU Memory Controller (PCM)SiS85C497AT Bus Controller & Megacell (ATM)

The SiS 486-VIP (VESA/ISA/PCI) chips are two-chip solution ideally for Intel's 80486, SL Enhanced 486, P24D/P24T/DX4 CPU, AMD's 486, Enhanced Am486 and Cyrix's Cx486 (M7)/Cx 5x86 CPU based on green AT system. By supporting the most popular industrial standard system interfaces, it provides flexible configurations for system design and applications.

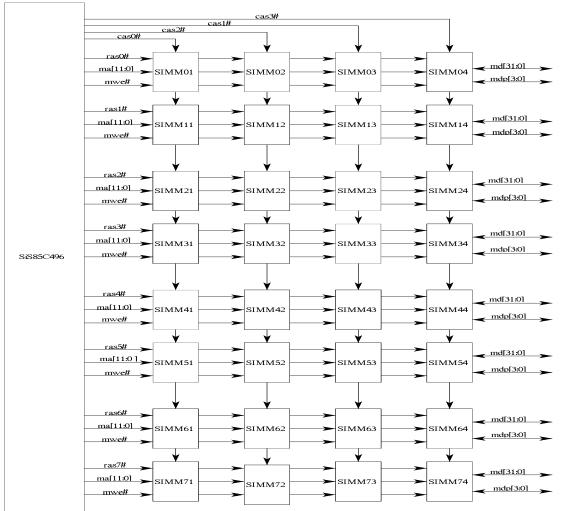

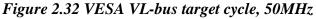

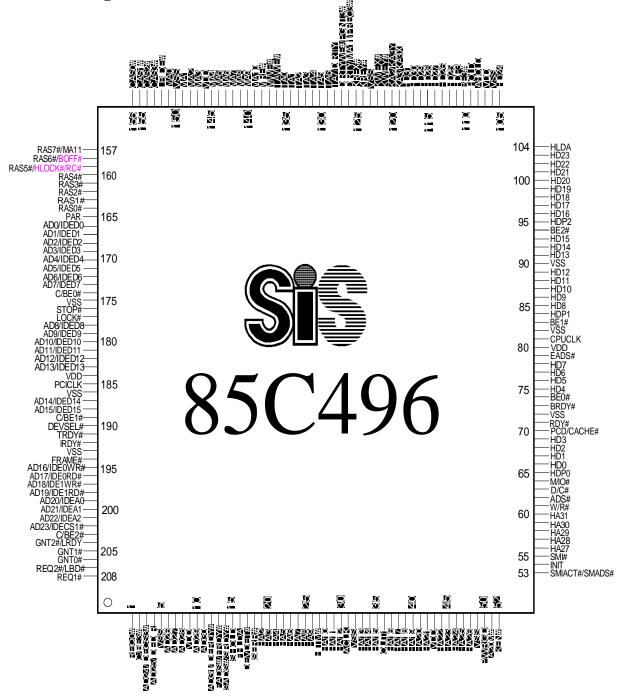

The SiS85C496 PCI & CPU Memory Controller (PCM) integrates the Host Bridge (Host Interface), the cache and main memory DRAM Controller, the PCI Bridge, the built-in IDE Controller, and the FS-Link Bus (Fast Slow Link Bus). It provides the address paths and bus control for transfers among the Host (CPU/L1 cache), main memory (L2 cache and DRAM), the Peripheral Component Interconnect (PCI) Bus, and the FS-Link Bus. The L2 cache controller supports both write-through and write-back cache policies and cache sizes up to 1 MBytes. The cache memory can be built using standard asynchronous SRAMs. The main memory DRAM controller interfaces DRAM to the Host Bus, PCI Bus, and FS-Link Bus. Up to eight single sided SIMMs or four double sided SIMMs provide a maximum of 255 MBytes of main memory. The installation of DRAM SIMMs is "Table-Free", which allows the SIMMs be installed into any slot location and any combinations. The built-in IDE hard disk controller allows CPU accessing hard disk and also provides higher system integration with lower system cost. The 85C496 is intended to be used with the SiS85C497 which is a AT Bus Controller with built-in 206 controller.

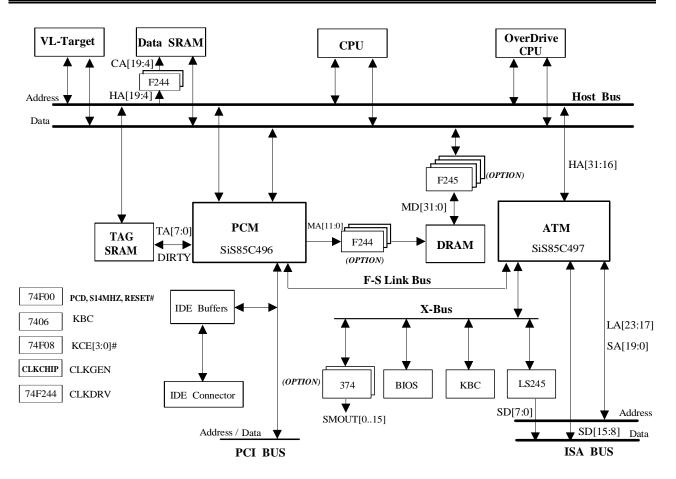

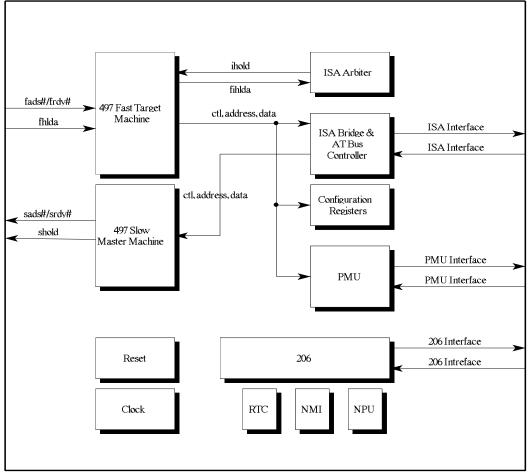

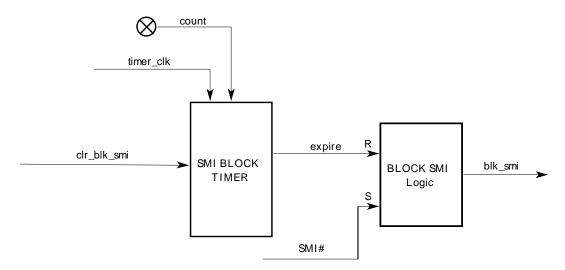

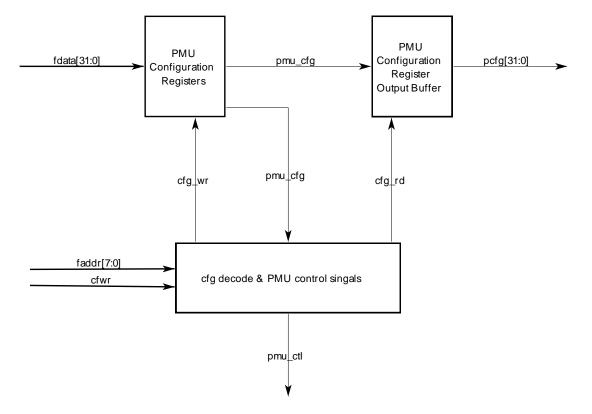

The SiS85C497 AT Bus Controller and Megacells (ATM) provides the interface between PCI/CPU/Memory Bus (fast machine) and the ISA Bus (slow machine). It also integrates many of the common I/O functions in today's ISA based PC systems. The 85C497 comprises the FS-Link interface (Fast-Slow Link interface), ISA bus controller, DMA controller and data buffers to isolate the FS-Link Bus from the ISA Bus and to enhance performance. It also integrates a 14 channel edge/level interrupt controller, refresh controller, a 8-bit BIOS timer, three programmable timer/counters, non-maskable-interrupt (NMI) control logic, Power Management Unit, and RTC. Figure 1.1 shows the system block diagram.

Figure 1.1 SiS85C496/497 System Block Diagram

Silicon Integrated Systems Corporation

# Part II 1. SiS85C496 PCI & CPU Memory Controller

# **1.1 Features**

- Host Bus

- Supports Intel 486, P24D, P24T, DX4, SL-Enhanced 486, AMD 486, Enhanced Am486, and Cyrix M7/Cx 5x86 in 25/33/40/50 Mhz, 5V CPU.

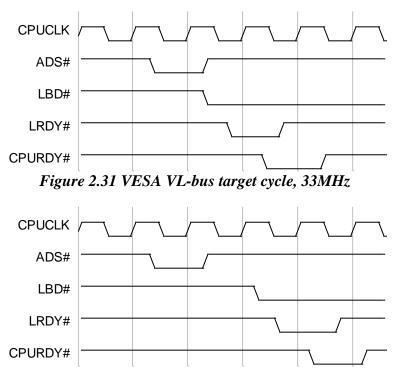

- VESA Bus Slave

- Supports VESA Bus Specification Rev. 2.0p with Local Device Target only.

# • PCI Local Bus

- Supports PCI Bus Specification Rev. 2.0 with up to 4 PCI Masters.

- Implements 3 Level Post Write Buffer for CPU write PCI Target Memory Cycle.

- Supports Back to Back Single Memory Write to PCI Burst Write.

- Supports PCI Interrupt Steering with Four PIRQ Inputs.

- Supports PCI Master Burst Accesses On-Board Memory Up to 64 Double Word Long.

- Supports Concurrency PCI Bus.

- Snoop Filter and Advanced Snooping for Reducing CPU Snoops During Sequential PCI Master Accesses On-Board Memory Cycles.

- Supports PCI Bus PCI to PCI Bridge.

### • Supports L1 Cache Write Back CPU (P24T/P24D/M7/Enhanced Am486) systems

• Supports Cx 5x86 Linear Burst Order Mode.

### • L2 Cache Controller

- Write-Back or Write-Through Schemes

- Bank Interleave/Non-Interleave Cache Access

- Cache Size: 64K/128K/256K/512K/1MB

- 8 bit or 7 bit Tag (Combined Tag and Dirty SRAM) with Direct-Mapped cache organization.

- Optional Separate Dirty SRAM.

# • DRAM Controller

- Supports 8 Banks Non-Interleaved Access for Single and Double Sided SIMMs up to 255 MBytes.

- Supports DRAM CAS Before RAS Refresh.

- Supports "Table-Free" DRAM configuration.

- Programmable driving current for the DRAM signals.

- Supports Symmetrical and Asymmetrical DRAMs.

- Supports 256K/512K/1M/2M/4M/8M/16M/32M xN Fast Page Mode and EDO DRAM.

# • Built-In Local Bus IDE Interface

- Supports Data Conversion for the Double Word Accessing

- Supports Symmetry Configuration for Channel 1 and Channel 0, PIO Mode IDE Hard Disks.

- Supports Mode 3 and above Timing.

- Supports Individual Drive Timing Setting for Optimal Performance.

- Supports Posted Write Buffers and Pre-fetch Buffer.

- Supports Primary IDE or Secondary IDE Addressing (1Fx/17x)

# • Fast-Slow Link Interface

- Linkage to ISA Bridge by FS-Link Interface.

- Fast Access to BIOS, ISA Memory Holes, and Interrupt Acknowledge Cycle by FS-Link.

- Two Programmable Non-Cacheable Regions

- Two Programmable PCI Memory Holes and One Programmable ISA Memory Holes.

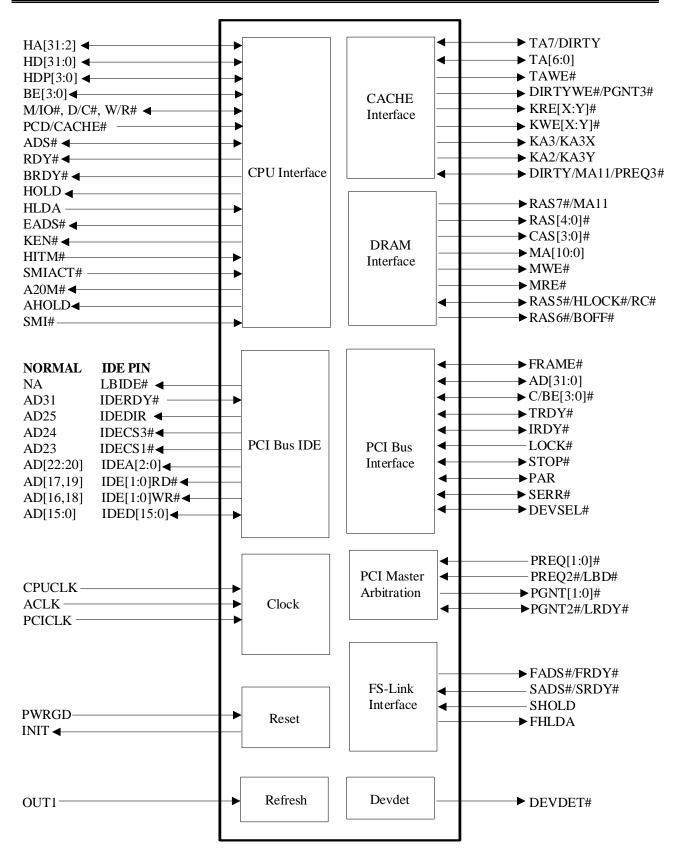

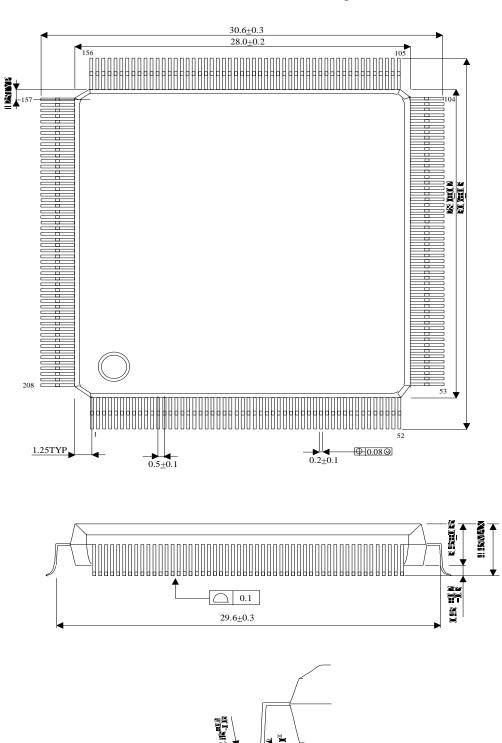

### • 208-Pin PQFP

• 0.6µm Low Power CMOS Technology

### **1.2 Architectural Overview**

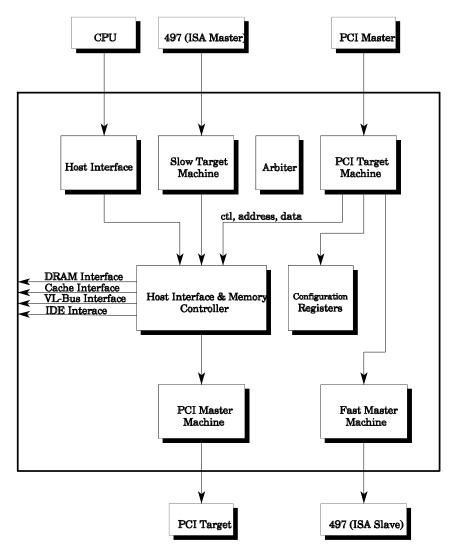

The 85C496 provides six basic functions: Host Interface, Cache controller, DRAM controller, PCI Bridge, IDE interface and FS-Link interface. This section describes an overview of these functions.

Figure 1.2 Architectural Overview Diagram

# **1.2.1 Host Interface Operations**

The Host Interface provides an interface among the Bus masters (CPU, PCI master, and ISA master), the main memory (L2 cache and DRAM), and the I/O devices (VL-Slave, PCI target, and ISA slave).

# **1.2.2 Cache Operations**

The secondary cache controller in 85C496 supports direct mapped cache organization. The implementation of the level two (L2) cache is done by using the standard SRAMs. Both cache write-back and write-through policy are supported. The SRAMs is external to the 85C496 and located on the Host address and data bus.

The structure of the level two cache uses same cache line size (four double words or 16 bytes) as the level one cache inside Intel 486 compatible CPUs. With direct mapped cache organization, 85C496 supports 4K, 8K, 16K, 32K, or 64K cache lines to implement 64K, 128K, 256K, 512K or 1M Bytes of L2 cache. Associated with each line of cache data, there are address tag field and a dirty bit to control the access of L2 cache. Cache tag field is used for address comparison to determine whether L2 cache contains the data for the access. While the dirty bit is used in conjunction with write-back policy to determine the status of the data. The 85C496 supports both 7-bit and 8-bit wide address tag field. Together with one dirty bit, The 85C496 provides three different combinations of cache implementation to meet different system integration requirements.

During a memory read or write operation, the 85C496 searches the L2 cache first before forwarding the access to the main memory. For the I/O read or write operations, L2 cache is not involved since I/O operations are not cacheable.

The operation of the secondary cache is dependent on the cache policy and can be programmed by Register 42h~43h bit 8.

# Write-Through

The basic concept of cache write-through policy is that the contents of main memory is always consistant with those in the L2 cache. During memory read operations, the 85C496 searches the L2 cache first. If the addressed data is located in the L2 cache (cache hit) then data is return directly from the L2 cache. If the addressed data is not located in the L2 cache (cache miss) then the access is forwarded to main memory. When data is read from the main memory, L2 cache is also being updated (cache line fill). For memory write operations, the 85C496 searches the L2 cache first, if the addressed memory location is in the L2 cache then data is written both to the L2 cache and the main memory to maintain data consistancy. If the addressed data is not located in L2 cache then only main memory is written with that data, and no operation is performed on L2 cache (no write allocate).

# Write-Back

The basic concept of cache write-back policy is that the data in the L2 cache and the main memory is updated only whenever is necessary. During a memory write operation, the 85C496 searches the L2 cache first. If the addressed memory location is in L2 cache then data is written to L2 cache only but not to the main memory. If the addressed memory location is done to L2 cache (no write allocate). For a memory read operation, the 85C496 searches the L2 cache first. If the addressed operation, the 85C496 searches the L2 cache first. If the addressed operation, the 85C496 searches the L2 cache (no write allocate). For a memory read operation, the 85C496 searches the L2 cache first. If the addressed data locates in the L2 cache (cache hit) then data is return directly from L2 cache. If the addressed data does not locate in L2 cache (cache miss) then the access is forwarded to main memory. When data is return from main memory, L2 cache will also be updated (cache line fill). However, if the cache line fill operation is to a dirty line (the Dirty bit associated with cache line is set), the dirty line is first written back to main memory before the new line is brought into the L2 cache. For a dirty line write-back operation, the 85C496 first performs a read from the dirty cache line and then writes the data to main memory.

In addition to supporting burst reads for the cache line fills of the CPU, the 85C496 is capable of accepting burst write data of the CPU's internal cache dirty line(s) during CPU write-back cycles. The support of the CPU burst write cycle is optional through the control of the Configuration Registers in the 85C496.

# **1.2.3 DRAM Memory Operations**

The 85C496 can support 8 rows of DRAM, and memory size from 1 MBytes up to 255 MBytes. Each bank could be single or double sided 32 bits Fast Page Mode or Extended Data-Out DRAM. The installed DRAM type can be  $256K/512K \times 36$ ,  $1M/2M \times 36$  or  $4M/8M/16M/32M \times 36$  SIMMs.

# **1.2.4 PCI Bridge Operations**

PCI bridge communicates to the host interface and FS-link interface for cycle translation and redirection.

### • PCI bridge to HOST interface communication

The PCI bridge provides an interface between bus masters (CPU and ISA master) and the PCI bus. A PCI cycle is generated by the PCI bridge if a CPU or ISA master- initiated cycle is not targeted to VL-slave, cache, or on-board memory. The PCI cycle is completed if PCI target claims the cycle and returns the TRDY#. One exception is master abort that occurs when none of the PCI targets claim the PCI cycle in a certain amount of time. In this case the PCI bridge returns all ones on the data bus to the host bridge then completes the cycle.

For PCI master accessing the cache or on-board memory, PCI bridge requests Host bridge for the memory cycle. The memory access can be single or burst transfers.

If the address of the undergoing cycle is within ISA memory area, the PCI bridge redirects the cycle to ISA bus via FS-link interface. All these information are passed from the PCI bridge target machine via host interface to the PCI bridge master machine then to the FS-link interface.

#### • PCI bridge to FS-link communication

When a PCI cycle is targeted at the ISA slave, the PCI bridge redirects the cycle to ISA bus via FS-link machine. The FS-link cycle can be initiated only through the PCI bridge. The PCI bridge redirects all the unclaimed PCI I/O cycle with address under 64k to ISA bus. It also redirects all the unclaimed memory cycles with address within ISA memory hole or ROM area to ISA bus.

#### • Inside PCI bridge

PCI bridge incorporates a 3-level post write buffer for PCI memory write cycle. When CPU writes PCI memory, host interface will receive ready from bridge before the data is actually written to the target. In this way, CPU access cache or on-board memory cycle can be executed concurrently with PCI memory write cycle. Note that only PCI memory write cycle can be posted in to the write buffer. I/O cycles, configure cycles and ISA memory cycles are not posted.

### **1.2.5 FS-Link Operations**

85C496 implements two link machines, fast master machine and slow target machine. They provide the same purposes as fast target machine and slow master machine in 85C497. Resources with higher bandwidth such as CPU, cache, main memory and PCI bus are considered as fast interface. While ISA resources which has lower bandwidth are considered as slow interface. The link machines in both chips provide the necessary interface control between fast interface and slow interface. When CPU master or PCI master wants to access ISA slave, the fast master machine is requested to transfer bus cycle information to the 85C497 fast link target machine. The 85C497 fast link target machine then converts cycle to AT bus controller for the ISA bus access. For ISA master, on the other hand, when it wants to access resource such as main memory, the AT bus controller requests the slow link master machine for the FS-link bus, then the 85C497 slow link master machine converts the ISA cycle to the 85C496 slow link target machine for that access.

# **2. Detailed Functional Description**

There is the functional description of the 85C496 interfaces and functional blocks in this section which includes the following topics: CPU/Cache Interface, DRAM Control Interface, PCI Interface, FS-Link Interface, IDE Controller, Clocks and Reset Logic.

### **2.1 CPU/Cache Interface**

There are some essential topics about the interface between CPU and Cache discussed in this section.

- L2 cache Controller

- The cache policy configuration between the L1 and L2 caches.

- Snoop protocol

# 2.1.1 L2 Cache Controller

85C496 provides control for level 2 cache ranging in size from 64K, 128K, 256K, 512K up to 1M byte, which uses asynchronous data SRAM of one bank or two, tag width can be either 7 or 8 bits, and dirty bit is optional too. 85C496's secondary-level cache protocol do not need an extra SRAM for the valid bit.

Second level cache supported by 85C496 has line size of 16 bytes or 4 double words with direct map organization, cache lines are updated at reads, but not on writes. Caching protocol can be configured to be either write through or write back.

During CPU, PCI, ISA master or DMA accesses, data is read from the level 2 cache on a cache hit. Data is written to cache only on a cache hit when the level 2 cache is configured in write back mode. When the level 2 cache is configured in write through mode, data will be written to both cache and DRAM on cache hits.

Only the data in the main memory can be allocated in the level 1 and level 2 cache, memory on either VESA bus, PCI bus or ISA bus will not be cached.

The portion of on-board DRAM that's above the cacheable DRAM size will not be cached in the level 2 cache, however, software resides in this area will not be suffered because 85C496 still caches data in this location to the CPU level 1 cache.

For example; if 10M bytes of DRAM, 64K bytes of cache with 7 bit tags is installed. Then the lower 8M DRAM will be cached in both level 1 and level 2 cache, and the upper 2M DRAM which is not cacheable in the level 2 cache will still be cached in the level 1 cache.

#### Shadow cacheable

UMB (Upper Memory Block) which is not in main memory area is by default non-cacheable. However, once shadowed, the RAM segments 0C0000-0FFFFFh can be further cached in Level 2 and Level 1 cache. By setting Register 46h, each 32K memory segments can be individually enabled to be cacheable by both 85C496's secondary level cache and CPU's internal cache.

System designer should be aware that for Intel P24D and P24T CPU operating in write back mode, shadow cacheable areas are not write protected in CPU's internal cache because once the data line being filled in CPU's level 1 cache, there will be no observable bus cycle outside the CPU while CPU write on these cache lines. The line by line write-back / write-through mode (WB/WT# pin) is not supported by the 85C496. Therefore programmers must make sure that software do not write on these locations unless they really meant to change it's contents. For Cyrix Cx486DX, Cx486DX2 these areas can still be write protected by setting the WT1 bit in CPU's CCR2 register.

#### Non-cacheable area

Three non-cacheable areas can be defined by setting register 50h through 55h. Only the main memory can be cached, memory on the extension bus is by default non-cacheable. The non-cacheable areas are programmed by specifying the starting address and the size of that area, each holes can be sized as either 64k, 128k, 256k, 512k, 1M, 2M or 4M.

#### Cache Sizing

To perform the level 2 cache auto sizing, the bit 1 of register 43-42 should be set to force level 2 cache always hit (bit1 = 1). After the cache size is detected, the bit 1 of register 43-42 should then set to 0 for the normal operation.

### Cache initialization

85C496 do not need a valid bit SRAM for the level 2 cache. To do so it assumes all the cache line in the level 2 cache are valid. Therefore level 2 cache must be initialized with accurate data from main board memory before it can be enabled. To initialize level 2 cache, the bit 1 of register 43-42 should be set to normal operation mode (bit1 = 0). Since the address tag field is at unknown state, the address generated for memory read (line fill) can be a cache hit, therefore it is necessary to read of a block of main memory data equal to twice the size of level 2 cache. Then cache is updated and cache initialization is completed.

#### Cache timing

The Level 2 cache data SRAM can be either 1 bank or 2 banks, in two bank configuration accesses are interleaved. The bit 4 of Register 43-42 controls whether cache accesses are interleaved.

Depending on the system clock rate, and the speed of the data/tag/dirty bit SRAM being used, CPU access level 2 cache can be completed in either zero or one wait state. Therefore single read or write takes either 2 clocks or 3 clocks, and burst read or write takes either 2-1-1-1, 2-2-2, 3-1-1-1, or 3-2-2-2 clocks.

The bit 9 of Register 43-42 selects the lead off cycle to be either zero or one wait state, the bit 10 of register 43-42 selects the subsequent three read cycles to be either zero or one wait state, and the bit 11 of register 43-42 selects the subsequent three write cycles to be either zero (with this option, the bits[1:0] of register 40: DRAM speed should be 'Faster' or 'Fastest') or one wait state. The bit 11 of register 43-42 also selects the single write cycles to be either zero or one wait state.

Note that the bit 9 of register 43-42 also defines the lead off cycle wait state for DRAM cycles. Moreover burst writes is only applicable with CPUs that supports burst write and the bits[6:5] of register 40 has being enabled for 85C496 to respond accordingly.

### • Cache Line Description

The internal cache of the 80486 has a 16-byte line size. When a read miss occurs in the internal cache, the 80486 initiates off-chip memory read cycles to update the current cache line. The 80486 reads in 16-byte blocks (4 doublewords). To increase the bus throughput, the 80486 provides a burst mode transfer. Four doublewords can be read sequentially in 5 processor clocks (2-1-1-1).

The second level cache provided by the SiS85C496 also has a 16-byte line size. It supports the 80486 burst read cycles to do the fastest cache line fill. When the 80486 internal and external caches encounter a read miss, they are simultaneously updated with the data line read from DRAM.

In addition to supporting burst reads for the cache line fills of the CPU, the 85C496 is capable of handling burst writes from the CPU's internal cache dirty line write back cycles. The CPU burst write support is optional by programming the Configuration Registers. The 85C496 supports the cache size up to 1MB and the DRAM size up to 255MB.

The address bits used to access cache lines depends on the size of the cache as follows:

| Cache size | Tag field   | Tag field   | Cache line |

|------------|-------------|-------------|------------|

|            | (8 bit tag) | (7 bit tag) | selection  |

| 64K byte   | A[23:16]    | A[22:16]    | A[15:4]    |

| 128K byte  | A[24:17]    | A[23:17]    | A[16:4]    |

| 256K byte  | A[25:18]    | A[24:18]    | A[17:4]    |

| 512K byte  | A[26:19]    | A[25:19]    | A[18:4]    |

| 1M byte    | A[27:20]    | A[26:20]    | A[19:4]    |

| Table 2.1 | Cache | Line | Selection |

|-----------|-------|------|-----------|

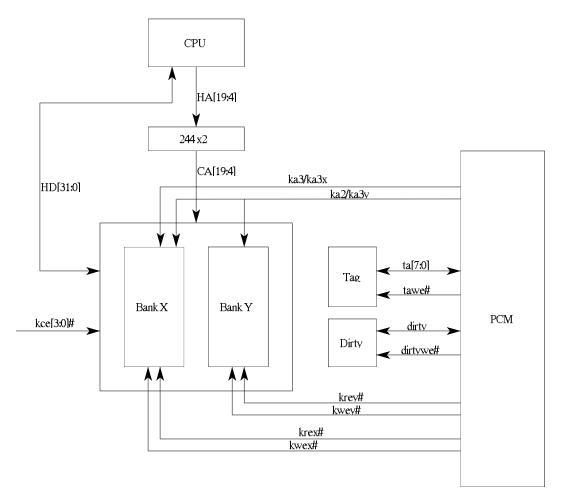

The 85C496 provides cache data and tag control signals for a two banks, interleaved cache implemented using standard asynchronous SRAMs. Figure 2.5 shows the block diagram of the CPU-L2 Cache connections.

Figure 2.5 CPU-L2 Cache Connections

# L2 Cache Size Options

Table 2.2 gives the information about the size option of L2 Cache and SRAM components. This table also shows Tag and Dirty SRAM requirements. The Tag and Dirty bits may be combined in a proper speeded 8-bit SRAM.

| Cache size | Data SRAM    | Tag SRAM      | Dirty SRAM    |

|------------|--------------|---------------|---------------|

| 64K byte   | 8 (8K x 8)   | 1 (4K x 8/7)  | 1 (4K x 1/0)  |

| 128K byte  | 4 (32K x 8)  | 1 (8K x 8/7)  | 1 (8K x 1/0)  |

| 256K byte  | 8 (32K x 8)  | 1 (16K x 8/7) | 1 (16K x 1/0) |

| 512K byte  | 4 (128K x 8) | 1 (32K x 8/7) | 1 (32K x 1/0) |

| 1M byte    | 8 (128K x 8) | 1 (64K x 8/7) | 1 (64K x 1/0) |

#### Table 2.2 L2 Cache Size Options

Table 2.3 shows the cacheable DRAM size with different L2 cache settings. The cacheable DRAM size is determined by cache size as well as the tag address field width. The on-board memory beyond the cacheable size is not cacheable by the L2 cache, however it is still cacheable by the 80486 internal cache.

#### Table 2.3 Cacheable Size Options

| Cache size | Cacheable DRAM size | Cacheable DRAM size |

|------------|---------------------|---------------------|

|            | (8 bit tag)         | (7 bit tag)         |

| 64K byte   | 16M byte            | 8M byte             |

| 128K byte  | 32M byte            | 16M byte            |

| 256K byte  | 64M byte,           | 32M byte            |

| 512K byte  | 128M byte           | 64M byte            |

| 1M byte    | 255M byte           | 128M byte           |

#### L2 Cache Performance Options

Table 2.4 gives the information about the performance options of the L2 cache and DRAM.

| Table 2.4 L2 Cache / DRAM Performance |

|---------------------------------------|

| Fast Page Mode DRAM                   |

| Cycle Definition                  |         | Total Clocks  | at Host Interfac | e             |

|-----------------------------------|---------|---------------|------------------|---------------|

| Host-to-Memory                    | 25 MHz  | <b>33 MHz</b> | <b>40 MHz</b>    | <b>50 MHz</b> |

| L2 read hit, non-burst            | 2       | 2             | 3                | 3             |

| L2 read hit, burst                | 2-1-1-1 | 2-1-1-1       | 3-2-2-2          | 3-2-2-2       |

| L2 write hit, non-burst           | 2       | 2             | 3                | 3             |

| L2 write hit, burst               | 2-1-1-1 | 2-1-1-1       | 3-2-2-2          | N/A           |

| DRAM read, non-burst, page-hit    | 3       | 4             | 5                | 6             |

| DRAM read, non-burst, row-miss    | 5       | 6             | 7                | 8             |

| DRAM read, non-burst, page-miss   | 7       | 8             | 10               | 12            |

| DRAM read, burst, page-hit        | 3-2-2-2 | 4-3-3-3       | 5-3-3-3          | 6-4-4-4       |

| DRAM read, burst, row-miss        | 5-2-2-2 | 6-3-3-3       | 7-3-3-3          | 8-4-4-4       |

| DRAM read, burst, page-miss       | 7-2-2-2 | 8-3-3-3       | 10-3-3-3         | 12-4-4-4      |

| DRAM write, non-burst, page-hit   | 3       | 4             | 5                | 5             |

| DRAM write, non-burst, page-start | 5       | 6             | 7                | 7             |

| DRAM write, non-burst, page-miss  | 7       | 8             | 10               | 11            |

| DRAM write, burst, page-hit       | 3-2-2-2 | 4-3-3-3       | 5-3-3-3          | N/A           |

| DRAM write, burst, page-start     | 5-2-2-2 | 6-3-3-3       | 7-3-3-3          | N/A           |

| DRAM write, burst, page-miss      | 7-2-2-2 | 8-3-3-3       | 10-3-3-3         | N/A           |

Preliminary V3.0 July 31, 1995

| ED | $\mathbf{n}$ | n                  | D  | A   | ۸۸  |  |

|----|--------------|--------------------|----|-----|-----|--|

| LD |              | $\boldsymbol{\nu}$ | n. | AL. | (VI |  |

| Cycle Definition                  |         | Total Clocks  | s at Host Interfac | ce            |

|-----------------------------------|---------|---------------|--------------------|---------------|

| Host-to-Memory                    | 25 MHz  | <b>33 MHz</b> | <b>40 MHz</b>      | <b>50 MHz</b> |

| L2 read hit, non-burst            | 2       | 2             | 3                  | 3             |

| L2 read hit, burst                | 2-1-1-1 | 2-1-1-1       | 3-2-2-2            | 3-2-2-2       |

| L2 write hit, non-burst           | 2       | 2             | 3                  | 3             |

| L2 write hit, burst               | 2-1-1-1 | 2-1-1-1       | 3-2-2-2            | N/A           |

| DRAM read, non-burst, page-hit    | 3       | 4             | 5                  | 5             |

| DRAM read, non-burst, row-miss    | 5       | 6             | 7                  | 7             |

| DRAM read, non-burst, page-miss   | 7       | 8             | 10                 | 11            |

| DRAM read, burst, page-hit        | 3-2-2-2 | 4-2-2-2       | 5-2-2-2            | 5-2-2-2       |

| DRAM read, burst, row-miss        | 5-2-2-2 | 6-2-2-2       | 7-2-2-2            | 7-2-2-2       |

| DRAM read, burst, page-miss       | 7-2-2-2 | 8-2-2-2       | 10-2-2-2           | 11-2-2-2      |

| DRAM write, non-burst, page-hit   | 3       | 4             | 5                  | 5             |

| DRAM write, non-burst, page-start | 5       | 6             | 7                  | 7             |

| DRAM write, non-burst, page-miss  | 7       | 8             | 10                 | 11            |

| DRAM write, burst, page-hit       | 3-2-2-2 | 4-3-3-3       | 5-3-3-3            | N/A           |

| DRAM write, burst, page-start     | 5-2-2-2 | 6-3-3-3       | 7-3-3-3            | N/A           |

| DRAM write, burst, page-miss      | 7-2-2-2 | 8-3-3-3       | 10-3-3-3           | N/A           |

NOTE: Burst write function is applicable only with L1 W/B CPU.

| Cycle Definition        | ]                     | Total Clocks at       | Host Interface       |                      |

|-------------------------|-----------------------|-----------------------|----------------------|----------------------|

| PCI-to-Memory           | 25 MHz                | 33 MHz                | <b>40 MHz</b>        | <b>50 MHz</b>        |

| L2 read hit, non-burst  | 6 <sup>T</sup>        | 6 <sup>T</sup>        | 6 <sup>T</sup>       | 6 <sup>T</sup>       |

|                         | 9 <sup>B</sup>        | 9 <sup>B</sup>        | 7 <sup>B</sup>       | 7 <sup>B</sup>       |

| L2 read hit, burst      | 6-4-4-4 <sup>T</sup>  | 6-4-4-4 <sup>T</sup>  | 6-4-4-4 <sup>T</sup> | 6-4-4-4 <sup>T</sup> |

|                         | 9-6-4-4 <sup>B</sup>  | 9-6-4-4 <sup>B</sup>  | 7-5-4-4 <sup>в</sup> | 7-5-4-4 <sup>в</sup> |

| L2 read miss, non-burst | 7 <sup>T</sup>        | 8 <sup>T</sup>        | 7 <sup>T</sup>       | 7 <sup>T</sup>       |

|                         | 10 <sup>B</sup>       | 11 <sup>B</sup>       | 8 <sup>B</sup>       | 9 <sup>B</sup>       |

| L2 read miss, burst     | 7-5-5-5 <sup>T</sup>  | 8-6-6-6 <sup>T</sup>  | 7-5-5-5 <sup>T</sup> | 7-5-5-5 <sup>T</sup> |

|                         | 10-7-5-5 <sup>в</sup> | 11-8-6-6 <sup>в</sup> | 8-6-5-5 <sup>B</sup> | 9-7-5-5 <sup>B</sup> |

| L2 write hit, non-burst | 6 <sup>T</sup>        | 6 <sup>T</sup>        | 6 <sup>T</sup>       | 6 <sup>T</sup>       |

|                         | 9 <sup>B</sup>        | 9 <sup>B</sup>        | 7                    | 7                    |

| L2 write hit, burst     | 6-4-4-4 <sup>T</sup>  | 6-4-4-4 <sup>T</sup>  | 6-4-4-4 <sup>т</sup> | 6-4-4-4 <sup>T</sup> |

|                         | 9-6-4-4 <sup>B</sup>  | 9-6-4-4 <sup>B</sup>  | 7-5-4-4 <sup>B</sup> | 7-5-4-4 <sup>B</sup> |

| L2 read miss, non-burst | 7 <sup>T</sup>        | 8 <sup>T</sup>        | 7 <sup>T</sup>       | 7 <sup>T</sup>       |

|                         | 10 <sup>B</sup>       | 11 <sup>B</sup>       | 8 <sup>B</sup>       | 9 <sup>B</sup>       |

| L2 write miss, burst    | 7-5-5-5 <sup>T</sup>  | 8-6-6-6 <sup>T</sup>  | 7-5-5-5 <sup>T</sup> | 7-5-5-5 <sup>T</sup> |

|                         | 10-7-5-5 <sup>в</sup> | 11-8-6-6 <sup>в</sup> | 8-6-5-5 <sup>B</sup> | 9-6-5-5 <sup>B</sup> |

**NOTE** : The above timing is with reference to the PCI clock.  $^{T}$  : CPU L1 cache in Write Through Mode.

<sup>B</sup> : CPU L1 cache in Write Back Mode.

Those following figures show the Cache read cycle and Cache write cycle.

### L2 Cache Fill Without Dirty Line Replacement

|          |   |   |   |          |    | _ |          |          |            |     |    |          |          | _  |   |   |    |    |          |                     |   |          |   |    |   |    |

|----------|---|---|---|----------|----|---|----------|----------|------------|-----|----|----------|----------|----|---|---|----|----|----------|---------------------|---|----------|---|----|---|----|

|          |   |   | 2 | L        | IN | E | FI       | ш        | <u>, I</u> | 11_ | JE | C        | LE       | ΞA | N |   |    |    |          |                     |   |          |   |    |   |    |

| CPUCLK   |   | h | h | h        | h  | h | h        | h        | h          | h   | h. | h        | h        | n. | h | h | n. | n, | h        | h                   | h | h        | h | h. | N | n_ |

| ADS#     |   | - | h | Г        |    |   |          |          |            |     |    |          |          |    | - | - |    | _  |          |                     |   |          | - | —  | _ |    |

| BRDY#    | - | - |   |          |    | _ | $\vdash$ | $\vdash$ | -          | h   | Г  |          | h        | Г  | - | h | Г  | _  | h        | Г                   | - | -        | - | _  | _ |    |

| RDY#     |   | - | - |          |    | - |          | -        | -          | -   |    |          |          |    | - | - | _  | _  | h        | Г                   | - | -        | - | _  | _ |    |

| DIRTYWE# |   | _ | - |          |    | h |          |          |            |     |    |          |          |    |   |   |    |    | Г        | -                   | - | -        | - | —  | _ |    |

| DIRTY    |   | - | - | $\vdash$ | -  | - | $\vdash$ | $\vdash$ | -          | -   | -  | $\vdash$ | $\vdash$ |    | - | - |    | _  | $\vdash$ | $\vdash$            | - | $\vdash$ | - | _  | _ |    |

| TAWE#    |   | - | - | -        | -  | h |          |          |            |     |    |          |          |    |   |   |    |    | Г        | -                   | - | -        | - | _  |   |    |

| KWEY#    |   | _ | - |          | -  | _ |          | -        | _          | h   | Г  | -        |          |    | - | ľ | Г  | _  | -        | -                   | - | -        | - | _  | _ |    |

| KWEX#    |   | _ |   |          |    |   |          |          |            |     |    |          | Ы        | Г  | - | - |    | _  | h        | $\lfloor r \rfloor$ | - |          | - | —  | _ |    |

| КАЗХ     |   |   | 5 | -        | _  | - | $\vdash$ |          |            |     |    |          |          | ľ  |   |   |    |    |          | Г                   | - | $\vdash$ | - | —  | _ |    |

| KA3Y     |   |   | 5 |          |    |   | $\vdash$ |          | _          |     | h  |          |          |    |   |   | Г  | _  |          |                     | - | $\vdash$ | - | —  | _ |    |

| RAS4#    |   |   |   | Г        |    |   | $\vdash$ |          | -          |     |    |          |          |    | - | _ | _  | _  |          |                     | - | $\vdash$ | _ | _  | _ |    |

| RAS6#    |   | - |   |          |    | _ | h        |          |            |     |    |          |          |    |   |   |    |    |          |                     |   |          |   |    |   |    |

| CAS0#    |   | _ |   |          |    | _ |          | _        | h          |     | Г  | h        |          | Г  | ľ |   | Г  | ſ  |          | Г                   | _ | -        | _ |    | _ |    |

| MA[0:11] |   |   |   | x        |    |   |          | x        |            |     | x  |          |          | x  | E |   | х  | _  |          | bc                  |   |          |   | _  | _ |    |

| MRE#     |   |   | _ | _        |    |   |          |          | h          |     | 5  | h        |          | 5  | h |   | Г  | ſ  |          | $\lfloor r \rfloor$ |   |          | _ | _  | _ |    |

| MWE#     |   |   |   |          |    |   |          |          |            |     |    |          |          |    |   | _ |    |    |          | F                   |   |          | _ |    |   |    |

Figure 2.6 Level 2 Cache Line Fill with no Dirty

### L2 Cache Line Fill with Dirty Line Replacement

|          | l | 2 | Ca | ch | еL | ine           | Fi | ll v | vith | ۱D | irtv      | Li              | ne | Re | epla | ace | em | en | t |   |   |           |    |          |             |

|----------|---|---|----|----|----|---------------|----|------|------|----|-----------|-----------------|----|----|------|-----|----|----|---|---|---|-----------|----|----------|-------------|

| CLOCK    | - | 1 | 1  |    | 1  |               |    |      |      |    |           |                 |    |    |      |     |    |    |   | h | h |           | Λ. | $\sim$   |             |

| ADS#     | _ |   | 5  |    | -  | _             |    | _    | -    | -  | -         | _               | _  | _  |      |     |    | -  |   | - | - | _         |    |          | -           |

| BRDY#    | - | - | -  |    |    | _             |    | _    | -    | -  | -         | _               | _  | _  |      |     |    | _  |   | _ | _ | _         |    |          |             |

| RDY#     | - | - | -  |    | -  | _             |    | -    | -    | -  | -         | _               | _  |    |      |     |    | -  |   | - |   | Γ         |    |          |             |

| DIRTYWE# | - | - |    |    |    | _             |    | -    |      |    |           | _               | _  |    |      |     |    |    |   |   |   |           |    |          |             |

| DIRTY    | _ |   |    |    |    | _             |    |      |      |    |           |                 |    |    |      |     |    |    |   |   |   |           |    |          |             |

| TAWE#    | _ |   |    |    |    |               |    |      |      |    | _         |                 |    |    |      |     |    |    |   |   |   |           |    |          |             |

| KREY#    | _ |   |    |    |    |               |    | Γ    | _    |    |           |                 |    | Л  |      |     |    |    |   | _ | _ | _         |    |          |             |

| KREX#    | _ | - |    |    | 5  | _             |    |      |      |    | Г         | _               | _  |    |      |     |    |    |   | - | - |           |    |          |             |

| KWEY#    | _ | - |    |    |    | _             |    |      | -    | -  |           | _               |    |    |      |     |    |    |   | - | - |           |    |          | <u>را</u> ر |

| KWEX#    | _ | - |    |    |    |               |    | _    |      |    |           | _               | _  | _  |      |     |    | _  |   | _ |   | Γ         |    |          |             |

| КАЗХ     | _ |   |    |    | Г  |               |    | -    |      |    |           |                 |    |    |      |     |    |    |   |   |   | Γ         |    |          |             |

| KA23Y    | _ |   |    |    |    |               |    | Г    |      |    |           | _               |    | N  |      |     |    |    |   |   |   |           |    |          |             |

| RASx#    |   |   |    |    |    |               |    |      |      |    |           |                 |    |    |      |     |    |    |   |   |   |           |    |          |             |

| RASy#    | _ |   |    |    |    |               |    |      |      |    |           |                 |    |    | Γ    |     |    |    |   |   |   |           |    |          |             |

| CAS#     |   |   |    |    |    | $\overline{}$ |    | Г    |      |    | $\square$ | $\overline{\ }$ |    | Γ  |      |     |    |    |   |   |   | $\square$ |    | ٦.       |             |

| MRE#     |   |   |    |    |    |               |    | _    |      |    |           | _               |    | _  |      |     |    |    |   |   |   | $\square$ |    | N.       |             |

| MWE#     |   | - |    |    |    |               |    |      |      |    |           |                 |    |    | Г    |     |    | -  |   | - | - |           |    | $\vdash$ | -           |

Figure 2.7 Level 2 Cache Line Fill with Dirty Line Replacement

|          |     |                    |    | L        | 2 | R | E٨ | ١D     | H      | T,E        | зU       | RS | т  |   |        |        |    |          |          |        |   |  |

|----------|-----|--------------------|----|----------|---|---|----|--------|--------|------------|----------|----|----|---|--------|--------|----|----------|----------|--------|---|--|

| CPUCLK   |     |                    |    | $\sim$   |   |   |    |        | $\neg$ | $\uparrow$ |          |    |    | ┢ |        | +      | ╢  |          |          | $\neg$ |   |  |

| ADS#     | ]   | $\vdash$           |    |          |   |   | Л  |        | +      | +          | -        |    | _  |   |        | +      | +  | -        | <br>-    | _      |   |  |

| BRDY#    | 1—— | $\left  \right $   | +- | -        | ſ |   |    |        |        |            |          |    |    |   |        |        |    |          |          | r      |   |  |

| RDY#     | ]   | $\left  - \right $ | -  | -        |   |   |    | -      | +      | +          | -        |    |    | - | $\neg$ | $\neg$ |    |          |          | r      | - |  |

| DIRTYWE# | ]   | $\left  \right $   | -  | —        |   |   |    | _      | +      | +          | <u> </u> |    |    | _ | -      | +      | ┼╴ | <u> </u> | <br>-    | _      | - |  |

| DIRTY    |     |                    |    |          |   |   |    |        |        |            |          |    |    |   |        |        |    |          |          |        |   |  |

| TAWE#    | ]   | $\left  \right $   | -  | -        |   |   |    | -      | +      | -          | -        |    |    | - |        | +      | +  | -        | <br>-    |        | - |  |

| KREY#    | ]   | $\left  - \right $ | -  | h        |   |   |    |        |        | +          | <u> </u> |    | ιL |   |        | / +    | +  | <u> </u> | <br>-    | _      | - |  |

| KREX#    | ]   | $\left  \right $   | -  |          |   |   |    | $\neg$ | ٦L     |            |          |    | /─ | - | $\neg$ | L      |    |          | <u>_</u> |        | - |  |

| КАЗХ     |     |                    |    | <u> </u> |   |   |    | _      | +      | +          | -        |    | L  |   |        |        |    |          | ∽        |        | - |  |

| KA3Y     |     |                    |    |          |   |   |    | _      |        |            |          |    |    |   |        |        |    | -        | <br>     |        |   |  |

Figure 2.8 L2 Cache Read Hit, Burst Transfer in Write Through or Write Back Mode

L2 Cache Write Hit, Non-Burst Transfer in Write Back Mode

|          |          |   | Ľ             | 2 V | <b>/</b> R | ITE | ΕH              | IIT,            | N               | ٥Ņ | <b>І-</b> Е    | BUF       | RS     | Т        |                |      |                     |      |        |  |

|----------|----------|---|---------------|-----|------------|-----|-----------------|-----------------|-----------------|----|----------------|-----------|--------|----------|----------------|------|---------------------|------|--------|--|

| ACLK     | <b>_</b> | J | Γ             |     |            |     | $\square$       |                 |                 |    |                |           |        | ſ        |                |      |                     |      | $\neg$ |  |

| CPUCLK   | -        |   | $\overline{}$ |     | $\sum$     |     | $\overline{\ }$ |                 |                 |    | $\overline{\}$ |           | $\int$ |          | $\overline{\}$ | 7    | <br>$\overline{\ }$ | Л    |        |  |

| ADS#     |          |   |               |     |            |     |                 | $\overline{\ }$ |                 |    |                | $\square$ |        |          |                | <br> | <br>                | <br> |        |  |

| BRDY#    |          |   |               |     |            |     |                 |                 |                 |    |                |           |        |          |                | <br> | <br>                | <br> |        |  |

| RDY#     |          | _ |               |     |            |     |                 |                 |                 |    |                |           |        | <u>_</u> |                | <br> | <br>                | <br> |        |  |

| DIRTYWE# |          | _ |               |     |            |     |                 |                 |                 |    |                |           |        |          |                | <br> | <br>                | <br> |        |  |

| DIRTY    |          |   |               |     |            |     |                 |                 |                 |    |                |           |        |          |                |      |                     |      |        |  |

| TAWE#    |          |   |               |     |            | _   |                 |                 |                 |    |                |           |        |          |                | <br> | <br>                | <br> |        |  |

| KWEY#    |          |   |               |     |            |     |                 |                 |                 |    |                |           |        |          |                | <br> | <br>                | <br> |        |  |

| KWEX#    |          |   |               |     |            |     |                 |                 | $\overline{\ }$ |    |                |           | Г      |          |                | <br> | <br>                | <br> |        |  |

Figure 2.9 L2 Cache Write Hit, Non-Burst Transfer in Write Back Mode

|          |   |   |    |          | E        | BU       | R        | ЗΤ | ٦V | VF       | શા | E, | Ľ | 2⊢             | IIT                  | - |   |    |   |   |   |               |              |   |   |       |   |   |

|----------|---|---|----|----------|----------|----------|----------|----|----|----------|----|----|---|----------------|----------------------|---|---|----|---|---|---|---------------|--------------|---|---|-------|---|---|

| CPUCLK   |   | - | ┢╲ |          | ſ        |          | ┢╲       |    | Г  |          | ┢╲ |    | Л |                | J                    |   | Л |    | ſ |   | Л | -             | $\mathbf{r}$ |   | Г | <br>J |   | Г |

| ADS#     | — |   | -  | h        |          |          |          | Г  |    |          | -  |    | _ | -              | -                    | _ |   |    |   | _ | _ | _             | _            | _ | _ | <br>_ | _ |   |

| BRDY#    |   | - | -  | -        |          | ┢        |          |    |    |          |    |    |   |                |                      |   |   |    |   |   |   | Л             |              | - | - | <br>_ | - |   |

| RDY#     |   | - | -  | -        | $\vdash$ | $\vdash$ | -        |    |    |          |    | -  | - | -              | -                    | - |   | ſ  |   |   |   | Л             | _            | _ | _ | <br>_ | - |   |

| DIRTYWE# |   |   | -  | -        | ┝        | -        | ┢        |    |    | Г        | h  |    |   | ₼              | J                    |   |   | Г  | ٦ |   |   | Л             | _            | _ | _ | <br>_ | _ |   |

| DIRTY    |   |   |    |          |          |          |          |    |    | <u> </u> |    |    | _ | $\overline{4}$ | ∽                    | _ |   | ~_ |   | _ | _ | $\overline{}$ |              |   | L |       |   |   |

| TAWE#    |   |   |    | _        | F        | -        | -        |    |    |          | -  |    | _ | _              | _                    | _ |   |    |   | _ | _ | _             | _            | - |   | <br>_ | _ |   |

| KREY#    | — | _ | -  | -        | $\vdash$ | -        | <u> </u> |    |    |          | -  |    | _ | _              | _                    | _ |   |    |   | _ | _ | _             |              | _ | _ | <br>_ | _ |   |

| KREX#    |   | _ | -  | <u> </u> | $\vdash$ |          | <u> </u> |    |    |          |    |    | _ | _              | _                    | _ |   |    |   | _ | _ | _             |              | _ |   | <br>_ | _ |   |

| KWEY#    |   | _ | -  | -        | $\vdash$ |          |          |    |    | Г        |    |    | _ | _              | $\gamma$             |   |   | Г  |   | _ | _ | _             |              | _ |   | <br>_ | - |   |

| KWEX#    |   |   | -  | -        | $\vdash$ | -        | _        | _  |    | _        |    | h  |   |                | $\overline{\Lambda}$ | _ |   | _  | ٦ |   |   | Г             |              | _ | _ | <br>_ |   |   |

| КАЗХ     |   | _ | -  | _        | -        | -        | _        |    |    |          | _  |    | _ |                | -<br>\               |   |   |    |   |   |   | -             | Г            | _ |   | <br>  | _ |   |

| КАЗҮ     |   |   |    |          |          |          |          |    |    |          |    |    |   |                |                      |   |   | Г  |   | _ |   | _             |              |   |   | <br>  |   |   |

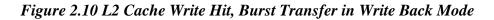

L2 Cache Write Hit, Burst Transfer in Write Back Mode

# 2.1.2 L1/L2 Cache Mode Configurations

The 85C496 supports the L1 and L2 caches with write-through (WT)/write-back (WB) mode. Both caches can be in the write-back mode in a given configuration. Table 2.5 shows the five configurations supported by the 85C496. The 85C496 can also enable/disable L1 (System BIOS disable L1 cache via CPU Control Register) or L2 cache (System BIOS disable L2 cache via Cache Configure Register 43-42 bit 0) individually.

| Processor Type               | L1 Cache Mode | L2 Cache Mode |

|------------------------------|---------------|---------------|

| 486SX/DX/DX2/DX4/SL-Enhanced | WT            | WT/WB         |

| P24D/P24T                    | WT/WB         | WT/WB         |

| M7/Cx 5x86                   | WT/WB         | WT/WB         |

| Am486 DX4/DX2/DX/SX          | WT            | WT/WB         |

| Enhanced Am486 DX4/DX2       | WT/WB         | WT/WB         |

Table 2.5 L2 Cache Configurations

# **2.1.3 Snoop Operations**

The Snoop operation by 85C496 ensures data consistency between the L1 cache, L2 cache and main memory. Once the Snoop is enabled by 85C496, it monitors PCI/ISA Bus accesses to main memory. The type of PCI/ISA access (read or write) and the caching modes(write-through or write-back) of the L1 and L2 caches determines the snoop operation be taken. All the caching modes are shown below:

| Type of Access | L1:WT,           | L1:WT,           | L1:WB,           | L1:WB,           |

|----------------|------------------|------------------|------------------|------------------|

| Type of Access | L1:W1,<br>L2:WT  | L1:W1,<br>L2:WB  | L1:WD,<br>L2:WT  | L1:WB,<br>L2:WB  |

| PCI/ISA        | No Snoop.        | Snoop L2.        | Snoop L1.        | Snoop both       |

| Master Read of | Data in L1 and   | L2 is Snooped    | L1 is Snooped    | L1 and L2.       |

| Main Memory    | L2 is consistent | for dirty data.  | for dirty data.  | Both L1 and      |

| Wrann Wrennory | with data in     | If L2 line is    | If L1 line is    | L2 caches are    |

|                | main memory.     | dirty, then the  | dirty, then the  | Snooped for      |

|                | main memory.     | 85C496 writes    | CPU writes       | dirty data.      |

|                |                  | cache line back  | cache line back  | unty uata.       |

|                |                  | to main          | to main          |                  |

|                |                  | memory before    | memory before    |                  |

|                |                  | permitting       | permitting       |                  |

|                |                  | PCI/ISA          | PCI/ISA          |                  |

|                |                  | Master to read   | Master to read   |                  |

|                |                  | memory. L2       | memory.          |                  |

|                |                  | line is marked   | During write-    |                  |

|                |                  | as clean (Dirty  | back, data is    |                  |

|                |                  | = 0). No L1      | also written to  |                  |

|                |                  | action is taken. | L2.              |                  |

| PCI/ISA        | Snoop both L1    | Snoop both L1    | Snoop both L1    | Snoop both       |

| Master Write   | and L2.          | and L2.          | and L2.          | L1 and L2.       |

| to Main        | Invalidate L1    | Invalidate L1    | Invalidate L1    | Invalidate L1    |

| Memory         | and overwrite    | and overwrite    | and overwrite    | and overwrite    |

|                | L2 on Snoop      | L2 on Snoop      | L2 on Snoop      | L2 on Snoop      |

|                | hit.             | hit.             | hit. If L1       | hit. If L1       |

|                |                  |                  | Snoop hits a     | Snoop hits a     |

|                |                  |                  | dirty line, then | dirty line, then |

|                |                  |                  | the CPU writes   | the CPU          |

|                |                  |                  | cache line back  | writes cache     |

|                |                  |                  | to main          | line back to     |

|                |                  |                  | memory before    | main me-mory     |

|                |                  |                  | permitting PCI   | before per-      |

|                |                  |                  | /ISA to write to | mitting PCI      |

|                |                  |                  | main memory.     | /ISA to write    |

|                |                  |                  |                  | to main          |

|                |                  |                  |                  | memory.          |

### Table 2.6 Snoop Protocol

#### Advanced Snooping and Snoop Filter

The 85C496 integrates an Advanced Snooping mechanism that eliminates the main memory access delay due to Snoop cycles. During a PCI burst cycle, the 85C496 performs Snoop cycle in advance before the actual burst cycle is generated. The snoop filter is used so that the advanced snooping is performed in very 4 Double words.

# **2.2 DRAM Interface**

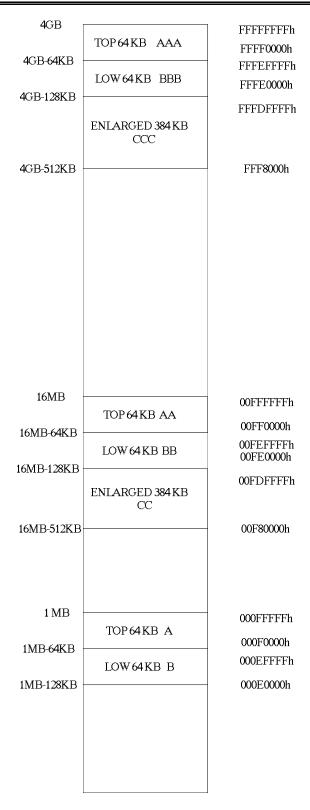

The size of DRAM supported by 85C496 range from 1M to 255M bytes, UMB (upper memory block) is excluded from the main memory, and can either be used to shadow BIOS or extension card ROM, or be appended to the top of main memory or remapped for use as SMRAM.

Three memory holes can also be used to extract portions of DRAM from main memory. All non-main memory accesses will first be presented to VESA bus, then forwarded to PCI bus, and only accesses to memory hole 2 (ISA memory hole) will be further forward to ISA bus. Memory hole do not necessary have to be configured within the range of main memory. But it is illegal to install any VESA, PCI or ISA bus memory overlapped with main memory.

The 85C496 DRAM interface is designed to support DRAM with FP/EDO mode with CAS# before RAS# refresh. DRAM type can be 256K/512K by 32/36 bits, 1M/2M by 32/36 bits, 4M/8M/16M/32M by 32/36 bits or any combination of the above.

85C496 has multiple share function pins to meet individual system requirement. MA11 is shared with RAS7 at pin 157, and shared with DIRTY or fourth PCI master request at pin 126. If any 16M by 32/36 bits DRAM is installed, then either the DRAM on row 7 will not be accessible, or the cache interface should be implemented without the dirty bit (always dirty), or fourth PCI master is not supported. More detailed information is in section 2.8.

# 2.2.1 DRAM Organization

The 85C496 DRAM Interface is organized into eight rows (RAS#[7:0]), with each row consisting of one 36-bit bank (non-interleaved, 32 bits data and 4 bits data parity). The DRAM organization is shown in Figure 2.11. Each row is four bytes wide (CAS#[3:0]).

Figure 2.11 DRAM Organization Supporting Single & Double Bank SIMMs

# 2.2.2 DRAM Size Configuration

85C496 supports 8 rows of DRAMs each 32 or 36 bits wide. Register 4Fh to 48h defines the address boundary of these 8 rows of memory. The 8 rows of DRAMs may be implemented in 8 banks of single-sided SIMMs, 4 banks of double-sided SIMMs or any other combinations as required. Access to the rows are not interleaved and need not to be populated starting from row 0 or in consecutive sequence.

The DRAM may be installed with 256K/512K by 32/36 bits, 1M/2M by 32/36 bits, 4M/8M/16M/32M by 32/36 bits type. Since these register came up with initial value of 00h after power up, 85C496 do not recognize any DRAM at that time. To configure the DRAM size registers, software routine must first set each row to its maximum capacity and attempt to write, read a specific pattern in order to determine whether DRAM is actually installed in that slot, and if installed, what is the size and type of the DRAM. After going through each rows in the same manner, the 8 address boundaries to be written in the registers can be calculated by adding up the number of megas of DRAM between each bank and bank 0. For example, if after DRAM sizing routine, it's found that row 2, 3, 5 is populated with 16M, 1M, 4M of DRAM respectively, then the row boundary registers should be programmed in the following manner:

|       | DRAM Size | Row Boundary Register |

|-------|-----------|-----------------------|

| Row 7 | 0 M       | 21 (15h)              |

| Row 6 | 0 M       | 21 (15h)              |

| Row 5 | 4 M       | 21 (15h)              |

| Row 4 | 0 M       | 17 (11h)              |

| Row 3 | 1 M       | 17 (11h)              |

| Row 2 | 16 M      | 16 (10h)              |

| Row 1 | 0 M       | 0 (0h)                |

| Row 0 | 0 M       | 0 (0h)                |

Table 2.7 DRAM Auto Detection

### Shadow RAM

Memory location 0C0000h-0FFFFFh in standard PC system are reserved for use by system BIOS and extension cards, 85C496 provides a shadow mechanism that enables the contents of these ROMs in that area be duplicated to the same location in main memory that can be accessed by CPU in very little wait states. Therefore overall system performance will be greatly improved because low speed ROM accesses are eliminated.

85C496 implements read and write access attributes to control the access of the shadow RAM areas. To use shadow RAM, first register 44h - 45h have to be programmed to enable the areas to be shadowed, while setting shadow RAM as read disable and write enable, read then write the same address will copy the contents of the ROMs into their corresponding locations into main memory. After the whole memory segment being transport to DRAM, shadowing can be enabled by setting shadow RAM as read enable and write disable. Any further reads to those locations will be accessing main memory and writes will be directed to the ROMs.

PCI master, ISA master and DMA is not permitted to access 0C0000h-0FFFFh unless the bit 10 of register 44-45h is enabled. Once enabled, the read enable, write protect settings in the bits[8:9] of register 44-45h still control the read/write attribute of that area.

#### Memory hole

Since 85C496 can handles on-board main memory up to 255M bytes, any memory resides on extension cards that locates on the location overlapped with main memory will not be accessed by CPU. To solve this problem 85C496 provides three memory holes that can be programmed by register 50h through 55h to prevent those areas from interpreted as main memory. The memory holes are programmed by specifying the starting address and the size of that hole, each holes can be sized as either 64K, 128K, 256K, 512K, 1M, 2M or 4M.

#### Relocate

Again in standard PC system, UMB (upper memory block) in main memory is not used by the system. To recover the unused DRAM, 85C496 relocates memory segment 0A0000-0BFFFh and 0D0000-0EFFFh to the top of DRAM installed. To facilitate the relocation feature, if total DRAM installed is 8M or less, memory segment D and E is not shadowed, and SMRAM relocation is not enabled, 256K byte of DRAM will be appended to the top of DRAM after enabling relocation by setting the bit 0 of register 47.

#### **SMRAM**

SMRAM may be located at either 060000-06FFFFh or 0E0000-0EFFFFh, and can be physically mapped to 0A0000-0AFFFFh or 0B0000-0BFFFFh. The DRAM relocation feature is not applicable if SMRAM is utilized.

The bits[4:3] of register 5A selects the SMRAM base address and to which location it relocates. The bit 2 of register 5A forces remapping even when CPU is not in SMI mode so that SMI routines can be initialize at that area. Contrarily, the bit 1 of register 5A forces relocation ineffective during SMI mode to enable the un-remapped data at that address be accessed. SMRAM area should not be cacheable. To use logical address of 6XXXX segment or Exxxx segment, it is BIOS engineer's responsibility to make sure that these addresses are set to non-cacheable. While accessing SMRAM, the contents will then not be cached by either level 1 or level 2 cache, therefore it is not necessary to flush the contents of the cache upon existing SMI mode.

Another possible way of implementing SMRAM is by shadowing segment 0E0000-0EFFFh and use it directly as SMRAM, therefore it is no need for relocation, and the contents will be accessible regardless whether it is in SMI mode or not.

#### DRAM timing

85C496 is designed with very flexible DRAM control timing, basic timings are selected by the bits[1:0] of register 40, while more detail timings are individually adjustable (all 'clocks' listed below refers to CPUCLK).

#### **RAS#** precharge time:

The bits[1:0] of register 40 selects the RAS# precharge time to be 3 clocks at 'Fastest' and 'Faster', 4 clocks at 'Slower' and 5 clocks at 'Slowest'.

#### **RAS# to CAS# delay:**

The bit 3 of register 41 selects RAS# to CAS# delay to be either 2 clocks or 3 clocks.

#### CAS# precharge time:

The bit 0 of register 41 selects CAS# precharge time to be either 1 clock or 2 clocks.

These setting should be selected to meet DRAM minimum timing requirements for proper operation.

|          |   |                   |   | PA      | ١G | E | ST | AR | T |   |   |        |               |                 |      |        |                 |  |

|----------|---|-------------------|---|---------|----|---|----|----|---|---|---|--------|---------------|-----------------|------|--------|-----------------|--|

| CPUCLK   |   |                   | _ |         |    |   |    |    |   |   |   | $\neg$ | $\overline{}$ |                 |      | $\neg$ | $\overline{\ }$ |  |

| ADS#     | — | <br>$\overline{}$ |   | <u></u> |    |   |    |    |   |   |   |        |               | —               | <br> | <br>   |                 |  |

| RDY#     | _ |                   | - |         |    |   |    |    |   |   |   |        |               | _               |      | Л      |                 |  |

| RAS2#    |   | <br>              | - | _       |    |   |    |    |   |   |   |        |               |                 |      |        |                 |  |

| CASO#    |   | <br>              | - |         |    |   |    |    |   |   |   |        |               | $\overline{\ }$ |      |        | Л               |  |

| MA[11:0] |   |                   |   |         |    |   |    |    |   | Х | х |        |               | _               | <br> | <br>   |                 |  |

| MRE#     | — | <br>              | - | _       |    |   |    |    |   |   |   |        |               | _               | <br> | <br>   |                 |  |

| MWE#     |   | <br>              |   |         |    |   |    |    |   |   |   |        |               |                 | <br> |        |                 |  |

FP/EDO DRAM Write with Non-Burst Transfer and Page start

Figure 2.12 FP DRAM Write with Non-Burst Transfer and Page start

# FP/EDO DRAM Read with Non-Burst Transfer and Page Miss

|          | PAGE MISS/ROW MISS |

|----------|--------------------|

| CPUCLK   |                    |

| ADS#     |                    |

| RDY#     |                    |

| RAS2#    |                    |

| RAS4#    |                    |

| CAS0#    |                    |

| MA[0:11] |                    |

| MRE#     |                    |

| MWE#     |                    |

Figure 2.13 FP DRAM Read with Non-Burst Transfer and Page Miss

### FP DRAM Read with Burst Transfer and Row Miss

|          |               |                         |   | E                       | BU | R | ST | R | ΕA     | ١D | , F | RO | $\sim$ | / N | 115 | S  |   |    |   |   |   |    |   |   |   |   |   |   |   |

|----------|---------------|-------------------------|---|-------------------------|----|---|----|---|--------|----|-----|----|--------|-----|-----|----|---|----|---|---|---|----|---|---|---|---|---|---|---|

| CPUCLK   | $\neg \wedge$ | $\overline{\mathbf{v}}$ | N | $\overline{\mathbf{v}}$ |    | V | V  |   | Л      | Л  | Л   | Л  | Л      | Л   | Л   | Λ. | Λ | Λ. |   | Л |   | h. | Л | Л | Л | Л | N |   | Ŵ |

| ADS#     | ]\_           | Г                       | — | -                       | -  | _ | -  | _ | -      | -  | -   | -  |        |     | -   |    |   |    | — |   | _ |    |   | - | - |   | - | - | _ |

| BRDY#    | ]             |                         |   | -                       | -  | _ | +  | _ | -      | -  | ľ   | 5  |        |     |     | ſ  | Г |    |   |   | ſ | 5  |   | - | - | ╎ |   | - |   |

| RDY#     | 1——           |                         | _ | -                       | -  | - | -  | _ | -      | -  |     | -  |        |     | -   |    |   |    | _ | _ | _ |    |   |   | - |   |   | - |   |

| RASO#    |               | Л                       | _ | -                       | -  |   |    |   |        |    |     |    |        |     |     |    |   |    |   |   |   |    |   |   |   |   |   |   |   |

| CASO#    | 1——           | —                       | _ | -                       | -  | - | +  | _ | $\neg$ |    |     | ]_ | -      |     |     |    | Г |    | J |   |   | 5  | - | ╢ |   |   |   | - | _ |

| MA[0:11] |               | х                       | х | _                       |    | _ | _  |   |        |    |     |    | х      |     |     |    |   | х  |   |   |   |    | x |   |   |   |   | χ |   |

| MRE#     | 1             |                         | _ | -                       | _  | - | -  | _ | $\neg$ |    |     |    |        |     |     |    | Г |    | J |   |   | 5  |   | ┢ |   |   |   | - |   |

| MWE#     |               |                         |   |                         |    | _ | -  |   | _      | _  |     |    |        |     |     |    |   |    | _ | _ |   |    |   | _ |   |   | - |   |   |

Figure 2.14 FP DRAM Read with Burst Transfer and Row Miss

### EDO DRAM Read with Burst Transfer and Page Miss

| E        | DC                 | ) E | BUF    | RS     | ΓF                      | RE     | AC     | ), F   | PAC    | GE       | M | IS              | 5               |        |   |          |   |        |        |

|----------|--------------------|-----|--------|--------|-------------------------|--------|--------|--------|--------|----------|---|-----------------|-----------------|--------|---|----------|---|--------|--------|

| CPUCLK   | $\left  1 \right $ | h.  | $\sim$ | $\sim$ | $\overline{\mathbf{v}}$ | $\sim$ | $\sim$ | $\sim$ | $\sim$ | $\frown$ | h | $\sim$          | $\sim$          | $\sim$ | h | $\wedge$ | h | $\sim$ | $\sim$ |

| ADS#     |                    |     |        |        |                         |        |        |        |        |          |   |                 |                 |        |   |          |   |        |        |

| BRDY#    |                    |     |        |        |                         |        |        |        |        | <u>_</u> |   |                 | $\overline{\ }$ |        |   | <u>_</u> |   |        |        |

| RDY#     |                    |     |        |        |                         |        |        |        |        |          |   |                 |                 |        |   |          |   |        |        |

| RAS#     |                    |     |        |        |                         |        |        |        |        |          |   |                 |                 |        |   |          |   |        |        |

| CAS#     |                    |     |        |        |                         |        |        |        | $\int$ |          |   | $\overline{\ }$ |                 |        | 5 |          |   |        |        |

| MA[11:0] |                    |     | х      |        |                         |        | Х      |        | Х      |          | Х |                 | x               |        | Х |          |   |        |        |

| MRE#     |                    |     |        |        |                         |        |        |        |        |          |   |                 |                 |        |   |          |   |        |        |

| MWE#     |                    |     |        |        |                         |        |        |        |        |          |   |                 |                 |        |   |          |   |        |        |

Figure 2.14-1 EDO DRAM Read with Burst Transfer and Page Miss

### EDO DRAM Read with Burst Transfer and Page Hit

| EDO      | BL                          | JR:      | ST       | R        | ΞA           | D,       | PA           | ٩G       | Εŀ           | ΗT        | -            |          |          |          |        |

|----------|-----------------------------|----------|----------|----------|--------------|----------|--------------|----------|--------------|-----------|--------------|----------|----------|----------|--------|

| CPUCLK   | $\left  \mathbf{n} \right $ | $\frown$ | $\frown$ | $\frown$ | $\frown$     | $\frown$ | $\frown$     | $\frown$ | $\frown$     | $\frown$  | $ \land $    | $\frown$ | $\frown$ | $\frown$ | $\sim$ |

| ADS#     |                             |          |          |          |              |          |              |          |              |           |              |          |          |          |        |

| BRDY#    |                             |          |          |          |              |          |              |          |              | $\square$ |              |          |          |          |        |

| RDY#     |                             |          |          |          |              |          |              |          |              |           |              |          |          |          |        |

| RAS#     |                             |          |          |          |              |          |              |          |              |           |              |          |          |          |        |

| CAS#     |                             |          |          |          |              |          | $\square$    |          |              |           |              |          |          |          |        |

| MA[11:0] |                             |          |          |          | $\mathbf{x}$ |          | $\mathbf{x}$ |          | $\mathbf{x}$ |           | $\mathbf{x}$ |          |          |          |        |

| MRE#     |                             |          |          |          |              |          |              |          |              |           |              |          |          |          |        |

| MWE#     | <b> </b>                    |          |          |          |              |          |              |          |              |           |              |          |          |          |        |

Figure 2.14-2 EDO DRAM Read with Burst Transfer and Page Hit

# FP/EDO DRAM Write with Burst Transfer and Page Start

| DRA      | WRITE WITH BURST TRANSFER AND PAGE START |                         |

|----------|------------------------------------------|-------------------------|

| CPUCLK   |                                          | $\overline{\mathbf{x}}$ |

| ADS#     |                                          |                         |

| BRDY#    | ┼┼┼┼┼┼┼┼┼┼┼┼╷╷╷╱┼┼┼┼┑╷╻╱┼┼┼┼┑            |                         |

| RDY#     |                                          |                         |

| RAS6#    |                                          |                         |

| CASO#    | ┽┾┾┾┾┾┾┾┾┾┾┾┑╎╎╎╎╱┾┿╲╎╎╎╎╱┾┿╲╎╵╎         |                         |

| MA[0:11] |                                          | ±χ                      |

| MRE#     |                                          |                         |

| MWE#     |                                          |                         |

Figure 2.15 FP DRAM Write with Burst Transfer and Page Start

Parity

Preliminary V3.0 July 31, 1995

The bit 7 of register 41 enables checking for DRAM parity error during read cycles, and if register 05-04[8] is enabled for SERR# output, then parity errors will activate SERR# output to instruct 85C497 to assert NMI which further alerts CPU of this faulty situation. DRAM parity bits are generated by 85C496 during level 2 cache write back DRAM cycles to keep parity bits updated, also parity bits are generated during PCI master and ISA master to main board DRAM write cycles.

#### Refresh

85C496 enforces CAS# before RAS# refresh and supports RAS# staggering that reduces power surge induced by simultaneously switch of the RAS# lines. Refresh is triggered by the OUT1 input from 85C497. 85C496 do not hold CPU during refresh in progress, also the refresh cycle is concurrent with every other cycles in the system except DRAM cycles so that the system time consumed by refresh is very few. The bit 4 of register 41 enables power saving slow refresh by reducing the rate of refresh to one refresh per every 4 OUT1 refresh requests.

|        | CAS# BEFORE RAS#, STAGGERED REFRESH            |

|--------|------------------------------------------------|

| CPUCLK |                                                |

| OUT1   | ┨╾┥╲ <u></u> ┛╱┥╾┥╾┥╼┥╼┥╼┥╼┥╼┥╼┥╼┥╼┥╼┥╼┥╼┥╼┥╼┥ |

| CAS3#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽┑┥┑                             |

| CAS2#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽┑┥┑                             |

| CAS1#  | ┨╾┥╾┥╼┽╼┽╼┽╼┽╼┽┑┥╲╽┊╵╹╹╹╹╹╹╹╹╹╹╹╹╹╹╹╹          |

| CASO#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽┑┥┑╻╸╸╸╸╸╸╸╸╸                   |

| RAS7#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽╼┼┑╲╸╸╸╸╸╸╸╸                    |

| RAS6#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽╼┽┑┑╴╸╸╸╸╸╸                     |

| RAS5#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽┑┥┑╸╸╸╸╸╸╸                      |

| RAS4#  | ┨╾┥╾┥╼┥╼┥╼┥╼┥╼┥┑┥╴╸╸╸╸╸                        |

| RAS3#  | ┨╾┽╾┽╼┽╼┽╼┽╾┽╼┽╼┼┑╲╻╻╻╹╻╹╻╹╻╹╻╹╻╹╻╹╻╹          |

| RAS2#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽╼┽┑┥╸┥╸╸╸╸                      |

| RAS1#  | ┨╾┥╾┥╼┽╼┽╼┽╼┽╼┽╼┽┑┥╴┥╸╸╸╸╸                     |

| RASO#  | ┨╾┽╾┽╼┽╼┽╼┽╼┽╼┽╼┽┑┥                            |

Figure 2.16 CAS# before RAS#, staggered refresh

#### High current drive support

Since 85C496 supports up to 8 rows of DRAMs, the capacitance loading of the DRAM interface in 85C496 varies fairly distantly, therefore 85C496 provides programmable I/O buffers which have driving capability of 12 or 24mA.

System designer may program register 57[6:4] to select CAS#[3:0], MA[10:0] and MWE# depending on the number and type of DRAM populated and the actual board wire layout. If the ultimate timing still do not meet the minimum requirements after setting this register and turning other corresponding DRAM timing settings, external TTL driver should be installed to provide sufficient current drive for the DRAMs.

# 2.2.3 DRAM Address Translation

Table 2.8.1 and 2.8.2 show the Host/PCI/ISA address multiplexing scheme for generation of row and column addresses at the DRAM interface (MA[11:0]).

| 1 aute 2.6.1 Dr | 11011100 | ebb illandi | ution        |     |       |       |

|-----------------|----------|-------------|--------------|-----|-------|-------|

|                 | 256K     | /512K       | 1 <b>M</b> / | 2M  | 4M/8N | Л/16M |

| MA#             | CAS      | RAS         | CAS          | RAS | CAS   | RAS   |

| MA 0            | A3       | A13         | A3           | A13 | A3    | A13   |

| MA 1            | A2       | A12         | A2           | A12 | A2    | A22   |

| MA 2            | A4       | A14         | A4           | A14 | A4    | A14   |

| MA 3            | A5       | A15         | A5           | A15 | A5    | A15   |

| MA 4            | A6       | A16         | A6           | A16 | A6    | A16   |

| MA 5            | A7       | A17         | A7           | A17 | A7    | A17   |

| MA 6            | A8       | A18         | A8           | A18 | A8    | A18   |

| MA 7            | A9       | A19         | A9           | A19 | A9    | A19   |

| MA 8            | A10      | A11         | A10          | A20 | A10   | A20   |

| MA 9            | A21      | A20         | A11          | A21 | A11   | A21   |

| MA 10           | A23      | A22         | A23          | A22 | A12   | A23   |

| MA 11           | A25      | A24         | A25          | A24 | A25   | A24   |

Table 2.8.1 DRAM Address Translation

|       | 1M ( | 12x8) | <b>2M</b> (1 | 12x9) | 4M (1 | 2x10) |

|-------|------|-------|--------------|-------|-------|-------|

| MA#   | CAS  | RAS   | CAS          | RAS   | CAS   | RAS   |

| MA 0  | A3   | A13   | A3           | A13   | A3    | A13   |

| MA 1  | A2   | A12   | A2           | A12   | A2    | A12   |

| MA 2  | A4   | A14   | A4           | A14   | A4    | A14   |

| MA 3  | A5   | A15   | A5           | A15   | A5    | A15   |

| MA 4  | A6   | A16   | A6           | A16   | A6    | A16   |

| MA 5  | A7   | A17   | A7           | A17   | A7    | A17   |

| MA 6  | A8   | A18   | A8           | A18   | A8    | A18   |

| MA 7  | A9   | A19   | A9           | A19   | A9    | A19   |

| MA 8  |      | A20   | A10          | A20   | A10   | A20   |

| MA 9  |      | A21   |              | A21   | A11   | A21   |

| MA 10 |      | A10   |              | A22   |       | A22   |

| MA 11 |      | A11   |              | A11   |       | A23   |

# **2.3 PCI Interface**

The PCI Interface of 85C496 is to provide the interface between the CPU/main memory /ISA Bus and the PCI Bus. When PCI-to-main memory transfer happens, the 85C496 is a target; when CPU-to-PCI or ISA-to-PCI transfer happens, the 85C496 is a master.

Both of the non-configuration and configuration address spaces can be read or written by the Host. The 85C496 is both a master and target for the transaction, when the CPU is accessing the 85C496's configuration registers. It is essential to know that PCI-to-CPU accesses are not permitted.

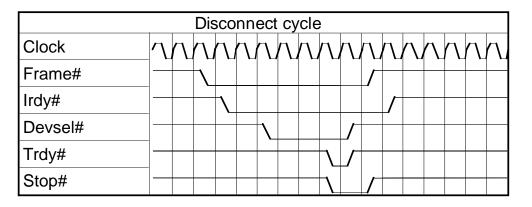

This section describes PCI cycle termination, exclusive access cycles, parity support and system error generation on the PCI Bus.

# **2.3.1 Functional Overview**

### Command Set

PCI Bus commands indicate to the target the type of transaction desired by the master. These commands are presented on the C/BE[3:0]# signals during the address phase of a transfer. Table 2.9 summaries the 85C496's support of the PCI Bus commands.

| C/BE[3:0]# | Command Type                | 85C496 as a Master | 85C496 as a Target |

|------------|-----------------------------|--------------------|--------------------|

| 0000       | Interrupt Acknowledge       | Yes                | No                 |

| 0001       | Special Cycle               | No                 | No                 |

| 0010       | I/O Read                    | Yes                | Yes (for ISA)      |

| 0011       | I/O Write                   | Yes                | Yes (for ISA)      |

| 0100       | Reserved                    | No                 | No                 |

| 0101       | Reserved                    | No                 | No                 |

| 0110       | Memory Read                 | Yes                | Yes                |

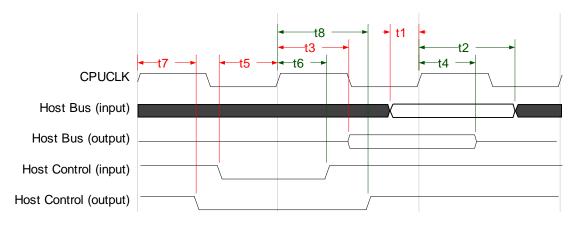

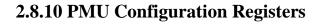

| 0111       | Memory Write                | Yes                | Yes                |