# Intel 430TXPCIset Desktop Design Guide

**June 1997**

297739-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The **Intel 430TX PCIset** may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

\*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

# **TABLE OF CONTENTS**

| CHAPTER 1                                                      |                          |

|----------------------------------------------------------------|--------------------------|

| OVERVIEW                                                       |                          |

| 1. Overview                                                    |                          |

| 1.1 Intel 430TX PCIset                                         |                          |

| 1.1.1 82439TX MTXC Features                                    |                          |

| 1.1.2 82371AB PIIX4 Features                                   | 1-7                      |

| CHAPTER 2 FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST  |                          |

| 2. Flexible Motherboard Design Layout Review Checklist         | 2.1                      |

| 2.1 MTXC Design Checklist                                      | ۱ - ک<br>1 ر             |

| 2.1.1 Clocks                                                   | ۱ -ک<br>1 <sub>-</sub> 2 |

| 2.1.2 MTXC Power                                               |                          |

| 2.1.3 Host Interface                                           |                          |

| 2.1.4 L2 Cache                                                 |                          |

| 2.1.5 DRAM                                                     |                          |

| 2.2 PIIX4 Design Checklist                                     |                          |

| 2.2.1 Power and Ground Pins                                    |                          |

| 2.2.2 PCI Bus Signals                                          |                          |

| 2.2.3 ISA Signals                                              |                          |

| 2.2.4 X-Bus Signals                                            | 2-8                      |

| 2.2.5 Power Management Signals                                 |                          |

| 2.2.6 Power Button Implementation                              |                          |

| 2.2.7 USB Interface                                            |                          |

| 2.2.8 IDE Interface                                            |                          |

| 2.2.9 System and Test Signals                                  | 2-10                     |

| 2.2.10 Clocks                                                  | 2-10                     |

| 2.3 Flash                                                      |                          |

| 2.3.1 Miscellaneous                                            |                          |

|                                                                |                          |

| CHAPTER 3                                                      |                          |

| BOARD LAYOUT AND ROUTING GUIDELINES                            |                          |

| 3. 430TX Board Layout and Routing Guidelines                   | 3-1                      |

| 3.1 Placement                                                  |                          |

| 3.2 Board Description                                          |                          |

| 3.3 Layout and Routing Guidelines                              |                          |

| 3.3.1 BGA Component Layout Guidelines                          |                          |

| 3.3.1.1 BGA Pad Size                                           |                          |

| 3.3.1.2 BGA Vias                                               |                          |

| 3.4 BGA Routing                                                |                          |

| 3.4.1 General Guidelines                                       |                          |

| 3.4.2 Memory/Cache Layout Guidelines                           | 3-9                      |

| 3.4.3 Memory/Cache Routing Guidelines                          |                          |

| 3.4.4 Clock Routing Guidelines                                 | 3-18                     |

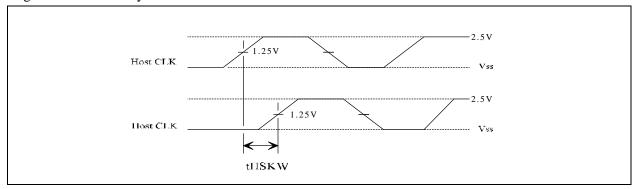

| 3.4.4.1 Clock Skew Requirements                                |                          |

| 3.4.4.2 Host Clock Skew Requirements                           | 3-18                     |

| 3.4.4.4 PCI Clock Skow                                         |                          |

| 3.4.4.5 Heat and BCI Clock I avoid for an EDC/EDM/CDBAM Design | 3-15                     |

| 3.4.4.5 Host and PCI Clock Layout for an EDO/FPM/SDRAM Design  |                          |

| 3.5 IDE Routing Guidelines                                     |                          |

| 3.3.1 Capillu                                                  | ు-∠ !                    |

| 3.5.2 Motherboard                                                                                                                                                                                                                         |                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

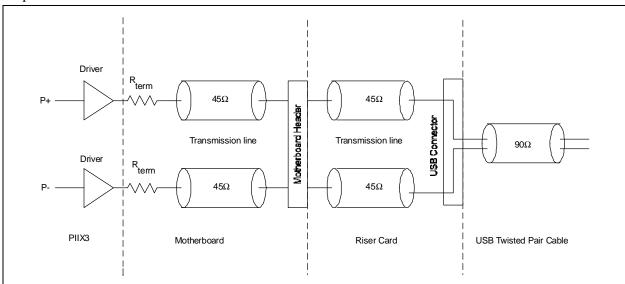

| 3.6 Motherboard Layout Guidelines for PIIX4 USB Implementations                                                                                                                                                                           | 3-23                     |

| 3.6.1 USB Data Signals Layout Guidelines                                                                                                                                                                                                  | 3-24                     |

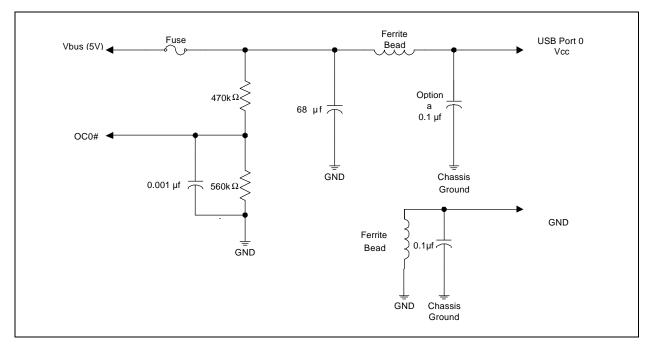

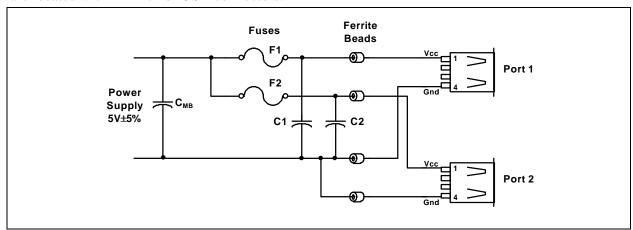

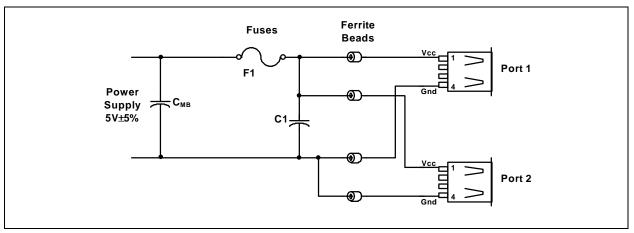

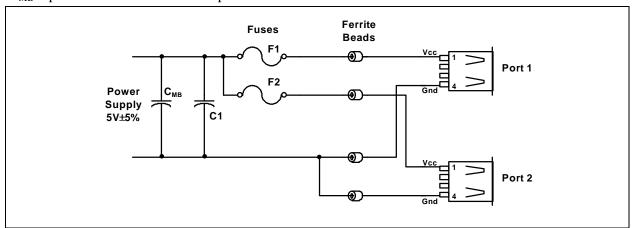

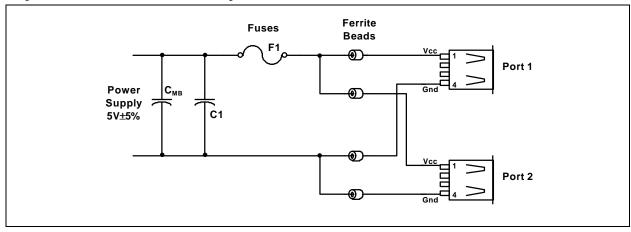

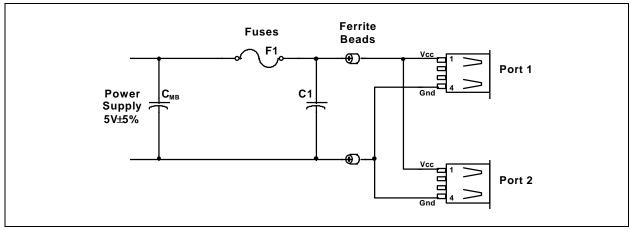

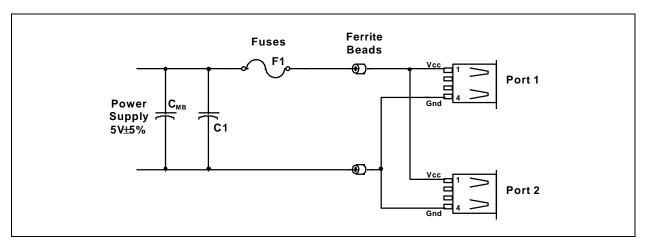

| 3.6.2 USB Power Distribution Layout Guidelines—Vbus                                                                                                                                                                                       | 3-26                     |

| 3.6.3 USB Power Line Layout Topologies                                                                                                                                                                                                    | 3-27                     |

| 3.6.3.1 Option #1 An Optimal Design—Recommended                                                                                                                                                                                           | 3-27                     |

| 3.6.3.2 Option #2 An Effective Design—Recommended                                                                                                                                                                                         | 3-28                     |

| 3.6.3.3 Option #3 A Less Effective Design                                                                                                                                                                                                 |                          |

| 3.6.3.4 Power Line Layout Topologies Are Not Recommended                                                                                                                                                                                  | 3-29                     |

| 3.6.4 Options for USB Connector Implementation                                                                                                                                                                                            | 3-30                     |

| 3.6.4.1 Recommended Options                                                                                                                                                                                                               |                          |

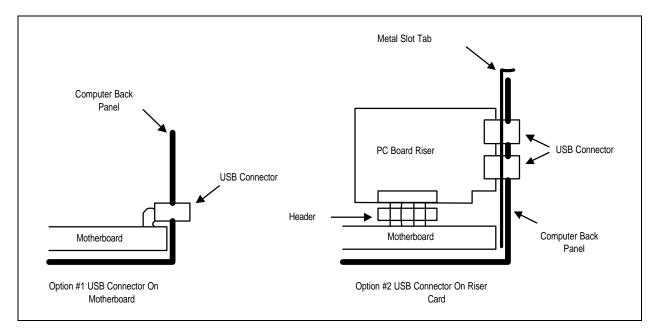

| 3.6.4.1.1 Option #1 USB Connector On Motherboard                                                                                                                                                                                          | 3-30                     |

| 3.6.4.1.2 Option #2 USB Connector On Riser Card                                                                                                                                                                                           |                          |

| 3.6.4.1.3 Option #3 Use A Full Speed USB Cable                                                                                                                                                                                            |                          |

| 3.6.4.2 Options Are NOT Recommended                                                                                                                                                                                                       |                          |

| 3.6.4.2.1 Flat Ribbon Cable or Unshielded Twisted Pair Cable                                                                                                                                                                              | 3-32                     |

| 3.6.4.2.2 Cable/Riser Card Combination                                                                                                                                                                                                    |                          |

| 3.7 Hardware Checklist                                                                                                                                                                                                                    |                          |

| 3.7.1 Motherboard Layout                                                                                                                                                                                                                  |                          |

| 3.7.2 USB Connectors Checklist                                                                                                                                                                                                            |                          |

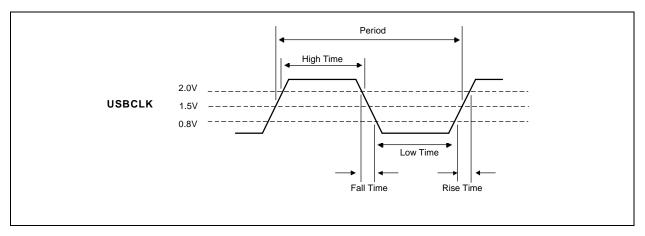

| 3.7.3 USBCLK Checklist                                                                                                                                                                                                                    |                          |

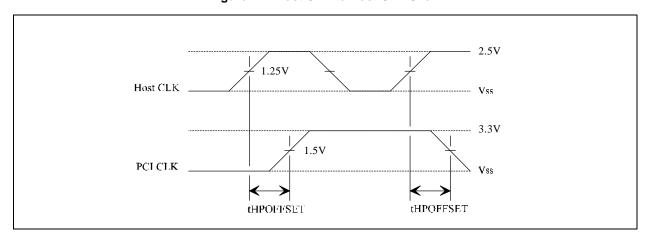

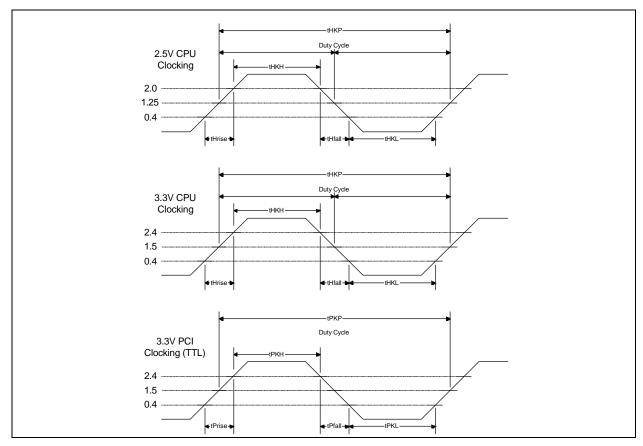

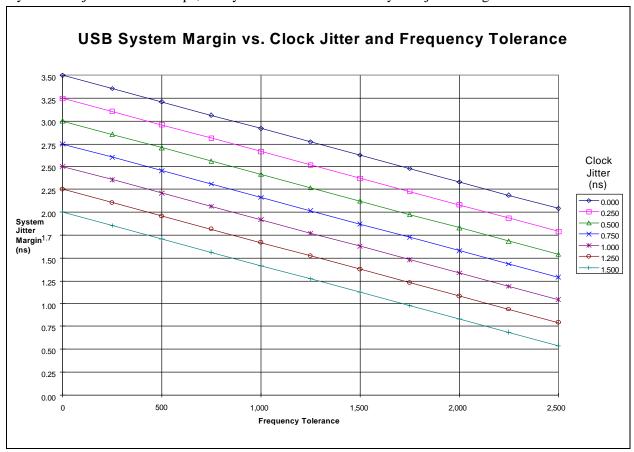

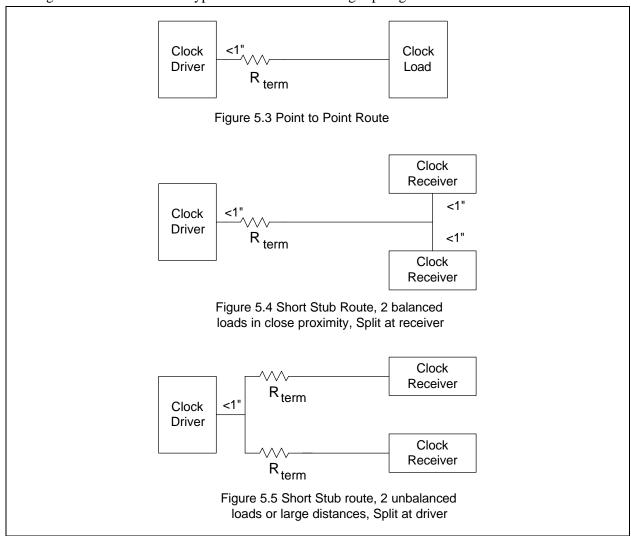

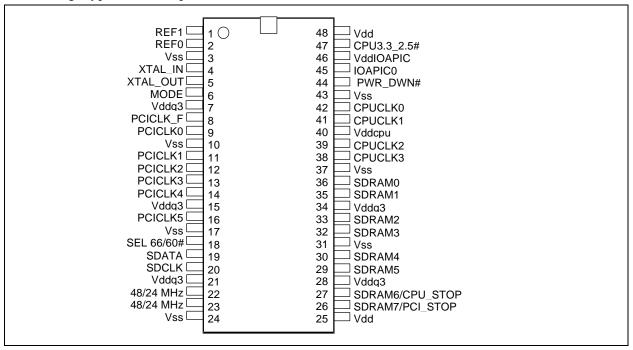

| SYSTEM CLOCK REQUIREMENTS  4. 430TX System Clock Requirements  4.1 PIIX4 USBCLK Guidelines  4.1.1 Frequency Tolerance  4.1.2 PIIX4 USBCLK Requirements  4.1.3 USBCLK Jitter  4.2 System Considerations  4.3 Suggested Pinout Requirements | 4-2<br>4-3<br>4-6<br>4-7 |

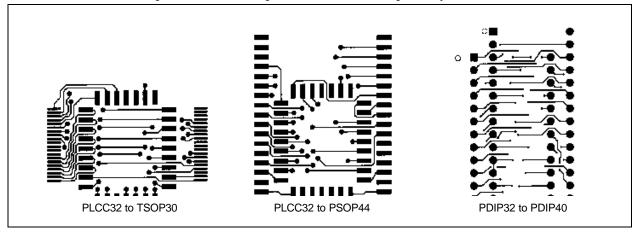

| CHAPTER 5 FLASH DESIGN  5. Flash Design  5.1 Dual-Footprint Flash Design  5.2 Flash Design Considerations  5.2.1 Desktop and Mobile  5.2.2 3V/5V Design Considerations (Optional)                                                         | 5-1<br>5-2<br>5-2        |

| CHAPTER 6 CUSTOMER REFERENCE BOARD SCHEMATIC OVERVIEW                                                                                                                                                                                     |                          |

| 6. 430TX PCIset Customer Reference Board Schematic Overview                                                                                                                                                                               | G 1                      |

| 6.1 System Description                                                                                                                                                                                                                    |                          |

| 6.2 Power Plane Connections                                                                                                                                                                                                               | 6.2                      |

|                                                                                                                                                                                                                                           |                          |

| 6.3 Jumpers, Connectors, and Valid Memory Configurations                                                                                                                                                                                  |                          |

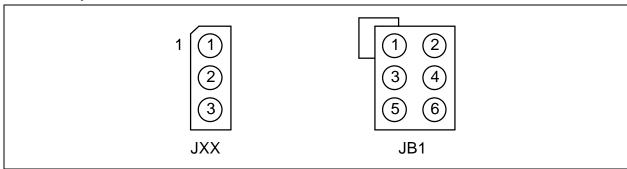

| 6.3.1 Jumper Description                                                                                                                                                                                                                  | 0-0                      |

| 6.3.2 Jumper Header Pin Orientations                                                                                                                                                                                                      |                          |

| 6.3.3 Connector Guide                                                                                                                                                                                                                     |                          |

| 6.3.4 Valid Memory Configurations                                                                                                                                                                                                         |                          |

| 6.3.5 Stuffing Options                                                                                                                                                                                                                    | 6-8                      |

| 6.3.5.1 Clock Generator Options                                                                                                                                                                                                           |                          |

| 6.3.5.2 Cache Options                                                                                                                                                                                                                     |                          |

| 6.3.5.3 Flash Size Options                                                                                                                                                                                                                |                          |

| 6.4 Bill of Materials                                                                                                                                                                                                                     | 6-11                     |

intel®

1

# **Overview**

# CHAPTER 1 OVERVIEW

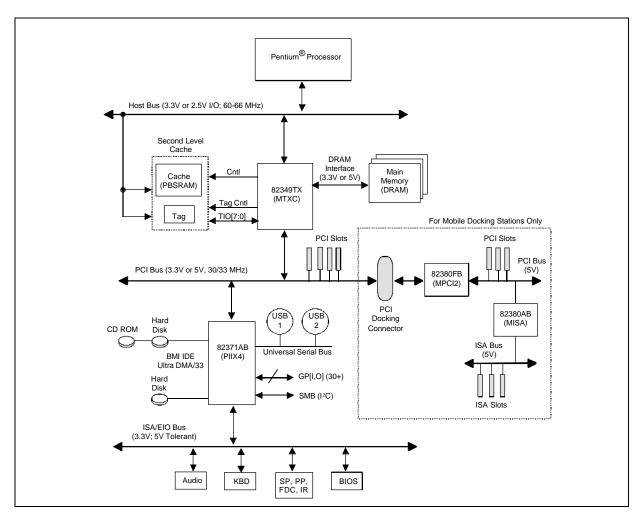

Figure 1-1. Intel 430TX PCIset System Block Diagram

# 1. Overview

# 1.1 Intel 430TX PCIset

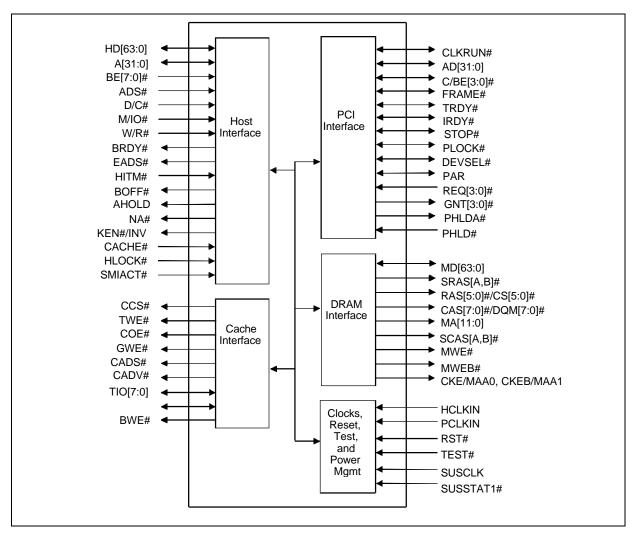

The MTXC host bridge provides a completely integrated solution for the system controller and datapath components in a Pentium® processor system. The MTXC supports all Pentium family processors since P54C, it has 64-bit Host and DRAM Bus Interface, 32-bit PCI Bus Interface, Second level Cache Interface, and it integrates the PCI arbiter.

The MTXC interfaces with the Pentium processor host bus, a dedicated memory data bus, and the PCI bus (see Figure 1-1).

The MTXC bus interfaces are designed to interface with 2.5V, 3.3V and 5V busses. The MTXC implements 2.5V and 3.3V drivers and 5V tolerant receivers. The MTXC connects directly to the

Pentium processor 3.3V or 2.5V host bus, directly to 5V or 3.3V DRAMs, and directly to the 5V or 3.3V PCI bus. The 430TX also interfaces directly to the 3.3V or 5.0V TAGRAM and 3.3V Cache.

The MTXC works with the PCI IDE/ISA Accelerator 4 (PIIX4). The PIIX4 provides the PCI-to-ISA/EIO bridge functions along with other features such as a fast IDE interface (PIO mode 4 and Ultra DMA/33), Plug-n-Play port, APIC interface, PCI 2.1 Compliance, SMBUS interface, and Universal Serial Bus Host Controller functions.

#### **DRAM Interface**

The DRAM interface is a 64-bit data path that supports Standard (or Fast) Page Mode (FPM), Extended Data Out (EDO) and Synchronous DRAM (SDRAM) memory. The DRAM controller inside the MTXC is capable of generating 3-1-1-1 for posted writes for any type of DRAM that is used. While read performance is 6-1-1-1 for SDRAM, 5-2-2-2 for EDO, and 6-3-3-3 for FPM.

The DRAM interface supports 4 Mbytes to 256 Mbytes with six RAS lines. The MTXC supports 4-Mbit, 16-Mbit, and 64-Mbit DRAM and SDRAM technology, both symmetrical and asymmetrical. Parity is not supported, and for loading reasons, x32 and x64 SIMMs/DIMMs/SO-DIMMs should be used.

## **Second Level Cache**

The second level cache is direct mapped and supports both 256-Kbyte and 512-Kbyte SRAM configuration using Pipeline Burst SRAM or DRAM Cache SRAM. The Cache performance is 3-1-1-1 for line read/write and 3-1-1-1-1-1 for back to back reads that are pipelined. Cacheless configuration is also supported.

## **PCI** Interface

The PCI interface is 2.1 compliant and supports up to four PCI bus masters in addition to the PIIX4 bus master requests.

## **Datapath and Buffers**

The MTXC contains three sets of data buffers for optimizing data flow. A five QWord deep DRAM write buffer is provided for CPU-to-DRAM writes, second level cache write backs, and PCI-to-DRAM transfers. This buffer is used to achieve 3-1-1-1 posted writes to DRAM and also provides DWord merging and burst merging for CPU-to-DRAM write cycles. In addition, an extra line of buffering is provided that is combined with the DRAM Write Buffer to supply an 18 DWord deep buffer for PCI to main memory writes. A five DWord buffer is provided for CPU-to-PCI writes to help maximize the bandwidth for graphic writes to the PCI bus. Also, five QWords of prefetch buffering has been added to the PCI-to-DRAM read path that allows up to two lines of data to be prefetched at an x-2-2-2 rate. The MTXC interfaces directly to the Host and DRAM data bus.

# **Enhanced Power Management Features**

The MTXC implements extensive power management features. The CLKRUN# feature enables controlling of the PCI clock (on/off). The MTXC supports POS, STR, STD, and Soft-off suspend states. SUSCLK and SUSSTAT1# signals are used for implementing Suspend Logic. The MTXC supports two SMRAM modes; Compatible SMRAM (C\_SMRAM) and Extended SMRAM (E\_SMRAM). The C\_SMRAM is the traditional SMRAM feature implemented in Intel PCIsets. The E\_SMRAM is a new feature that supports writeback cacheable SMRAM space up to 1 Mbytes. In order to minimize the idle power, the internal clock in MTXC is turned off (gated off) when there is no activity on the Host and PCI Bus.

PIIX4's power management functions include enhanced clock control, local and global monitoring support for 14 individual devices, and various low-power (suspend) states, such as Power-On Suspend, Suspend-to-DRAM, and Suspend-to-Disk. A hardware-based thermal management circuit permits software-independent entrance to low-power states. PIIX4 has dedicated pins to monitor various external events (e.g., interfaces to a notebook lid, suspend/resume button, battery low

indicators, etc.). PIIX4 contains full support for the Advanced Configuration and Power Interface (ACPI) Specification.

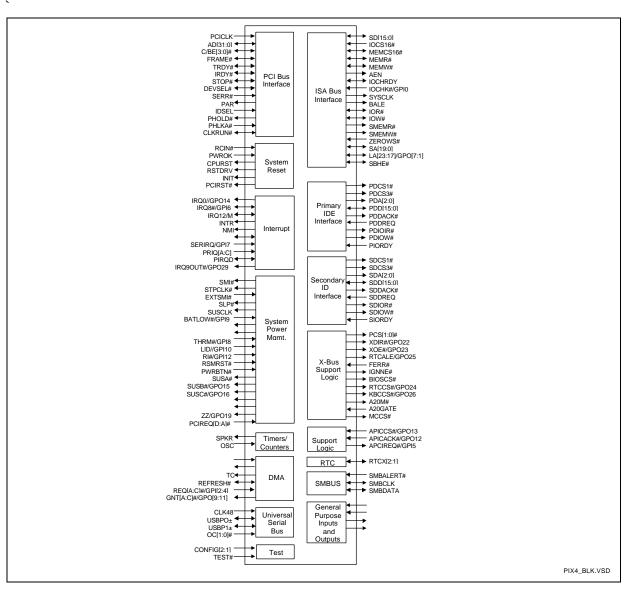

# PCI to ISA/EIO Bridge

PIIX4 is compatible with the PCI Rev 2.1 specification, as well as the IEEE 996 specification for the ISA (AT) bus. On PCI, PIIX4 operates as a master for various internal modules, such as the USB controller, DMA controller, IDE bus master controller, distributed DMA masters, and on behalf of ISA masters. PIIX4 operates as a slave for its internal registers or for cycles that are passed to the ISA or EIO buses. All internal registers are positively decoded.

PIIX4 can be configured for a full ISA bus or a subset of the ISA bus called the Extended IO (EIO) bus. The use of the EIO bus allows unused signals to be configured as general purpose inputs and outputs. PIIX4 can directly drive up to five ISA slots without external data or address buffering. It also provides byte-swap logic, I/O recovery support, wait-state generation, and SYSCLK generation. X-Bus chip selects are provided for Keyboard Controller, BIOS, Real Time Clock, a second microcontroller, as well as two programmable chip selects.

PIIX4 can be configured as either a subtractive decode PCI to ISA bridge or as a positive decode bridge. This gives a system designer the option of placing another subtractive decode bridge in the system (e.g., a 380FB PCI Docking Station PCI Set).

# IDE Interface (Bus Master capability and synchronous DMA Mode)

The fast IDE interface supports up to four IDE devices providing an interface for IDE hard disks and CD ROMs. Each IDE device can have independent timings. The IDE interface supports PIO IDE transfers up to 14 Mbytes/sec. and Bus Master IDE transfers up to 33 Mbytes/sec. It does not consume any ISA DMA resources. The IDE interface integrates 16x32-bit buffers for optimal transfers.

PIIX4's IDE system contains two independent IDE signal channels. They can be electrically isolated independently, allowing for the implementation of a "glueless" Swap Bay. They can be configured to the standard primary and secondary channels (4 devices) or primary drive 0 and primary drive 1 channels (2 devices). This allows flexibility in system design and device power management.

# Compatibility Modules (DMA Controller, Timer/Counters, Interrupt Controller)

The DMA controller incorporates the logic of two 82C37 DMA controllers, with seven independently programmable channels. Channels [0:3] are hardwired to 8-bit, count-by-byte transfers, and channels [5:7] are hardwired to 16-bit, count-by-word transfers. Any two of the seven DMA channels can be programmed to support fast Type-F transfers. The DMA controller also generates the ISA refresh cycles.

The DMA controller supports two separate methods for handling legacy DMA via the PCI bus. The PC/PCI protocol allows PCI-based peripherals to initiate DMA cycles by encoding requests and grants via three PC/PCI REQ#/GNT# pairs. The second method, Distributed DMA, allows reads and writes to 82C37 registers to be distributed to other PCI devices. The two methods can be enabled concurrently. The serial interrupt scheme typically associated with Distributed DMA is also supported.

The timer/counter block contains three counters that are equivalent in function to those found in one 82C54 programmable interval timer. These three counters are combined to provide the system timer function, refresh request, and speaker tone. The 14.31818-MHz oscillator input provides the clock source for these three counters.

PIIX4 provides an ISA-Compatible interrupt controller that incorporates the functionality of two 82C59 interrupt controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are possible. In addition, PIIX4 supports a serial interrupt scheme. PIIX4 provides full support for the use of an external IO APIC.

All of the registers in these modules can be read and restored. This is required to save and restore system state after power has been removed and restored to the circuit.

# **Enhanced Universal Serial Bus (USB) Controller**

The PIIX4 USB controller provides enhanced support for the Universal Host Controller Interface (UHCI). This includes support that allows legacy software to use a USB-based keyboard and mouse.

# **RTC**

PIIX4 contains a Motorola\* MC146818A-compatible real-time clock with 256 bytes of battery-backed RAM. The real-time clock performs two key functions: keeping track of the time of day and storing system data, even when the system is powered down. The RTC operates on a 32.768-kHz crystal and a separate 3V lithium battery that provides up to 7 years of protection.

The RTC also supports two lockable memory ranges. By setting bits in the configuration space, two 8-byte ranges can be locked to read and write accesses. This prevents unauthorized reading of passwords or other system security information.

The RTC also supports a date alarm, that allows for scheduling a wake up event up to 30 days in advance, rather than just 24 hours in advance.

# **GPIO** and Chip Selects

Various general purpose inputs and outputs are provided for custom system design. The number of inputs and outputs varies depending on PIIX4 configuration. Two programmable chip selects are provided which allows the designer to place devices on the X-Bus without the need for external decode logic.

# Pentium and Pentium Pro processor Interface

The PIIX4 CPU interface allows connection to all Pentium and Pentium Pro processors. The Sleep mode for the Pentium Pro processors is also supported.

# System Management Bus (SMBus)

PIIX4 contains an SMBus Host interface that allows the CPU to communicate with SMBus slaves and an SMBus Slave interface that allows external masters to activate power management events.

# Configurability

PIIX4 provides a wide range of system configuration options. This includes full 16-bit I/O decode on internal modules, dynamic disable on all the internal modules, various peripheral decode options, and many options on system configuration.

## 1.1.1 82439TX MTXC Features

- Supports Mobile and Desktop

- Supports the Pentium Processor Family Host Bus at 66 MHz and 60 MHz at 3.3V and 2.5V

- PCI 2.1 Compliant

- Integrated Data Path

- Integrated DRAM Controller

- 4-Mbytes to 256-Mbytes main memory

- 64-Mbit DRAM/SDRAM Technology Support

- FPM (Fast Page Mode), EDO and SDRAM DRAM Support

- 6 RAS Lines Available

- Integrated Programmable Strength for DRAM Interface

- CAS-Before-RAS Refresh, Extended Refresh and Self Refresh for EDO

- CAS-Before-RAS and Self Refresh for SDRAM

- Integrated L2 Cache Controller

- 64-MB DRAM Cacheability

- Direct Mapped Organization—Write Back Only

- Supports 256K and 512K Pipelined Burst SRAM and DRAM Cache SRAM

- Cache Hit Read/Write Cycle Timings at 3-1-1-1

- Back-to-Back Read/Write Cycles at 3-1-1-1-1-1-1

- 64K x 32 SRAM also supported

- Fully Synchronous, Minimum Latency 30/33-MHz PCI Bus Interface

- Five PCI Bus Masters (including PIIX4)

- 10 DWord PCI-to-DRAM Read Prefetch Buffer

- 18 DWord PCI-DRAM Post Buffer

- Multi-Transaction Timer to Support Multiple Short PCI Transactions

- Power Management Features

- PCI CLKRUN# Support

- Dynamic Stop Clock Support

- Suspend to RAM (STR)

- Suspend to Disk (STD)

- Power On Suspend (POS)

- Internal Clock Control

- SDRAM and EDO Self Refresh During Suspend

- ACPI Support

- Compatible SMRAM (C\_SMRAM) and Extended SMRAM (E\_SMRAM)

- SMM Writeback Cacheable in E\_SMRAM Mode up to 1 MB

- 3.3/5V DRAM, 3.3/5V PCI, 3.3/5V Tag and 3.3/2.5 SRAM Support

- Test Features

- NAND Tree Support for all Pins

- Supports the Universal Serial Bus (USB)

- 324-Pin MBGA 430TX PCIset Xcelerated Controller (MTXC) with integrated Data Paths

The Intel 430TX PCIset (430TX) consists of the 82439TX System Controller (MTXC) and the 82371AB PCI ISA IDE Xcelerator (PIIX4). The 430TX supports both mobile and desktop architectures. The 430TX forms a Host-to-PCI bridge and provides the second level cache control and a full function 64-bit data path to main memory. The MTXC integrates the cache and main memory DRAM control functions and provides bus control to transfers between the CPU, cache, main memory, and the PCI Bus. The second level (L2) cache controller supports a writeback cache policy for cache sizes of 256 Kbytes and 512 Kbytes. Cacheless designs are also supported. The cache memory can be implemented with pipelined burst SRAMs or DRAM cache SRAMs. An external Tag RAM is used for the address tag and an internal Tag RAM for the cache line status bits. For the MTXC DRAM controller, six rows are supported for up to 256 Mbytes of main memory. The MTXC is highly integrated by including the Data Path into the same BGA chip. Using the snoop ahead feature, the MTXC allows PCI masters to achieve full PCI bandwidth. For increased system performance, the MTXC integrates posted write and read prefetch buffers. The 430TX integrates many Power Management features that enable the system to save power when the system resources become idle.

Figure 1-2. MTXC Simplified Block Diagram

## 1.1.2 82371AB PIIX4 Features

- Supported Kits for both Pentium and Pentium Pro Microprocessors

- 82430TX ISA Kit

- 82440LX ISA/DP Kit

- Multifunction PCI to ISA Bridge

- Supports PCI at 30 MHz and 33 MHz

- Supports PCI Rev 2.1 specification

- Supports Full ISA or Extended I/O (EIO)

Bus

- Supports full Positive Decode or Subtractive Decode of PCI

- Supports ISA and EIO at 1/4 of PCI frequency

- Supports both Mobile and Desktop Deep Green Environments

- 3.3V Operation with 5V tolerant buffers

- Ultra-low power for mobile environments supports

- Power-On Suspend, Suspend to RAM, Suspend to Disk, and Soft-OFF System States

- All registers readable and restorable for proper resume from 0V suspend

- Power Management Logic

- Global and Local Device Management

- Suspend and Resume Logic

- Supports Thermal Alarm

- Support for external microcontroller

- Full support for Advanced Configuration and Power Interface (ACPI) Revision 1.0 Specification and OS Directed Power Management

- Integrated IDE Controller

- Independent Timing of up to 4 drives

- PIO Mode 4 and Bus Master IDE transfers up to 14 Mbytes/sec

- Supports "Últra DMA33" Synchronous DMA mode transfers up to 33 Mbytes/sec

- Integrated 16 x 32-bit buffer for IDE PCI Burst transfers

- Supports glue-less 'Swap-Bay" option with full electrical isolation

- **■** Enhanced DMA Controller

- Two 82C37 DMA controllers

- Supports PCI DMA with three PC/PCI channels and Distributed DMA protocols (simultaneously)

- Fast Type-F DMA for reduced PCI bus usage

- Interrupt Controller based on two 82C59

- 15 interrupt support

- Independently programmable for Edge/Level sensitivity

- Supports Optional I/O APIC

- Serial Interrupt input

- Timers based on 82C54

- System Timer, Refresh Request, Speaker Tone Output

- USE

- Two USB 1.0 ports for serial transfers at 12 or 1.5 Mbit/sec

- Supports legacy keyboard and mouse software with USB-based keyboard and mouse

- Supports UHCI Design Guide

- SMBus

- Host interface allows CPU to communicate via SMBus

- Slave interface allows external SMBus master to control resume events

- Real-Time Clock

- 256-byte Battery-Back CMOS SRAM

- Includes Date Alarm

- Two 8-byte Lockout Ranges

- Microsoft Win95\* Compliant

- 324 MBGA Package

The PCI ISA IDE Xcelerator (PIIX4) is a multi-function PCI device implementing a PCI-to-ISA bridge function, a PCI IDE function, a Universal Serial Bus host/hub function, and an Enhanced Power Management function. As a PCI-to-ISA bridge, PIIX4 integrates many common I/O functions found in ISA-based PC systems—two 82C37 DMA Controllers, two 82C59 Interrupt Controllers, an 82C54 Timer/Counter, and a Real Time Clock. In addition to Compatible transfers, each DMA channel supports Type F transfers. PIIX4 also contains full support for both PC/PCI and Distributed DMA protocols implementing PCI based DMA. The Interrupt Controller has Edge or Level sensitive programmable inputs and fully supports the use of an external I/O Advanced Programmable Interrupt Controller (APIC) and Serial Interrupts. Chip select decoding is provided for BIOS, Real Time Clock, Keyboard Controller, second external microcontroller, as well as two Programmable Chip Selects. PIIX4 provides full Plug and Play compatibility. PIIX4 can be configured as a Subtractive Decode bridge or as a Positive Decode bridge. This allows the use of a subtractive decode PCI-to-PCI bridge such as the 380FBPCIset which implements a PCI/ISA docking station environment.

## **OVERVIEW**

PIIX4 supports two IDE connectors for up to four IDE devices providing an interface for IDE hard disks and CD ROMs. Up to four IDE devices can be supported in Bus Master mode. PIIX4 contains support for "Ultra DMA/33" synchronous DMA compatible devices.

PIIX4 contains a Universal Serial Bus (USB) Host Controller that is Universal Host Controller Interface (UHCI) compatible. The Host Controller's root hub has two programmable USB ports.

PIIX4 supports Enhanced Power Management, including full Clock Control, Device Management for up to 14 devices, and Suspend and Resume logic with Power On Suspend, Suspend to RAM or Suspend to Disk. It fully supports Operating System Directed Power Management via the Advanced Configuration and Power Interface (ACPI) specification. PIIX4 integrates both a System Management Bus (SMBus) Host and Slave interface for serial communication with other devices.

Figure 1-3. PIIX4 Simplified Block Diagram

1-9

# Flexible Motherboard Design Layout Review Checklist

# CHAPTER 2 FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST

# 2. Flexible Motherboard Design Layout Review Checklist

The following checklist is a guide when designing or reviewing a board design that uses the Intel 430TXPCIset (430TX).

# 2.1 MTXC Design Checklist

#### 2.1.1 Clocks

- Refer to Section 3 for clock layout and routing recommendations.

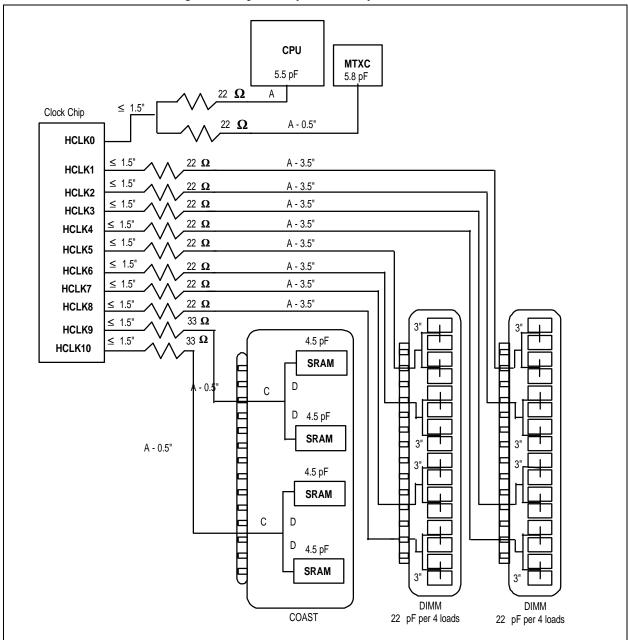

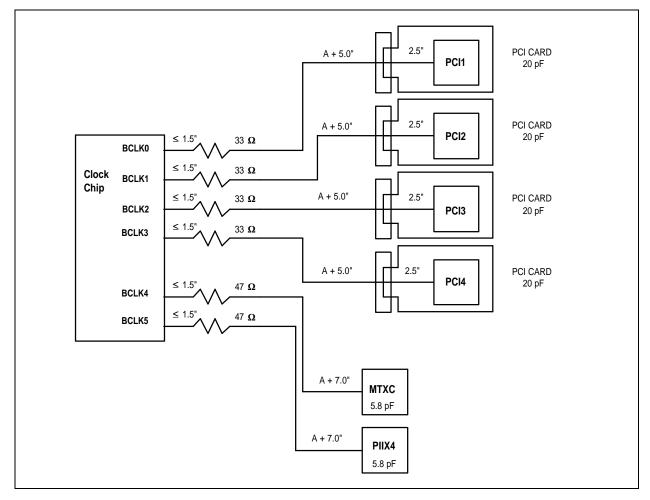

- The CPU and MTXC clock should be on the same net. Only two PBSRAMs per clock net. Four separate clocks are connected to a double sided SDRAM DIMM.

- Two separate clocks are connected to a COAST module when supporting 512K dual bank configuration.

- CPU clocks—The CLK input on the P54 family is 5V tolerant. The CLK input on the P55C family is **not** 5V tolerant.

- The clock synthesizer used should be compliant to the "CKDM66-M Clock Synthesizer Specification."

- The latest CKDM66-M clock synthesizer specification redefines the functionality of pin 47. Pin 47 used to be a clock output (14.318 MHz), but the new spec requires that pin 47 be used for strapping of the voltage level. For desktop designs, pin 47 should be left as a No Connect, as a weak pull up is integrated in the clock synthesizer. The extra clock output will be provided by adding another load to the clock output from either pin 1 or pin 2. A series termination of 33 ohm is recommended when adding a clock trunk to pin 1 or pin 2. Please contact your clock synthesizer vendor for more details.

# 2.1.2 MTXC Power

- To avoid any leakage issues, the designer must take care that pull-up resistors on any signal are tied to the power plane in which that signal resides. Likewise, any external logic or buffer to which a signal is connected should be powered up only while that signal's power plane is powered up. Generally, no signal should see a voltage potential higher than that of the plane in which it resides. The only exceptions are the 5V tolerant signals, which may see 5V potentials during active states if the V<sub>REF</sub> pin has been tied to a 5V supply.

- V<sub>CC</sub>(CORE) must be tied to 3.3V.

- $V_{CC}(CPU)$ —For all desktop designs,  $V_{CC}(CPU)$  must be tied to 3.3V.

- V<sub>CC</sub>(SUS) must be tied to a 3.3V supply that is active during Suspend to RAM. If Suspend to RAM state is not used then V<sub>CC</sub>(SUS) must be tied directly to 3.3V.

- All three V<sub>CCS</sub> (i.e. V<sub>CC</sub>(CORE), V<sub>CC</sub>(CPU), and V<sub>CC</sub>(SUS)) can be tied to the same 3.3V plane.

- If implementing the MTXC  $V_{CC}(CPU)$  and CPU CPUVIO voltages through independent power planes, it should be verified that the CPU will not drive any signals to the MTXC above  $V_{IH}=V_{CC}(CPU)+0.3$ .

- In a system that implements  $V_{CC}(CORE)$  and  $V_{CC}(CPU)$  as independent power planes, the  $V_{CC}(CPU)$  pins must power up after or simultaneous to  $V_{CC}(CORE)$ , and must power down before or simultaneous to  $V_{CC}(CORE)$ . At any time,  $V_{CC}(CORE)$  should not be more than 1.2V below the  $V_{CC}(CPU)$  plane.  $V_{CC}(SUS)$  can power up and power down independent of all other power planes.

- V<sub>CC</sub>5<sub>REF</sub> MTXC Power Up Requirements—Refer to the 82439TX System Controller datasheet. V<sub>CC</sub>5<sub>REF</sub> must be tied to 5V in a 5V tolerant system. This signal must be powered up before or simultaneous to V<sub>CC</sub>(CORE), and it must be powered down after or simultaneous to V<sub>CC</sub>(CORE). V<sub>CC</sub>5<sub>REF</sub> can be tied directly to V<sub>CC</sub>(CORE) in a non-5V tolerant system. The V<sub>CC</sub>5<sub>REF</sub> circuitry can be shared between MTXC and PIIX4. If the circuitry is placed close to the MTXC, then please ensure that an extra 1μf capacitor is placed on the V<sub>EF</sub> pin of the PIIX4.

- Tie V<sub>SS</sub> to ground.

POWER PINS

BALL#

V<sub>CC</sub>(CORE)

F05, L16, E12, F14, F15, P15, R15, T13

V<sub>CC</sub>(CPU)

F06, G06, R06, R07

V<sub>CC</sub>5<sub>REF</sub>

E14

V<sub>CC</sub>(SUS)

P16, R16, N16

V<sub>SS</sub>

E15, J09, J10, J11, J12, K09, K10, K11, K12, L09, L10, L11, L12, M09, M10, M11, M12, T06, T16

**Table 2-1. MTXC Power Pin Summary**

# 2.1.3 Host Interface

- A27 strapping option—This MTXC signal has a weak pull-down and should be pulled up (with an external pull-up) for a host bus frequency of 60 MHz, and left as a no connect for a host bus frequency of 66 MHz. The inverted state of A27 at reset rising determines the DRAM refresh rate and host bus frequency for the TX. The state is sampled and stored in bit 7 of DRTH—DRAM ROW TYPE REGISTER HIGH. BIOS can use this bit to determine if the system host bus frequency is 60 MHz or 66 MHz.

- A26 strapping option—This strap should be tied to V<sub>SS</sub> (weak pull-down) for a 2.5V CPU interface, and should be tied to 3.3V V<sub>CC</sub>(CORE) for a 3.3V CPU I/O interface. For all desktop designs, A26 should be tied to 3.3V through a weak pull up (2Rohm).

- Pull-ups to 3.3V (CPU I/O voltage)—A20M#, SMI#, STPCLK#, INTR, NMI, and IGNNE# (4.7 kohm). These are open collector outputs from the PIIX4 component.

- No external logic is required between INIT and Keyboard Reset. This logic has been integrated in PIIX4. Keyboard Reset is tied into RCIN# input of PIIX4. Refer to reference schematics for implementation details.

- Internal CPU connections for BF0 and BF1 on the P54 are different from the way BF0 and BF1 are connected internally on the P55C. Please see the table below.

|      | BF0                               | BF1                             |

|------|-----------------------------------|---------------------------------|

| P54C | Internal pull-up (default is 1)   | Internal pull-up (default is 1) |

| P55C | Internal pull-down (default is 0) | Internal pull-up (default is 1) |

Table 2-2. Bus Frequency Pull-ups

- Refer to the "P55C/FMB Design Review Checklist," "Socket 7 Design Review Checklist," and "Socket 7 Specification" for additional information on CPU related requirements including CPU decoupling requirements.

- $V_{CC}$ 2DET (P55C)—This signal can be used as a safeguard to prevent plugging a P54C into a socket set up for P55C support (2.8 Vcore). The P55C will always drive  $V_{CC}$ 2DET low. This pin can be used in a flexible motherboard implementation to correctly set the voltage regulator to drive the correct  $V_{CC}$  to the CPU.

- ADSC# should be used to drive the cache subsystem and ADS# should be used to drive the chip set. These signals are functionally identical to each other and two copies are provided by the processor for loading reasons.

- INV and KEN# should be tied together at the CPU. The 430TX muxes these signals. KEN# is used during CPU read cycles and INV is used during L1 snoop cycles.

- Pull-ups (3V)—FLUSH#, FRCMC#, WB/WT#, AP, & PEN# (8k2bhm).

- The HOLD and EWBE# pins on the processor are tied to ground.

- No Connects—R/S#, TCK, TDI, TMS, TRST#, APCHK#, BP[3:0], HIT#, HLDA, IERR#, PCHK#, PRDY, PWT, PCD, SCYC, TDO, PICCLK, PICDO, PICD1, PHITM#, PHIT#, PBGNT#, CPUTYP, PBREQ#, U/O# (or D/P#), UPVRM (or KEY), BUSCHK#, BRDYC#, BREQ#. Please note that BUSCHK# and BRDYC# have pull up resistors shown on the schematics. These two signals can be left as no connects also.

- Host Bus Parity—The 430TX does not support host bus parity so these signals are not used. Data parity pins DP[7:0] on the CPU are pulled up through weak pull up resistors on the motherboard.

- Unlike the Pentium processor, these inputs on the P55C are not 5V tolerant: CLK, PICCLK, AHOLD, BRDYC#, EADS#, KEN, WB/WT#, INV, NA#, EWBE#, BOFF#.

- Split Core V<sub>CC</sub>2 for P55C—The P55C requires two supply voltages; 2.8V±5% on its Vcore pins. Its external I/O pins operate at STDE (3.125-3.6V) levels. If a dual regulator is used to support the P54CS and P55C, then the core current requirement is 5.7A and the I/O requirements is 1A. These regulators supply voltages exclusively for the CPU plane. The I/O regulator is set up for 2.8/3.5V and the I/O regulator is set up for 3.3/3.5V. The VRE CPU's operate at the voltage level of 3.5V for both core and I/O. It is not an absolute requirement to set these regulators to 3.5V. The main goal is to keep the voltage levels within the specified voltage range of the CPU.

- The PCIRST# signal from PIIX4 is used to reset the MTXC RST# signal.

- Internal pull-downs—HD[63:0] on the MTXC have internal pull-downs. External pull-ups/pull-downs are not required.

- CPURST and INIT are timing critical, open collector outputs from the PIIX4 and need strong pull-ups (1 kohm).

## 2.1.4 L2 Cache

- A31:A30 Strapping Option—Secondary Cache Size. 1 = pull-up (4.7 kohm), 0 = pull-down (4.7 kohm)

- 11 Cache NOT POPULATED

- 1 0 256 Kbytes

- 0 1 512 Kbytes

- 00 Reserved

Note: These values are inverted from the value stored in the configuration register.

#### FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST

- A29:A28 Strapping Option—L2 SRAM Type. 1 = pull-up (4kohm), 0 = pull-down (4.7kohm)

- 11 PBSRAM

- 10 Reserved

- 0 1 Reserved

- 00 2 Banks of PBSRAM

Note: These values are inverted from the value stored in the configuration register. If the 512K cache is implemented using four 32Kx32 PBSRAMs, then select the "2 Banks of PBSRAM" option from the above table. If the 512K cache is implemented using two 64Kx32 PBSRAMs, then select the "PBSRAM" option from the above table.

- GWE# and BWE#—The MTXC only supports PBSRAM devices that use GWE# (Global Write Enable) and BWE#. GWE# and BWE# must be connected from the MTXC to each of the PBSRAMs.

- Proper Speed Parts—Intel recommends the use of PBSRAMs with too of 8.5 ns and cycle times of 15 ns, and 15 ns Tag for operation at 66 MHz host bus frequencies.

- TIO[7:0] on the MTXC have internal pull-downs (20cohm). Externals are not required.

- 512K PBSRAM Support—A18 determines which bank is accessed in a dual bank 512K configuration. This address is connected to CE2 on the PBSRAMs of the lower bank and CE3# of the upper bank PBSRAMs. A18 is required when the 512K cache is implemented using four 32Kx32 PBSRAMs. If the 512K is implemented using two 64Kx32 PBSRAMs then A18 should not be used for depth expansion. In other words, tie the CE2 and CE3# on both the PBSRAMs to an active state. Please note that A18 is still required for the Tag RAM addressing as shown in the schematics. It is also required for addressing the PBSRAMs.

- COAST Modules—If a COAST module is used, all recommendations and specifications contained in the COAST specification (Rev 3.1 and 3.1a) must be followed.

- DRAM cache logic—The 430TX provides an option for DRAM cache implementation. Additional logic is required to support this option. Refer to the cache pages in the reference schematics for information. (1) PCIRST# should be used for the reset to the DRAM CACHE. (2) KRQAK pin needs a weak pull up resistor for strapping DRAM cache (~10 kohm). If DRAM cache is not used, then no external pull-up or pull-downs are needed. (3) Only one of the DRAM cache devices should be strapped as Master.

# 2.1.5 DRAM

- For desktop designs we do not recommend the use of CKE and CKEB pins from the MTXC. These pins should be pulled high to 3.3V at the DIMM connector on the motherboard (pins 63 and 128 of DIMM).

- CKEB is not in the Suspend Well. This signal cannot be used on systems that implement Suspend to RAM (STR). For desktop designs we do not recommend the use of STR state.

- The MTXC A-1 provides a second copy of MA lines by muxing the CKE(MAA0) and CKEB(MAA1) signals. This means that CKE and CKEB function cannot be used if the second copy of MA lines are implemented. CKE functionality is not required in a desktop system.

- The first pair of MA0 and MA1 lines should be tied to the first DIMM. The second pair of MAA0 and MAA1 lines should be tied to the second DIMM. The CKE0 and CKE1 pins on both the DIMMS should be tied to 3.3V

- Note: It is recommended that this feature only be implemented on those boards that are intended to be used with the A-1 MTXC (or beyond) stepping (i.e. boards that are populated with the A-0 MTXC, should not implement this feature).

- MA[11:0] and WE# buffering—External buffering on the MA lines and WE# lines is not required, and must not be implemented in a system with four rows of memory. These lines must be connected directly to the DRAM. The MTXC provides integrated programmable buffers on the MA lines and two copies of MWE# (MWE# and MWEB#). The MTXC also provides two copies of

#### FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST

SRAS# (SRASA# and SRASB#) and SCAS# (SCASA# and SCASB#). Two copies of these signals were provided for loading reasons and should be evenly distributed throughout the DRAM subsystem. Please refer to the last paragraph of this section for series termination on memory control and address signals.

- The desktop reference design shows implementation using 4 rows of memory (2 DIMMs). If a design is implemented using more than 4 rows of memory, then please follow the guidelines listed in the 430TX Data Sheet. External buffering of signals is required for certain cases.

- Internal pull-downs—MD[63:0] on the MTXC have internal pull-downs. External pull-ups/pull-downs are not required.

- SDRAM—Refer to the latest Unbuffered Standard SDRAM DIMM specification for the latest DIMM and connectorpinout.

- The MTXC supports unbuffered DIMM modules only. SDRAM DIMMs require four separate HCLKs.

- Most SDRAM will be 3V only (i.e. SDRAM I/O pins will not be 5V tolerant). When mixing and

matching SDRAM with EDO/FPM, the EDO/FPM should also be 3V (i.e. receive and drive 3V

levels).

- 64-Mbit SDRAM Support—This feature is supported on A-1 MTXC. A-0 MTXC does not support 64-Mbit SDRAM.

# When 64MTEN = 0, (TIEN is Address offset 54, bit 1)

RAS5#/CS5#/MA13 drives RAS5#/CS5#

RAS4#/CS4#/BA1 drives RAS4#/CS4#

MA11/BA0 drives MA11

# When 64MTEN = 1,

RAS5#/CS5#/MA13 drives MA13

RAS4#/CS4#/BA1 drives BA1

MA11/BA0 drives MA11

# DIMM wiring guideline

- Connect MA11/BA0 to pin 122 of DIMM (BA0 for SDRAM, A11 for EDO/FPM)

- Connect RAS4#/CS4#/BA1 to pins 39 and 126 of DIMM (BA1, A12 for SDRAM, A12 for EDO/FPM)

- Connect RAS5#/CS5#/MA13 to pin 123 of DIMM (A11 for SDRAM, A13 for EDO/FPM)

- The A-1 MTXC will support five rows of 64-Mbit SDRAM.

In a five row SDRAM system that supports 64-Mbit SDRAM devices, KRQAK is muxed to provide the 5<sup>th</sup> CS# (or CS4#) function. This means that a system that supports DRAM cache cannot support five rows of 64-Mbit SDRAM. However, four rows of 64-Mbit SDRAM with DRAM cache is supported. Note: It is recommended that the 5<sup>th</sup> row feature only be implemented on those boards that are intended to be used with the A-1 MTXC (or beyond) stepping (i.e. boards that are populated with the A-0 MTXC, should not implement this feature).

When 64MTEN = 1 and DRAM Cache is not in the system (Bit 5 in Reg. offset 53h = 0)—64-Mbit SDRAM support is enabled for Five rowk. DRAM cache is in the system, then a pull-up resistor is present on the KRQAK pin. If DRAM cache is not in the system, then no resistor is present on the KRQAK line. Bit 5 in register offset 53h reflects the level of the KRQAK signal at power-up.

RAS5#/CS5#/MA13 drives MA13

RAS4#/CS4#/BA1 drives BA1

KRQAK/FRCL# drives FRCL# (or CS4#)

• Address input A13 to the DIMMs should not be left floating. The reference schematics use a 100 ohm pull down to ground on A13.

- Generally, only SDRAM and EDO come on DIMMs, however the DIMM spec also specifies FPM. To support EDO/FPM on the same DIMM, OE0# (pin 31) and OE2# (pin 44) on the DIMM connector must be connected to ground on the motherboard, and WE2# (pin 48) must be connected to one of the MTXC's memory write enable signals (MWE# or MWEB#).

- Parity—The 430TX does not support parity and requires that non-parity SIMMs and DIMMs be used.

- Since the DIMMs have only 3 address bits for the SMBus (SA2, SA1 and SA0), the BIOS should handle all address aliasing issues. The twoDIMMs should be strapped to unique addresses.

- SMBCLK and SMBDATA should be pulled up to the 3.3V core plane through 8.2 kohm resistors. It follows that the SMBus cannot be used as a resume event during STD/Soft-off since it is not tied to a standby voltage. These should not be pulled up to 3 VSB when used with devices being powered from the core voltage (e.g. SDRAM) due to excessive leakage when the core voltage is off. If they are pulled up to 3VSB then all the devices on the SMBus should be tied to 3 VSB. (This checklist item is not reflected in reference board schematics Rev. 2.1 ogerber files.)

- To insure that DRAM interface signal integrity is maintained for lightly loaded desktop systems, series termination and/or diodes (ground and V<sub>CC</sub> diodes) are recommended on the following signals: CAS#/DQMx, MWEx, SCASx, SRASx, CKEx, and all MA lines (Note: RAS4# and RAS5# are also used as MA lines, depending on the configuration, and should be terminated when used as MA lines). This will insure that the overshoot, undershoot, and most importantly, ring-back does not cause any problems.

- If series termination is used, use 10 ohm. This value provides the best signal integrity and flight time results. Place as close to the driver as possible. If diodes are used, the diodes should have a forward current of at least 200 mA at 1V. A MMBD1203 diode or equivalent meets this requirement. The diodes should be placed at the end of the trace. Diodes improve signal integrity without increasing the flight time. A 10 ohm series resistor will increase the flight time by approximately 300 ps. Both provide similar signal integrity results. The reference schematics show this implementation using 10 ohm series resistors.

# 2.2 PIIX4 Design Checklist

## 2.2.1 Power and Ground Pins

- To avoid any leakage issues, the designer must take care that pull-up resistors on any signal are tied to the power plane in which that signal resides. Likewise, any external logic or buffer to which a signal is connected should be powered up only while that signal's power plane is powered up. Generally, no signal should see a voltage potential higher than that of the plane in which it resides. The only exceptions are the 5V tolerant signals, which may see 5V potentials during active states if the V<sub>REF</sub> pin has been tied to a 5V supply.

- $V_{CC}$ ,  $V_{CC}(RTC)$ , and  $V_{CC}(USB)$  must be tied to 3.3V.

- Standby voltage from the power supply is used to power the resume well V<sub>CC</sub>(SUS), V<sub>CC</sub>(RTC) and the RSMRST# signal. If the standby voltage from power supply is at 5V, it must be divided down to 3.3V. In the 430TX reference board design, a Zener diode voltage regulator circuitry is used to provide the 3V standby voltage. This circuitry consists of a series resistor and a Zener diode with two capacitors provided to filter out noise. The Zener diode/series resistor should be validated to make sure the standby voltage is clamped to 3.3V. The series resistor value can be changed to correct the standby voltage and current requirements. The reference design uses a Zener diode that requires approximately 20 mA to sustain 3.3V, however a different Zener diode, requiring less current, can be used. Also note that the standby voltage connection to V<sub>CC</sub>(RTC) helps in preserving the on-board battery. Please refer to the schematics for implementation details.

- ullet  $V_{REF}$  must be tied to 5V in a 5V tolerant system. This signal must be powered up before or simultaneous to  $V_{CC}$ , and it must be powered down after or simultaneous to  $V_{CC}$ . The  $V_{REF}$

# FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST

circuitry can be shared between the MTXC and PIIX4. If the circuitry is placed close to the PIIX4, then please ensure that an extra 1  $\mu$ f capacitor is placed on the  $V_{C}5_{REF}$  pin of the MTXC.

- V<sub>REF</sub> can be tied to 3.3V V<sub>CC</sub> in a non-5V tolerant system.

- Tie  $V_{SS}$  and  $V_{SS}(USB)$  to ground.

Table 2-3. PIIX4 Power Pin Summary

| POWER PINS            | BALL#                                                         |

|-----------------------|---------------------------------------------------------------|

| V <sub>CC</sub>       | E9, E11, E12, E16, F5, F6, F14, F15, G6, P15, R6, R7, R15, T6 |

| V <sub>CC</sub> (RTC) | L16                                                           |

| V <sub>CC</sub> (SUS) | N16, R16                                                      |

| V <sub>CC</sub> (USB) | K5                                                            |

| V <sub>SS</sub> (USB) | J5                                                            |

| V <sub>SS</sub>       | D10, E7, E13, J9–J12, K9–K12, L9–L12, M9–M12                  |

| No Connects           | J4, M5, M16, N3, N18, R5                                      |

• The reference schematics show an implementation with a power supply capable of providing a standby voltage. It is not a requirement to design a system that relies on power supplies capable of providing standby voltages. In such cases, the pull-ups which are to 3.3 VSB can be replaced with pull-ups to 3.3 V.

# 2.2.2 PCI Bus Signals

- 5V PCI environment—2.7 kohm pull-up resistors to 5V on PIRQ[A:D]#, SDONE, SBO#, FRAME#, TRDY#, STOP#, IRDY#, DEVSEL#, PLOCK#, PERR#, SERR#, REQ64# and ACK64# and PAR on PCI connectors. Resistors (10kohm) on REQ[3:0]#.

- 3.3V PCI environment—10 kohm pull-up resistors to 3.3V on PIRQ[A:D]#, SDONE, SBO#, FRAME#, TRDY#, STOP#, IRDY#, DEVSEL#, PLOCK#, PERR#, SERR#, and REQ64# and ACK64# and PAR on PCI connectors. Resistors (10kohm) on REQ[3:0]#.

- Pull-ups to 3V—10kohm pull-ups on GNT[3:0]#

- PCI slots—The 430TX supports up to four PCI masters with REQ[3:0]# and GNT[3:0]#. Also, it is recommended, per the PCI Spec. 2.1, to place series resistors (~100 ohm) on each of the PCI connector IDSEL lines.

- PHLD# and PHLDA#—10kohm pull-ups to 3V.

- The PCI Boundary Scan signals on the PCI connector are TRST#, TMS, TDI, TDO, and TCK. Pull-up and pull-down resistor values for these signals should follow the recommendations listed in the PCI Specification, Rev 2.1. If boundary scan is not supported on the motherboard, then TMS (connector pin A3) and TDI (connector pin A4) should be independently bused and pulled up, each with ~5 kohm resistors. TRST# (connector pin A1) and TCK (connector pin B2) should be independently bused and pulled down, each with ~5 kohm resistors. TDO (connector pin B4) should be left open. This checklist item is not reflected in reference board schematics Rev. 2.1.

## 2.2.3 ISA Signals

- 10 kohm pull-up on SD[15:0].

- 1 kohm pull-up on IOCHRDY and REFRESH#.

- 8.2 kohm pull-up on IRQx, MEMR#, MEMW#, IOR#, IOW#, LA [23:17], SA [19:0], SMEMR#, SMEMW#, SBHE#, BALE. The PIIX4 is not 5V tolerant on IRQ8 as V<sub>CC</sub>(SUS) is tied to the 3V levels. Please refer to the data sheet for a list of signals that are not 5V tolerant. If an external RTC is used, then please ensure that IRQ8 is not driven to the 5V levels.

#### FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST

- If Power-On-Suspend (POS) is to be implemented, the pull-ups on ISA SA[19:0] signals should be removed due to possible reverse current leakage on the ISA bus during this state. The ISA specification does not require pull-ups on the SA[19..0] lines. This checklist item is not reflected in the reference board schematics Rev. 2.1.

- 5.6 kohm pull-down on DRQx.

- MASTER#—The PIIX4 doesn't require connection with the MASTER# signal from the ISA bus (same as the PIIX3). Place a pull-up resistor (300 ohm) on MASTER# signal from ISA connectors.

- 1 kohm pull-up on MEMCS16#, IOCS16#, ZEROWS#. This checklist item is not reflected in reference board schematics Rev. 2.1.

- 4.7 kohm pull-up on IOCHK#.

- Some of the ISA signals shown in the schematics will have slightly different pull-up resistor values than recommended in this checklist. This was done to optimize for resistor packs selected for the design.

# 2.2.4 X-Bus Signals

- XOE# and XDIR# are connected to the ULTRA I/O device.

- If the internal RTC is used, RTCALE and RTCCS# are no connect or become general purpose outputs by programming the General Configuration Register(GENCFG) in Function 0, Offset B0h-B3h.

# 2.2.5 Power Management Signals

- CLKRUN#—If CLKRUN# is not connected between PIIX4 and MTXC, it should be tied low through a 100 ohm resistor at the MTXC. If CLKRUN# is connected between PIIX4 and MTXC, it should have a weak pull-up resistor on the CLKRUN# signal.

- SUS\_STAT1# and SUSCLK are connected between the MTXC and PIIX4. These are required for all designs even if power management features are not utilized.

- SUSC# is connected to the power supply through an inverter to control the remote-off function.

- ZZ is connected to the ZZ pin on the cache when the ZZ feature is used.

- PCIREQ[3:0]# is connected between the PIIX4 and the PCI bus. Bus master requests are considered as power management events.

- PWRBTN#—This signal is connected to front panel on/off power button. The logic on power button circuitry should be powered using the 3V standby voltage.

- RSMRST#—Standby voltage should be provided to RSMRST# input at a 3V level. The RSMST# connection requires a minimum time delay of 1 millisecond from the rising edge of the standby power supply voltage. A Schmitt trigger circuit is recommended to drive the RSMRST# signal. To provide the required rise time, the 1 millisecond delay should be placed before the Schmitt trigger circuit. The reference design implements a 20 ms delay at the input of the Schmitt trigger to ensure the Schmitt trigger has sufficiently powered up before switching the input. Also ensure that voltage on RSMRST# does not exceed V<sub>CC</sub>(RTC). Refer to the reference schematics for implementation details. If standby voltage is not provided by the power supply, tie the PWROK signal on the PIIX4 to the RSMRST# signal.

Based on the resistor values and input capacitance of the PIIX4 RSMRST# pin, the rise time in the reference board schematics is approximately 170 ns (within the max. 250 ns requirement for the PIIX4). It is important that if any other components are connected to RSMRST#, the resistor divider values may need to be adjusted to meet a faster rise time required by the other parts and increased loading. 3V driving devices, such as an 74LVC14 could also be used as a replacement for the voltage divider.

• THRM# is connected to thermal protection logic if used.

# int<sub>d</sub>®

#### FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST

• RI# is connected to the modem if this feature is used. To implement ring indicate as a wake event from STD, the source driving the RI# signal must be powered when the PIIX4 suspend well is powered.

# 2.2.6 Power Button Implementation

The items below should be considered when implementing a power management model for a desktop system. The power states are as follows:

- S1 POS (CPU context not lost)

- S2 POSCCL (CPU context lost)

- S3 STR

- S4 STD

- S5 Soft-off

- Wake: Pressing the power button wakes the computer from S1-S5.

- Sleep: Pressing the power button signals software/firmware in the following manner:

- If SCI is enabled, the power button will generate an SCI to the OS.

- The OS will implement the power button policy to allow orderly shutdowns.

- Do not override this with additional hardware.

- If SCI is not enabled:

- Enable the power button to generate an SMI and go directly to soft-off or a supported sleep state.

- Poll the power button status bit during POST while SMIs are not loaded and go directly to soft-off if it gets set.

- Always install an SMI handler for the power button that operates until ACPI is enabled.

- Emergency Override: Pressing the power button for 4 seconds goes directly to S5.

- This is only to be used in EMERGENCIES when software is locked-up.

- This will cause user data to be lost in most cases.

- Do not promote pressing the power button for 4 seconds as the normal mechanism to power the machine off—this violates ACPI

- To be compliant with the latest PC97 Specification, machines must appear off to the user when in the S1–S4 sleeping states. This includes:

- All lights except a power state light must be off.

- The system must be inaudible: Silent or stopped fan; drives are off.

- Please contact Microsoft for the latest information concerning PC97 and Microsoft Logo programs.

# 2.2.7 USB Interface

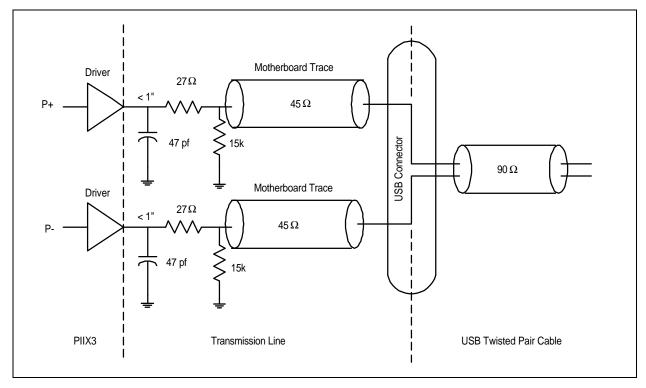

• Refer to Section 3.6 for the layout recommendations for USB signals.

# 2.2.8 IDE Interface

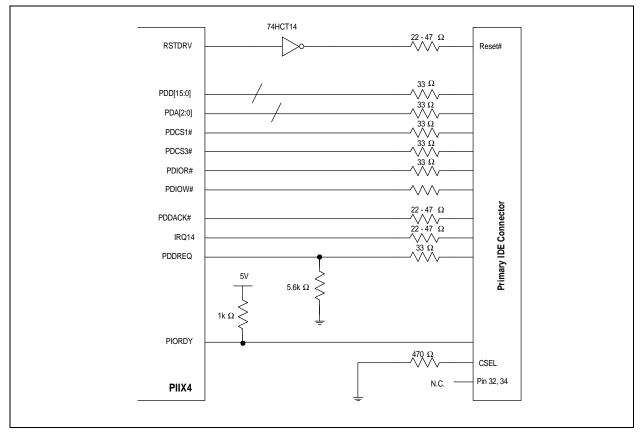

- 5.6 kohm pull-down resistors on PDDREQ and SDDREQ.

- 1 kohm pull-up resistors on PIORDY# and SIORDY#.

- 470 ohm pull-down resistor on pin 28 of the IDE connectors(CSEL). The state of the cable select pin determines the master/slave configuration of the hard drive at the end of the cable.

- Primary IDE connector uses IRQ14 and the secondary IDE connector uses IRQ15.

- All signals running to the two IDE connectors (except for PIORDY# and SIORDY# which are 47 ohm) have series termination resistors of 33 ohm. These series termination resistors should be placed as close as possible to the ATA connectors.

- Layout—Proper operation of the IDE circuit depends on the total length of the IDE bus. The total signal length from the IDE drivers to the end of the IDE cables should not exceed 18". Therefore, the PIIX4 should be located at close as possible to the ATA connectors to allow the IDE cable to be as long as possible.

- Use ISA reset signal RSTDRV from PIIX4 through Schmitt trigger for RESET# signals.

- Ground pin 19, 2, 22, 24, 26, 30, 40 on both ATA connectors

- No connect on pin 20, 32, 34 on both ATA connectors.

- Please note that the Primary IDE connector and the Secondary IDE connector have separate sets of DATA lines on the PIIX4. This has changed from PIIX3, where a single set of data line was only provided by the PIIX3.

- There is no internal pull-up or down on PDD7 or SDD7 of the PIIX4. The ATA3 specification requires a 10 Kohm pull-down on DD7 in section 4.3.1. Devices shall not have a pull-up resistor on DD7. It is recommended that a host have a 10 Kohm pull-down resistor on PDD7 and SDD7 to allow the host to recognize the absence of a device at power-up. It is intended that this recommendation become mandatory in the next revision of this standard.

- Please refer to Section 3.5 for IDE routing recommendations.

# 2.2.9 System and Test Signals

- 1 kohm pull-up resistor on TEST#.

- In a Pentium processor system, CONFIG[1] should be connected to ground. In a Pentium Pro Processor system, CONFIG[1] should be connected to V<sub>CC</sub>. CONFIG[2] should be tied to ground in all 430TX based designs.

# 2.2.10 Clocks

Refer to Section 3 for clock and general board layout recommendations.

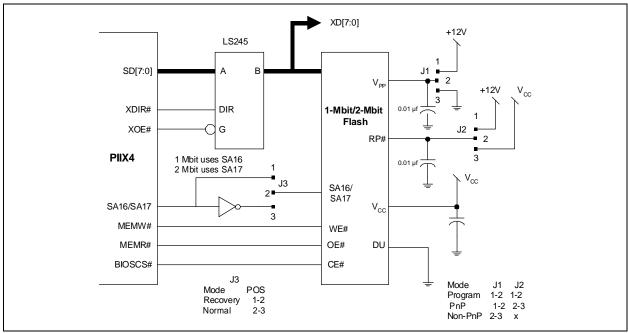

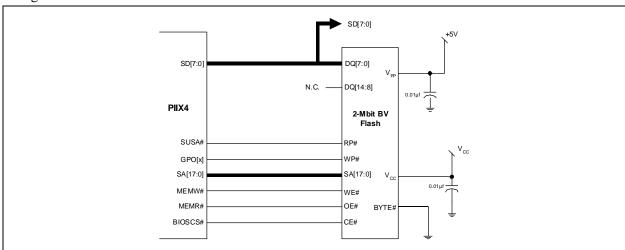

# 2.3 Flash

- 1-Mbit flash—1 Mbit of flash is generally all that is required to support the 430TX in all configurations. However, it is highly recommended that support for an optional 2M Boot Block Flash be designed in, even if a 1-Mbit device is planned (each size comes in a different package type). By simply laying out 2 pad sets, one for the 1-Mbit device, and another for a 2-Mbit device, the board will allow the use of a 2-Mbit flash if the BIOS becomes larger than Mbit.

- For a 2-Mbit flash implementation, there is no need to externally OR BIOSCS# with XOE# to drive the CE# input of the flash device. This logic is integrated in PIIX4.

- Connect V<sub>PP</sub> to GND for write protection.

- Use 0.01 μf-0.1 μf capacitors for power supply (Υ<sub>C</sub> and V<sub>PP</sub>) decoupling.

- Connect BYTE# to GND if a x16 device is used.

#### 2.3.1 Miscellaneous

- It is highly recommended that the PWRGOOD signal from the power supply **not** be connected directly to logic on the board without first going through a Schmitt trigger type circuit to square-off and maintain the signal integrity of PWROK.

- If the PWRGOOD signal from the power supply is at 5V level, then it must be divided down to 3V before connecting to the PIIX4. Please ensure that the voltage level on PWROK does not exceed

# intel

#### FLEXIBLE MOTHERBOARD DESIGN LAYOUT REVIEW CHECKLIST

the  $V_{CC}(RTC)$  level. The reference schematics meet this requirement by using a divide by two voltage divider on the 5V signal.

- Based on the resistor values and input capacitance of the PIIX4 PWROK pin, the rise time in the reference board schematics is approximately 170 ns (within the max. 250 ns requirement for the PIIX4). It is important that if any other components are connected to PWROK, the resistor divider values may need to be adjusted to meet a faster rise time required by the other parts and increased loading. 3V driving devices, such as an 74LVC14 could also be used as a replacement for the voltage divider.

- The 32-kHz oscillator is always required by the PIIX4, even if the internal RTC is not used. Also, if the internal RTC is not used then the on board battery is not required. In this case, connect  $V_{CC}(RTC)$  of the PIIX4 directly to 3 VSB.

- A20GATE and KBRESET output signals from the SMC ULTRA I/O device need a pull-up to 5V through a 10kohm resistor.

- All unused GPIx inputs on the PIIX4 should be tied high through pull-up resistors (8.2 kohm—10 kohm) to a power plane. Tying them directly to the power plane is also acceptable. In the 430TX reference board, GPI13–GPI21 are tied to the 3.3V core power plane through 8.2k resistors. GPI1 is tied to 3 VSB through an 8.2 kohm resistor. If GPI1 is left floating, this will violate ACPI compliance by preventing the GPI\_STS bit (register base + 0Ch, bit 9) from functioning properly. Please note that GPI1 is tied to the resume well.

- To maintain RTC accuracy, the external capacitor values for the RTC crystal circuit should be chosen to provide the manufacturer's specified load capacitance for the crystal when combined with the parasitic capacitance of the trace, socket (if used), and package, which can vary from 0 pF to 8 pF. When choosing the capacitors, the following equation can be used:

- Specified Crystal Load = (Cap1 \* Cap2)/(Cap1 + Cap2) + parasitic capacitance

- The reference board uses 22 pF capacitors and a crystal with a specified load of 12.5 pF. This provides an accuracy of approximately 20 ppm (10.5 minutes per year), however, using the above guidelines, the capacitors should be between 16 pF and 18 pF. This increases the accuracy from 20 ppm using the 22 pF capacitors, to between 0–7ppm (3.5 minutes per year, worst case) using 16 pF to 18 pF capacitors. Note that while 20 ppm is still within spec, using these guidelines can improve the RTC accuracy.

# **Board Layout and Routing Guidelines**

# CHAPTER 3 BOARD LAYOUT AND ROUTING GUIDELINES

# 3. 430TX Board Layout and Routing Guidelines

This section describes the 430TX layout and routing recommendations to insure a robust design. These guidelines should be followed as closely as possible. Any deviations from the guidelines listed here should be simulated to insure adequate margin is still maintained in the design.

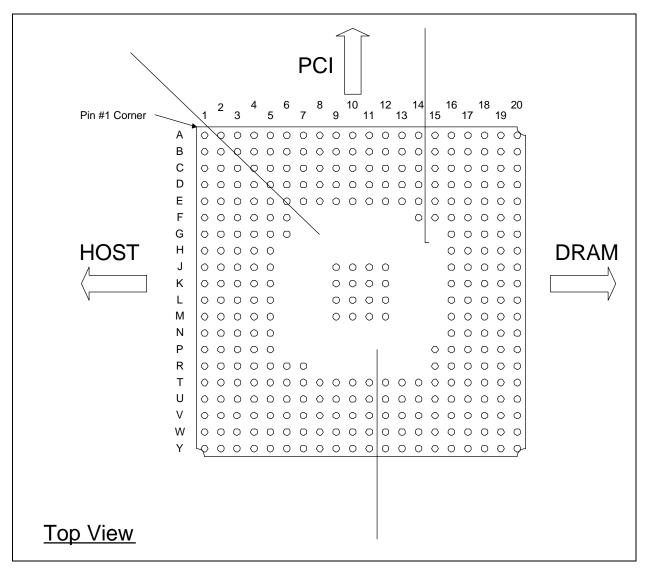

# 3.1 Placement

The pins on the MTXC have been assigned in order to simplify routing. The major signal sections of the MTXC (i.e. Host, DRAM and PCI) are shown in Figure 3-1. The component placement on the motherboard should be done with this general flow in mind. This will simplify routing and minimize the number of signals which must cross. The individual signals within the respective groups have also been laid out in order to minimize any signal crossing.

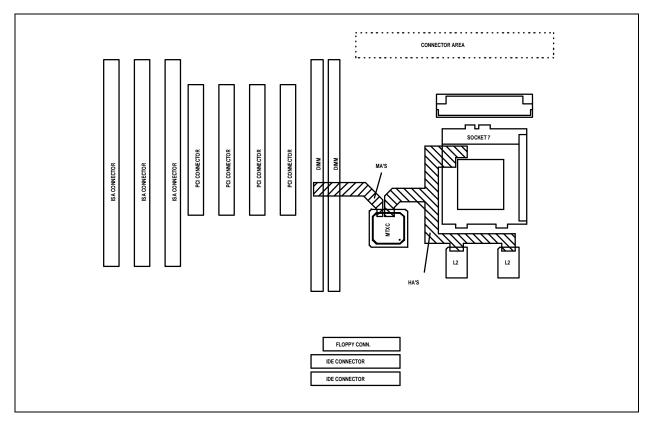

Figure 3-1. 430TX Pinout

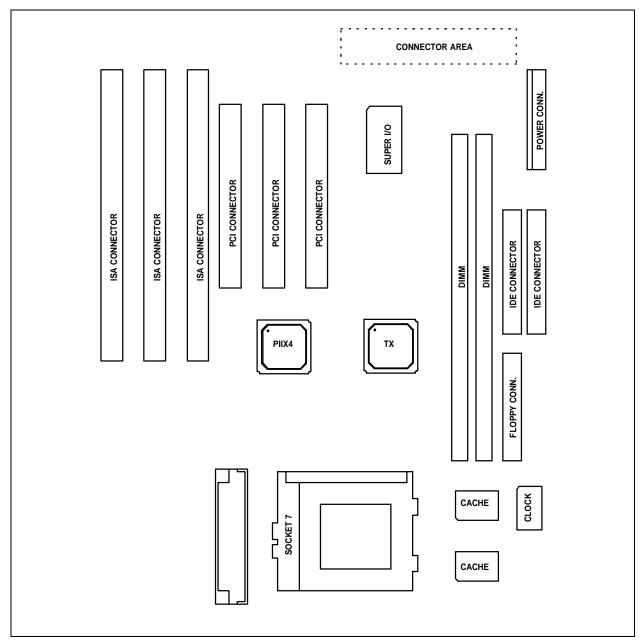

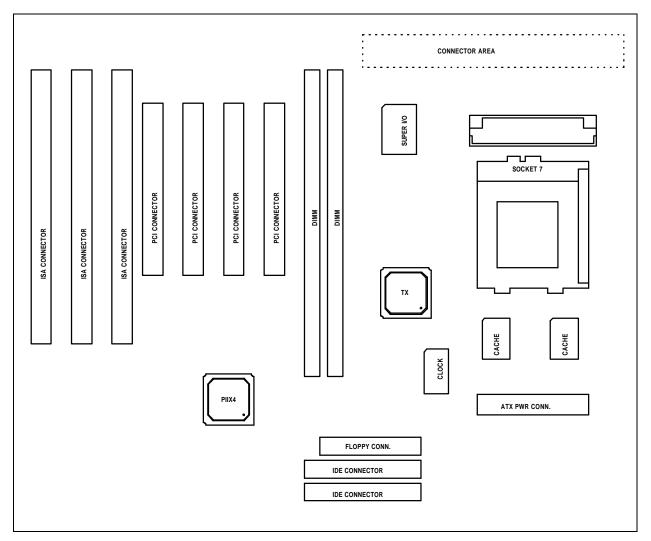

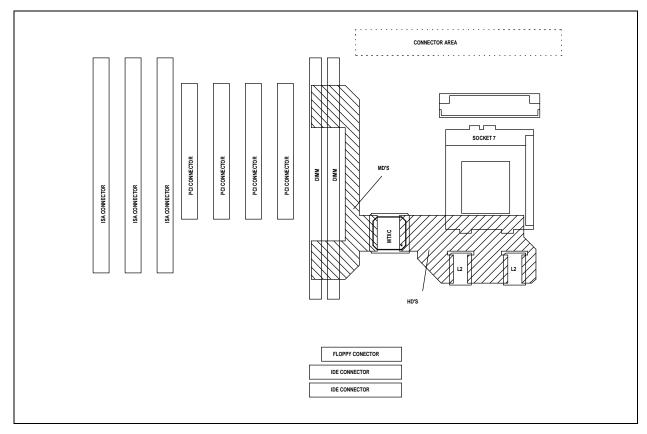

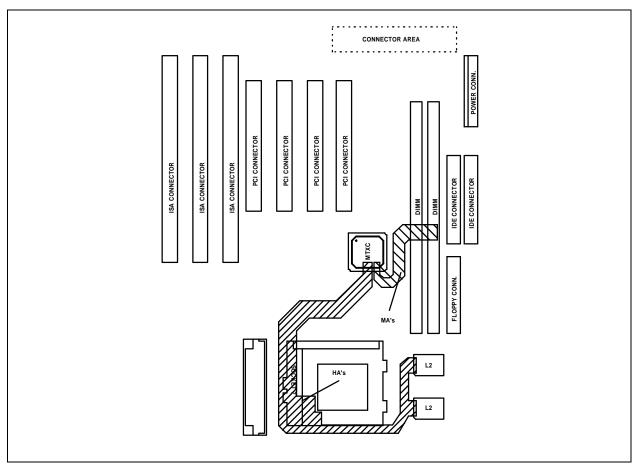

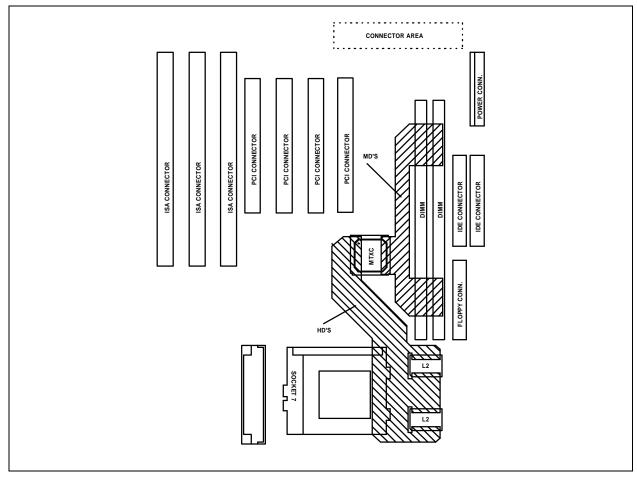

Examples of the recommended component placement for Pentium processor 430TX designs are shown below for a 2/3 baby AT form factor and an ATX form factor. An ATX layout will allow more open full length ISA and PCI slots for better CPU cooling, more I/O connectors on the motherboard for I/O peripherals (serial, parallel ports, video....), and a better USB connector implementation that will allow the USB connectors to be soldered directly to the motherboard. The following two examples show a 2/3 baby AT with two DIMMs that support EDO, FPM, or SDRAM memory and an ATX with the same memory configuration.

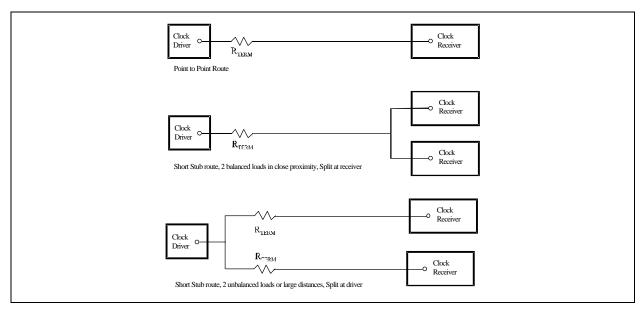

Figure 3-2. Example Placement for 2/3 baby AT and EDO/FPM/SDRAM DRAM 430TX Design

Figure 3-3. Example Placement for an ATX form factor EDO/FPM DRAM, SDRAM 430TX Design

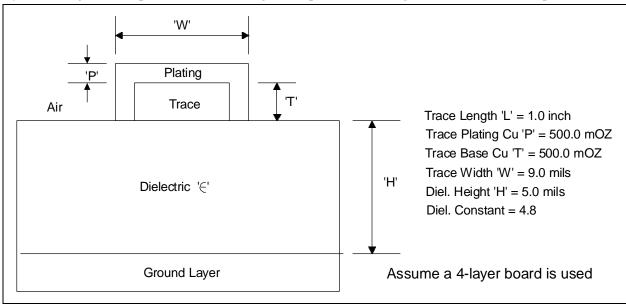

# 3.2 Board Description

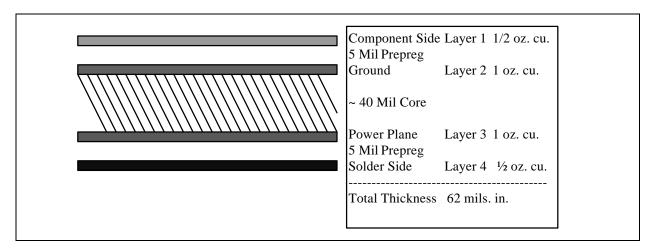

A 430TX motherboard can be designed using a four layer stack-up arrangement. The stack up of the board is shown in Figure 3-4. The impedance of all the signal layers are to be 60 and 90 ohms. The overall board thickness is to be .062 inch.

Figure 3-4. Four Layer Board Stack-up

Note that the top and bottom routing layers specify 1/2 oz. cu. However, by the time the board is plated, the traces will end up being about 1 to 1.5 oz. cu. Please check with your fab vendor on the exact value and insure that any signal simulation accounts for this.

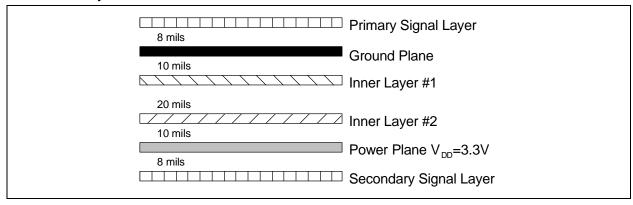

As mentioned above, the layout of this board will first be attempted using a four layer stack-up. If for some reason it becomes apparent that more signal layers will be needed to complete the routing of the board, the following six layers stack-up should be used.

If a six layer stack-up is used, routes on the two inner layers should be orthogonal to reduce crosstalk between the layers.

Figure 3-5. Six Layer Board Stack-up

Additional guidelines on board buildup, placement and layout include:

- The board impedance (Z) must be between 60 and 90 ohms (75 ohms  $\pm$  20%)

- FR-4 material should be used for the board fabrication.

- The ground plane should not be split on the ground plane layer. If a signal must be routed for a short distance on a power plane, then it should be routed on the  $V_C$  plane, not the ground plane.

- Group 5V and 3V components near each other. This will allow for fewer isolated V<sub>CC</sub> islands on the power plane.

- Place vias for decoupling capacitors inside the footprint for the capacitor if possible.

- Use the first (nearest) available via site for decoupling caps if inside footprint is not possible.

# 3.3 Layout and Routing Guidelines

This section lists guidelines to be followed when routing the signal traces for the board design. The order of which signals are routed first and last will vary from designer to designer. Some designers prefer routing all of the clock signals first, while others prefer routing all of the high speed bus signals first. Either order can be used, as long as the guidelines listed here are followed.

# 3.3.1 BGA Component Layout Guidelines

## 3.3.1.1 BGA Pad Size

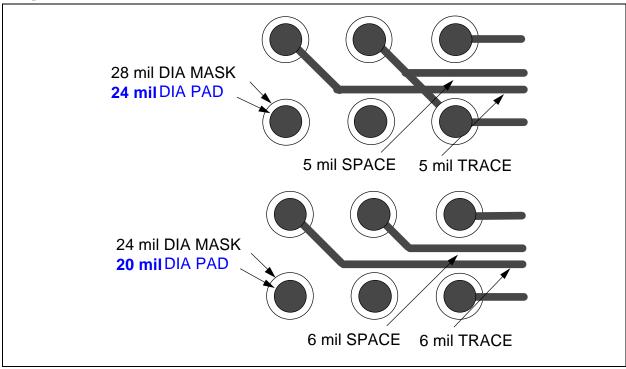

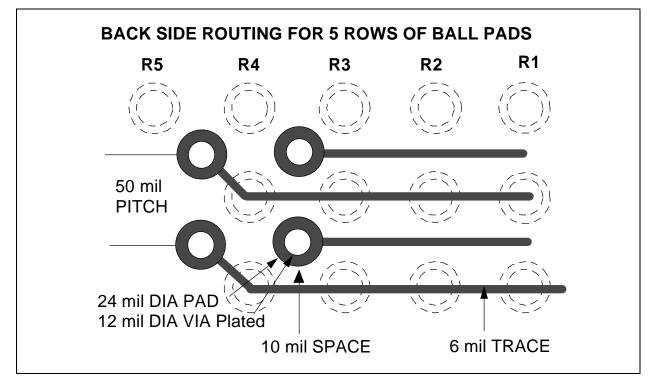

Since the BGA component contains 5 rows of balls, it is necessary to route two traces between pads in order to route in a four layer board. The figure below shows a routing example for 24 mil and 20 mil ball pads. In order to route two tracks between pads, 5 mil traces and 5 mil spaces are required for a 24 mil pad size. For a 20 mil pad size, 6 mil traces and 6 mil spacing can be used. Either pad size is acceptable, so the choice is primarily determined by the manufacturer's preferred line width and spacing technology. If larger trace widths are desired, another alternative is to route 5/5 or 6/6 within the BGA pads, and then "neck up" to the larger trace widths once you have cleared the BGA component area.

Figure 3-6. BGA Routing

Figure 3-7. BGA Routing Example

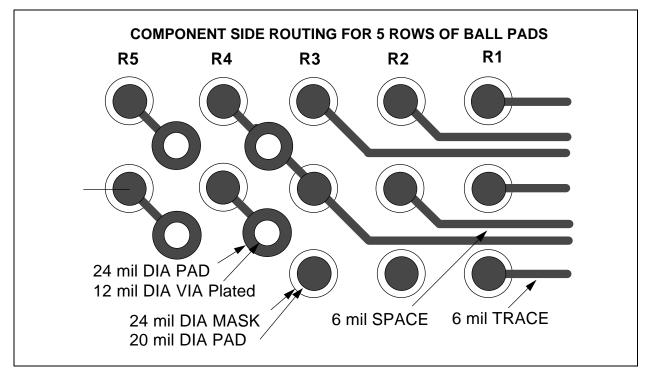

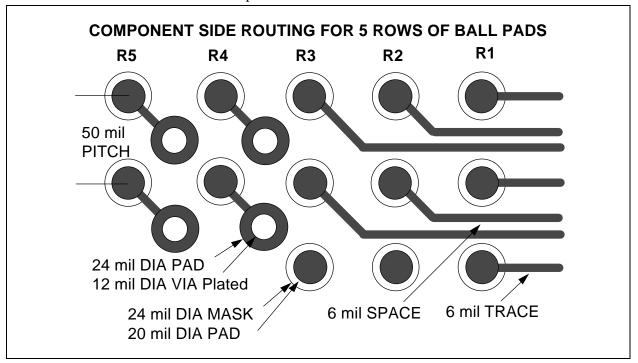

Using the routing scheme shown above, the first three rows of balls can be routed on the top signal layer. The inner two rows must be routed on the bottom side of the board. As a result, vias are required in between the BGA pads. The vias will be discussed in the next section.

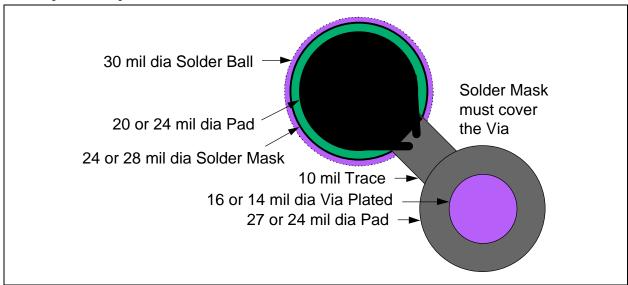

## 3.3.1.2 BGA Vias

The figure below shows the connection between the BGA ball pad and a via. All vias located between the BGA ball pads must be covered with solder mask his will prevent solder from wicking over to the via pad. A via pad size of 24 mils is recommended.

Figure 3-8. BGA Pads and Vias

# 3.4 BGA Routing

The figures below show a routing example for both the component and solder sides of a four layer board. The first three rows are routed on the component side, while the inner two rows are routed on the solder side of the board. This example shows 6 mil trace widths.

Figure 3-9. BGA Component Side Routing Example

Figure 3-10. BGA Solder Side Routing Example

# 3.4.1 General Guidelines

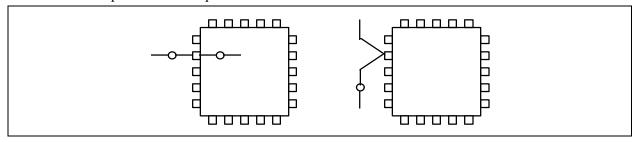

It is recommended that the address, data and control signals are routed using a "daisy chain" topology. The use of this topology implies that no stubs are to be used to connect any devices on the net. Figure 3-11 shows two possible techniques to achieve a stubless trace.

Figure 3-11. Stubless Routing Examples

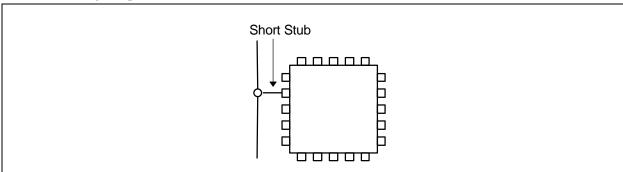

In instances where it's not possible to apply one of these two techniques due to congestion, a very short stub is allowed. The length of this stub should be kept short. Figure 3-12 shows a trace with a short stub connecting the pin.

Figure 3-12. Short Stub Routing Example

# 3.4.2 Memory/Cache Layout Guidelines

The 430TX PCIset supports a wide range of design options. The following are key options that must be determined before layout and routing.

- How many rows of memory will the design support.

- Which type of DRAM module will be used (DRAM, SDRAM, or both).

- How much cache memory will be supported (256K vs. 512K).

The possible DRAM and system options supported by the 430TX PCIset are shown in the following table.

Table 3-1. Memory/Cache Types Supported by 430TX

| DRAM Type                | FPM, EDO, SDRAM                             |

|--------------------------|---------------------------------------------|

| DRAM/SDRAM Module Type   | 72-pin SIMM: 32 bit, 168-pin DIMM: 64 bit   |

| DRAM/SDRAM Voltage       | 3.3V, 5.0V                                  |

| Number of rows of memory | 1 to 6                                      |

| DRAM Speed               | 50, 60, 70 ns                               |

| DRAM Component Width     | x4, x8, x16                                 |

| SDRAM Speed              | 66/60 MHz, RAS-to-CAS latency=2 or 3 clocks |

| SDRAM Component Width    | x8, x16                                     |

| CPU Bus Frequency        | 60, 66 MHz                                  |

The text below will use the term 'row' or 'row of memory' to describe 64 bits of memory connected to the same RAS# signal. There are a few different ways to create a row of memory that include the following: