# W83782D Winbond H/W Monitoring IC

|    | Pages | Dates | Version | Version<br>on Web | Main Contents                                                         |

|----|-------|-------|---------|-------------------|-----------------------------------------------------------------------|

| 1  | n.a.  |       |         | n.a.              | All the version before 0.50 are for internal use.                     |

| 2  | n.a.  | 98/7  | 0.5     | n.a.              | First publication.                                                    |

| 3  | P.40  | 99/4  | 0.55    | A1                | Add the content of Diode Selection Register Index 59h(Bank0)          |

| 4  | P.42  | 99/4  | 0.55    | A1                | Add the content of VBAT Monitor Control Register<br>Index 5Dh (Bank0) |

| 5  |       |       |         |                   |                                                                       |

| 6  |       |       |         |                   |                                                                       |

| 7  |       |       |         |                   |                                                                       |

| 8  |       |       |         |                   |                                                                       |

| 9  |       |       |         |                   |                                                                       |

| 10 |       |       |         |                   |                                                                       |

# W83782D Data Sheet Revision History

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

# LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

# TABLE OF CONTENTS

| 1. GENERAL DESCRIPTION1                                                                  |

|------------------------------------------------------------------------------------------|

| 2. FEATURES                                                                              |

| 2.1 MONITORING ITEMS                                                                     |

| 2.2 ACTIONS ENABLING                                                                     |

| 2.3 GENERAL                                                                              |

| 2.4 PACKAGE                                                                              |

| 3. KEY SPECIFICATIONS                                                                    |

| 4. PIN CONFIGURATION                                                                     |

| 5. PIN DESCRIPTION                                                                       |

| 6. FUNCTIONAL DESCRIPTION7                                                               |

| 6.1 GENERAL DESCRIPTION7                                                                 |

| 6.2 ACCESS INTERFACE7                                                                    |

| 6.2.1 ISA interface7                                                                     |

| 6.2.2 I2C interface                                                                      |

| 6.2.3 The first serial bus access timing are shown as follow:                            |

| 6.2.4 The serial bus timing of the temperature 2 and 3 is shown as follow:               |

| 6.3 ANALOG INPUTS                                                                        |

| 6.3.1 Monitor over 4.096V voltage:                                                       |

| 6.3.2 Monitor negative voltage:                                                          |

| 6.3.3 Monitor temperature from thermistor:                                               |

| 6.3.4 Monitor temperature from Pentium IITM thermal diode or bipolar transistor 2N390416 |

| 6.4 FAN SPEED COUNT AND FAN SPEED CONTROL17                                              |

| 6.4.1 Fan speed count                                                                    |

| 6.4.2 Fan speed control19                                                                |

# Preliminary W83782D

| 6.5 TEMPERATURE MEASUREMENT MACHINE                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.5.1 The W83782D temperature sensor 1 SMI# interrupt has two modes:                                                                                                                              |

| <ul><li>6.5.2 The W83782D temperature sensor 2 and sensor 3 SMI# interrupt has two modes and it is programmed at CR[4Ch] bit 6</li></ul>                                                          |

| 6.5.3 The W83782D temperature sensor 2 and 3 Over-Temperature (OVT) has two modes, and they are programmed at Bank1 and Bank2 CR[52h] bit1. These two bits needs to be programmed the same value. |

| 7. REGISTERS AND RAM24                                                                                                                                                                            |

| 7.1 ADDRESS REGISTER (PORT X5H)                                                                                                                                                                   |

| 7.2 DATA REGISTER (PORT X6H)                                                                                                                                                                      |

| 7.3 CONFIGURATION REGISTER <sup>3</sup> / <sub>4</sub> INDEX 40H                                                                                                                                  |

| 7.4 INTERRUPT STATUS REGISTER 1 <sup>3</sup> / <sub>4</sub> INDEX 41H                                                                                                                             |

| 7.5 INTERRUPT STATUS REGISTER 2 <sup>3</sup> / <sub>4</sub> INDEX 42H                                                                                                                             |

| 7.6 SMI# MASK REGISTER 1 <sup>3</sup> / <sub>4</sub> INDEX 43H                                                                                                                                    |

| 7.7 SMI# MASK REGISTER 2 <sup>3</sup> / <sub>4</sub> INDEX 44H                                                                                                                                    |

| 7.8 RESERVED REGISTER <sup>3</sup> / <sub>4</sub> INDEX 45H                                                                                                                                       |

| 7.9 CHASSIS CLEAR REGISTER INDEX 46H                                                                                                                                                              |

| 7.10 VID/FAN DIVISOR REGISTER ¾ INDEX 47H                                                                                                                                                         |

| 7.11 SERIAL BUS ADDRESS REGISTER ¾ INDEX 48H                                                                                                                                                      |

| 7.12 VALUE RAM <sup>3</sup> / <sub>4</sub> INDEX 20H- 3FH OR 60H - 7FH (AUTO-INCREMENT)                                                                                                           |

| 7.13 VOLTAGE ID (VID4) & DEVICE ID - 49H                                                                                                                                                          |

| 7.14 TEMPERATURE 2 AND TEMPERATURE 3 SERIAL BUS ADDRESS REGISTERINDEX 4AH.33                                                                                                                      |

| 7.15 PIN CONTROL REGISTER - INDEX 4BH                                                                                                                                                             |

| 7.16 IRQ#/OVT# PROPERTY SELECT - INDEX 4CH                                                                                                                                                        |

| 7.17 FAN IN/OUT AND BEEP/GPO# CONTROL REGISTER - INDEX 4DH                                                                                                                                        |

| 7.18 REGISTER 50H ~ 5FH BANK SELECT - INDEX 4EH (NO AUTO INCREASE)                                                                                                                                |

| 7.19 WINBOND VENDOR ID - INDEX 4FH (NO AUTO INCREASE)                                  |

|----------------------------------------------------------------------------------------|

| 7.20 WINBOND TEST REGISTER INDEX 50H - 55H (BANK 0)                                    |

| 7.21 BEEP CONTROL REGISTER 1 INDEX 56H (BANK 0)                                        |

| 7.21 BEEP CONTROL REGISTER 1 INDEX 50H (BANK 0)                                        |

|                                                                                        |

| 7.23 CHIP ID INDEX 58H (BANK 0)                                                        |

| 7.24 DIODE SELECTION REGISTER INDEX 59H (BANK 0)                                       |

| 7.25 PWMOUT2 CONTROL INDEX 5AH (BANK 0)                                                |

| 7.26 PWMOUT1 CONTROL INDEX 5BH (BANK 0)                                                |

| 7.27 PWMOUT1/2 CLOCK SELECT INDEX 5CH (BANK 0)                                         |

| 7.28 VBAT MONITOR CONTROL REGISTER INDEX 5DH (BANK 0)                                  |

| 7.29 PWMOUT3 CONTROL INDEX 5EH (BANK 0)                                                |

| 7.30 PWMOUT4 CONTROL INDEX 5FH (BANK 0)                                                |

| 7.31 TEMPERATURE SENSOR 2 TEMPERATURE (HIGH BYTE) REGISTER - INDEX 50H (BANK1)44       |

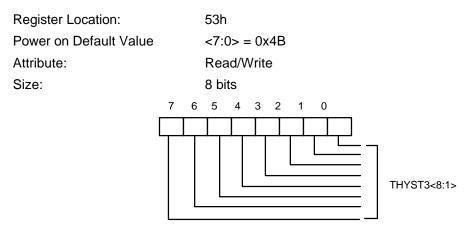

| 7.32 TEMPERATURE SENSOR 2 TEMPERATURE (LOW BYTE) REGISTER - INDEX 51H (BANK1)44        |

| 7.33 TEMPERATURE SENSOR 2 CONFIGURATION REGISTER - INDEX 52H (BANK1)45                 |

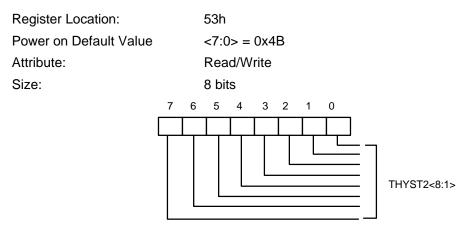

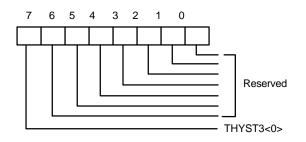

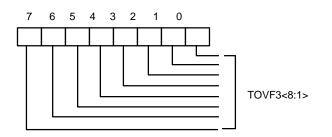

| 7.34 TEMPERATURE SENSOR 2 HYSTERESIS (HIGH BYTE) REGISTER - INDEX 53H (BANK 1)46       |

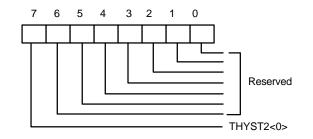

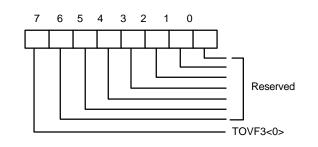

| 7.35 TEMPERATURE SENSOR 2 HYSTERESIS (LOW BYTE) REGISTER - INDEX 54H (BANK 1)46        |

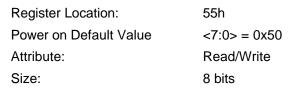

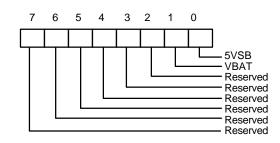

| 7.36 TEMPERATURE SENSOR 2 OVER-TEMPERATURE (HIGH BYTE) REGISTER - INDEX 55H            |

| (BANK 1)                                                                               |

| 7.37 TEMPERATURE SENSOR 2 OVER-TEMPERATURE (LOW BYTE) REGISTER - INDEX 56H             |

| (BANK 1)                                                                               |

| 7.38 TEMPERATURE SENSOR 3 TEMPERATURE (HIGH BYTE) REGISTER - INDEX 50H (BANK2)48       |

| 7.39 TEMPERATURE SENSOR 3 TEMPERATURE (LOW BYTE) REGISTER - INDEX 51H (BANK2)48        |

| 7.40 TEMPERATURE SENSOR 3 CONFIGURATION REGISTER - INDEX 52H (BANK 2)48                |

| 7.41 TEMPERATURE SENSOR 3 HYSTERESIS (HIGH BYTE) REGISTER - INDEX 53H (BANK 2)49       |

| 7.42 TEMPERATURE SENSOR 3 HYSTERESIS (LOW BYTE) REGISTER - INDEX 54H (BANK 2)49        |

| 7.43 TEMPERATURE SENSOR 3 OVER-TEMPERATURE (HIGH BYTE) REGISTER - INDEX 55H            |

| (BANK 2)                                                                               |

| 7.44 TEMPERATURE SENSOR 3 OVER-TEMPERATURE (LOW BYTE) REGISTER - INDEX 56H<br>(BANK 2) |

| 7.45 INTERRUPT STATUS REGISTER 3 <sup>3</sup> / <sub>4</sub> INDEX 50H (BANK4)         |

| 7.46 SMI# MASK REGISTER 3 ¾ INDEX 51H (BANK 4)51                                       |

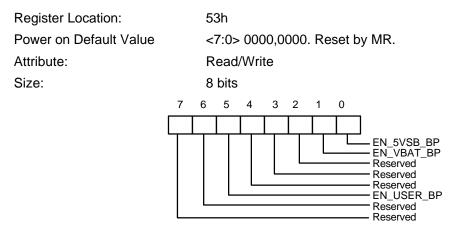

| 7.47 BEEP CONTROL REGISTER 3 INDEX 53H (BANK 4)                                        |

| 7.48 RESERVED REGISTER - INDEX 54H58H (BANK 4)                                         |

|                                                                                        |

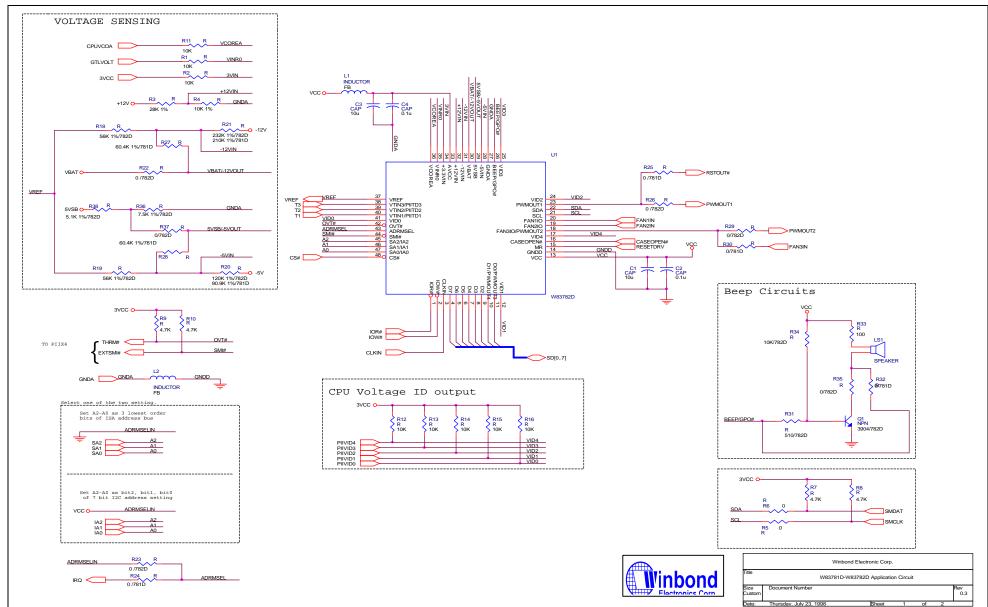

| 11. APPLICATION CIRCUIT OF WINBOND W83782D / 781D                                            | 63 |

|----------------------------------------------------------------------------------------------|----|

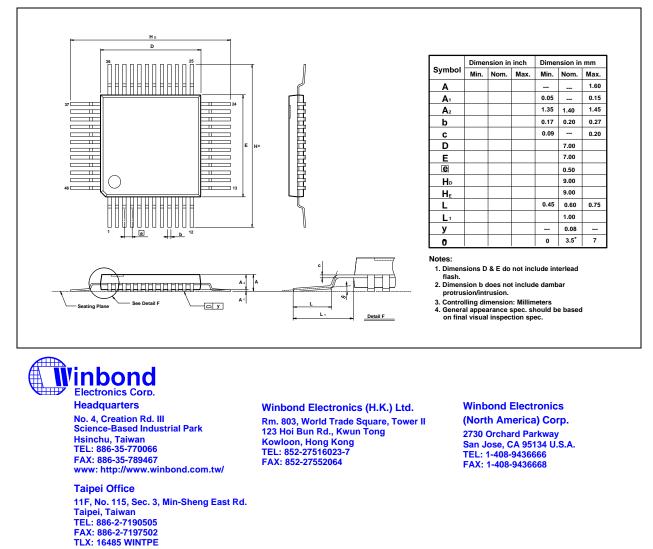

| 10. PACKAGE DIMENTIONS                                                                       | 62 |

| 9. HOW TO READ THE TOP MARKING                                                               | 61 |

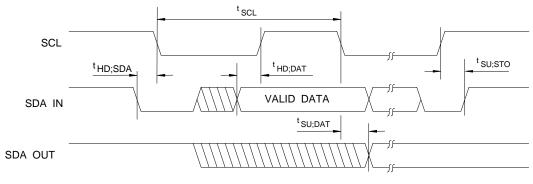

| 8.3.2 Serial Bus Timing Diagram                                                              | 60 |

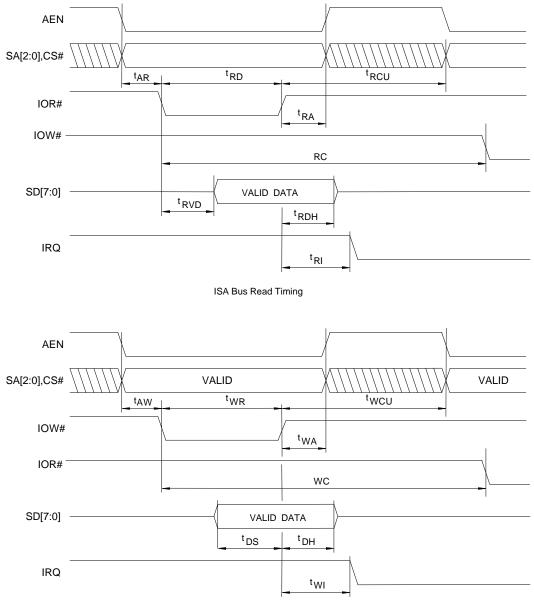

| 8.3.1 ISA Read/Write Interface Timing                                                        |    |

| 8.3 AC Characteristics                                                                       | 59 |

| 8.2 DC CHARACTERISTICS                                                                       |    |

| 8.1 ABSOLUTE MAXIMUM RATINGS                                                                 | 57 |

| 8. SPECIFICATIONS                                                                            | 57 |

| 7.54 WINBOND TEST REGISTER - INDEX 50H (BANK 6)                                              | 56 |

| 7.53 VALUE RAM 2 <sup>3</sup> / <sub>4</sub> INDEX 50H - INDEX 5AH (AUTO-INCREMENT) (BANK 5) | 56 |

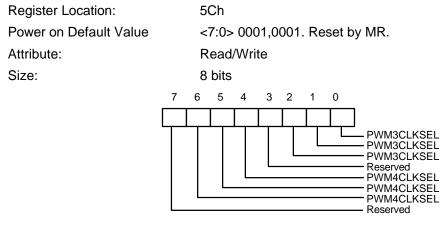

| 7.52 PWMOUT3/4 CLOCK SELECT INDEX 5CH (BANK 4)                                               | 55 |

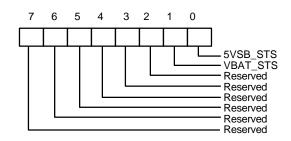

| 7.51 REAL TIME HARDWARE STATUS REGISTER III INDEX 5BH (BANK 4)                               | 54 |

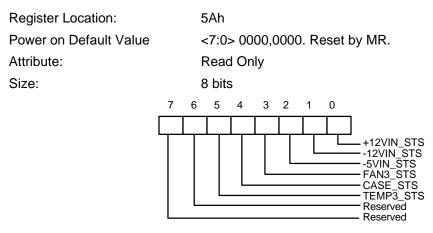

| 7.50 REAL TIME HARDWARE STATUS REGISTER II INDEX 5AH (BANK 4)                                | 54 |

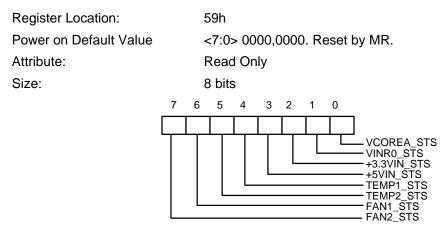

| 7.49 REAL TIME HARDWARE STATUS REGISTER I INDEX 59H (BANK 4)                                 | 53 |

# WINBOND H/W MONITORING IC

# 1. GENERAL DESCRIPTION

W83782D is an evolving version of W83782D --- Winbond's most popular hardware status monitoring IC. The W83782D can be used to monitor several critical hardware parameters of the system, including power supply voltages, fan speeds, and temperatures, which are very important for a high-end computer system to work stable and properly. W83782D provides both ISA and  $I^2C^{TM}$  serial bus interface.

An 8-bit analog-to-digital converter (ADC) was built inside W83782D. The W83782D can simultaneously monitor 9 analog voltage inputs, 2 fan tachometer inputs, 3 remote temperature, one case-open detection signal. The remote temperature sensing can be performed by thermistors, or 2N3904 NPN-type transistors, or directly from Intel<sup>™</sup> Deschutes CPU thermal diode output. Also the W83782D provides: 4 PWM (pulse width modulation) outputs for the fan speed control; beep tone output for warning; SMI#, OVT#, GPO# signals for system protection events.

Through the application software or BIOS, the users can read all the monitored parameters of system from time to time. And a pop-up warning can be also activated when the monitored item was out of the proper/preset range. The application software could be Winbond's Hardware Doctor<sup>™</sup>, or Intel<sup>™</sup> LDCM (LanDesk Client Management), or other management application software. Also the users can set up the upper and lower limits (alarm thresholds) of these monitored parameters and to activate one programmable and maskable interrupts. An optional beep tone could be used as warning signal when the monitored parameters is out of the preset range.

Additionally, 5 VID inputs are provided to read the VID of CPU (i.e. Pentium<sup>™</sup> II) if applicable. This is to provide the Vcore voltage correction automatically. Also W83782D uniquely provides an optional feature: early stage (before BIOS was loaded) beep warning. This is to detect if the fatal elements present --- Vcore or +3.3V voltage fail, and the system can not be boomed up. Also there are 3 specific pins to provide selectable address setting for application of multiple devices (up to 8 devices) wired through I<sup>2</sup>C<sup>™</sup> interface.

# Preliminary W83782D

# 2. FEATURES

### 2.1 Monitoring Items

- 3 thermal inputs from remote thermistors or 2N3904 NPN-type transistors or Pentium<sup>™</sup> II (Deschutes) thermal diode output

- 9 voltage inputs

- --- typical for Vcore, +3.3V, +12V, -12V, +5V, -5V, +5V Vsb, Vbat, and one reserved

- 3 fan speed monitoring inputs

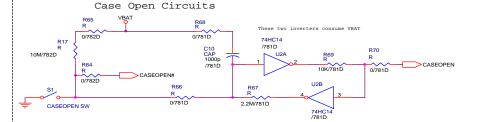

- Case open detection input

- WATCHDOG comparison of all monitored values

- Programmable hysteresis and setting points (alarm thresholds) for all monitored items

# 2.2 Actions Enabling

- Beep tone warning

- 4 PWM (pulse width modulation) outputs for fan speed control (3 are MUX optional)

--- Total up to 3 sets of fan speed monitoring and controlling

- Issue SMI#, OVT#, GPO# signals to activate system protection

- Warning signal pop-up in application software

### 2.3 General

- ISA and  $I^2C^{TM}$  serial bus interface

- 5 VID input pins for CUP Vcore identification (for Pentium<sup>™</sup> II)

- Initial power fault beep (for +3.3V, Vcore)

- Master reset input to W83782D

- Independent power plane of digital Vcc and analog Vcc (inputs to IC)

- 3 pins (IA0, IA1, IA2) to provide selectable address setting for application of multiple devices (up to 8 devices) wired through I<sup>2</sup>C<sup>™</sup> interface

- Intel<sup>™</sup> LDCM (DMI driver 2.0) support

- Acer<sup>™</sup> ADM (DMI driver 2.0) support

- Winbond hardware monitoring application software (Hardware Doctor<sup>™</sup>) support, for both Windows 95/98 and Windows NT 4.0/5.0

- Input clock rate optional for 24, 48, 14.318 Mhz

- 5V Vcc operation

### 2.4 Package

• 48-pin LQFP

# 3. KEY SPECIFICATIONS

| Voltage monitoring accuracy               | ±1% (Max)             |  |  |  |

|-------------------------------------------|-----------------------|--|--|--|

| Monitoring Temperature Range and Accuracy |                       |  |  |  |

| - 40°C to +120°C                          | $\pm 3^{\circ}C(Max)$ |  |  |  |

| Supply Voltage                            | 5V                    |  |  |  |

| Operating Supply Current                  | 5 mA typ.             |  |  |  |

| ADC Resolution                            | 8 Bits                |  |  |  |

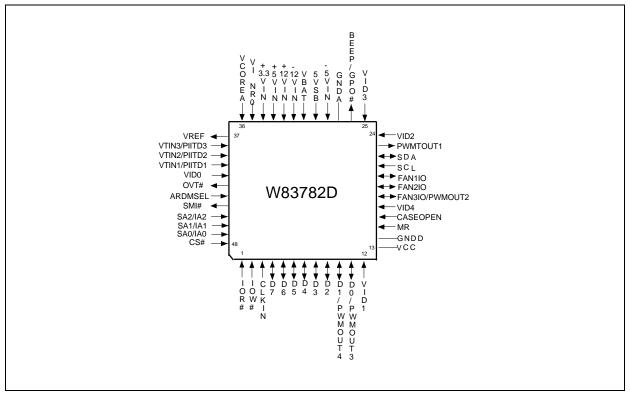

# 4. PIN CONFIGURATION

# 5. PIN DESCRIPTION

- I/O<sub>12t</sub> TTL level bi-directional pin with 12 mA source-sink capability

- I/O<sub>12ts</sub> TTL level and schmitt trigger

- $OUT_{12}$  Output pin with 12 mA source-sink capability

- AOUT Output pin(Analog)

- OD<sub>12</sub> Open-drain output pin with 12 mA sink capability

- INt TTL level input pin

- INts TTL level input pin and schmitt trigger

- AIN Input pin(Analog)

| PIN NAME              | PIN NO. | TYPE               | DESCRIPTION                                                                                                                                                                     |

|-----------------------|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOR#                  | 1       | INts               | An active low standard ISA bus I/O Read Control.                                                                                                                                |

| IOW#                  | 2       | INts               | An active low standard ISA bus I/O Write Control.                                                                                                                               |

| CLKIN                 | 3       | IN <sub>t</sub>    | System clock input. Can select 48MHz or 24MHz or 14.318MHz. The default is 24MHz.                                                                                               |

| D7~D2                 | 4-9     | I/O <sub>12t</sub> | Bi-directional ISA bus Data lines. D0 corresponds to the low order bit, with D7 the high order bit. These pins are activated if pin ADRMSEL=0.                                  |

| D1 /                  | 10      | I/O <sub>12t</sub> | Bi-directional ISA bus Data lines. This pin is activated if pin ADRMSEL=0. /                                                                                                    |

| PWMOUT4               |         | OUT <sub>12</sub>  | Fan speed control PWM output. This pin is activated if pin ADRMSEL=1.                                                                                                           |

| D0 /                  | 11      | I/O <sub>12t</sub> | Bi-directional ISA bus Data lines. This pin is activated if pin ADRMSEL=0. /                                                                                                    |

| PWMOUT3               |         | OUT <sub>12</sub>  | Fan speed control PWM output. This pin is activated if pin ADRMSEL=1.                                                                                                           |

| VID1                  | 12      | INt                | Voltage Supply readouts from P6. This value is read in the VID/Fan Divisor Register.                                                                                            |

| V <sub>CC</sub> (+5V) | 13      | POWER              | +5V V <sub>CC</sub> power. Bypass with the parallel combination of $10\mu F$ (electrolytic or tantalum) and $0.1\mu F$ (ceramic) bypass capacitors.                             |

| GNDD                  | 14      | DGROUND            | Internally connected to all digital circuitry.                                                                                                                                  |

| MR                    | 15      | INts               | Master reset input.                                                                                                                                                             |

| CASEOPEN#             | 16      | IN <sub>t</sub>    | CASE OPEN detection . An active low input from an external device when case is opened. This signal can be latched if pin VBAT is connect to battery, even W83782D is power off. |

| VID4                  | 17      | IN <sub>t</sub>    | Voltage Supply readouts from P6. This value is read in the bit <0> of Device ID Register.                                                                                       |

| Pin Discription, con |         |                    |                                                                                             |  |

|----------------------|---------|--------------------|---------------------------------------------------------------------------------------------|--|

| PIN NAME             | PIN NO. | TYPE               | DESCRIPTION                                                                                 |  |

| FAN3IO/              | 18      | I/O <sub>12t</sub> | 0V to +5V amplitude fan tachometer input. /                                                 |  |

| PWMOUT2              |         |                    | Fan speed control PWM output.                                                               |  |

| FAN2IO-              | 19-20   | I/O <sub>12t</sub> | 0V to +5V amplitude fan tachometer input /                                                  |  |

| FAN1IO               |         |                    | Fan on-off control output. These multi-functional pins can be programmable input or output. |  |

| SCL                  | 21      | IN <sub>ts</sub>   | Serial Bus Clock.                                                                           |  |

| SDA                  | 22      | OD <sub>12</sub>   | Serial Bus bi-directional Data.                                                             |  |

| PWMOUT1              | 23      | OUT <sub>12</sub>  | Fan speed control PWM output.                                                               |  |

| VID2                 | 24      | IN <sub>t</sub>    | Voltage Supply readouts from P6. This value is read in the VID/Fan Divisor Register.        |  |

| VID3                 | 25      | IN <sub>t</sub>    | Voltage Supply readouts from P6. This value is read in the VID/Fan Divisor Register.        |  |

| BEEP/GPO#            | 26      | OD <sub>12</sub>   | Beep (Default) / General purpose output                                                     |  |

|                      |         |                    | This multi-functional pin is programmable.                                                  |  |

| GNDA                 | 27      | AGROUND            | Internally connected to all analog circuitry. The ground reference for all analog inputs.   |  |

| -5VIN                | 28      | AIN                | 0V to 4.096V FSR Analog Inputs.                                                             |  |

| 5VSB                 | 29      | AIN                | 0V to 4.096V FSR Analog Inputs.                                                             |  |

| VBAT                 | 30      | AIN                | 0V to 4.096V FSR Analog Inputs. (This pin should be connected to 3V BATTERY.)               |  |

| -12VIN               | 31      | AIN                | 0V to 4.096V FSR Analog Inputs.                                                             |  |

| +12VIN               | 32      | AIN                | 0V to 4.096V FSR Analog Inputs.                                                             |  |

| +5VIN                | 33      | AIN                | This pin is Analog Vcc and connects internal monitor channel IN3 with fixed scale.          |  |

| +3.3VIN              | 34      | AIN                | 0V to 4.096V FSR Analog Inputs.                                                             |  |

| VINR0                | 35      | AIN                | 0V to 4.096V FSR Analog Inputs.                                                             |  |

| VCOREA               | 36      | AIN                | 0V to 4.096V FSR Analog Inputs.                                                             |  |

| VREF                 | 37      | AOUT               | Reference Voltage.                                                                          |  |

| VTIN3 /              | 38      | AIN                | Thermistor 3 terminal input.(Default) /                                                     |  |

| PIITD3               |         |                    | Pentium <sup>™</sup> II diode 3 input.                                                      |  |

|                      |         |                    | This multi-functional pin is programmable.                                                  |  |

| Pin Discription, con | Pin Discription, continued |                  |                                                                                                                                                             |  |  |

|----------------------|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN NAME             | PIN NO.                    | TYPE             | DESCRIPTION                                                                                                                                                 |  |  |

| VTIN2 /              | 39                         | AIN              | Thermistor 2 terminal input. (Default)/                                                                                                                     |  |  |

| PIITD2               |                            |                  | Pentium <sup>™</sup> II diode 2 input.                                                                                                                      |  |  |

|                      |                            |                  | This multi-functional pin is programmable.                                                                                                                  |  |  |

| VTIN1 /              | 40                         | AIN              | Thermistor 1 terminal input. (Default)/                                                                                                                     |  |  |

| PIITD1               |                            |                  | Pentium <sup>™</sup> II diode 1 input.                                                                                                                      |  |  |

|                      |                            |                  | This multi-functional pin is programmable.                                                                                                                  |  |  |

| VID0                 | 41                         | IN <sub>t</sub>  | Voltage Supply readouts from P6. This value is read in the VID/Fan Divisor Register.                                                                        |  |  |

| OVT#                 | 42                         | OD <sub>12</sub> | Over temperature Shutdown Output.                                                                                                                           |  |  |

| ADRMSEL              | 43                         | INt              | Pin 4547 mode selection.                                                                                                                                    |  |  |

|                      |                            |                  | 0 = The 3 lowest order bits of ISA Address Bus.(Default, internal pull-down 47K ohm)                                                                        |  |  |

|                      |                            |                  | $1 = 7$ bit $I^2 C^{TM}$ address setting pin.(bit2 - bit0)                                                                                                  |  |  |

| SMI#                 | 44                         | OD <sub>12</sub> | System Management Interrupt (open drain). This output is<br>enabled when Bit 1 in the Configuration Register is set to 1. The<br>default state is disabled. |  |  |

| SA2-SA0              | 45-47                      | IN <sub>t</sub>  | The three lowest order bits of the 16-bit ISA Address Bus. A0 corresponds to the lowest order bit.                                                          |  |  |

|                      |                            |                  | (Default, when ARDMSEL =0 or left open )                                                                                                                    |  |  |

| IA2,IA1,IA0          |                            | INt              | The hardware setting pin of 7 bit $I^2C^{TM}$ serial address bit2, bit1 and bit0 at CR[48h]. (When ARDMSEL =1)                                              |  |  |

| CS#                  | 48                         | IN <sub>t</sub>  | Chip Select input from an external decoder which decodes high<br>order address bits on the ISA Address Bus. This is an active low<br>input.                 |  |  |

# 6. FUNCTIONAL DESCRIPTION

### 6.1 General Description

The W83782D provides 7 analog positive inputs, 3 fan speed monitors, at most 4 sets for fan PWM (Pulse Width Modulation) control, 3 thermal inputs from remote thermistors or 2N3904 transistors or Pentium<sup>TM</sup> II (Deschutes) thermal diode outputs, case open detection and beep function output when the monitor value exceed the set limit value including voltage, temperature, or fan counter. When start the monitor function on the chip, the watch dog machine monitor every function and store the value to registers. If the monitor value exceeds the limit value, the interrupt status will be set to 1.

### 6.2 Access Interface

The W83782D provides two interface for microprocessor to read/write internal registers.

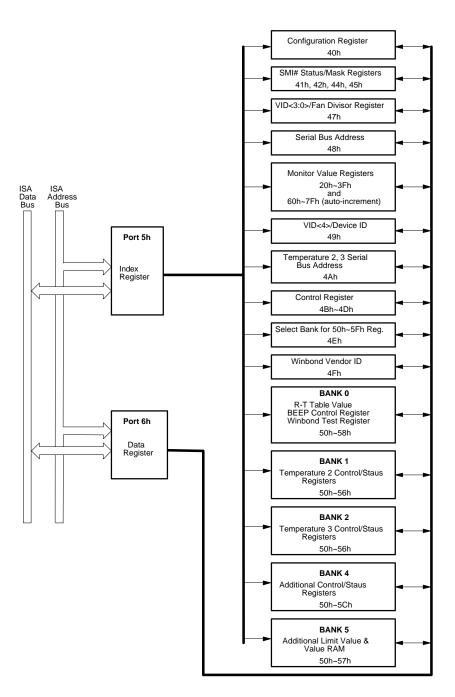

### 6.2.1 ISA interface

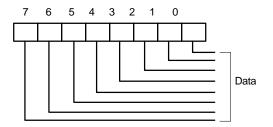

The first interface uses ISA Bus to access which the ports of low byte (bit2~bit0) are defined in the port 5h and 6h. The high byte (from ISA address bus bit15~bit3) of these ports is decoded by Chip Select (CS#), the general decoded address is set to port 295h and port 296h. These two ports are described as following:

Port 295h: W83782D Index register port.

Port 296h: Data port.

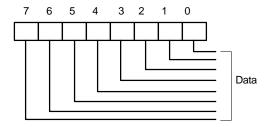

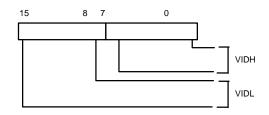

The register structure is showed as the Figure 1.

Figure 1. ISA interface access diagram

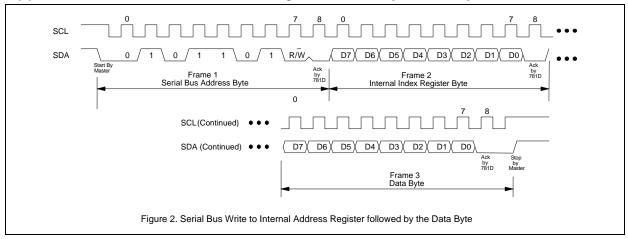

# 6.2.2 I<sup>2</sup>C interface

The second interface uses  $I^2C$  Serial Bus. In the W83782D has three serial bus address. That is, the first address defined at CR[48h] can read/write all registers excluding Bank 1 and Bank 2 temperature sensor 2/3 registers. The second address defined at CR[4Ah] bit2-0 only read/write temperature sensor 2 registers, and the third address defined at CR[4Ah] bit6-4 only can access (read/write) temperature sensor 3 registers.

The first serial bus address of W83782D has 3 hardware setting bits set by pin47-45 when pin 43 is set to high. The address is 00101[pin45][pin46][pin47]. If pin45=1, pin46=1, pin47=0, for example, the content of CR[48h] is 00101110. If CR[4Ah] bit 2-0 is XXX, the temperature sensor 2 serial address is 1001XXXG, in which G is the read/write bit. If CR[4Ah] bit 6-4 is YYY, the temperature sensor 3 serial address is 1001YYYG, in which G is the read/write bit.

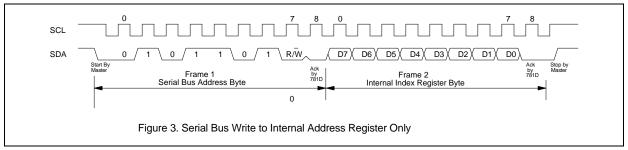

### 6.2.3 The first serial bus access timing are shown as follow:

(a) Serial bus write to internal address register followed by the data byte

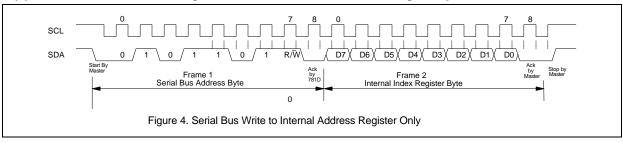

### (b) Serial bus write to internal address register only

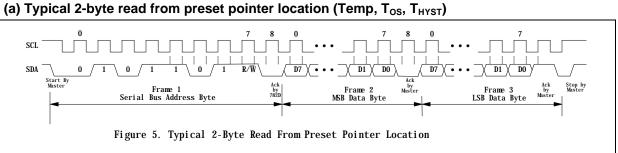

(c) Serial bus read from a register with the internal address register prefer to desired location

# 6.2.4 The serial bus timing of the temperature 2 and 3 is shown as follow:

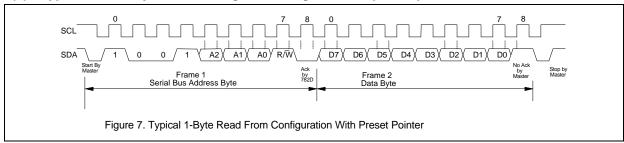

Typical read 1-byte from configuration register with preset pointer (C)

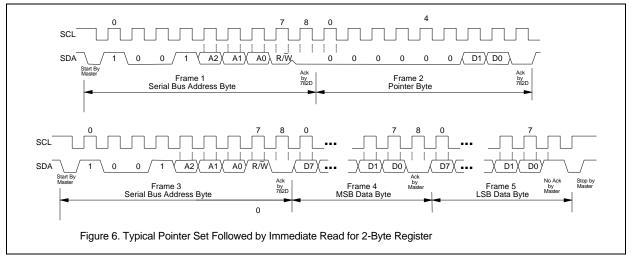

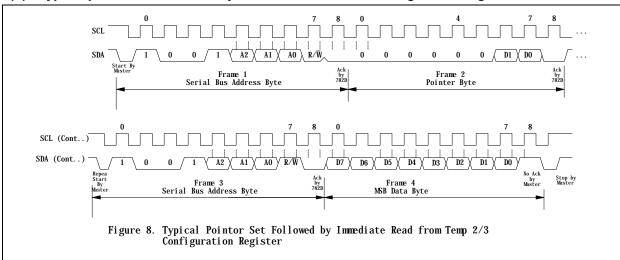

### (d) Typical pointer set followed by immediate read from configuration register

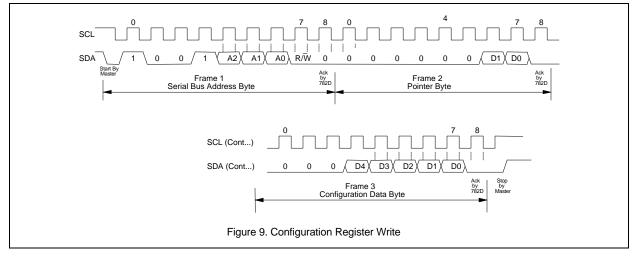

### (e) Temperature 2/3 configuration register Write

# (f) Temperature 2/3 Tos and THYST write

## 6.3 Analog Inputs

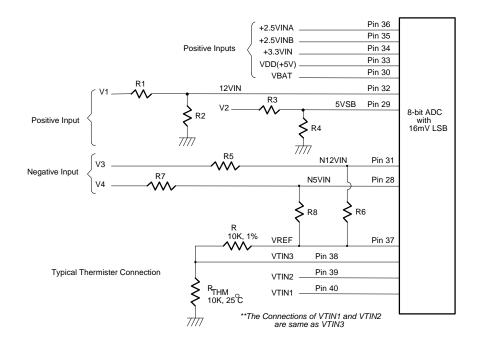

The maximum input voltage of the analog pin is 4.096V because the 8-bit ADC has a 16mv LSB. Really, the application of the PC monitoring would most often be connected to power suppliers. The CPU V-core voltage ,+3.3V and battery voltage can directly connected to these analog inputs. The 5VSB and +12V inputs should be reduced a factor with external resistors so as to obtain the input range. As Figure 11 shows.

Figure 11.

#### 6.3.1 Monitor over 4.096V voltage:

The input voltage +12VIN can be expressed as following equation.

$$12VIN = V_1 \times \frac{R_2}{R_1 + R_2}$$

The value of R1 and R2 can be selected to 28K Ohms and 10K Ohms, respectively, when the input voltage V1 is 12V. The node voltage of +12VIN can be subject to less than 4.096V for the maximun input range of the 8-bit ADC. Similarly, the node voltage of 5VSB (measure standby power VSB for ATX power supply) also can be evaluated by using two series resistors R3 and R4 which real value can be 5.1K ohms and 7.5K ohms so as to obtain the 5VSB is limited to less than 4.096V. The Pin 33 is connected to the power supply VCC with +5V. There are two functions in this pin with 5V. The first function is to supply internal analog power in the W83782D and the second function is that this voltage with 5V is connected to internal serial resistors to monitor the +5V voltage. The value of two serial resistors are 34K ohms and 50K ohms so that input voltage to ADC is 2.98V which is less than 4.096V of ADC maximum input voltage. The express equation can represent as follows.

$$V_{in} = VCC \times \frac{50 K\Omega}{50 K\Omega + 34 K\Omega} \cong 2.98V$$

where VCC is set to 5V.

#### 6.3.2 Monitor negative voltage:

The negative voltage should be connected two series resistors and a positive voltage VREF (is equal to 3.6V). In the Figure 11, the voltage V3 and V4 are two negative voltage which they are -12V and -5V respectively. The voltage V3 is connected to two serial resistors then is connected to another terminal VREF which is positive voltage. So as that the voltage node N12VIN can be obtain a posedge voltage if the scales of the two serial resistors are carefully selected. It is recommanded from Winbond that the scale of two serial resistors are R5=232K ohms and R6=56K ohm. the The input voltage of node -12VIN can be calculated by following equation.

$$N12VIN = (VREF + |V_5|) \times (\frac{232K\Omega}{232K\Omega + 56K\Omega}) + V_5$$

where VREF is equal 3.6V.

If the  $V_5$  is equal to -12V then the voltage is equal to 0.567V and the converted hexdecimal data is set to 35h by the 8-bit ADC with 16mV-LSB. This monitored value should be converted to the real negative votage and the express equation is shown as follows.

$$V_5 = \frac{N12VIN - VREF \times b}{1 - b}$$

Publication Release Date: April 1999 Revision A1

Where b is 232K/(232K+56K). If the N2VIN is 0.567 then the V5 is approximately equal to -12V.

The another negative voltage input V6 (approximate -5V) also can be evaluated by the similar method and the serial resistors can be selected with R7=120K ohms and R8=56K ohms by the Winbond recommended. The expression equation of V6 With -5V voltage is shown as follows.

$$V_{6} = \frac{N5VIN - VREF \times g}{1 - g}$$

Where the b is set to 120K/(120K+56K). If the monitored ADC value in the N5VIN channel is 0.8635, VREF=3.6V and the parameter b is 0.6818 then the negative voltage of V6 can be evalated to be - 5V.

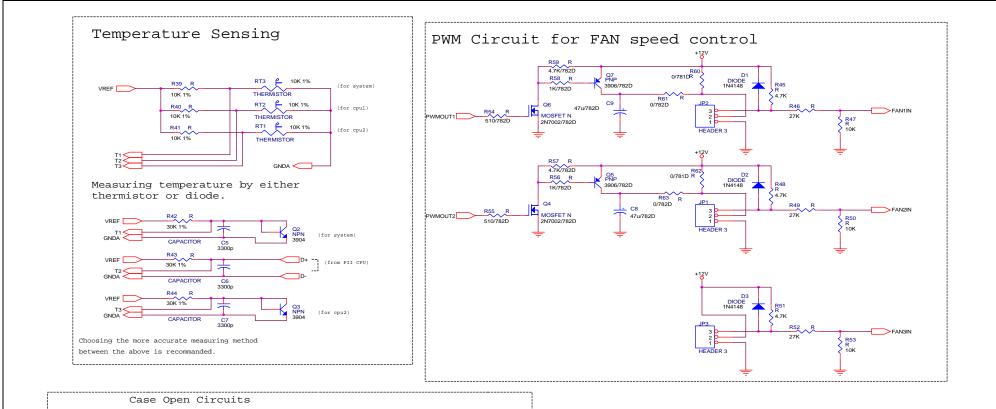

### 6.3.3 Monitor temperature from thermistor:

The W83782D can connect three thermistors to measure three different envirment temperature. The specification of thermistor should be considered to (1)  $\beta$  value is 3435K, (2) resistor value is 10K ohms at 25°C. In the Figure 11, the themistor is connected by a serial resistor with 10K Ohms, then connect to VREF (Pin 37).

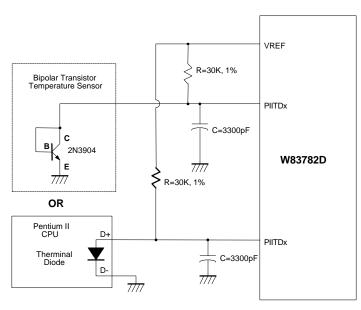

### 6.3.4 Monitor temperature from Pentium II<sup>™</sup> thermal diode or bipolar transistor 2N3904

The W83782D can alternate the thermistor to Pentium  $II^{TM}$  (Deschutes) thermal diode interface or transistor 2N3904 and the circuit connection is shown as Figure 12. The pin of Pentium  $II^{TM}$  D- is connected to power supply ground (GND) and the pin D+ is connected to pin PIITDx in the W83782D. The resistor R=30K ohms should be connected to VREF to supply the diode bias current and the bypass capacitor C=3300pF should be added to filter the high frequency noise. The transistor 2N3904 should be tied togeter to act as a thermal diode.

Figure 12.

### 6.4 FAN Speed Count and FAN Speed Control

### 6.4.1 Fan speed count

Vinbond

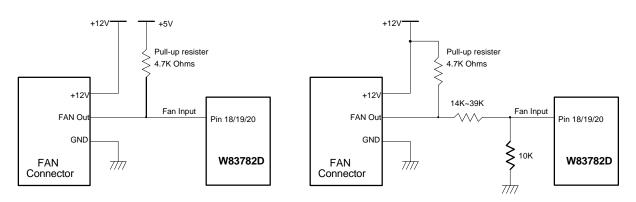

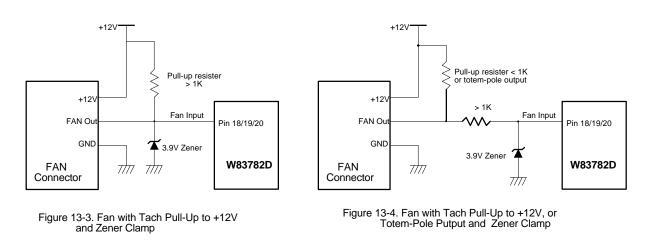

Inputs are provides for signals from fans equipped with tachometer outputs. The level of these signals should be set to TTL level, and maximum input voltage can not be over +5.5V. If the input signals from the tachometer outputs are over the VCC, the external trimming circuit should be added to reduce the voltage to obtain the input specification. The normal circuit and trimming circuits are shown as Figure 13.

Determine the fan counter according to:

$$Count = \frac{1.35 \times 10^6}{RPM \times Divisor}$$

In other words, the fan speed counter has been read from register CR28 or CR29 or CR2A, the fan speed can be evaluated by the following equation.

$$RPM = \frac{1.35 \times 10^6}{Count \times Divisor}$$

Publication Release Date: April 1999 Revision A1

The default divisor is 2 and defined at CR47.bit7~4, CR4B.bit7~6, and Bank0 CR5D.bit5~7 which are three bits for divisor. That provides very low speed fan counter such as power supply fan. The followed table is an example for the relation of divisor, PRM, and count.

| Divisor     | Nominal<br>PRM | Time per<br>Revolution | Counts | 70% RPM | Time for 70% |

|-------------|----------------|------------------------|--------|---------|--------------|

| 1           | 8800           | 6.82 ms                | 153    | 6160    | 9.74 ms      |

| 2 (default) | 4400           | 13.64 ms               | 153    | 3080    | 19.48 ms     |

| 4           | 2200           | 27.27 ms               | 153    | 1540    | 38.96 ms     |

| 8           | 1100           | 54.54 ms               | 153    | 770     | 77.92 ms     |

| 16          | 550            | 109.08 ms              | 153    | 385     | 155.84 ms    |

| 32          | 275            | 218.16 ms              | 153    | 192     | 311.68 ms    |

| 64          | 137            | 436.32 ms              | 153    | 96      | 623.36 ms    |

| 128         | 68             | 872.64 ms              | 153    | 48      | 1246.72 ms   |

Table 1.

# Preliminary W83782D

Figure 13-2. Fan with Tach Pull-Up to +12V, or Totem-Pole

Output and Register Attenuator

Figure 13-1. Fan with Tach Pull-Up to +5V

### 6.4.2 Fan speed control

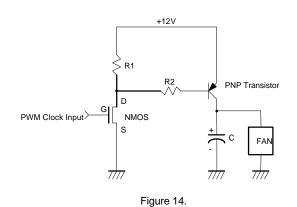

The W83782D provides four sets for fan PWM speed control. The duty cycle of PWM can be programmed by a 8-bit registers which are defined in the Bank0 CR5A, CR5B, CR5E, and CR5F. The default duty cycle is set to 100%, that is, the default 8-bit registers is set to FFh. The expression of duty can be represented as follows.

$$Duty - cycle(\%) = \frac{Programmed \ 8 - bit \ Register \ Value}{255} \times 100\%$$

The PWM clock frequency also can be program and defined in the Bank0.CR5C and Bank4.CR5C. The application circuit is shown as follows.

# Preliminary W83782D

### 6.5 Temperature Measurement Machine

The temperature data format is 8-bit two's-complement for sensor 1 and 9-bit two's-complement for sensor 2/3. The 8-bit temperature data can be obtained by reading the CR[27h]. The 9-bit temperature data can be obtained by reading the 8 MSBs from the Bank1/2 CR[50h] and the LSB from the Bank1/2 CR[51h] bit 7. The format of the temperature data is show in Table 1.

| Temperature | 8-Bit Digi   | ital Output | 9-Bit Digital Output |           |

|-------------|--------------|-------------|----------------------|-----------|

|             | 8-Bit Binary | 8-Bit Hex   | 9-Bit Binary         | 9-Bit Hex |

| +125øC      | 0111,1101    | 7Dh         | 0,1111,1010          | 0FAh      |

| +25øC       | 0001,1001    | 19h         | 0,0011,0010          | 032h      |

| +1øC        | 0000,0001    | 01h         | 0,0000,0010          | 002h      |

| +0.5øC      | -            | -           | 0,0000,0001          | 001h      |

| +0øC        | 0000,0000    | 00h         | 0,0000,0000          | 000h      |

| -0.5øC      | -            | -           | 1,1111,1111          | 1FFh      |

| -1øC        | 1111,1111    | FFh         | 1,1111,1110          | 1FFh      |

| -25øC       | 1110,0111    | E7h         | 1,1100,1110          | 1CEh      |

| -55øC       | 1100,1001    | C9h         | 1,1001,0010          | 192h      |

Table 2.

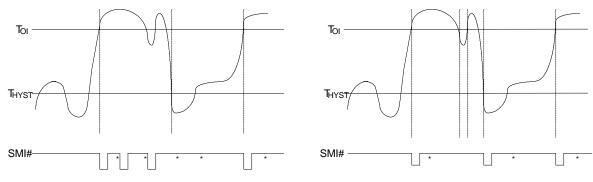

### 6.5.1 The W83782D temperature sensor 1 SMI# interrupt has two modes:

#### (1) Comparator Interrupt Mode

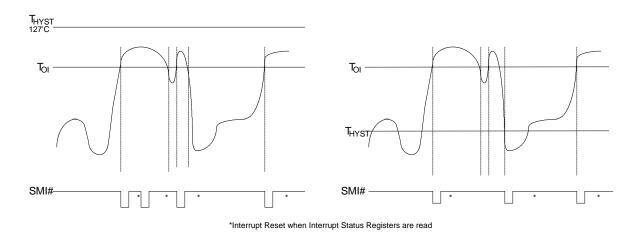

Setting the  $T_{HYST}$  (Temperature Hysteresis) limit to 127øC will set temperature sensor 1 SMI# to the Comparator Interrupt Mode. Temperature exceeds  $T_O$  (Over Temperature) Limit causes an interrupt and this interrupt will be reset by reading all the Interrupt Status Register. Once an interrupt event has occurred by exceeding  $T_O$ , then reset, if the temperature remains above the  $T_O$ , the interrupt will occur again when the next conversion has completed. If an interrupt event has occurred by exceeding  $T_O$  and not reset, the interrupts will not occur again. The interrupts will continue to occur in this manner until the temperature goes below  $T_O$ . (Figure 16-1)

#### (2) Two-Times Interrupt Mode

Setting the  $T_{\rm HYST}$  lower than  $T_{\rm O}$  will set temperature sensor 1 SMI# to the Two-Times Interrupt Mode. Temperature exceeding  $T_{\rm O}\,$  causes an interrupt and then temperature going below  $T_{\rm HYST}$  will also cause an interrupt if the previous interrupt has been reset by reading all the interrupt Status Register. Once an interrupt event has occurred by exceeding  $T_{\rm O}\,$ , then reset, if the temperature remains above the  $T_{\rm HYST}$ , the interrupt will not occur. (Figure 15-2 )

Figure 15-1. Comparator Interrupt Mode

Figure 15-2. Two-Times Interrupt Mode

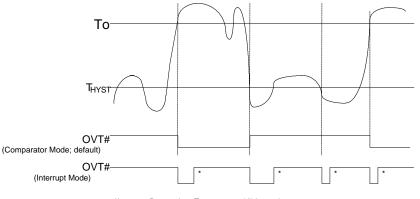

# 6.5.2 The W83782D temperature sensor 2 and sensor 3 SMI# interrupt has two modes and it is programmed at CR[4Ch] bit 6.

#### (1) Comparator Interrupt Mode

Temperature exceeding  $T_O$  causes an interrupt and this interrupt will be reset by reading all the Interrupt Status Register. Once an interrupt event has occurred by exceeding  $T_O$ , then reset, if the temperature remains above the  $T_{HYST}$ , the interrupt will occur again when the next conversion has completed. If an interrupt event has occurred by exceeding  $T_O$  and not reset, the interrupts will not occur again. The interrupts will continue to occur in this manner until the temperature goes below  $T_{HYST}$ . (Figure 16-1)

#### (2) Two-Times Interrupt Mode

Temperature exceeding  $T_{\rm O}\,$  causes an interrupt and then temperature going below  $T_{\rm HYST}$  will also cause an interrupt if the previous interrupt has been reset by reading all the interrupt Status Register. Once an interrupt event has occurred by exceeding  $T_{\rm O}$ , then reset, if the temperature remains above the  $T_{\rm HYST}$ , the interrupt will not occur. (Figure 16-2 )

\*Interrupt Reset when Interrupt Status Registers are read

Figure 16-1. Comparator Interrupt Mode

Figure 16-2. Two-Times Interrupt Mode

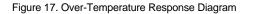

6.5.3 The W83782D temperature sensor 2 and 3 Over-Temperature (OVT#) has two modes, and they are programmed at Bank1 and Bank2 CR[52h] bit1 . These two bits needs to be programmed the same value.

### (1) Comparator Mode :

Temperature exceeding  $T_0$  causes the OVT# output activated until the temperature is less than  $T_{HYST}$ . (Figure 17)

### (2) Interrupt Mode:

Temperature exceeding  $T_{\rm O}$  causes the OVT# output activated indefinitely until reset by reading temperature sensor 2 or sensor 3 registers. Temperature exceeding  $T_{\rm O}$ , then OVT# reset, and then temperature going below  $T_{\rm HYST}$  will also cause the OVT# activated indefinitely until reset by reading temperature sensor2 or sensor 3 registers. Once the OVT# is activated by exceeding  $T_{\rm O}$ , then reset, if the temperature remains above  $T_{\rm HYST}$ , the OVT# will not be activated again.(Figure 17)

\*Interrupt Reset when Temperature 2/3 is read

# 7. REGISTERS AND RAM

## 7.1 Address Register (Port x5h)

| Data Port:             | Port x5h                              |

|------------------------|---------------------------------------|

| Power on Default Value | 00h                                   |

| Attribute:             | Bit 6:0 Read/write , Bit 7: Read Only |

| Size:                  | 8 bits                                |

### Bit7: Read Only

The logical 1 indicates the device is busy because of a Serial Bus transaction or another ISA bus transaction. With checking this bit, multiple ISA drivers can use W83782D without interfering with each other or a Serial Bus driver.

It is the user's responsibility not to have a Serial Bus and ISA bus operations at the same time.

This bit is:

Set: with a write to Port x5h or when a Serial Bus transaction is in progress.

**Reset:** with a write or read from Port x6h if it is set by a write to Port x5h, or when the Serial Bus transaction is finished.

Bit 6-0: Read/Write

| Bit 7                | Bit 6                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------------|----------------------------------------|-------|-------|-------|-------|-------|-------|

| Busy                 | Address Pointer (Power On default 00h) |       |       |       |       |       |       |

| (Power On default 0) | A6                                     | A5    | A4    | A3    | A2    | A1    | A0    |

# Address Pointer Index (A6-A0)

| Registers and RAM           | A6-A0 in Hex | Power On Value of Registers:<br><k7:0>in Binary</k7:0> | Notes                                                                                           |

|-----------------------------|--------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Configuration Register      | 40h          | 00001000                                               |                                                                                                 |

| Interrupt Status Register 1 | 41h          | 0000000                                                | Auto-increment to the address of Interrupt Status Register 2 after a read or write to Port x6h. |

| Interrupt Status Register 2 | 42h          | 0000000                                                |                                                                                                 |

| SMI#Ý Mask Register 1       | 43h          | 0000000                                                | Auto-increment to the address of SMIÝ Mask Register 2 after a read or write to Port x6h.        |

| SMIÝ Mask Register 2        | 44h          | 0000000                                                |                                                                                                 |

| NMI Mask Register 1         | 45h          | 0000000                                                | Auto-increment to the address of NMI Mask<br>Register 2 after a read or write to Port x6h       |

| NMI Mask Register 2         | 46h          | 0100000                                                |                                                                                                 |

| VID/Fan Divisor Register    | 47h          | <7:4> = 0101;                                          |                                                                                                 |

|                             |              | <3:0> = VID3-ID0                                       |                                                                                                 |

| Serial Bus Address Register | 48h          | <6:0> = 0101101; <7> = 0                               |                                                                                                 |

| POST RAM                    | 00-1Fh       |                                                        | Auto-increment to the next location after a read or write to Port x6h and stop at 1Fh.          |

| Value RAM                   | 20-3Fh       |                                                        |                                                                                                 |

| Value RAM                   | 60-7Fh       |                                                        | Auto-increment to the next location after a read or write to Port x6h and stop at 7Fh.          |

# 7.2 Data Register (Port x6h)

| Data Port:             | Port x6h   |

|------------------------|------------|

| Power on Default Value | 00h        |

| Attribute:             | Read/write |

| Size:                  | 8 bits     |

Bit 7-0: Data to be read from or to be written to RAM and Register.

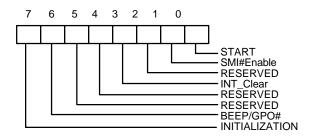

# 7.3 Configuration Register <sup>3</sup>/<sub>4</sub> Index 40h

| Register Location:     | 40h             |

|------------------------|-----------------|

| Power on Default Value | 00000001 binary |

| Attribute:             | Read/write      |

| Size:                  | 8 bits          |

- Bit 7: A one restores power on default value to all registers except the Serial Bus Address register. This bit clears itself since the power on default is zero.

- Bit 6: The logical 1 in this bit drives a zero on BEEP/GPO# pin.

Bit 5: Reserved

Bit 4: Reserved

Bit 3: A one disables the SMI# output without affecting the contents of Interrupt Status Registers. The device will stop monitoring. It will resume upon clearing of this bit.

Bit 2: Reserved

Bit 1: A one enables the SMI# Interrupt output.

Bit 0: A one enables startup of monitoring operations, a zero puts the part in standby mode.

**Note:** The outputs of Interrupt pins will not be cleared if the user writes a zero to this location after an interrupt has occurred unlike "INT\_Clear" bit.

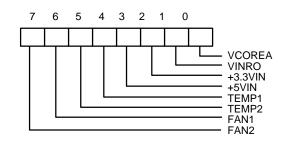

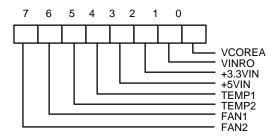

### 7.4 Interrupt Status Register 1<sup>3</sup>/<sub>4</sub> Index 41h

| Register Location:     | 41h       |

|------------------------|-----------|

| Power on Default Value | 00h       |

| Attribute:             | Read Only |

| Size:                  | 8 bits    |

# Priliminary W83782D

Bit 7: A one indicates the fan count limit of FAN2 has been exceeded.

- Bit 6: A one indicates the fan count limit of FAN1 has been exceeded.

- Bit 5: A one indicates a High limit of VTIN2 has been exceeded from temperature sensor 2.

- Bit 4: A one indicates a High limit of VTIN1 has been exceeded from temperature sensor 1.

- Bit 3: A one indicates a High or Low limit of +5VIN has been exceeded.

- Bit 2: A one indicates a High or Low limit of +3.3VIN has been exceeded.

- Bit 1: A one indicates a High or Low limit of VINR0 has been exceeded.

- Bit 0: A one indicates a High or Low limit of VCOREA has been exceeded.

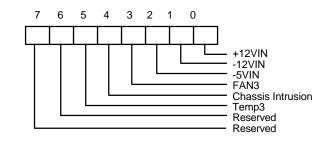

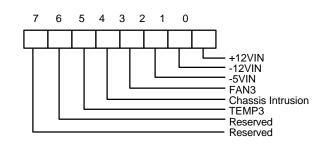

### 7.5 Interrupt Status Register 2 <sup>3</sup>/<sub>4</sub> Index 42h

| Register Location:     | 42h       |

|------------------------|-----------|

| Power on Default Value | 00h       |

| Attribute:             | Read Only |

| Size:                  | 8 bits    |

Bit 7-6:Reserved.This bit should be set to 0.

Bit 5: A one indicates a High limit of VTIN3 has been exceeded from temperature sensor 3.

Bit 4: A one indicates Chassis Intrusion has gone high.

Bit 3: A one indicates the fan count limit of FAN3 has been exceeded.

Bit 2: A one indicates a High or Low limit of -5VIN has been exceeded.

Bit1: A one indicates a High or Low limit of -12VIN has been exceeded.

Bit0: A one indicates a High or Low limit of +12VIN has been exceeded.

# 7.6 SMI# Mask Register 1 <sup>3</sup>⁄<sub>4</sub> Index 43h

| Register Location:     | 43h        |

|------------------------|------------|

| Power on Default Value | 00h        |

| Attribute:             | Read/Write |

| Size:                  | 8 bits     |

Bit 7-0: A one disables the corresponding interrupt status bit for SMI interrupt.

### 7.7 SMI# Mask Register 2 3/4 Index 44h

| Register Location:     | 44h        |

|------------------------|------------|

| Power on Default Value | 00h        |

| Attribute:             | Read/Write |

| Size:                  | 8 bits     |

Bit 7-6: Reserved. This bit should be set to 0.

Bit 5-0: A one disables the corresponding interrupt status bit for  $\overline{SMI}$  interrupt.

### 7.8 Reserved Register ¾ Index 45h

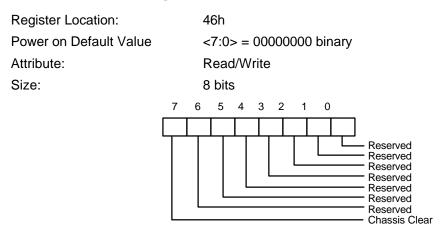

### 7.9 Chassis Clear Register -- Index 46h

Bit 7: Set 1, clear Chassis Intrusion event. This bit self clears after clearing Chassis Intrusion event. Bit 6-0:Reserved. This bit should be set to 0.

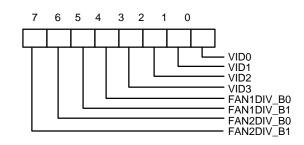

### 7.10 VID/Fan Divisor Register 3/4 Index 47h

| Register Location:     | 47h                                        |

|------------------------|--------------------------------------------|

| Power on Default Value | <7:4> is 0101, <3:0> is mapped to VID<3:0> |

| Attribute:             | Read/Write                                 |

| Size:                  | 8 bits                                     |

# Priliminary W83782D

Bit 7-6: FAN2 Speed Control.

Bit 5-4: FAN1 Speed Control.

Bit 3-0: The VID <3:0> inputs

Note : Please refer to Bank0 CR[5Dh] , Fan divisor table.

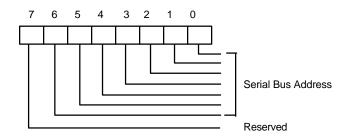

### 7.11 Serial Bus Address Register <sup>3</sup>/<sub>4</sub> Index 48h

Register Location:48hPower on Default Value Serial Bus address<6:0> = 0101101 and <7> = 0 binarySize:8 bits

Bit 7: Read Only - Reserved.

Bit 6-0: Read/Write - Serial Bus address <6:0>.

| Address A6-A0 | Address A6-A0 with<br>Auto-Increment | Description                                                                                  |

|---------------|--------------------------------------|----------------------------------------------------------------------------------------------|

| 20h           | 60h                                  | VCOREA reading                                                                               |

| 21h           | 61h                                  | VINR0 reading                                                                                |

| 22h           | 62h                                  | +3.3VIN reading                                                                              |

| 23h           | 63h                                  | +5VIN reading                                                                                |

| 24h           | 64h                                  | +12VIN reading                                                                               |

| 25h           | 65h                                  | -12VIN reading                                                                               |

| 26h           | 66h                                  | -5VIN reading                                                                                |

| 27h           | 67h                                  | Temperature reading                                                                          |

| 28h           | 68h                                  | FAN1 reading                                                                                 |

|               |                                      | <b>Note:</b> This location stores the number of counts of the internal clock per revolution. |

| 29h           | 69h                                  | FAN2 reading                                                                                 |

|               |                                      | <b>Note:</b> This location stores the number of counts of the internal clock per revolution. |

| 2Ah           | 6Ah                                  | FAN3 reading                                                                                 |

|               |                                      | <b>Note:</b> This location stores the number of counts of the internal clock per revolution. |

| 2Bh           | 6Bh                                  | VCOREA High Limit, default value is defined by Vcore Voltage +0.2v.                          |

| 2Ch           | 6Ch                                  | VCOREA Low Limit, default value is defined by Vcore Voltage -0.2v.                           |

| 2Dh           | 6Dh                                  | VINR0 High Limit.                                                                            |

| 2Eh           | 6Eh                                  | VINR0 Low Limit.                                                                             |

| 2Fh           | 6Fh                                  | +3.3VIN High Limit                                                                           |

| 30h           | 70h                                  | +3.3VIN Low Limit                                                                            |

| 31h           | 71h                                  | +5VIN High Limit                                                                             |

| 32h           | 72h                                  | +5VIN Low Limit                                                                              |

## 7.12 Value RAM <sup>3</sup>/<sub>4</sub> Index 20h- 3Fh or 60h - 7Fh (auto-increment)

| Address A6-A0 | Address A6-A0 with<br>Auto-Increment | Description                                                                                       |

|---------------|--------------------------------------|---------------------------------------------------------------------------------------------------|

| 33h           | 73h                                  | +12VIN High Limit                                                                                 |

| 34h           | 74h                                  | +12VIN Low Limit                                                                                  |

| 35h           | 75h                                  | -12VIN High Limit                                                                                 |

| 36h           | 76h                                  | -12VIN Low Limit                                                                                  |

| 37h           | 77h                                  | -5VIN High Limit                                                                                  |

| 38h           | 78h                                  | -5VIN Low Limit                                                                                   |

| 39h           | 79h                                  | Temperature sensor 1 (VTIN1) High Limit                                                           |

| 3Ah           | 7Ah                                  | Temperature sensor 1 (VTIN1) Hysteresis Limit                                                     |

| 3Bh           | 7Bh                                  | FAN1 Fan Count Limit                                                                              |

|               |                                      | <b>Note:</b> It is the number of counts of the internal clock for the Low Limit of the fan speed. |

| 3Ch           | 7Ch                                  | FAN2 Fan Count Limit                                                                              |

|               |                                      | <b>Note:</b> It is the number of counts of the internal clock for the Low Limit of the fan speed. |

| 3Dh           | 7Dh                                  | FAN3 Fan Count Limit                                                                              |

|               |                                      | <b>Note:</b> It is the number of counts of the internal clock for the Low Limit of the fan speed. |

| 3E- 3Fh       | 7E- 7Fh                              | Reserved                                                                                          |

7.12 Value RAM — Index 20h- 3Fh or 60h - 7Fh (auto-increment), continued

Setting all ones to the high limits for voltages and fans (0111 1111 binary for temperature) means interrupts will never be generated except the case when voltages go below the low limits.

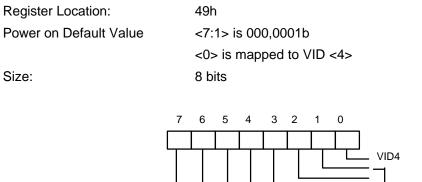

## 7.13 Voltage ID (VID4) & Device ID -- Index 49h

\_\_\_\_ DID<6:0>

Bit 7-1: Read Only - Device ID<6:0>

Bit 0 : Read/Write - The VID4 inputs.

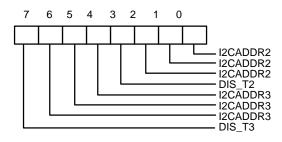

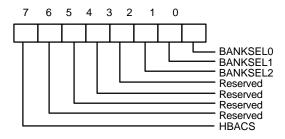

#### 7.14 Temperature 2 and Temperature 3 Serial Bus Address Register--Index 4Ah

Register Location:4AhPower on Default Value<7:0> = 0000,0001 binary. Reset by MRAttribute:Read/WriteSize:8 bits

Bit 7: Set to 1, disable temperature sensor 3 and can not access any data from Temperature Sensor 3.

Bit 6-4: Temperature 3 Serial Bus Address. The serial bus address is 1001xxx. Where xxx are defined in these bits.

Bit 3: Set to 1, disable temperature Sensor 2 and can not access any data from Temperature Sensor 2.

Bit 2-0: Temperature 2 Serial Bus Address. The serial bus address is 1001xxx. Where xxx are defined in these bits.

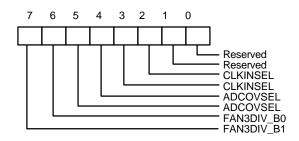

#### 7.15 Pin Control Register -- Index4Bh

Register Location: Power on Default Value Attribute: Size: 4Bh <7:0> 44h. Reset by MR. Read/Write 8 bits

Bit 7-6:Fan3 speed divisor.

Please refer to Bank0 CR[5Dh] , Fan divisor table.

- Bit 5-4: Select A/D Converter Clock Input.

- <5:4> = 00 default. ADC clock select 22.5 Khz.

- <5:4> = 01- ADC clock select 5.6 Khz. (22.5K/4)

- <5:4> = 10 ADC clock select 1.4Khz. (22.5K/16)

- <5:4> = 11 ADC clock select 0.35 Khz. (22.5K/64)

Bit 3-2: Clock Input Select.

<3:2> = 00 - Pin 3 (CLKIN) select 14.318M Hz clock.

<3:2> = 01 - Default. Pin 3 (CLKIN) select 24M Hz clock.

<3:2> = 10 - Pin 3 (CLKIN) select 48M Hz clock .

<3:2> = 11 - Reserved. Pin3 no clock input.

Bit 1-0: Reserved. User defined.

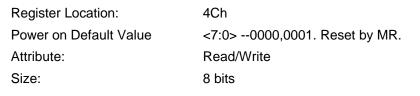

#### 7.16 IRQ#/OVT# Property Select -- Index 4Ch

- Bit 7: Reserved. User Defined.

- Bit6: Set to 1, the SMI# output type of Temperature 2 and 3 is set to Comparator Interrupt mode. Set to 0, the SMI# output type is set to Two-Times Interrupt mode. (default 0)

- Bit5: Reserved. User Defined.

- Bit 4: Disable temperature sensor 3 over-temperature (OVT) output if set to 1. Default 0, enable OVT2 output through pin OVT#.

- Bit 3: Disable temperature sensor 2 over-temperature (OVT) output if set to 1. Default 0, enable OVT1 output through pin OVT#.

- Bit 2: Over-temperature polarity. Write 1, OVT# active high. Write 0, OVT# active low. Default 0.

- Bit 1: Reserved. User Defined.

- Bit 0: Reserved. User Defined.

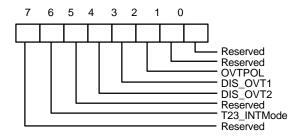

## 7.17 FAN IN/OUT and BEEP/GPO# Control Register -- Index 4Dh

| Register Location:     |   | 4[ | Dh                            |     |      |   |   |   |

|------------------------|---|----|-------------------------------|-----|------|---|---|---|

| Power on Default Value |   | <7 | <7:0> 0001,0101. Reset by MR. |     |      |   |   |   |

| Attribute:             |   | R  | eac                           | I/W | rite |   |   |   |

| Size:                  |   | 8  | bits                          | 5   |      |   |   |   |

|                        | 7 | 6  | 5                             | 4   | 3    | 2 | 1 | 0 |

- Bit 7: Disable power-on abnormal the monitor voltage including V-Core A and +3.3V. If these voltage exceed the limit value, the pin (Open Drain) of BEEP will drives 300Hz and 600Hz frequency signal. Write 1, the frequency will be disable. Default 0. After power on, the system should set 1 to this bit to 1 in order to disable BEEP.

- Bit 6: BEEP/GPO# Pin Function Select. Write 1 Select GPO# function. Set 0, select BEEP function. This bit default 0.

- Bit 5: FAN 3 output value if FANINC3 sets to 0. Write 1, then pin 18 always generate logic high signal. Write 0, pin 18 always generates logic low signal. This bit default 0.

- Bit 4: FAN 3 Input Control. Set to 1, pin 18 acts as FAN clock input, which is default value. Set to 0, this pin 18 acts as FAN control signal and the output value of FAN control is set by this register bit 5. This output pin can connect to power PMOS gate to control FAN ON/OFF.

- Bit 3: FAN 2 output value if FANINC2 sets to 0. Write 1, then pin 19 always generate logic high signal. Write 0, pin 19 always generates logic low signal. This bit default 0.

- Bit 2: FAN 2 Input Control. Set to 1, pin 19 acts as FAN clock input, which is default value. Set to 0, this pin 19 acts as FAN control signal and the output value of FAN control is set by this register bit 3. This output pin can connect to power NMOS gate to control FAN ON/OFF.

- Bit 1: FAN 1 output value if FANINC1 sets to 0. Write 1, then pin 20 always generate logic high signal. Write 0, pin 20 always generates logic low signal. This bit default 0.

- Bit 0: FAN 1 Input Control. Set to 1, pin 20 acts as FAN clock input, which is default value. Set to 0, this pin 20 acts as FAN control signal and the output value of FAN control is set by this register t 1. This output pin can connect to power PMOS gate to control FAN ON/OFF.

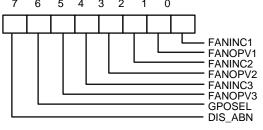

## 7.18 Register 50h ~ 5Fh Bank Select -- Index 4Eh

| Register Location:     | 4Eh                                               |

|------------------------|---------------------------------------------------|

| Power on Default Value | <6:3> = Reserved, <7> = 1, <2:0> = 0. Reset by MR |

| Attribute:             | Read/Write                                        |

| Size:                  | 8 bits                                            |

|                        |                                                   |

Bit 7: HBACS- High byte access. Set to 1, access Register 4Fh high byte register.

Set to 0, access Register 4Fh low byte register. Default 1.

Bit 6-3: Reserved. This bit should be set to 0.

Bit 2-0: Index ports 0x50~0x5F Bank select.

#### 7.19 Winbond Vendor ID -- Index 4Fh

| Register Location:     | 4Fh            |

|------------------------|----------------|

| Power on Default Value | <15:0> = 5CA3h |

| Attribute:             | Read Only      |

| Size:                  | 16 bits        |

Bit 15-8: Vendor ID High Byte if CR4E.bit7=1.Default 5Ch.

Bit 7-0: Vendor ID Low Byte if CR4E.bit7=0. Default A3h.

## 7.20 Winbond Test Register -- Index 50h - 55h (Bank 0)

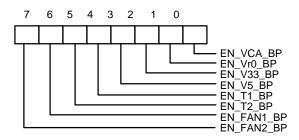

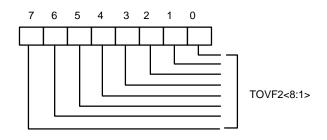

### 7.21 BEEP Control Register 1-- Index 56h (Bank 0)

Register Location: Power on Default Value Attribute: Size: 56h <7:0> 0000,0000. Reset by MR. Read/Write 8 bits

- Bit 7: Enable BEEP Output from FAN 2 if the monitor value exceed the limit value. Write 1, enable BEEP output, which is default value.

- Bit 6: Enable BEEP Output from FAN 1 if the monitor value exceed the limit value. Write 1, enable BEEP output, which is default value.

- Bit 5: Enable BEEP Output from Temperature Sensor 2 if the monitor value exceed the limit value. Write 1, enable BEEP output. Default 0

- Bit 4: Enable BEEP output for Temperature Sensor 1 if the monitor value exceed the limit value. Write 1, enable BEEP output. Default 0

- Bit 3: Enable BEEP output from VDD (+5V), Write 1, enable BEEP output if the monitor value exceed the limits value. Default 0, that is disable BEEP output.

- Bit 2: Enable BEEP output from +3.3V. Write 1, enable BEEP output, which is default value.

- Bit 1: Enable BEEP output from VINR0. Write 1, enable BEEP output, which is default value.

- Bit 0: Enable BEEP Output from VCOREA if the monitor value exceed the limits value. Write 1, enable BEEP output, which is default value

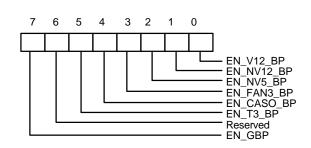

## 7.22 BEEP Control Register 2-- Index 57h (Bank 0)

Register Location: 57h

Power on Default Value <7:0> 1000-0000. Reset by MR.

Attribute: Read/Write

Size: 8 bits

- Bit 7: Enable Global BEEP. Write 1, enable global BEEP output. Default 1. Write 0, disable all BEEP output.

- Bit 6: Reserved. This bit should be set to 0.

- Bit 5: Enable BEEP Output from Temperature Sensor 3 if the monitor value exceed the limit value. Write 1, enable BEEP output. Default 0

- Bit 4: Enable BEEP output for case open if the monitor value exceed the limit value. Write 1, enable BEEP output. Default 0.

- Bit 3: Enable BEEP Output from FAN 3 if the monitor value exceed the limit value. Write 1, enable BEEP output. Default 0.

- Bit 2: Enable BEEP output from -5V, Write 1, enable BEEP output if the monitor value exceed the limits value. Default 0, that is disable BEEP output.

- Bit 1: Enable BEEP output from -12V, Write 1, enable BEEP output if the monitor value exceed the limits value. Default 0, that is disable BEEP output.

- Bit 0: Enable BEEP output from +12V, Write 1, enable BEEP output if the monitor value exceed the limits value. Default 0, that is disable BEEP output.

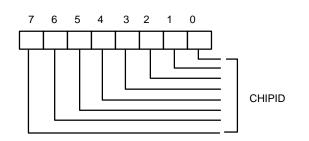

#### 7.23 Chip ID -- Index 58h (*Bank 0*)

| Register Location:     | 58h                           |

|------------------------|-------------------------------|

| Power on Default Value | <7:0> 0011-0000. Reset by MR. |

| Attribute:             | Read Only                     |

| Size:                  | 8 bits                        |

Bit 7: Winbond Chip ID number. Read this register will return 30h.

#### 7.24 Diode Selection Register -- Index 59h (Bank 0)

Register Location: Power on Default Value Attribute: Size:

59h <7>=0 and <6:4> = 111 and <3:0> = 0000 Read/Write 8 bits 7 6 5 4 3 2 0 1 Reserved Reserved Reserved Reserved SELPIIV1 SELPIIV2 SELPIIV3 Reserved

Bit 7: Reserved

- Bit 6: Temperature sensor diode 3. Set to 1, select Pentium II compatible Diode. Set to 0 to select 2N3904 Bipolar mode.

- Bit 5: Temperature sensor diode 2. Set to 1, select Pentium II compatible Diode. Set to 0 to select 2N3904 Bipolar mode.

- Bit 4: Temperature sensor diode 1. Set to 1, select Pentium II compatible Diode. Set to 0 to select 2N3904 Bipolar mode.

Bit 3-0: Reserved

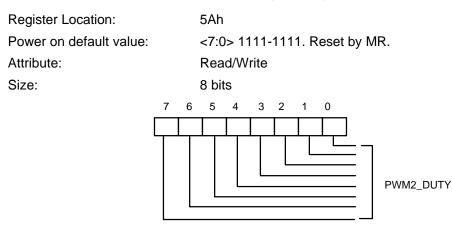

## 7.25 PWMOUT2 Control -- Index 5Ah (Bank 0)

Bit 7: PWMOUT2 duty cycle control

Write FF, Duty cycle is 100%, Write 00, Duty cycle is 0%.

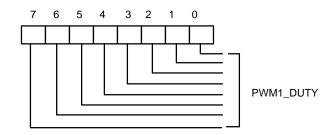

### 7.26 PWMOUT1 Control -- Index 5Bh (Bank 0)

Register Location: Power on default value: Attribute: Size:

5Bh <7:0> 1111-1111. Reset by MR. Read/Write 8 bits

Bit 7: PWMOUT1 duty cycle control Write FF, Duty cycle is 100%, Write 00, Duty cycle is 0%.

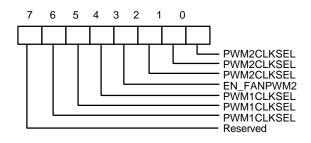

## 7.27 PWMOUT1/2 Clock Select -- Index 5Ch (Bank 0)

Register Location: Power on Default Value Attribute: Size: 5Ch <7:0> 0001-0001. Reset by MR. Read/Write 8 bits

Bit 7: Reserved

Bit 6-4: PWMOUT1 clock selection.

The clock defined frequency is same as PWMOUT2 clock selection.

Bit 3: Set to 1. Enable PWMOUT2 PWM Control Bit 2-0: PWMOUT2 clock Selection. <2:0> = 000: 46.87K Hz <2:0> = 001: 23.43K Hz (Default) <2:0> = 010: 11.72K Hz <2:0> = 011: 5.85K Hz <2:0> = 100: 2.93K Hz

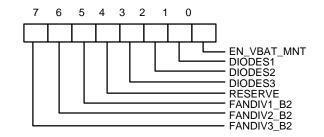

#### 7.28 VBAT Monitor Control Register -- Index 5Dh (Bank 0)

| Register Location:     | 5Dh                           |

|------------------------|-------------------------------|

| Power on Default Value | <7:0> 0000-0000. Reset by MR. |

| Attribute:             | Read/Write                    |

| Size:                  | 8 bits                        |

- Bit 7: Fan3 divisor Bit 2.

- Bit 6: Fan2 divisor Bit 2.

- Bit 5: Fan1 divisor Bit 2.

- Bit 4: Reserve.

- Bit 3: Temperature sensor 3 select into thermal diode such as Pentium II CPU supported. Set to 1, select bipolar sensor. Set to 0, select thermistor sensor.

- Bit 2: Sensor 2 type selection. Defined as DIODES3 described in the bit 3.

- Bit 1: Sensor 1 type selection. Defined as DIODES2 described in the bit 3.

- Bit 0: Set to 1, enable battery voltage monitor. Set to 0, disable battery voltage monitor. If enable this bit, the monitor value is value after one monitor cycle. Note that the monitor cycle time is at least 300ms for W83782D.

## Fan divisor table :

| Bit 2 | Bit 1 | Bit 0 | Fan<br>Divisor | Bit 2 | Bit 1 | Bit 0 | Fan Divisor |

|-------|-------|-------|----------------|-------|-------|-------|-------------|

| 0     | 0     | 0     | 1              | 1     | 0     | 0     | 16          |

| 0     | 0     | 1     | 2              | 1     | 0     | 1     | 32          |

| 0     | 1     | 0     | 4              | 1     | 1     | 0     | 64          |

| 0     | 1     | 1     | 8              | 1     | 1     | 1     | 128         |

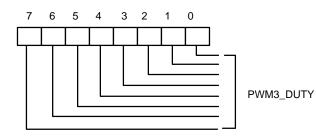

## 7.29 PWMOUT3 Control -- Index 5Eh (Bank 0)

Register Location: Power on Default Value Attribute: Size:

5Eh <7:0> 1111-1111. Reset by MR. Read/Write 8 bits

Bit 7: PWMOUT3 duty cycle control

Write FF, Duty cycle is 100%,

Write 00, Duty cycle is 0%.

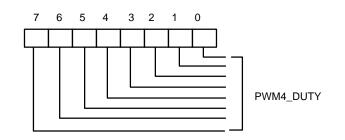

## 7.30 PWMOUT4 Control -- Index 5Fh (Bank 0)

| Register Location:     | 5Fh                           |

|------------------------|-------------------------------|

| Power on Default Value | <7:0> 1111-1111. Reset by MR. |

| Attribute:             | Read Only                     |

| Size:                  | 8 bits                        |

Bit 7: PWMOUT4 duty cycle control

Write FF, Duty cycle is 100%,

Write 00, Duty cycle is 0%.

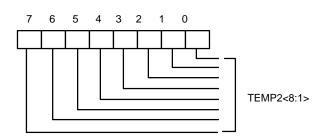

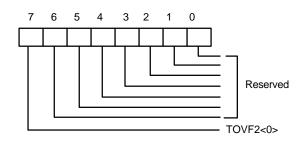

## 7.31 Temperature Sensor 2 Temperature (High Byte) Register - Index 50h (Bank 1)

| Register Location: | 50h       |

|--------------------|-----------|

| Attribute:         | Read Only |

| Size:              | 8 bits    |

Bit 7: Temperature <8:1> of sensor 2, which is high byte.

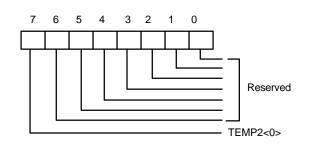

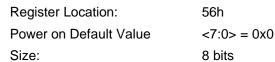

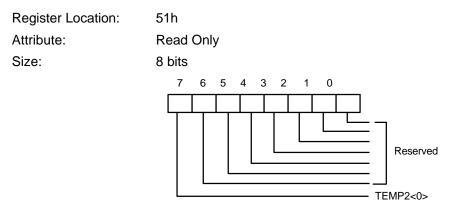

## 7.32 Temperature Sensor 2 Temperature (Low Byte) Register - Index 51h (Bank 1)

| Register Location: | 51h       |

|--------------------|-----------|

| Attribute:         | Read Only |

| Size:              | 8 bits    |

Bit 7: Temperature <0> of sensor2, which is low byte.

Bit 6-0: Reserved. This bit should be set to 0.

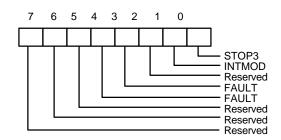

### 7.33 Temperature Sensor 2 Configuration Register - index 52h (Bank 1)

| Register Location:     | 52h          |

|------------------------|--------------|

| Power on Default Value | <7:0> = 0x00 |

| Size:                  | 8 bits       |

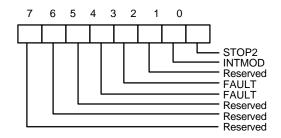

Bit 7-5: Read - Reserved. This bit should be set to 0.