OPTi Inc. 888 Tasman Drive Milpitas, CA 95035 (408) 486-8000 Fax: (408) 486-8001

# **Application Note (OPTi Confidential)**

Product Name: Viper Xpress+ Chipset

Title: BIOS Programming Guide

Date:

January 16, 1997

## Scope

This document outlines the recommended procedure for programming the internal registers of the Viper Xpress+ Chipset. It is intended to be a reference for a BIOS developer using the Viper Xpress+ Chipset in a PC design. This document classifies the internal registers of the Viper Xpress+ Chipset based on the subsystems that they control.

### Discussion

#### **BIOS Settings**

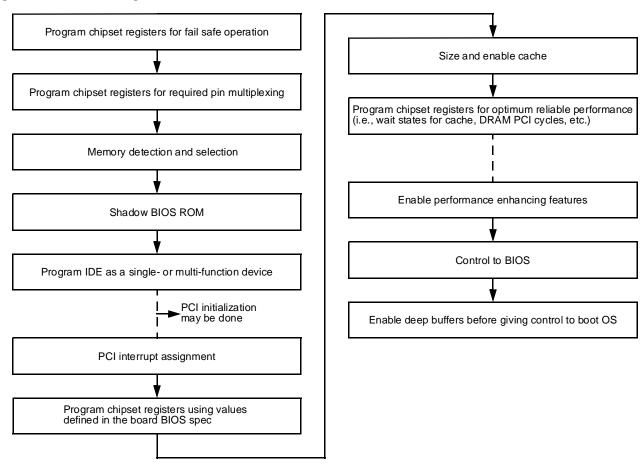

Given below is a chipset specific illustrative flow chart that a BIOS needs to follow to program the chipset registers.

Tables 1 through 4 provide the register settings required of the chipset that the BIOS should ensure in order for the system to boot. These are fail safe boot values.

#### Figure 1 Boot Setting

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

#### Table 1 82C579 Fail Safe Boot Values

| Loc. | Value                |

|------|----------------------|

|      | DV0<br>egister Space |

| 00h  | 45h                  |

| 01h  | 10h                  |

| 02h  | 69h                  |

| 03h  | C5h                  |

| 04h  | 07h                  |

| 05h  | 00h                  |

| 06h  | 80h                  |

| 07h  | 02h                  |

| 08h  | 10h                  |

| 09h  | 00h                  |

| 0Ah  | 00h                  |

| 0Bh  | 06h                  |

| 0Ch  | 00h                  |

| 0Dh  | 00h                  |

| 0Eh  | 00h                  |

| 0Fh  | 00h                  |

| 10h  | 00h                  |

| 11h  | 00h                  |

| 12h  | 00h                  |

| 13h  | 00h                  |

| 14h  | 00h                  |

| 15h  | 00h                  |

| 16h  | 00h                  |

| 17h  | 00h                  |

| 18h  | 00h                  |

| 19h  | 00h                  |

| 1Ah  | 00h                  |

| 1Bh  | 00h                  |

| 1Ch  | 00h                  |

| 1Dh  | 00h                  |

| 1Eh  | 00h                  |

| 1Fh  | 00h                  |

| 20h  | 00h                  |

| 21h  | 00h                  |

| Loc.               | Value |

|--------------------|-------|

| 22h                | 00h   |

| 23h                | 00h   |

| 24h                | 00h   |

| 25h                | 00h   |

| 26h                | 00h   |

| 27h                | 00h   |

| 28h                | 00h   |

| 29h                | 00h   |

| 2Ah                | 00h   |

| 2Bh                | 00h   |

| 2Ch                | 00h   |

| 2Dh                | 00h   |

| 2Eh                | 00h   |

| 2Fh                | 00h   |

| 30h                | 00h   |

| 31h                | 00h   |

| 32h                | 00h   |

| 33h                | 00h   |

| 34h                | 00h   |

| 35h                | 00h   |

| 36h                | 00h   |

| 37h                | 00h   |

| 38h                | 00h   |

| 39h                | 00h   |

| 3Ah                | 00h   |

| 3Bh                | 00h   |

| 3Ch                | 00h   |

| 3Dh                | 00h   |

| 3Eh                | 00h   |

| 3Fh                | 00h   |

| 40h                | 00h   |

| 41h                | 00h   |

| 42h                | 00h   |

| 43h                | 20h   |

| 44h <sup>(1)</sup> | 01h   |

| 45h                | 00h   |

|                    |       |

| 1                  |                    |  |

|--------------------|--------------------|--|

| Loc.               | Value              |  |

| 46h                | 00h                |  |

| 47h                | 00h                |  |

| 48h                | 00h                |  |

| 49h                | 00h                |  |

| 4Ah                | 00h                |  |

| 4Bh                | 00h                |  |

| 4Ch                | 40h <sup>(2)</sup> |  |

| 4Dh                | 00h                |  |

| 4Eh                | 00h                |  |

| 4Fh                | 00h                |  |

| SYSCFG             |                    |  |

|                    | gister Space       |  |

| 00h                | 00h                |  |

| 01h                | 00h                |  |

| 02h                | 00                 |  |

| 03h                | 00h                |  |

| 04h                | 00h                |  |

| 05h                | 00h                |  |

| 06h                | 00h                |  |

| 07h                | 00h                |  |

| 08h                | 00h                |  |

| 09h                | 00h                |  |

| 0Ah                | 00h                |  |

| 0Bh                | 00h                |  |

| 0Ch                | 00h                |  |

| 0Dh                | 00h                |  |

| 0Eh                | 00h                |  |

| 0Fh                | 00h                |  |

| 10h                | 00h                |  |

| 11h                | 00h                |  |

| 12h                | 00h                |  |

| 13h                | 80h                |  |

| 14h <sup>(1)</sup> | 80h                |  |

| 15h                | 00h                |  |

| 16h                | 00h                |  |

| 471                | 0.01               |  |

17h

00h

| Loc. | Value |

|------|-------|

| 18h  | 00h   |

| 19h  | 88h   |

| 1Ah  | 00h   |

| 1Bh  | 00h   |

| 1Ch  | 00h   |

| 1Dh  | 00h   |

| 1Eh  | 08h   |

| 1Fh  | 02h   |

| 20h  | 8Ah   |

| 21h  | 01h   |

| 22h  | 00h   |

| 23h  | 00h   |

| 24h  | 00h   |

| 25h  | 00h   |

| 26h  | 00h   |

| 27h  | 06h   |

| 28h  | 00h   |

| 29h  | 00h   |

| 2Ah  | 01h   |

| 2Bh  | 00h   |

| 2Ch  | 00h   |

| 2Dh  | 00h   |

| 2Eh  | 00h   |

| 2Fh  | 00h   |

SYSCFG 14h must be written first followed by PCIDV0 44h[1]. It is important that PCIDV0 44h-47h is always a 32-bit write and in a tight sequence code.

(2) If L2 cache is being used in the system, 4Eh[6] should be set to 1.

#### Table 2 82C578 Fail Safe Boot Values

| Loc. | Value                |

|------|----------------------|

|      | DV1<br>egister Space |

| 00h  | 45h                  |

| 01h  | 10h                  |

| 02h  | 68h                  |

| 03h  | C5h                  |

| 04h  | 07h                  |

| 05h  | 00h                  |

| 06h  | 80h                  |

| 07h  | 02h                  |

| 08h  | 10h                  |

| 09h  | 00h                  |

| 0Ah  | 01h                  |

| 0Bh  | 06h                  |

| 0Ch  | 00                   |

| 0Dh  | 00                   |

| 0Eh  | 00h                  |

| 0Fh  | 00h                  |

| 10h  | 00h                  |

| 11h  | 00h                  |

| 12h  | 00h                  |

| 13h  | 00h                  |

| 14h  | 00h                  |

| 15h  | 00h                  |

| 16h  | 00h                  |

| 17h  | 00h                  |

| 18h  | 00h                  |

| 19h  | 00h                  |

| 1Ah  | 00h                  |

| 1Bh  | 00h                  |

| 1Ch  | 00h                  |

| 1Dh  | 00h                  |

| 1Eh  | 00h                  |

| 1Fh  | 00h                  |

| 20h  | 00h                  |

| 21h  | 00h                  |

| 22h  | 00h                  |

| Loc. | Value |

|------|-------|

| 23h  | 00h   |

| 24h  | 00h   |

| 25h  | 00h   |

| 26h  | 00h   |

| 27h  | 00h   |

| 28h  | 00h   |

| 29h  | 00h   |

| 2Ah  | 00h   |

| 2Bh  | 00h   |

| 2Ch  | 00h   |

| 2Dh  | 00h   |

| 2Eh  | 00h   |

| 2Fh  | 00h   |

| 30h  | 00h   |

| 31h  | 00h   |

| 32h  | 00h   |

| 33h  | 00h   |

| 34h  | 00h   |

| 35h  | 00h   |

| 36h  | 00h   |

| 37h  | 00h   |

| 38h  | 00h   |

| 39h  | 00h   |

| 3Ah  | 00h   |

| 3Bh  | 00h   |

| 3Ch  | 00h   |

| 3Dh  | 00h   |

| 3Eh  | 00h   |

| 3Fh  | 00h   |

| 40h  | 00h   |

| 41h  | 00h   |

| 42h  | 00h   |

| 43h  | 00h   |

| 44h  | 00h   |

| 45h  | 00h   |

| 46h  | 06h   |

| 47h  | 00h   |

| Loc.                         | Value |

|------------------------------|-------|

| 48h                          | 00h   |

| 49h                          | 00h   |

| 4Ah                          | 00h   |

| 4Bh                          | 00h   |

| 4Ch                          | 00h   |

| 4Dh                          | 00h   |

| 4Eh                          | 00h   |

| 4Fh                          | 00h   |

| 50h                          | 00h   |

| 51h                          | 00h   |

| 52h                          | 00h   |

| 53h                          | 00h   |

| 54h                          | 00h   |

| 55h                          | 02h   |

| 56h                          | 00h   |

| 57h                          | 00h   |

| 58h                          | 00h   |

| 59h                          | 00h   |

| 5Ah                          | 00h   |

| 5Bh                          | 00h   |

| 5Ch                          | 00h   |

| 5Dh                          | 00h   |

| 5Eh                          | 00h   |

| 5Fh                          | C0h   |

| 60h                          | 00h   |

| 61h                          | 00h   |

| 62h                          | 00h   |

| 63h-FCh                      | 00h   |

| FDh                          | xxh   |

| FEh                          | xxh   |

| FFh                          | xxh   |

| SYSCFG<br>Pwr Mgmt Registers |       |

| E0h                          | 00h   |

| E1h                          | 00h   |

| E2h                          | 00h   |

| E3h                          | 00h   |

|                              |       |

| Loc. | Value |

|------|-------|

| E4h  | 00h   |

| E5h  | 00h   |

| E6h  | 00h   |

| E7h  | 00h   |

| E8h  | 00h   |

| E9h  | 00h   |

| EAh  | 01h   |

| EBh  | 01h   |

| ECh  | 01h   |

| EDh  | 00h   |

| EEh  | 00h   |

| EFh  | 00h   |

| F0h  | 00h   |

| F1h  | 00h   |

| F2h  | 00h   |

| F3h  | 00h   |

| F4h  | 00h   |

| F5h  | 00h   |

| F6h  | 00h   |

| F7h  | 00h   |

| F8h  | 00h   |

| F9h  | 00h   |

| FAh  | 00h   |

| FBh  | 00h   |

| FCh  | 00h   |

| FDh  | 00h   |

| FEh  | 00h   |

| FFh  | 10h   |

### Table 3 Register Boot Values without Deep Buffers

| Loc. | Value                              |  |

|------|------------------------------------|--|

|      | SYSCFG<br>Sys Cntrl Register Space |  |

| 00h  | 00h                                |  |

| 01h  | DDh                                |  |

| 02h  | 03h                                |  |

| 03h  | EEh                                |  |

| 04h  | 05h                                |  |

| 05h  | 00h                                |  |

| 06h  | 15h                                |  |

| 07h  | xxh                                |  |

| 08h  | 6Ah                                |  |

| 09h  | 00h                                |  |

| 0Ah  | 00h                                |  |

| 0Bh  | 00h                                |  |

| 0Ch  | 40h                                |  |

| 0Dh  | 02h                                |  |

| 0Eh  | 43h                                |  |

| 0Fh  | 24h                                |  |

| 10h  | 83h                                |  |

| 11h  | 08h                                |  |

| 12h  | 00h                                |  |

| 13h  | 83h                                |  |

| 14h  | 80h                                |  |

| 15h  | A1h                                |  |

| 16h  | A4h                                |  |

| 17h  | 02h                                |  |

| 18h  | 50h                                |  |

| 19h  | 00h                                |  |

| 1Ah  | 00h                                |  |

| 1Bh  | 00h                                |  |

| 1Ch  | 00h                                |  |

| 1Dh  | 20h                                |  |

| 1Eh  | CCh                                |  |

| 1Fh  | 02h                                |  |

| 20h  | 8Fh                                |  |

| 21h  | 03h                                |  |

|               | Leep Barro    |

|---------------|---------------|

| Loc.          | Value         |

| 22h           | 00h           |

| 23h           | 06h           |

| 24h           | 00h           |

| 25h           | 00h           |

| 26h           | 00h           |

| 27h           | 00h           |

| 28h           | 00h           |

| 29h           | 00h           |

| 2Ah           | 01h           |

| 2Bh           | 00h           |

| 2Ch           | 00h           |

| 2Dh           | 00h           |

| 2Eh           | 40h           |

| 2Fh           | 00h           |

| PCI           | DV0           |

| PCI Config Re | egister Space |

| 80000000h     | C5691045h     |

| 80000004h     | 02800007h     |

| 8000008h      | 06000010h     |

| 8000000Ch     | 00000000h     |

| 80000010h     | 00000000h     |

| 80000014h     | 00000000h     |

| 80000018h     | 00000000h     |

| 8000001Ch     | 00000000h     |

| 80000020h     | 00000000h     |

| 80000024h     | 00000000h     |

| 80000028h     | 00000000h     |

| 8000002Ch     | 00000000h     |

| 80000030h     | 00000000h     |

| 80000034h     | 00000000h     |

| 80000038h     | 00000000h     |

| 8000003Ch     | 00000000h     |

| 80000040h     | 20000000h     |

| 80000044h     | 0000007h      |

| 80000048h     | 00000000h     |

| 8000004Ch     | 00000000h     |

| Loc.         | Value         |

|--------------|---------------|

| 80000050h    | 00000000h     |

| 80000054h    | 00000000h     |

| 80000058h    | 00000000h     |

| 8000005Ch    | 00000000h     |

| 80000060h    | 00000000h     |

| 80000064h    | 00000000h     |

| 8000068h     | 00000000h     |

| 8000006Ch    | 00000000h     |

| 80000070h    | 00000000h     |

| 80000074h    | 00000000h     |

| 80000078h    | 00000000h     |

| 8000007Ch    | 00000000h     |

| PCI          | DV1           |

| PCI Config R | egister Space |

| 80000800h    | C5681045h     |

| 80000804h    | 92800107h     |

| 80000808h    | 06010010h     |

| 8000080ch    | 00800000h     |

| 80000810h    | 00000000h     |

| 80000814h    | 00000000h     |

| 80000818h    | 00000000h     |

| 8000081Ch    | 00000000h     |

| 80000820h    | 00000000h     |

| 80000824h    | 00000000h     |

| 80000828h    | 00000000h     |

| 8000082Ch    | 00000000h     |

| 80000830h    | 00000000h     |

| 80000834h    | 00000000h     |

| 80000838h    | 00000000h     |

| 8000083Ch    | 00000000h     |

| 80000840h    | 20000000h     |

| 80000844h    | 40060001h     |

| 80000848h    | C0000000h     |

| 8000084Ch    | 40000000h     |

| 80000850h    | 0004C000h     |

| 80000854h    | 000000D0h     |

| Loc.      | Value     |

|-----------|-----------|

| 80000858h | 00000000h |

| 8000085Ch | 00000000h |

| 80000860h | 00000000h |

| 80000864h | 00000000h |

| 80000868h | 00000000h |

| 8000086Ch | 00000000h |

| 80000870h | 00000000h |

| 80000874h | 00000000h |

| 80000878h | 00000000h |

| 8000087Ch | 00000000h |

#### Table 4 Register Boot Values with Deep Buffers

| Loc.                | Value               |

|---------------------|---------------------|

| SYS<br>Sys Cntrl Re | CFG<br>gister Space |

| 00h                 | 00h                 |

| 01h                 | DDh                 |

| 02h                 | 03h                 |

| 03h                 | EEh                 |

| 04h                 | 05h                 |

| 05h                 | 00h                 |

| 06h                 | 15h                 |

| 07h                 | xxh                 |

| 08h                 | 6Ah                 |

| 09h                 | 00h                 |

| 0Ah                 | 00h                 |

| 0Bh                 | 00h                 |

| 0Ch                 | 40h                 |

| 0Dh                 | 02h                 |

| 0Eh                 | 43h                 |

| 0Fh                 | 24h                 |

| 10h                 | 83h                 |

| 11h                 | 08h                 |

| 12h                 | 00h                 |

| 13h                 | 83h                 |

| 14h                 | 80h                 |

| 15h                 | A1h                 |

| 16h                 | A4h                 |

| 17h                 | 02h                 |

| 18h                 | 50h                 |

| 19h                 | 00h                 |

| 1Ah                 | 00h                 |

| 1Bh                 | 00h                 |

| 1Ch                 | 00h                 |

| 1Dh                 | 20h                 |

| 1Eh                 | CCh                 |

| 1Fh                 | 02h                 |

| l                   |                     |

| lues with De                                                                                                                                                                           | ep Dulleis                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Loc.                                                                                                                                                                                   | Value                                                                                                                                                                                                                                                                                                                                                                                              |

| 20h                                                                                                                                                                                    | 8Fh                                                                                                                                                                                                                                                                                                                                                                                                |

| 21h                                                                                                                                                                                    | 03h                                                                                                                                                                                                                                                                                                                                                                                                |

| 22h                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 23h                                                                                                                                                                                    | 06h                                                                                                                                                                                                                                                                                                                                                                                                |

| 24h                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 25h                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 26h                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 27h                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 28h                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 29h                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 2Ah                                                                                                                                                                                    | 0Dh                                                                                                                                                                                                                                                                                                                                                                                                |

| 2Bh                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 2Ch                                                                                                                                                                                    | 21h                                                                                                                                                                                                                                                                                                                                                                                                |

| 2Dh                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

| 2Eh                                                                                                                                                                                    | 48h                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2Fh                                                                                                                                                                                    | 00h                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                        | DV0                                                                                                                                                                                                                                                                                                                                                                                                |

| PCI                                                                                                                                                                                    | DV0                                                                                                                                                                                                                                                                                                                                                                                                |

| PCII<br>PCI Config Re                                                                                                                                                                  | DV0<br>egister Space                                                                                                                                                                                                                                                                                                                                                                               |

| PCII<br>PCI Config Re<br>80000000h                                                                                                                                                     | DV0<br>egister Space<br>C5691045h                                                                                                                                                                                                                                                                                                                                                                  |

| PCII<br>PCI Config Re<br>80000000h<br>80000004h                                                                                                                                        | <b>DV0</b><br>egister Space<br>C5691045h<br>02800007h                                                                                                                                                                                                                                                                                                                                              |

| PCI<br>PCI Config Rd<br>80000000h<br>80000004h<br>80000008h                                                                                                                            | DV0<br>egister Space<br>C5691045h<br>02800007h<br>06000010h                                                                                                                                                                                                                                                                                                                                        |

| PCI<br>PCI Config Re<br>80000000h<br>80000004h<br>80000008h<br>8000000Ch                                                                                                               | DV0<br>egister Space<br>C5691045h<br>02800007h<br>06000010h<br>00000000h                                                                                                                                                                                                                                                                                                                           |

| PCI<br>PCI Config Rd<br>80000000h<br>80000004h<br>80000008h<br>8000000Ch<br>80000010h                                                                                                  | DV0<br>egister Space<br>C5691045h<br>02800007h<br>06000010h<br>00000000h<br>00000000h                                                                                                                                                                                                                                                                                                              |

| PCI<br>PCI Config Re<br>80000000h<br>80000008h<br>80000000Ch<br>80000010h<br>80000014h                                                                                                 | DV0<br>egister Space<br>C5691045h<br>02800007h<br>06000010h<br>00000000h<br>00000000h                                                                                                                                                                                                                                                                                                              |

| PCI<br>PCI Config Rd<br>80000000h<br>80000004h<br>800000008h<br>80000000Ch<br>80000010h<br>80000014h<br>80000018h                                                                      | DV0<br>egister Space<br>C5691045h<br>02800007h<br>06000010h<br>00000000h<br>00000000h<br>0000000h                                                                                                                                                                                                                                                                                                  |

| PCI<br>PCI Config Re<br>80000000h<br>80000008h<br>80000008h<br>800000000                                                                                                               | DV0           Degister Space           C5691045h           02800007h           06000010h           00000000h           00000000h           00000000h           00000000h           00000000h           00000000h           00000000h                                                                                                                                                               |

| PCI<br>PCI Config Rd<br>80000000h<br>80000004h<br>800000000h<br>80000010h<br>80000010h<br>80000014h<br>80000018h<br>8000001Ch<br>80000020h                                             | DV0           egister Space           C5691045h           02800007h           06000010h           00000000h           00000000h           00000000h           00000000h           00000000h           00000000h           00000000h           00000000h           00000000h                                                                                                                        |

| PCII<br>PCI Config Rd<br>80000000h<br>80000008h<br>8000000Ch<br>80000010h<br>80000014h<br>80000018h<br>8000001Ch<br>80000020h<br>80000024h                                             | DV0           egister Space           C5691045h           02800007h           06000010h           00000000h                                                                                                    |

| PCI<br>PCI Config Re<br>80000000h<br>80000004h<br>800000000<br>80000010h<br>80000010h<br>80000014h<br>80000018h<br>80000010h<br>80000020h<br>80000020h<br>80000028h                    | DV0           gister Space           C5691045h           02800007h           06000010h           00000000h                                         |

| PCII<br>PCI Config Rd<br>80000000h<br>80000004h<br>800000000h<br>80000010h<br>80000014h<br>80000018h<br>8000001Ch<br>80000020h<br>80000024h<br>80000028h<br>8000002Ch                  | DV0           gister Space           C5691045h           02800007h           06000010h           00000000h           00000000h |

| PCI Config Re<br>80000000h<br>80000004h<br>80000008h<br>8000000Ch<br>80000010h<br>80000014h<br>80000014h<br>80000018h<br>8000001Ch<br>80000020h<br>80000020h<br>8000002Ch<br>8000002Ch | DV0           gister Space           C5691045h           02800007h           06000010h           00000000h           00000000h |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                       |                                                                                                                                              |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Loc.                                                                                                                                                                                  | Value                                                                                                                                        |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000040h                                                                                                                                                                             | 20000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000044h                                                                                                                                                                             | 20003071h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000048h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8000004Ch                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000050h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000054h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000058h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8000005Ch                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000060h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000064h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000068h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8000006Ch                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000070h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000074h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80000078h                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8000007Ch                                                                                                                                                                             | 00000000h                                                                                                                                    |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCIDV1<br>PCI Config Register Space                                                                                                                                                   |                                                                                                                                              |  |  |  |  |  |

| e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                     |                                                                                                                                              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                     |                                                                                                                                              |  |  |  |  |  |

| h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PCI Config R                                                                                                                                                                          | egister Space                                                                                                                                |  |  |  |  |  |

| h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PCI Config R<br>80000800h                                                                                                                                                             | C5681045h                                                                                                                                    |  |  |  |  |  |

| h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PCI Config R<br>80000800h<br>80000804h                                                                                                                                                | egister Space<br>C5681045h<br>92800107h                                                                                                      |  |  |  |  |  |

| h<br>h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PCI Config R<br>80000800h<br>80000804h<br>80000808h                                                                                                                                   | egister Space<br>C5681045h<br>92800107h<br>06010010h                                                                                         |  |  |  |  |  |

| h<br>h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PCI Config R<br>80000800h<br>80000804h<br>80000808h<br>8000080Ch                                                                                                                      | egister Space<br>C5681045h<br>92800107h<br>06010010h<br>00800000h                                                                            |  |  |  |  |  |

| h<br>h<br>h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PCI Config R<br>80000800h<br>80000804h<br>80000808h<br>8000080Ch<br>80000810h                                                                                                         | egister Space<br>C5681045h<br>92800107h<br>06010010h<br>00800000h<br>00000000h                                                               |  |  |  |  |  |

| h<br>h<br>h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PCI Config R<br>80000800h<br>80000804h<br>80000808h<br>8000080Ch<br>80000810h<br>80000814h                                                                                            | egister Space<br>C5681045h<br>92800107h<br>06010010h<br>00800000h<br>00000000h                                                               |  |  |  |  |  |

| h<br>h<br>h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PCI Config R<br>80000800h<br>80000808h<br>80000808h<br>8000080Ch<br>80000810h<br>80000814h<br>80000818h                                                                               | egister Space<br>C5681045h<br>92800107h<br>06010010h<br>00800000h<br>00000000h<br>00000000h                                                  |  |  |  |  |  |

| h<br>h<br>h<br>h<br>h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PCI Config R<br>80000800h<br>80000804h<br>80000808h<br>8000080Ch<br>80000810h<br>80000814h<br>80000818h<br>8000081Ch                                                                  | egister Space<br>C5681045h<br>92800107h<br>06010010h<br>00800000h<br>00000000h<br>0000000h<br>0000000h                                       |  |  |  |  |  |