# ALADDIN<sup>-</sup>PRO II

M1621

North Bridge

Version 1.11

Please contact ALi applications deptment at 408-467-7456 to verify that all information is current before beginning a design using this datasheet.

# M1621 : AGP, PCI and Memory Controller

#### Section 1.0 : Features

#### **Processor Support**

- Supports Pentium II<sup>TM</sup> processors. Host bus frequency can be either 66 or 100MHz

- 64 bit data bus and 32 bit addressing

- Optimum buffer design for CPU to memory write

- Optimum buffer design for CPU to memory read

### **Memory Support**

- Supports FPM/EDO/Synchronized DRAMs

- Supports mixture of SDRAM, EDO and Fast Page Mode DRAMs

- Supports symmetrical and asymmetrical DRAM addressing

- Supports 4, 16, 64, 128, 256Mbit DRAMs

- Maximum memory size : 2GB

- Supports ECC, single bit error correct, and multiple bits error detection

- 64 bit data bus and additional 8 bit ECC protection

- Total of 8 RAS and 8 CAS lines available

- Supports 640K to 1MB address range shadowing

- x-1-1-1-1-1-1 back-to-back SDRAM page hit

- x-2-2-2-2-2-2 back-to-back EDO DRAM page hit

- CAS before RAS and self refresh for SDRAM

- CAS before RAS refresh for FPM and EDO DRAMs

- Pipelined DRAM cycle control with hidden precharge

- Supports optional SMI memory address remapping and protection

- Supports LVTTL signal level

#### **Power Management**

- Power plane design supports the following dark green power management function

- 1. Power on Suspend

- 2. Suspend to DRAM

- 3. Suspend to Disk

- 4. PCI bus CLKRUN

- 5. Dynamic Clock Stop

## AGP Support

- AGP specification 1.0 compliant

- 66 MHz PCI bus protocol support

- Supports up to 128 entries table look aside buffer for GART

- 1x/2x mode support

- 28 entries of request queue

- 32 QUAD words of read buffer

- 16 QUAD words of write buffer

### **PCI Bus Support**

- Supports synchronous clock mode between processor bus and PCI bus

- 32-bit Address/Data PCI bus using PCI bus driver technology

- Supports up to 5 PCI masters excluding the M1621 and PCI-to-ISA bridge

- Parity protection on all PCI bus signals

- Fully supports PCI Configuration Space Enable (CSE) protocol

- Fully compliant with PCI Rev. 2.1

- Supports delayed transaction

- Dynamic memory prefetch algorithm and programmable post write flush algorithm

- Data Collection/Write assembly of line bursts

- Supports concurrent PCI bus burst transfer at zero wait-state

- More than 100 MBps data streaming for PCI bus to DRAM access with minimum latency

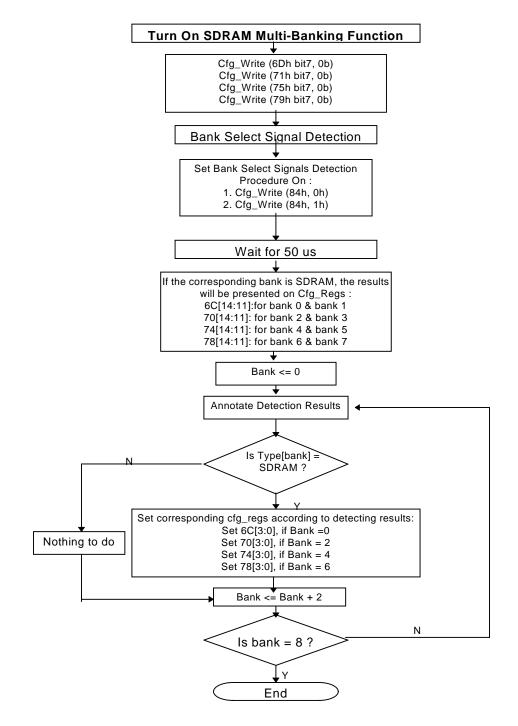

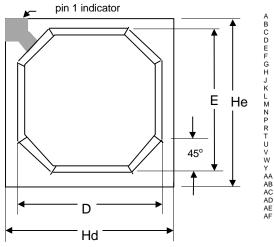

#### Packaging

476 pin BGA package

#### Others

Supports NAND-TREE scan function

# Table of Contents :

| ection 1 : Features                                      | 1   |

|----------------------------------------------------------|-----|

| 1.1 Introduction                                         |     |

| 1.2 System Architecture                                  |     |

| ection 2 : Pin Description                               | 7   |

| 2.1 Pin Diagram                                          | 8   |

| 2.2 Pin Description Table                                | 10  |

| 2.3 NAND Tree Scan List                                  |     |

| 2.4 Numerical Pin List                                   | 17  |

| 2.5 Alphabetical Pin List                                | 22  |

| ection 3 : Functional Description                        | 29  |

| 3.1 System Memory Features                               | 29  |

| 3.2 SDRAM Performance Summary                            |     |

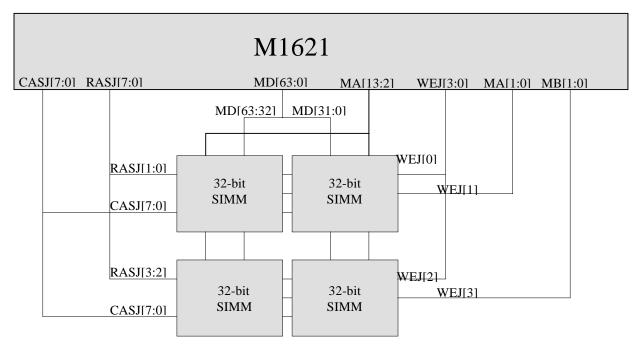

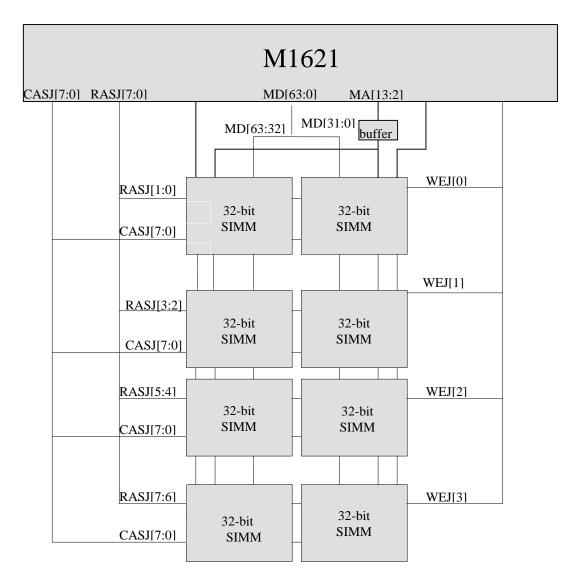

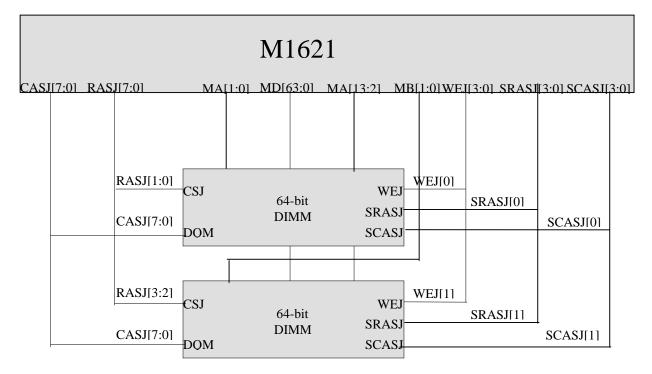

| 3.3 Connection between SIMM and M1621                    | 36  |

| ection 4 : Configuration Registers                       | 39  |

| ection 5 : Hardware Setup and Software Programming Guide | 100 |

| 5.1 Hardware Setup Table                                 | 100 |

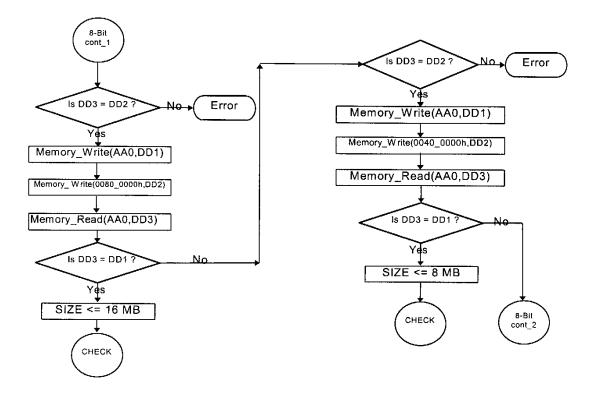

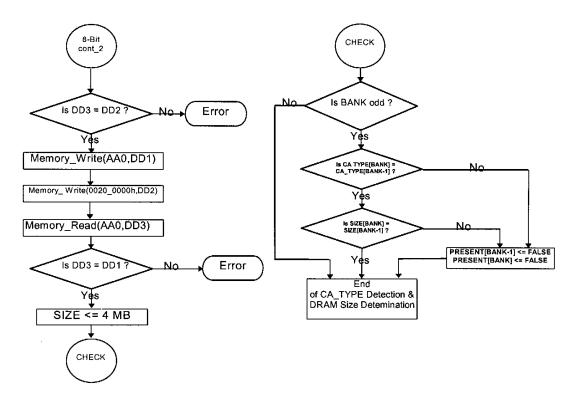

| 5.2 Software Programming Guide                           |     |

| ection 6 : Packaging Information                         | 121 |

| ection 7 : Revision History                              | 122 |

1.1 Introduction

#### 1.1.1 Aladdin Pro family

Aladdin Pro II is a new generation Pentium II system chip set which continuously supports cost effective PC solutions. Aladdin Pro II consists of two BGA packed chips, the M1621 and M1543C. However, the M1621 can also work with M1533, and M1543. The M1621 is an AGP, PCI and memory controller and a data path with multiport buffers for data acceleration. Aladdin Pro II supports the Pentium II processor interface. The M1533, M1543 or M1543C is a PCI to ISA bus bridge, it provides full PCI and ISA compatible functions for different market applications.

#### 1.1.2 PCI to ISA bridge

The M1533, M1543 and M1543C are all 328 pin BGA packaging design. The M1533 integrates power management unit, ACPI, deep green function, 2-channel dedicated Ultra-33 IDE master controller, 2-port USB controller, SMBus controller, and PS2 Keyboard/Mouse controller. The configuration of M1621/M1533 provides the user a high performance, efficient power management solution to meet notebook system requirements. Refer to the M1533 data sheet for detailed specifications.

The M1543 integrates ACPI, green function, 2-channel Ultra-33 IDE master controller, 2-port USB controller, SMBus controller, PS/2 keyboard/mouse controller and super I/O (floppy disk controller, 2 serial port/1 parallel port). In addition to the functions of the M1543 provided, the M1543C also integrates FIR functionality. The configuration of M1621/M1543 or M1621/M1543C provides the user a high performance, low cost solution for desktop systems. Refer to the M1543 or M1543C datasheet for detailed specifications.

### 1.1.3 CPU interface

The M1621 supports the Intel Pentium II processor. The processor bus supports either 66 or 100 MHz.

#### 1.1.4 Main memory size

The M1621 can support up to 2GB FPM, EDO, or SDRAM main memory. Refer to Memory Row Register to select DRAM type, row existence status, bank size, and timing information.

#### 1.1.5 Throughput improvement

Aladdin Pro II employs various techniques to improve the memory and I/O throughput to match up with the advanced super-scalar, super-pipelined Pentium II processors. On the memory subsystem side, the processor data bus utilization is minimized. The pipelined memory cycle design helps hidden pre-charge latency and refresh cycles. Different configurations optimize the performance for a wide range of memory configurations. On the I/O subsystem side, deep data- in/out buffers shadow the latency for both PCI device initiated master reads and writes. Programmable data-in buffer management policy for post write cycles can be tuned to maximize the PCI to memory transfer rate for different memory configurations and PCI device characteristics.

#### 1.1.6 ECC function over memory bus

Reliability and performance are the keys to a high quality PC design. They are also the major targets of the Aladdin Pro design for Pentium II processors. To reach this goal, 8 bit ECC protection over the 64 bit memory data bus is provided. The ECC can perform single bit error correction and multiple bit error detection.

### 1.1.7 PCI 2.1 Compliant

The M1621 is fully compliant to PCI 2.1 specification. With flexible PCI latency control, the M1621 can be adjusted to achieve the best system performance.

#### 1.1.8 PCI arbiter

The M1621 integrates an enhanced PCI arbiter which executes a fair arbitration by using a PCI and CPU time slice mechanism. In addition to itself and the PCI to ISA bridge, the M1621 can support up to 5 PCI masters. According to the PCI specifications, it is possible to support more PCI masters depending on the layout arrangement, impedance load, and the quality of motherboard.

#### 1.1.9 Power Management Design

To support the dark green power management function such as Power on Suspend, Suspend to DRAM, Suspend to Disk, PCI bus CLKRUN and Dynamic Clock Stop, three main power planes are implemented in the M1621. They are processor power plane, PCI and AGP power plane and main memory power plane. Each power plane has its own power source and is isolated from other power planes. To support the suspend mode, the main memory power plane is further divided into two sub-power planes. The power management design provides the desktop and notebook designs the most flexible green function available.

#### 1.1.10 Accelerated Graphics Port

The M1621 supports the Accelerated Graphics Port (AGP or A.G.P.) 1.0 specifications. The AGP is a high performance, component level interconnect targeted at 3D graphical display applications. The AGP interface of the M1621 uses the 66MHz PCI specifications as an operational baseline and provides three significant performance enhancements to the PCI specifications. These enhancements are :

- Deeply pipelined memory read and write operations, fully hiding memory access latency.

- De-multiplexing of address and data on the bus, allowing almost 100% bus efficiency.

- AC timing for 133MHz data transfer rate, allowing almost 100% bus efficiency.

## 1.2 System Architecture

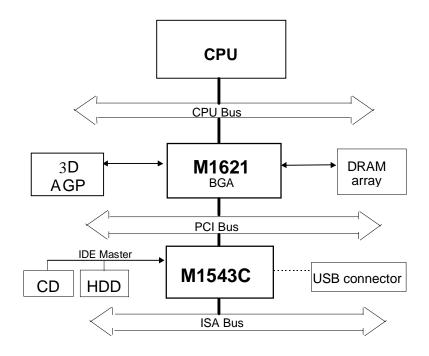

M1621/M1543C System Block Diagram

## **Section 2 : Pin Signal Description**

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface. The "J" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level.

The following notations are used to describe the signal and type

| I     | Input pin                          |

|-------|------------------------------------|

| 0     | Output pin                         |

| O/tri | Output with tri-state pin          |

| I/O   | Bi-directional pin                 |

| PCI   | PCI bus interface signals          |

| AGP   | AGP bus interface signals          |

| LVTTL | Low voltage TTL compatible signals |

| GND   | Ground                             |

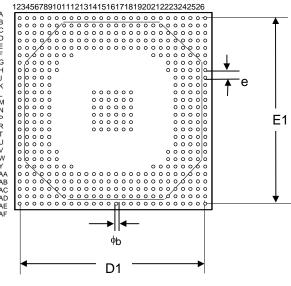

## 2.1 Pin Diagram

|    | 1           | 2            | 3       | 4         | 5       | 6        | 7       | 8       | 9       | 10           | 11    | 12        | 13     | 14        | 15    | 16     | 17      | 18         | 19       | 20       | 21      | 22      | 23         | 24            | 25        | 26         |

|----|-------------|--------------|---------|-----------|---------|----------|---------|---------|---------|--------------|-------|-----------|--------|-----------|-------|--------|---------|------------|----------|----------|---------|---------|------------|---------------|-----------|------------|

| Α  | AD 20       | AD 21        | AD 22   | AD 24     | AD 27   | AD<br>31 | PREQJ 1 | PREQJ 3 | HD 62   | HD 58        | HD 61 | HD 60     | HD 59  | HD 51     | HD 42 | HD 36  | HD 37   | HD 28      | HD 26    | HD 24    | HD 18   | HD 13   | HD 6       | HD 4          | GTL-REF 0 | HD 1       |

| в  | AD 17       | AD 18        | AD 19   | CBEJ 3    | AD 26   | AD<br>30 | PGNTJ 0 | PGNTJ 2 | PGNTJ 4 | HD 63        | HD 55 | GTL-REF 3 | HD 48  | HD 41     | HD 44 | HD 40  | HD 38   | HD 35      | HD 30    | HD 22    | HD 21   | HD 15   | HD 9       | HD 2          | HD 0      | HA 29      |

| с  | FRAM EJ     | CBEJ 2       | AD 16   | AD 23     | AD 25   | AD<br>29 | PREQJ 0 | PREQJ 2 | PREQJ 4 | HCLK_SEL1    | HD 56 | HD 54     | HD 46  | GTL-REF 2 | HD 45 | HD 34  | HD 32   | HD 31      | HD 25    | HD 19    | HD 20   | HD 11   | HD 8       | HD 5          | HD 3      | HA 30      |

| D  | DEV SELJ    | STOP J       | PLOC KJ | PTRD YJ   | IRDY J  | AD 28    | RES ETJ | PGNTJ 1 | PGNTJ 3 | Reserved     | HD 50 | HD 53     | HD 52  | HD 47     | HD 39 | HD 43  | HD 33   | HD 29      | HD 27    | HD 23    | HD 17   | HD 10   | HD 14      | CPU RSTJ      | BREQJO    | HA 26      |

| Е  | SERR J      | PAR          | CBEJ 1  | AD 15     | VCCP    | VCCP     | GND     | GND     | GND     | GND          | GND   | HD 57     | HD 49  | VCCHP     | VCCHP | GND    | GND     | GND        | VCCHP    | HD 16    | GND     | GND     | HA 24      | GTL-<br>REF 1 | HA 31     | HA 28      |

| F  | AD 14       | AD 13        | AD 12   | AD 11     | AD 10   | VCC      | VCCP    | GND     |         |              |       |           |        |           |       | •      |         |            | VCCHP    | GND      | GND     | GND     | HD 7       |               | HA 22     | HA 20      |

| G  | AD 9        | AD 8         | CBEJ    | AD 7      | GND     | GND      |         |         |         |              |       |           | M1     | 621       |       |        |         |            |          |          | GND     | NC      | HD 12      | HA 21         | HA 23     | HA 25      |

| н  | AD 6        | AD 5         | AD 4    | PHLD AJ   | GND     | GND      |         |         |         |              |       |           | Тор    | View      |       |        |         |            |          |          | GND     | HA 19   | HA 15      | HA 17         | HA 18     | HA 11      |

| J  | AD 3        | AD 2         | AD 1    | PCI CLK   | GND     |          |         |         |         |              |       |           | -      |           |       |        |         |            |          |          |         | VCCHP   | HA 16      | HA 13         | HA 12     | HA 8       |

| к  | AD 0        | GREQ J       | GGNT J  | PHLD J    | RATI OJ |          |         |         |         |              |       |           |        |           |       |        |         |            |          |          |         | GND     | HA 14      | HA 7          | HA 10     | BNRJ       |

| L  | ST 0        | ST 1         | ST 2    | A REQJ    | VCCP    |          |         |         |         |              | GND   | GND       | GND    | GND       | GND   | GND    |         |            |          |          |         | H VDDA  | HA 5       | НА З          | HREQ J0   | HREQ J1    |

| м  | RBF J       | PIPE J       | SBA 0   | SBA 1     | VCC5V   |          |         |         |         |              | GND   | GND       | GND    | GND       | GND   | GND    |         |            |          |          |         | HA 6    | HA 9       | BPRI J        | HA 4      | HREQ<br>J4 |

| N  | SBA 2       | AGP-REF      | SBA 3   | SB-STB    | SBA 4   |          |         |         |         |              | GND   | GND       | GND    | GND       | GND   | GND    |         |            |          |          |         | TRDYJ   | DEFE RJ    | LOCKJ         | DRDY J    | HREQ J2    |

| Р  | SBA 5       | SBA 6        | SBA 7   | GAD 31    | GAD 30  |          |         |         |         |              | GND   | GND       | GND    | GND       | GND   | GND    |         |            |          |          |         | HGNDA   | RSJ 0      | HREQ J3       | HITM J    | HITJ       |

| R  | GAD 29      | GAD 28       | GAD 27  | GAD 26    | AVDDA   |          |         |         |         |              | GND   | GND       | GND    | GND       | GND   | GND    |         |            |          |          |         | VCCP L3 | RSJ 2      | DBSY J        | RSJ 1     | ADSJ       |

| т  | GAD 25      | GAD 24       | AD-STB1 | GCBE J3   | AGNDA   |          |         |         |         |              | GND   | GND       | GND    | GND       | GND   | GND    |         |            |          |          |         | HCLK    | MD 1       | TEST IN       | MD 32     | MD 0       |

| U  | GAD 23      | GAD 22       | GAD 21  | GAD 20    | VCC PL1 |          |         |         |         |              |       |           |        |           |       |        |         |            |          |          |         | GND     | MD 3       | MD 34         | MD 2      | MD 33      |

| v  | AGP-REF 1   | GAD 19       | GAD 18  | GCLK O    | GND     |          | I       |         |         |              |       |           |        |           |       |        |         |            |          | I        |         | VCCMP   | MD 5       | MD 36         | MD 4      | MD 35      |

| w  | GAD 17      | GAD 16       | GCBE J2 | GCLK I    | VDD PLL | GND      |         |         |         |              |       |           |        |           |       |        |         |            |          |          | VCCMP   | MD 39   | MD 7       | MD 38         | MD 6      | MD 37      |

| Y  |             |              | GTRD YJ | GDEV SELJ | GND     | VCCP     |         |         | l       |              |       |           |        |           |       |        |         |            |          |          | GND     | MD 10   | MD 41      |               | MD 40     | MD 8       |

| AA | GSTO PJ     | GPAR         | GCBE J1 | GAD 15    | VCCP    | VCC<br>P | GND     | GND     |         |              |       |           |        |           |       | 1      |         |            | VCCMP    | VCCMP    | GND     | GND     | MD 12      | MD 43         | MD 11     | MD 42      |

| AB | GAD 14      | GAD 13       | GAD 12  | GAD 11    | VCCP    | GND      | GND     | GND     | VCC_SP  | VCC5V_S<br>P | MD 50 | MD 48     | D VDDA | DGNDA     | MA 6  | DCLK I | VCCP L2 | GND        | SMI ACKJ | VCCMP    | VCCMP   | GND     | MD 14      | MD<br>45      | MD 13     | MD 44      |

| AC | GAD 10      | AGP-REF<br>0 | GAD 9   | GAD 8     | MD 62   | MD 60    | MD 58   | MD 56   | MD 54   | MD 52        | MD 18 | MD 16     | CASJ 2 | MA 11     | MA 7  | MA 2   | CLK 32K | DCLK O     | CKE      | SUSPENDJ | REF ENV | CASJ 4  | SCAS J2    | MD<br>47      | MD 15     | MD 46      |

| AD | AD-<br>STB0 | GAD 7        | GAD 6   | GCBE J0   | MD 30   | MD 28    | MD 26   | MD 24   | MD 22   | MD 20        | MDP 7 | MDP 2     | CASJ 6 | MA 12     | MA 8  | MA 3   | MB 1    | SRASJ<br>1 | RASJ 0   | RASJ 3   | RASJ 6  | CASJ 1  | SCAS<br>J1 | MWE<br>J1     | MDP 5     | MDP 0      |

| AE | GAD 5       | GAD4         | GAD 3   | MD 63     | MD 61   | MD 59    | MD 57   | MD 55   | MD 53   | MD 51        | MD 49 | MDP 6     | CASJ 3 | MA 13     | MA 9  | MA 4   | MA 0    | SRASJ 0    | SRASJ 3  | RASJ 2   | RASJ 5  | CASJ 5  | SCAS J0    | MWE J0        | MWE J3    | MDP 4      |

| AF | GAD 2       | GAD 1        | GAD 0   | MD 31     | MD 29   | MD 27    | MD 25   | MD 23   | MD 21   | MD 19        | MD 17 | MDP 3     | CASJ 7 | MA 14     | MA 10 | MA 5   | MA 1    | MB 0       | SRASJ 2  | RASJ 1   | RASJ 4  | RASJ 7  | CASJ 0     | SCAS J3       | MWE J2    | MDP 1      |

|    | 1           | 2            | 3       | 4         | 5       | 6        | 7       | 8       | 9       | 10           | 11    | 12        | 13     | 14        | 15    | 16     | 17      | 18         | 19       | 20       | 21      | 22      | 23         | 24            | 25        | 26         |

|        | 1           | 2         | 3                 | 4         | 5       | 6        | 7       | 8       | 9          | 10        | 11    | 12        | 13     | 14         | 15    | 16     | 17         | 18     | 19       | 20       | 21      | 22      | 23          | 24               | 25            | 26            |

|--------|-------------|-----------|-------------------|-----------|---------|----------|---------|---------|------------|-----------|-------|-----------|--------|------------|-------|--------|------------|--------|----------|----------|---------|---------|-------------|------------------|---------------|---------------|

| AF     | GAD 2       | GAD 1     | GAD 0             | MD 31     | MD 29   | MD 27    | MD 25   | MD 23   | MD 21      | MD 19     | MD 17 | MDP 3     | CASJ 7 | MA 14      | MA 10 | MA 5   | MA 1       | MB 0   | SRASJ    | RASJ 1   | RASJ 4  | RASJ 7  | CASJ 0      | SCAS             | MWE<br>J2     | MDP 1         |

| AE     | GAD 5       | GAD4      | GAD 3             | MD 63     | MD 61   | MD 59    | MD 57   | MD 55   | MD 53      | MD 51     | MD 49 | MDP 6     | CASJ 3 | MA 13      | MA 9  | MA 4   | MA 0       | SRASJ  | SRASJ    | RASJ 2   | RASJ 5  | CASJ 5  | SCAS        | MWE<br>J0        | MWE<br>J3     | MDP 4         |

| AD     | AD-<br>STB0 | GAD 7     | GAD 6             | GCBE      | MD 30   | MD 28    | MD 26   | MD 24   | MD 22      | MD 20     | MDP 7 | MDP 2     | CASJ 6 | MA 12      | MA 8  | MA 3   | MB 1       | SRASJ  | RASJ 0   | RASJ 3   | RASJ 6  | CASJ 1  | SCAS        | MWE<br>J1        | MDP 5         | MDP 0         |

| AC     | GAD 10      | AGP-REF 0 | GAD 9             | GAD 8     | MD 62   | MD 60    | MD 58   | MD 56   | MD 54      | MD 52     | MD 18 | MD 16     | CASJ 2 | MA 11      | MA 7  | MA 2   | CLK 32K    | DCLK O | CKE      | SUSPENDJ | REF ENV | CASJ 4  | SCAS        |                  | MD 15         | MD 46         |

| AB     | GAD 14      | GAD 13    | GAD 12            | GAD 11    | VCCP    | GND      | GND     | GND     | VCC_SP     | VCC5V_SP  | MD 50 | MD 48     | D      | DGNDA      | MA 6  | DCLK I | VCCP<br>L2 | GND    | SMI ACKJ | VCCMP    | VCCMP   | GND     | J2<br>MD 14 | MD 45            | MD 13         | MD 44         |

| AA     | GSTO PJ     | GPAR      | GCBE J1           | GAD 15    | VCCP    |          | GND     | GND     |            |           |       |           | VDDA   | 1          |       |        |            |        | VCCMP    | VCCMP    | GND     | GND     | MD 12       | MD 43            | MD 11         | MD 42         |

| Y      | GFRA MEJ    | GIRD YJ   | GTRD YJ           | GDEV SELJ | GND     | P<br>VCC |         |         |            |           |       |           | M4     | 621        |       |        |            |        |          |          | GND     | MD 10   | MD 41       | MD 9             | MD 40         | MD 8          |

|        |             |           |                   |           | VDD PLL | Р        |         |         |            |           |       |           |        | 021        |       |        |            |        |          |          |         |         |             |                  |               |               |

| w      |             | GAD 16    | J2                | GCLK I    |         | GND      |         |         |            |           |       |           |        |            |       |        |            |        |          |          | VCCMP   | MD 39   | MD 7        | MD 38            | MD 6          | MD 37         |

| v      | 1           |           | GAD18             | 0         | GND     |          |         |         |            |           |       |           |        |            |       |        |            |        |          |          |         | VCCMP   |             | MD 36            | MD 4          | MD 35         |

| U      |             |           | GAD 21<br>AD-STB1 |           | VCC PL1 |          |         |         |            |           |       |           |        |            |       |        |            |        |          |          |         | GND     | MD 3        | MD 34<br>TEST IN | MD 2<br>MD 32 | MD 33<br>MD 0 |

| T<br>R |             |           | GAD 27            |           | AVDDA   |          |         |         |            |           |       |           | -      | GND<br>GND |       | -      |            |        |          |          |         | VCCP L3 |             | DBSY J           | RSJ 1         | ADSJ          |

| P      |             |           | SBA 7             |           | GAD 30  |          |         |         |            |           |       |           |        | GND        |       |        |            |        |          |          |         | HGNDA   |             | HREQ J3          | нітм ј        | HITJ          |

| N      | SBA 2       | AGP-REF   | SBA 3             | SB-STB    | SBA 4   |          |         |         |            |           |       |           |        | GND        |       |        |            |        |          |          |         | TRDYJ   | DEFE RJ     |                  | DRDY J        | HREQ J2       |

| м      | RBF J       | PIPE J    | SBA 0             | SBA 1     | VCC5V   |          |         |         |            |           | GND   | GND       |        | GND        | GND   | GND    |            |        |          |          |         | HA 6    | HA 9        | J<br>BPRI J      | HA 4          | HREQ J4       |

| L      | ST 0        | ST 1      | ST 2              | A REQJ    | VCCP    |          |         |         |            |           |       |           |        | GND        |       |        |            |        |          |          |         | H VDDA  | HA 5        | HA 3             |               | HREQ J1       |

| к      | AD 0        | GREQ J    | GGNT J            | PHLD J    | RATI OJ |          |         |         |            |           |       |           | -      | _          |       | -      | 1          |        |          |          |         | GND     | HA 14       | HA 7             | HA 10         | BNRJ          |

| J      | AD 3        | AD 2      | AD 1              | PCI CLK   | GND     |          |         |         |            |           |       |           |        |            |       |        |            |        |          |          |         | VCCHP   | HA 16       | HA 13            | HA 12         | HA 8          |

| н      | AD 6        | AD 5      | AD 4              | PHLD AJ   | GND     | GND      |         |         |            |           |       |           |        |            |       |        |            |        |          |          | GND     | HA 19   | HA 15       | HA 17            | HA 18         | HA 11         |

| G      | AD 9        | AD 8      | CBEJ0             | AD 7      | GND     | GND      |         |         | I          |           |       |           |        |            |       |        |            |        |          |          | GND     | NC      | HD 12       | HA 21            | HA 23         | HA 25         |

| F      | AD 14       | AD 13     | AD 12             | AD 11     | AD 10   | VCC<br>P | VCCP    | GND     |            |           |       |           | •      |            |       |        |            |        | VCCHP    | GND      | GND     | GND     | HD 7        | HA 27            | HA 22         | HA 20         |

| Е      | SERR J      | PAR       | CBEJ 1            | AD 15     | VCCP    | VCCP     | GND     | GND     | GND        | GND       | GND   | HD 57     | HD 49  | VCCHP      | VCCHP | GND    | GND        | GND    | VCCHP    | HD 16    | GND     | GND     | HA 24       | GTL-REF 1        | HA 31         | HA 28         |

| D      | DEV SELJ    | STOP J    | PLOC KJ           | PTRD YJ   | IRDY J  |          | RES ETJ | PGNTJ 1 | PGNTJ 3    |           | HD 50 | HD 53     | HD 52  | HD 47      | HD 39 | HD 43  | HD 33      | HD 29  | HD 27    | HD 23    | HD 17   | HD 10   | HD 14       | CPU RSTJ         | BREQJ0        | HA 26         |

| С      |             |           | 1                 |           | AD 25   |          | PREQJ 0 | PREQJ 2 | PREQJ<br>4 | HCLK_SEL1 |       |           |        | GTL-REF 2  |       |        | HD 32      |        |          |          |         |         | HD 8        |                  |               |               |

| в      | AD 17       | AD 18     | AD 19             | CBEJ 3    | AD 26   | AD<br>30 | PGNTJ 0 | PGNTJ 2 | PGNTJ 4    | HD 63     | HD 55 | GTL-REF 3 | HD 48  | HD 41      | HD 44 | HD 40  | HD 38      | HD 35  | HD 30    | HD 22    | HD 21   | HD 15   | HD 9        | HD 2             | HD 0          | HA 29         |

| A      | AD 20       | AD 21     | AD 22             | AD 24     | AD 27   | AD<br>31 | PREQJ 1 | PREQJ 3 | HD 62      | HD 58     | HD 61 | HD 60     | HD 59  | HD 51      | HD 42 | HD 36  | HD 37      | HD 28  | HD 26    | HD 24    | HD 18   | HD 13   | HD 6        | HD 4             | GTL-REF 0     | HD 1          |

|        | 1           | 2         | 3                 | 4         | 5       | 6        | 7       | 8       | 9          | 10        | 11    | 12        | 13     | 14         | 15    | 16     | 17         | 18     | 19       | 20       | 21      | 22      | 23          | 24               | 25            | 26            |

Bottom View (chip rotated top -bottom)

## 2.2 Pin Description Table :

| Name           | Туре | Description                                                                                                                                                                                                                                     |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface | ):   |                                                                                                                                                                                                                                                 |

| BPRIJ          | I/O  | <b>Priority Agent</b> bus request is issued by the high priority bus agent to acquire the request bus. The high priority agent will always be the next bus owner.                                                                               |

| ADSJ           | I/O  | <b>Address Strobe</b> . The address strobe signal is asserted during the first cycle request phase and indicates that address and command signal are valid.                                                                                     |

| LOCKJ          | I/O  | Lock. The LOCKJ signal is asserted for indivisible sequence of transaction.                                                                                                                                                                     |

| HA[31-3]       | I/O  | <b>Request Information</b> . HA[31-3] contain the transaction address on clock cycles with ADSJ asserted. Byte Enable, deferred ID, and additional transaction information are encoded on these lines during the cycle following ADSJ.          |

| HREQJ[4-0]     | I/O  | <b>Request Type</b> . HREQJ[4-0] contain the command on the clock cycle with ADSJ asserted and data size/length information on the next cycle.                                                                                                  |

| BREQJ[0]       | I/O  | Bus Request 0. Asserted at reset to set agent IDs on all processors.                                                                                                                                                                            |

| BNRJ           | I/O  | <b>Block Next Request</b> is asserted by an agent to prevent the request bus owner from issuing further request.                                                                                                                                |

| HITJ           | I/O  | <b>Hit.</b> The bridge will assert HITJ and HITMJ together to extend the snoop window of a transaction targeting its PCI bus. HITJ indicates that a caching agent holds an unmodified version of the requested line.                            |

| HITMJ          | I/O  | <b>Hit Modified</b> . This signal indicates that a caching agent holds a modified version of the requested line and the agent assumes responsibility for providing the line. Also, driven in conjunction with HITMJ to extend the snoop window. |

| DEFERJ         | I/O  | <b>DEFERJ</b> is driven by addressed agent to indicate that the transaction cannot be guaranteed bus completion.                                                                                                                                |

| RSJ[2-0]       | I/O  | RSJ[2-0] encode the response to a request.                                                                                                                                                                                                      |

| TRDYJ          | I/O  | <b>Target Ready</b> is driven by the target of the data to indicate that it is ready to receive data.                                                                                                                                           |

| DRDYJ          | I/O  | <b>Data Ready</b> is driven by the data bus owner for each cycle that contains valid data.<br>DRDYJ is asserted to indicate idle cycle during data phase.                                                                                       |

| DBSYJ          | I/O  | <b>DBSYJ</b> is asserted by the data bus owner to hold the data bus for the next cycle. DBSYJ is not asserted for single cycle transfer.                                                                                                        |

| CPURSTJ        | I/O  | CPU Bus Reset. This signal is used to reset the CPU.                                                                                                                                                                                            |

| HD[63-0]       | I/O  | <b>Host Data</b> : These signals are connected to the CPU data bus. Note that the data signals are inverted on the CPU bus. HD[63] applies to the most significant bit and HD[0] applies to the least significant bit.                          |

| Name                   | Туре         | Description                                                                                                                                                                                                                                                                                                            |

|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM Interfac          | ce :         |                                                                                                                                                                                                                                                                                                                        |

| MA[14-0]               | I/O<br>LVTTL | <b>Memory address</b> , multiplexed row and column memory address. These signals are connected to the address lines of all DRAMs. M1621 supports DRAM types from 256K to 256Mbits.                                                                                                                                     |

| MB[1-0]                | I/O<br>LVTTL | <b>Memory address</b> , multiplexed row and column memory address for DRAM address bit 0,1. These two signals are the copy of MA[1-0].                                                                                                                                                                                 |

| RASJ[7-0]/<br>CSJ[7-0] | I/O<br>LVTTL | <b>Row Address Strobe</b> . Indicates that address on MA[14-0] is the row address for EDO/FPM. There is one RASJ per memory row. When used with the SDRAM, the RASJ is used as chip select, CSJ, of SDRAM. There is one CSJ per memory row. When Index 82h bit4 is set to 1, RASJ[7:6] will become SDRAM CKE function. |

| CASJ[7-0]/<br>DQM[7-0] | I/O<br>LVTTL | <b>Column Address Strobe</b> . Indicates that the address on MA[14-0] is the column address for EDO/FPM. There is one CASJ per memory row. When used with the SDRAM, this is the data mask, DQM, of SDRAM. There is one DQM per memory row.                                                                            |

| SRASJ[3-0]             | I/O<br>LVTTL | <b>SDRAM, Row Address Strobe</b> . SRASJ[3-0] are of same function for sharing loading.<br>They are used to connect SDRAM RASJ. There is one SRASJ per memory bank (two rows). When Index 82h bit4 is set to 1, SRASJ[3] will become SDRAM CKE function.                                                               |

| SCASJ[3-0]             | I/O<br>LVTTL | <b>SDRAM, Column Address Strobe</b> . SCASJ[3-0] are of same function for sharing loading. They are used to connect SDRAM CASJ. There is one SCASJ per memory bank (two rows). When Index 82h bit4 is set to 1, SCASJ[3] will become SDRAM CKE function.                                                               |

| REFENV                 | I/O<br>LVTTL | <b>Refresh Envelope.</b> Indicates refresh period in 5V suspend mode. This signal will cover the whole period of refresh cycle.                                                                                                                                                                                        |

| MWEJ[3-0]              | I/O<br>LVTTL | <b>Write Enable</b> . Indicates that the current memory request is a write. MWEJ[3-0] are the same function to share loading. When Index 82h bit4 is set to 1, MWEJ[3] will become SDRAM CKE function.                                                                                                                 |

| MD[63-0]               | I/O<br>LVTTL | <b>Memory Data.</b> These signals are connected to the DRAM data bus. MD[63] is the most significant bit and MD[0] is the least significant bit.                                                                                                                                                                       |

| MDP[7-0]               | I/O<br>LVTTL | <b>Memory ECC bits.</b> These signals are ECC bits of the DRAM data bus. MDP[7] is the most significant bit and MDP[0] is the least significant bit.                                                                                                                                                                   |

| Name          | Туре       | Description                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| AGP Address   | ing :      |                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| PIPEJ         | I          | <b>Pipeline Request,</b> is asserted by master to indicate a full width request to be en-<br>queued by the target. The master en-queues one request each rising edge of AGP<br>clock while PIPEJ is asserted. When PIPEJ is de-asserted no new requests are en-<br>queued across GAD bus.                                          |  |  |  |  |  |  |  |

| SBA[7-0]      | I/O        | Side band Address port, provides an additional bus to pass address and command to the target from the master.                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| AGP Flow Co   | ntrol :    |                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| RBFJ          | I          | <b>Read Buffer Full</b> , indicated if the master is ready to accept previously requested low priority read data or not. When RBFJ is asserted the arbiter is not allowed to initiate the return of low priority read data to the master.                                                                                          |  |  |  |  |  |  |  |

| ST[2-0]       | I/O        | <b>Status Bus,</b> provides information from the arbiter to a Master on what it may do. Refer to AGP spec. 1.0. for details.                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| AGP Clock Lis | st :       |                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| AD_STB0       | I/O        | <b>AD Bus Strobe 0</b> , provides strobe timing for the 2x data transfer mode on the GAD[15-00]. The agent that is providing data drives this signal.                                                                                                                                                                              |  |  |  |  |  |  |  |

| AD_STB1       | I/O        | <b>AD Bus Strobe 1</b> , provides strobe timing for the 2x data transfer mode on the GAD[31-16]. The agent that is providing data drives this signal.                                                                                                                                                                              |  |  |  |  |  |  |  |

| SB_STB        | I          | Side Band Strobe, provides strobe timing for SBA[7:0] and is always driven by the AGP master.                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| AGP Semanti   | cs PCI Sia |                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| GFRAMEJ       | 1/0        | Not Used by AGP. It remains de-asserted by its own pull up resistor.                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| GIRDYJ        | I/O        | <b>GIRDYJ</b> indicates the AGP compliant master is ready to provide all write data for the current transaction. Once GIRDYJ is asserted for a write operation, the master is not allowed to insert wait states. The assertion of GIRDYJ for read, indicates that the master is ready to transfer a subsequent block of read data. |  |  |  |  |  |  |  |

| GTRDYJ        | I/O        | <b>GTRDYJ</b> indicates the AGP compliant target is ready to provide read data for the entire transaction or is ready to transfer a block of data, when the transfer requires more than four clocks to complete.                                                                                                                   |  |  |  |  |  |  |  |

| GSTOPJ        | I/O        | Not Used by AGP.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| GDEVSELJ      | I/O        | Not Used by AGP.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| GREQJ         |            | GREQJ is used to request access to the bus to initiate a PCI or an AGP request.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| GGNTJ         | I/O        | <b>GGNTJ</b> provides additional information on ST[2:0]. The additional information indicates that the master is the recipient of previously requested read data, it is to provide write data, for a previously en-queued write command or has been given permission to start a bus transaction.                                   |  |  |  |  |  |  |  |

| GAD[31-0]     | I/O        | <b>GAD[31-0]</b> is the multiplexed address and data transfer bus. GAD[31] is the most significant bit and GAD[0] is the least significant bit.                                                                                                                                                                                    |  |  |  |  |  |  |  |

| GCBEJ[3-0]    | I/O        | <b>GCBEJ[3-0]</b> is the multiplexed command and byte enable bus. They also provide command information by the master when requests are being en-queued using PIPEJ. Provides valid byte information during AGP write transactions and is driven by the master.                                                                    |  |  |  |  |  |  |  |

| GPAR          | I/O        | <b>GPAR</b> is parity bit on GAD[31:0] and GCBEJ[3:0].                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Name              | Туре        | Description                                                                                                                                                                                                                                                                                                                                     |

|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Interface     |             |                                                                                                                                                                                                                                                                                                                                                 |

| AD[31-0]          | I/O         | <b>PCI Address and Data.</b> These signals contain the address or data for PCI transaction, and connect to PCI bus.                                                                                                                                                                                                                             |

| CBEJ[3-0]         | I/O         | <b>PCI Bus Command and Byte Enables.</b> These signals contain command during address phase and byte enables during the data phase.                                                                                                                                                                                                             |

| PTRDYJ            | I/O         | <b>PCI Target Ready.</b> This signal is asserted by the target to indicate that it is able to complete the current data transfer. A data transfer occurs if PTRDYJ and IRDYJ are asserted during the rising edge of PCICLK.                                                                                                                     |

| STOPJ             | I/O         | STOPJ is a request from the target to stop the current transaction.                                                                                                                                                                                                                                                                             |

| PLOCKJ            | I/O         | PCI Lock is asserted by the agent requiring exclusive access to target.                                                                                                                                                                                                                                                                         |

| DEVSELJ           | I/O         | <b>Device Select</b> is driven by the device that has decoded its address as the target of the current access.                                                                                                                                                                                                                                  |

| PAR               | I/O         | <b>PCI Parity</b> is driven to even parity across AD[31-0] and CBEJ[3-0] by the master during address and write data phase. The target drives parity during read data phase.                                                                                                                                                                    |

| IRDYJ             | I/O         | <b>PCI Initiator Ready</b> is asserted by the master to indicate that it is able to complete the current data transfer. A data transfer occurs if both PTRDYJ and IRDYJ are asserted during the rising edge of PCICLK.                                                                                                                          |

| FRAMEJ            | I/O         | <b>PCI Frame</b> is driven by a master to indicate the beginning and duration of a transaction.                                                                                                                                                                                                                                                 |

| SERRJ/<br>CLKRUNJ | I/O         | <b>PCI System Error or PCI Clock Run.</b> When Index 5Ch bit0 is reset to 0, SERRJ function is selected. It is pulsed by the M1621 when the programmed error condition happened (like DRAM ECC checking). When Index 5Ch bit0 is set to 1, CLKRUNJ function is selected. CLKRUNJ is for stopping PCI clock during green function.               |

| PCI Side band     | l/Bridge In |                                                                                                                                                                                                                                                                                                                                                 |

| PHLDJ             | 1           | <b>PHLDJ: PCI Hold</b> , this signal comes from the standard bus bridge (South Bridge) to PCI arbiter to request the PCI bus.                                                                                                                                                                                                                   |

| PHLDAJ            | I/O         | <b>PHLDAJ: PCI Hold Acknowledge</b> : this signal is driven by the internal PCI arbiter to grant the PCI bus to the standard bus bridge (South Bridge).                                                                                                                                                                                         |

| PREQJ[4-0]        | 1           | Request: PCI master requests for PCI slots or on board PCI device.                                                                                                                                                                                                                                                                              |

| PGNTJ[4-0]        | I/O         | <b>Grant</b> : Permission is given to the PCI master to use PCI bus. These are inputs when the test mode is enabled. These pins are required to be external pull high.                                                                                                                                                                          |

| HCLK_SEL1         | I/O         | Hardware Setting. Refer to hardware setup section 5.1.                                                                                                                                                                                                                                                                                          |

| AREQJ             | I/O         | Any Request represents bus request of any PCI bus masters. As output, this signal will be asserted by M1621 when any PREQJ[4:0] has been asserted. It is used to connect to south bridge to support ACPI function. As input, it is used to enable/disable host PLL. This signal wakes up system via south for the sake of ACPI circuitry there. |

| Name             | Туре         | Description                                                                                                                                                                                                                                                                                                                 |

|------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLOCK :          |              | · · · ·                                                                                                                                                                                                                                                                                                                     |

| PCICLK           | I<br>LVTTL   | <b>PCI Clock input</b> . The PCI state machine will be based on this clock. It comes from an external clock generator and must lag HCLK 1 ~ 4 ns.                                                                                                                                                                           |

| HCLK             | I<br>LVTTL   | <b>CPU Bus Clock</b> . This is the CPU bus clock input. When the Host PLL is disabled, the M1621 will use this clock for Host and DRAM state machines. When the Host PLL is enabled, this input clock will become the Host PLL reference clock.                                                                             |

| DCLKO            | I/O<br>LVTTL | <b>DIMM Clock Output.</b> When DRAM PLL is enabled, M1621 will drive this clock out for Clock Buffer to generate DIMM clocks.                                                                                                                                                                                               |

| DCLKI            | I/O<br>LVTTL | DRAM Side PLL's Reference Clock. When DRAM PLL is enabled, this input signal must trace the DIMM clock to compensate the clock skew. Refer to the layout design guide.                                                                                                                                                      |

| GCLKO            | I/O<br>LVTTL | <b>AGP CLOCK Output.</b> When AGP PLL is enabled, the M1621 will drive this clock out for AGP slot. The M1621 will automatically determine if the Host bus frequency is 100 MHz or 66 MHz and generate the AGP clock. The M1621 AGP PLL will also generate an internal 133MHz frequency to enhance the 2X mode reliability. |

| GCLKI            | I/O<br>LVTTL | AGP Side PLL's Reference Clock. When AGP PLL is enabled, this clock input is for the PLL reference clock to compensate the layout delay. When AGP PLL is disabled, this clock input is for the AGP state machine clock. This input clock must delay Host clock for 1 ~ 4 ns due to drop specification.                      |

| CLK32K           | I<br>LVTTL   | <b>32KHz Clock</b> for 5 volt suspend DRAM refresh. This signal must be pulled to a fixed value when the suspend feature is disabled.                                                                                                                                                                                       |

| SUSPENDJ         | I/O<br>LVTTL | <b>Suspend</b> request. This request is coming from a south bridge. When actively sampled, the M1621 will enter DRAM suspend refresh state. This signal must be pulled high when the suspend feature is disabled.                                                                                                           |

| CKE              | I/O<br>LVTTL | <b>Clock enable</b> for SDRAM to perform a self refresh cycle. When Index 82h bit4 is set to 1, RASJ[7:6], SRASJ[3], SCASJ[3], and MWEJ[3] will become SDRAM CKE function also. This is the preferred configuration for a 3-DIMM layout.                                                                                    |

| Miscellaneous    | ;:           |                                                                                                                                                                                                                                                                                                                             |

| AGP_REF[2-<br>0] | I/O<br>LVTTL | <b>AGP Bus Reference Voltage.</b> These inputs are used for the AGP pad reference input. System designer must provide a stable 0.4VCCP input for AGP pad to work reliably.                                                                                                                                                  |

| GTL_REF[3-<br>0] | I/O<br>LVTTL | Host bus reference voltage. GTL+ pad will use this voltage for the reference. System designer must provide a stable 1V input for GTL+ pad to work reliably.                                                                                                                                                                 |

| SMIACKJ          | I<br>LVTTL   | <b>Internal Test Mode.</b> This input is used to enable the internal NAND-tree scan function for Group 3, and 4. Refer to section 2.3 for more details. This pin must be pulled high for normal operation.                                                                                                                  |

| TESTIN           | I<br>LVTTL   | <b>Internal Test Mode.</b> This input is used to enable the internal NAND-tree scan function for Group 1,2, 5, and 6. Refer to section 2.3 for more details. This pin must be pulled low for normal operation.                                                                                                              |

| RESETJ           | I<br>LVTTL   | <b>System Reset.</b> This reset is from the system. The M1621 will reset the whole state machine and generate CPURSTJ to the CPU.                                                                                                                                                                                           |

| RATIOJ           | I/O<br>LVTTL | <b>Ratio.</b> The M1621 will use this signal out to external circuitry to add the CPU configuration latch hold time. Refer to the reference circuit.                                                                                                                                                                        |

| Name         | Type  | Description                                                                |

|--------------|-------|----------------------------------------------------------------------------|

| Power & Grou | und : |                                                                            |

| VCC5V        | Р     | Core power, 5V. No power is provided during suspend mode.                  |

| VCC5V_SP     | Р     | Suspend core power, 5V. Provides necessary core power during suspend mode. |

| VCCP         | Р     | PCI and AGP pad power, 3.3V.                                               |

| VCCHP        | Р     | Host pad power, 3.3V.                                                      |

| VCCMP        | Р     | Memory pad power, 3.3V.                                                    |

| VCC_SP       | Р     | Suspend pad power, 3.3V.                                                   |

| VCCPL1       | Р     | AGP PLL pad power, 3.3V.                                                   |

| VCCPL2       | Р     | Memory PLL pad power, 3.3V.                                                |

| VCCPL3       | Р     | Host PLL pad power, 3.3V.                                                  |

| VDDPLL       | Р     | Digital pad power, 3.3V.                                                   |

| AVDDA        | Р     | Analog power of AGP PLL, 3.3V.                                             |

| DVDDA        | Р     | Analog power of DRAM PLL, 3.3V.                                            |

| HVDDA        | Р     | Analog power of host PLL 3V.                                               |

| AGNDA        | G     | Analog ground of AGP PLL.                                                  |

| DGNDA        | G     | Analog ground of memory PLL.                                               |

| HGNDA        | G     | Analog ground of host PLL.                                                 |

| GND          | G     | Ground.                                                                    |

## 2.3 NAND-Tree Scan Functions:

Group 1 :

| GCBEJ[0] -> | GAD[6] ->   | GAD[11] ->  | GAD[8] ->   | GAD[0] ->  | GAD[3] ->  |

|-------------|-------------|-------------|-------------|------------|------------|

| GAD[1] ->   | GAD[9] ->   | GAD[15] ->  | GAD[4] ->   | GAD[2] ->  | GAD[5] ->  |

| GDEVSELJ -> | GAD[7] ->   | AD_STB0 ->  | GAD[10] ->  | GAD[12] -> | GAD[13] -> |

| GAD[14] ->  | GCBEJ[1] -> | GPAR ->     | GCLKI ->    | GCLKO ->   | GSTOPJ ->  |

| GTRDYJ ->   | GIRDYJ ->   | GFRAMEJ ->  | GCBEJ[2] -> | GAD[16] -> | GAD[20] -> |

| GAD[17] ->  | GAD[18] ->  | GCBEJ[3] -> | GAD[19] ->  | GAD[21] -> | GAD[22] -> |

| GAD[23] ->  | AD_STB1->   | GAD[26] ->  | GAD[24] ->  | GAD[25] -> | GAD[27] -> |

| GAD[31] ->  | GAD[29] ->  | GAD[28] ->  | GAD[30] ->  | SBA[7] ->  | SBA[6] ->  |

| SBA[5] ->   | SBA[3] ->   | SBA[2] ->   | SBA[0] ->   | PIPEJ ->   | RBFJ ->    |

| ST[2] ->    | ST[1] ->    | SBA[4] ->   | ST[0] ->    | SB_STB ->  | GREQJ ->   |

| SBA[1] ->   | GGNTJ       |             |             |            |            |

Group 2 :

| AD[0] ->    | AD[2] ->    | AD[1] ->    | AD[3] ->    | AD[6] ->          | AD[5] ->     |

|-------------|-------------|-------------|-------------|-------------------|--------------|

| AREQJ ->    | AD[9] ->    | AD[4] ->    | PHLDJ ->    | AD[8] ->          | RATIOJ ->    |

| AD[7] ->    | CBEJ[0] ->  | AD[14] ->   | AD[13] ->   | AD[12] ->         | AD[11] ->    |

| PAR ->      | SERRJ ->    | PCICLK ->   | CBEJ[1] ->  | DEVSELJ ->        | AD[15] ->    |

| STOPJ ->    | FRAMEJ ->   | PLOCKJ ->   | CBEJ[2] ->  | AD[18] ->         | AD[17] ->    |

| AD[20] ->   | PHLDAJ ->   | AD[16] ->   | AD[10] ->   | PTRDYJ ->         | AD[23] ->    |

| AD[19] ->   | AD[21] ->   | AD[22] ->   | IRDYJ ->    | AD[25] ->         | CBEJ[3] ->   |

| AD[26] ->   | AD[28] ->   | AD[29] ->   | AD[30] ->   | AD[24] ->         | AD[27] ->    |

| RESETJ ->   | PREQJ[0] -> | PGNTJ[0] -> | AD[31] ->   | PGNTJ[1] ->       | PREQJ[2] ->  |

| PGNTJ[2] -> | PREQJ[1] -> | PREQJ[4] -> | PREQJ[3] -> | Reserved (D10) -> | HCLK_SEL1 -> |

|             |             |             |             |                   |              |

## Group 3 :

| MD[63] ->   | MD[62] ->   | MD[31] ->  | MD[60] ->   | MD[30] ->  | MD[61] ->  |

|-------------|-------------|------------|-------------|------------|------------|

| MD[28] ->   | MD[29] ->   | MD[58] ->  | MD[59] ->   | MD[27] ->  | MD[26] ->  |

| MD[57] ->   | MD[56] ->   | MD[16] ->  | MD[25] ->   | MD[24] ->  | MD[50] ->  |

| MD[55] ->   | MD[23] ->   | MD[54] ->  | MD[53] ->   | MD[22] ->  | MD[21] ->  |

| MD[52] ->   | MD[19] ->   | MD[51] ->  | MD[20] ->   | MD[18] ->  | MD[17] ->  |

| MD[49] ->   | MD[48] ->   | MDP[3] ->  | MDP[7] ->   | CASJ[2] -> | MDP[6] ->  |

| MA[7] ->    | MDP[2] ->   | CASJ[3] -> | MA[14] ->   | MA[13] ->  | MA[11] ->  |

| CASJ[6] ->  | MA[10] ->   | MA[2] ->   | MA[9] ->    | MA[6] ->   | MA[5] ->   |

| MA[4] ->    | MA[1] ->    | MB[0] ->   | MA[12] ->   | MA[0] ->   | MA[8] ->   |

| SRASJ[0] -> | SRASJ[2] -> | MA[3] ->   | SRASJ[3] -> | RASJ[1] -> | RASJ[4] -> |

| CLK32K ->   | CASJ[7] ->  |            |             |            |            |

### Group 4 :

| MD[32] ->   | MD[0] ->    | MD[3] ->    | MD[34] ->   | MD[1] ->    | MD[2] ->    |

|-------------|-------------|-------------|-------------|-------------|-------------|

| MD[33] ->   | MD[36] ->   | MD[4] ->    | MD[5] ->    | MD[35] ->   | MD[38] ->   |

| MD[6] ->    | MD[37] ->   | MD[7] ->    | MD[9] ->    | MD[40] ->   | MD[8] ->    |

| MD[41] ->   | MD[42] ->   | MD[39] ->   | MD[43] ->   | MD[11] ->   | MD[12] ->   |

| MD[10] ->   | MD[14] ->   | MD[45] ->   | MD[44] ->   | MD[13] ->   | MD[47] ->   |

| MD[46] ->   | MD[15] ->   | SMIACKJ ->  | SCASJ[2] -> | MWEJ[1] ->  | MDP[0] ->   |

| MDP[5] ->   | SCASJ[1] -> | CASJ[4] ->  | MDP[4] ->   | MWEJ[3] ->  | MDP[1] ->   |

| RASJ[6] ->  | CASJ[1] ->  | SUSPENDJ->  | MWEJ[0] ->  | CKE ->      | MWEJ[2] ->  |

| SCASJ[0] -> | RASJ[3] ->  | SCASJ[3] -> | CASJ[5] ->  | RASJ[0] ->  | CASJ[0] ->  |

| RASJ[5] ->  | RASJ[7] ->  | DCLKO ->    | DCLKI ->    | SRASJ[1] -> | SRASJ[2] -> |

| MB[1] ->    | REFENV ->   |             |             |             |             |

## Group 5 :

| HCLK ->     | ADSJ ->    | RSJ[2] ->   | RSJ[1] ->   | DBSYJ ->    | HITJ ->     |

|-------------|------------|-------------|-------------|-------------|-------------|

| HREQJ[2] -> | HITMJ ->   | HREQJ[3] -> | RSJ[0] ->   | HREQJ[4] -> | HREQJ[1] -> |

| DRDYJ ->    | LOCKJ ->   | DEFERJ ->   | BNRJ ->     | HA[4] ->    | TRDYJ ->    |

| BPRIJ ->    | HA[8] ->   | HA[9] ->    | HREQJ[0] -> | HA[11] ->   | HA[10] ->   |

| HA[6] ->    | HA[12] ->  | HA[3] ->    | HA[5] ->    | HA[7] ->    | HA[25] ->   |

| HA[20] ->   | HA[14] ->  | HA[18] ->   | HA[13] ->   | HA[17] ->   | HA[28] ->   |

| HA[23] ->   | HA[16] ->  | HA[26] ->   | HA[21] ->   | HA[15] ->   | HA[22] ->   |

| HA[27] ->   | HA[19] ->  | HA[31] ->   | HD[12] ->   | HA[30] ->   | HA[29] ->   |

| HD[7] ->    | HD[1] ->   | HD[3] ->    | HA[24] ->   | BREQJ[0] -> | HD[0] ->    |

| HD[5] ->    | CPURSTJ -> | HD[2] ->    | HD[4] ->    | PGNTJ[4] -> |             |

| Group | 6 | : |

|-------|---|---|

|       |   |   |

| HD[8] ->  | HD[6] ->  | HD[14] ->   | HD[10] -> | HD[9] ->  | HD[11] -> |

|-----------|-----------|-------------|-----------|-----------|-----------|

| HD[17] -> | HD[13] -> | HD[15] ->   | HD[20] -> | HD[23] -> | HD[16] -> |

| HD[21] -> | HD[19] -> | HD[27] ->   | HD[18] -> | HD[22] -> | HD[25] -> |

| HD[24] -> | HD[29] -> | HD[30] ->   | HD[31] -> | HD[26] -> | HD[33] -> |

| HD[35] -> | HD[28] -> | HD[32] ->   | HD[37] -> | HD[38] -> | HD[43] -> |

| HD[34] -> | HD[36] -> | HD[40] ->   | HD[39] -> | HD[45] -> | HD[42] -> |

| HD[44] -> | HD[47] -> | HD[51] ->   | HD[41] -> | HD[59] -> | HD[46] -> |

| HD[48] -> | HD[49] -> | HD[60] ->   | HD[52] -> | HD[54] -> | HD[61] -> |

| HD[57] -> | HD[53] -> | HD[58] ->   | HD[55] -> | HD[56] -> | HD[50] -> |

| HD[62] -> | HD[63] -> | PGNTJ[3] -> |           |           |           |

## 2.4 Numerical Pin List :

| Pin No. | Pin Name | Туре |

|---------|----------|------|

| A1      | AD20     | I/O  |

| A2      | AD21     | I/O  |

| A3      | AD22     | I/O  |

| A4      | AD24     | I/O  |

| A5      | AD27     | I/O  |

| A6      | AD31     | I/O  |

| A7      | PREQJ1   | I    |

| A8      | PREQJ3   | I    |

| A9      | HD62     | I/O  |

| A10     | HD58     | I/O  |

| A11     | HD61     | I/O  |

| A12     | HD60     | I/O  |

| A13     | HD59     | I/O  |

| A14     | HD51     | I/O  |

| A15     | HD42     | I/O  |

| A16     | HD36     | I/O  |

| A17     | HD37     | I/O  |

| A18     | HD28     | I/O  |

| A19     | HD26     | I/O  |

| A20     | HD24     | I/O  |

| A21     | HD18     | I/O  |

| A22     | HD13     | I/O  |

| A23     | HD6      | I/O  |

| A24     | HD4      | I/O  |

| A25     | GTL_REF0 | I/O  |

| A26     | HD1      | I/O  |

| B1      | AD17     | I/O  |

| B2      | AD18     | I/O  |

| B3      | AD19     | I/O  |

| B4      | CBEJ3    | I/O  |

| B5      | AD26     | I/O  |

| B6      | AD30     | I/O  |

| B7      | PGNTJ0   | I/O  |

| B8      | PGNTJ2   | I/O  |

| B9      | PGNTJ4   | I/O  |

| B10     | HD63     | I/O  |

| B11     | HD55     | I/O  |

| B12     | GTL_REF3 | I/O  |

| B13     | HD48     | I/O  |

| B14     | HD41     | I/O  |

| B15     | HD44     | I/O  |

| B16     | HD40     | I/O  |

| B17     | HD38     | I/O  |

| B18     | HD35     | I/O  |

| Pin No. | Pin Name  | Туре |

|---------|-----------|------|

| B19     | HD30      | I/O  |

| B20     | HD22      | I/O  |

| B21     | HD21      | I/O  |

| B22     | HD15      | I/O  |

| B23     | HD9       | I/O  |

| B24     | HD2       | I/O  |

| B25     | HD0       | I/O  |

| B26     | HA29      | I/O  |

| C1      | FRAMEJ    | I/O  |

| C2      | CBEJ2     | I/O  |

| C3      | AD16      | I/O  |

| C4      | AD23      | I/O  |

| C5      | AD25      | I/O  |

| C6      | AD29      | I/O  |

| C7      | PREQJ0    | I    |

| C8      | PREQJ2    | I    |

| C9      | PREQJ4    | I    |

| C10     | HCLK_SEL1 | I/O  |

| C11     | HD56      | I/O  |

| C12     | HD54      | I/O  |

| C13     | HD46      | I/O  |

| C14     | GTL_REF2  | I/O  |

| C15     | HD45      | I/O  |

| C16     | HD34      | I/O  |

| C17     | HD32      | I/O  |

| C18     | HD31      | I/O  |

| C19     | HD25      | I/O  |

| C20     | HD19      | I/O  |

| C21     | HD20      | I/O  |

| C22     | HD11      | I/O  |

| C23     | HD8       | I/O  |

| C24     | HD5       | I/O  |

| C25     | HD3       | I/O  |

| C26     | HA30      | I/O  |

| D1      | DEVSELJ   | I/O  |

| D2      | STOPJ     | I/O  |

| D3      | PLOCKJ    | I/O  |

| D4      | PTRDYJ    | I/O  |

| D5      | IRDYJ     | I/O  |

| D6      | AD28      | I/O  |

| D7      | RESETJ    | I/O  |

| D8      | PGNTJ1    | I/O  |

| D9      | PGNTJ3    | I/O  |

| D10     | RESERVED  |      |

Numerical Pin List : (continued)

| Pin No. | Pin Name | Туре |

|---------|----------|------|

| D11     | HD50     | I/O  |

| D12     | HD53     | I/O  |

| D13     | HD52     | I/O  |

| D14     | HD47     | I/O  |

| D15     | HD39     | I/O  |

| D16     | HD43     | I/O  |

| D17     | HD33     | I/O  |

| D18     | HD29     | I/O  |

| D19     | HD27     | I/O  |

| D20     | HD23     | I/O  |

| D21     | HD17     | I/O  |

| D22     | HD10     | I/O  |

| D23     | HD14     | I/O  |

| D24     | CPURSTJ  | I/O  |

| D25     | BRJ0     | I/O  |

| D26     | HA26     | I/O  |

| E1      | SERRJ    | I/O  |

| E2      | PAR      | I/O  |

| E3      | CBEJ1    | I/O  |

| E4      | AD15     | I/O  |

| E5      | VCCP     | Р    |

| E6      | VCCP     | Р    |

| E7      | GND      | Р    |

| E8      | GND      | Р    |

| E9      | GND      | Р    |

| E10     | GND      | Р    |

| E11     | GND      | Р    |

| E12     | HD57     | I/O  |

| E13     | HD49     | I/O  |

| E14     | VCCHP    | Р    |

| E15     | VCCHP    | Р    |

| E16     | GND      | Р    |

| E17     | GND      | Р    |

| E18     | GND      | Р    |

| E19     | VCCHP    | Р    |

| E20     | HD16     | I/O  |

| E21     | GND      | Р    |

| E22     | GND      | Р    |

| E23     | HA24     | I/O  |

| E24     | GTL_REF1 | I/O  |

| E25     | HA31     | I/O  |

| E26     | HA28     | I/O  |

| F1      | AD14     | I/O  |

| F2      | AD13     | I/O  |

| Pin No. | Pin Name | Туре |

|---------|----------|------|

| F3      | AD12     | I/O  |

| F4      | AD11     | I/O  |

| F5      | AD10     | I/O  |

| F6      | VCCP     | Р    |

| F7      | VCCP     | Р    |

| F8      | GND      | Р    |

| F19     | VCCHP    | Р    |

| F20     | GND      | Р    |

| F21     | GND      | Р    |

| F22     | GND      | Р    |

| F23     | HD7      | I/O  |

| F24     | HA27     | I/O  |

| F25     | HA22     | I/O  |

| F26     | HA20     | I/O  |

| G1      | AD9      | I/O  |

| G2      | AD8      | I/O  |

| G3      | CBEJ0    | I/O  |

| G4      | AD7      | I/O  |

| G5      | GND      | Р    |

| G6      | GND      | Р    |

| G21     | GND      | Р    |

| G22     | NC       |      |

| G23     | HD12     | I/O  |

| G24     | HA21     | I/O  |

| G25     | HA23     | I/O  |

| G26     | HA25     | I/O  |

| H1      | AD6      | I/O  |

| H2      | AD5      | I/O  |

| H3      | AD4      | I/O  |

| H4      | PHLDAJ   | I/O  |

| H5      | GND      | Р    |

| H6      | GND      | Р    |

| H21     | GND      | Р    |

| H22     | HA19     | I/O  |

| H23     | HA15     | I/O  |

| H24     | HA17     | I/O  |

| H25     | HA18     | I/O  |

| H26     | HA11     | I/O  |

| J1      | AD3      | I/O  |

| J2      | AD2      | I/O  |

| J3      | AD1      | I/O  |

| J4      | PCICLK   | I    |

| J5      | GND      | Р    |

| J22     | VCCHP    | Р    |

| Numerical Pin List : | (continued) |

|----------------------|-------------|

|----------------------|-------------|

| Pin No. | Pin Name | Туре |

|---------|----------|------|

| J23     | HA16     | I/O  |

| J24     | HA13     | I/O  |

| J25     | HA12     | I/O  |

| J26     | HA8      | I/O  |

| K1      | AD0      | I/O  |

| K2      | GREQJ    | I    |

| K3      | GGNTJ    | I/O  |

| K4      | PHLDJ    |      |

| K5      | RATIOJ   | I/O  |

| K22     | GND      | Р    |

| K23     | HA14     | I/O  |

| K24     | HA7      | I/O  |

| K25     | HA10     | I/O  |

| K26     | BNRJ     | I/O  |

| L1      | ST0      | I/O  |

| L2      | ST1      | I/O  |

| L3      | ST2      | I/O  |

| L4      | AREQJ    | I/O  |

| L5      | VCCP     | P    |

| L11     | GND      | Р    |

| L12     | GND      | Р    |

| L13     | GND      | Р    |

| L14     | GND      | Р    |

| L15     | GND      | Р    |

| L16     | GND      | Р    |

| L22     | H VDDA   | Р    |

| L23     | HA5      | I/O  |

| L24     | HA3      | I/O  |

| L25     | HREQJ0   | I/O  |

| L26     | HREQJ1   | I/O  |

| M1      | RBFJ     | I    |

| M2      | PIPEJ    | I    |

| M3      | SBA0     | I/O  |

| M4      | SBA1     | I/O  |

| M5      | VCC5V    | Р    |

| M11     | GND      | Р    |

| M12     | GND      | Р    |

| M13     | GND      | Р    |

| M14     | GND      | Р    |

| M15     | GND      | Р    |

| M16     | GND      | Р    |

| M22     | HA6      | I/O  |

| M23     | HA9      | I/O  |

| M24     | BPRIJ    | I/O  |

| Pin No. | Pin Name | Туре |

|---------|----------|------|

| M25     | HA4      | I/O  |

| M26     | HREQJ4   | I/O  |

| N1      | SBA2     | I/O  |

| N2      | AGP_REF2 | I/O  |

| N3      | SBA3     | I/O  |

| N4      | SB_STB   | I    |

| N5      | SBA4     | I/O  |

| N11     | GND      | Р    |

| N12     | GND      | Р    |

| N13     | GND      | Р    |

| N14     | GND      | Р    |

| N15     | GND      | Р    |

| N16     | GND      | Р    |

| N22     | TRDYJ    | I/O  |

| N23     | DEFERJ   | I/O  |

| N24     | LOCKJ    | I/O  |