# M1543C

South Bridge Pentium/Pentium II Chip Set with Super I/O & FIR

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

# M1543C : PCI-to-ISA Bus Bridge with Super I/O & Fast IR

### Section 1 : Introduction

### 1.1 Features

- Provides a highly integrated bridge (with Super I/O & <u>Fast IR</u>) between PCI and ISA bus for both Pentium and Pentium II systems

- PCI 3.3V/5V Tolerance Interface

- Supports PCI Master and Slave Interface

- Supports PCI Master and Slave Initiated Termination

- Concurrent PCI Architecture

- PCI spec. 2.1 Compliant (Delayed Transaction & Passive Release Support)

- Buffers Control

- 8-byte Bi-directional Line Buffers for DMA/ISA Memory Read/Write Cycles to PCI Bus

- 32-bit Posted Write Buffer for PCI Memory Write and I/O Data Write (for Sound Card) to ISA Bus

- Provides Steerable PCI Interrupts for PCI device Plug-and-Play

- Up to 8 PCI Interrupts Routing

- Level to Edge Trigger Transfer

- Enhanced DMA Controller

- Provides 7 Programmable Channels, 4 for 8-bit Data Size, 3 for 16-bit Data Size

- 32-bit Addressability

- Provides Compatible DMA Transfers

- Provides Type F Transfers

#### Interrupt Controller

- Provides 14 Interrupt Channels

- Independent Programmable Level/Edge Triggered Channels

- Counter/Timers

- Provides 8254 Compatible Timers for System Timer, Refresh Request, Speaker Output Use

- Supports Distributed DMA

- 7 DMA Channels can be Arbitrarily Programmed as Distributed Channels

- Supports Serialized IRQ

- Quiet/Continuous Mode

- Programmable (Default 21) IRQ/DATA Frames

- Programmable START Frame Pulse Width

- Supports Plug-and-Play

- 1 Programmable Chip Select

- 2 Steerable Interrupt Request Lines

- Built-in Keyboard Controller

- Built-in PS2/AT Keyboard and PS2 Mouse Controller

- Supports up to 256 KB ROM Size Decoding

- Supports Positive/Subtractive Decode for ISA Device

- PMU Features

- Full Support for ACPI and OS Directed Power Management

- CPU SMM Legacy Mode and SMI Feature Supported

- Supports Programmable STPCLKJ : Throttle/CKONSTP/CKOFFSTP Control

- Supports I/O Trap for I/O Restart Feature

- PMU Operation States :

- -- ON

- -- Standby

- -- Sleep (Power On Suspend)

- -- Suspend (Suspend to DRAM)

- -- Suspend to HDD

- -- Soft-Off

- -- Mechanical Off

- APM State Detection and Control Logic Supported

- Global and Local Device Power Control Logic

- 3 Programmable Timers : Standby/ APMA/ Global Display

- Provides System Activity and Display Activity Monitorings, including

- -- Video

- -- Audio

- -- Hard Disk

- -- Floppy Disk

- -- Serial Ports

- -- Parallel Port

- -- Keyboard

- -- 1 Programmable I/O Group

- -- 1 Programmable Memory Space

### --Preliminary, Confidential, Proprietary--

# Data Sheet

### Acer Laboratories Inc.

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

- Provides Hot Plugging Events Detection -- Docking Insert

- Multiple External Wakeup Events of Standby Mode

- -- Power Button (Hotkey)

- -- Modem Ring

- -- RTC Alarm

- -- DRQ2

- Suspend Wakeup Detected

- -- Modem Ring

- -- RTC Alarm

- -- Docking Insert

- -- Power Button (Hotkey)

- -- USB Events

- -- IRQ

- -- ACPWR

- Thermal Alarm Supported

- Clock Generator Control Logic Supported

-- CPUCLK Stop Control

- -- PCICLK Stop Control

- L2 Cache Power Down Control Logic Supported

- 6 General Purpose Input Signals, 10 General Purpose Output Signals

- <u>16 Extended General Purpose Input Signals and</u> <u>16 Extended General Purpose Output Signals</u>

- All Registers Readable/Restorable for Proper Resume from Suspend State

### Built-in PCI IDE Controller

- Supports Ultra 33 DMA Mode Transfers up to Mode 2 Timing (33 Mbytes/sec)

- Supports PIO Modes up to Mode 4 Timings, and Multiword DMA Mode 0,1,2 with Independent Timing of up to 4 Drives

- Integrated <u>16 x 32-bit</u> Read Ahead & Posted Write Buffers for each channel (Total : <u>32 DWords</u>)

- Dedicated pins of ATA Interface for each channel

- Supports tri-state IDE signals for Swap Bay

### USB Interface

- One Root Hub with <u>three</u> USB ports based on OpenHCI 1.0a specification

- Supports FS (12Mbits/sec) and LS (1.5Mbits/sec) Serial Transfer

- Supports Legacy Keyboard and Mouse Software with USB-based Keyboard and Mouse

### Super I/O Interface

- Supports Windows 95 Plug-and-Play

- Supports 2 Serial/ 1 Parallel/ FDC/ 1 IR Functions

- Supports 16-bit Address Decoder

- 2.88 MB (Formatted) Floppy Disk Controller

- -- Software Compatible with 82077 and Supports 16byte Data FIFOs

- -- High Performance Internal Data Separator

- -- Supports Standard 1 Mbps/ 500 Kbps/ 300 Kbps/ 250 Kbps Data Transfer Rate

- -- Supports 3 modes of 3.5" FDD (720K/1.2M/ 1.44MB)

- -- Swappable Drives A and B

- -- Programmable 7-bit I/O Base Address

- Various modes of Parallel Port

- -- Supports ECP/ EPP / PS/2 / SPP and 1284 Compliance

- -- Standard Mode

- --- Programmable 8-bit I/O Base Address

- -- Multiplexing of FDC signals through Parallel Port pins

- -- 12 IRQ Channel Options

- -- 4 8-bit DMA Channel Options

- -- IBM PC/XT, PC/AT and PS/2 Compatible Bidirectional Parallel Port

- -- Enhanced Mode

- Enhanced Parallel Port (EPP) Compatible

- EPP Is Compatible with EPP1.9 (IEEE 1284 <u>Compliant</u>), also supports EPP1.7 of Xircom <u>specification</u>

- -- High Speed Mode

- Microsoft and Hewlett Packard Extended Capabilities Port (ECP) Compatible

- IEEE 1284 Compatible ECP

- Includes protection circuit against damage caused when printer is powered up, or operated at higher voltages

- Serial Ports

- -- Two high performance <del>16450</del>/16550 compatible UARTs with Send/Receive 16-byte FIFOs

- -- Programmable Baud Rate Generator

- -- MIDI (Musical Instrument Digital Interface) Compatible

- -- Option between programmable 7-bit I/O base addresses, 12 IRQs, and 4 DMA channels for each device

- Wireless Communications -- Dedicated pins and COM Port for Infrared Transmission

- -- Supports IrDA 1.0 (SIR) and IrDA 1.1 (MIR and FIR)

- -- Supports Sharp-IR

- -- Option between programmable 7-bit I/O base addresses, 12 IRQs, and 4 DMA channels for each device

- High Performance Power Management for FDC, UART And Parallel Port

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

- SMBus Interface

- System Management Bus Interface meets the V1.0 specification

- Hotkey for Power on Button function through Keyboard

- **328-pin (27mmx27mm) BGA package**

\* Underlined words indicate difference with M1543

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

### Table of Contents :

| Section 1 : Introduction                                                  | 1   |

|---------------------------------------------------------------------------|-----|

| 1.1 Features                                                              | 1   |

| 1.2 Functions                                                             |     |

| 1.3 Functional Block Diagram                                              | 7   |

| 1.4 Differences between M1543 and M1543C                                  | 10  |

|                                                                           |     |

| Section 2 : Pin Description                                               | 14  |

| 2.1 Pinout Diagram                                                        | 14  |

| 2.2 Pin Description Table                                                 |     |

| 2.3 Numerical Pin List                                                    |     |

| 2.4 Alphabetical Pin List                                                 | 32  |

| 2.5 Hardware Setup Table                                                  | 36  |

| 2.6 XDIR Control                                                          | 37  |

| 2.7 GPIO Pins List Table                                                  | 38  |

| 2.8 PCI Interrupt Polling Hardware Implementation                         | 39  |

|                                                                           |     |

| Section 3 : Function Description                                          |     |

| 3.1 PCI Command Set                                                       |     |

| 3.2 PCI Slave Description                                                 | 40  |

| 3.3 PCI Master                                                            |     |

| 3.4 Parity Support                                                        | 42  |

| 3.5 Address Decoding                                                      | 42  |

| 3.6 IDE Master Controller                                                 |     |

| 3.7 Distributed DMA                                                       |     |

| 3.8 Serialized IRQ                                                        |     |

| 3.9 Advanced Power Management                                             |     |

| 3.10 System Management Bus (SMBus)                                        | 43  |

| 3.11 Universal Serial Bus (USB)                                           |     |

| 3.12 Super I/O                                                            | 44  |

|                                                                           |     |

| Section 4 : Configuration Registers                                       |     |

| 4.1 Register Description                                                  |     |

| 4.1.1 M1543C PCI-to-ISA Bridge Configuration Space                        |     |

| 4.1.2 IDE Master (5229) Configuration Registers                           | 84  |

| 4.1.3 USB (5237) Configuration Register                                   | 115 |

| 4.1.4 PMU (7101) Configuration Register                                   | 122 |

| 4.2 Other I/O and Memory Spaces                                           |     |

| 4.2.1 DMA Register Description                                            |     |

| 4.2.2 USB OpenHCI Registers<br>4.2.3 Power Management I/O Space Registers | 102 |

| 4.2.3 Fower Management //O Space Registers                                |     |

| 4.3 ISA Compatible Registers                                              | 213 |

| 4.4 Super NO with Fast IR                                                 |     |

| 4.4.2 Power Management Features                                           |     |

| 4.4.2 Floppy Disk Controller                                              |     |

| 4.4.4 Serial Port Registers                                               |     |

| 4.4.5 Keyboard Controller                                                 |     |

| 4.4.6 Parallel Port                                                       |     |

|                                                                           |     |

Data Sheet

| Section 5 : Power Management Unit Programming Guide          |     |

|--------------------------------------------------------------|-----|

| 5.1 Legacy Power Management Unit                             |     |

| 5.2 Advanced Configuration and Power Interface Specification |     |

| 5.3 System Management Bus Host Controller Programming Guide  | 294 |

| 5.4 Hotkey Function Implementation                           |     |

| 5.4.1 Hotkey Hardware Design Guide                           | 295 |

| 5.4.2 Hotkey Programming Guide                               |     |

| 5.4.3 Keyboard Scan Codes and Make Codes                     | 297 |

|                                                              |     |

| Section 6 : Electrical Characteristics                       |     |

| 6.1 Absolute Maximum Ratings                                 |     |

| 6.2 North Bridge AC specs                                    |     |

| 6.3 South Bridge AC specs                                    |     |

| 6.4 FDC AC Characteristics                                   |     |

| 6.5 AC Test Conditions                                       |     |

|                                                              |     |

| Section 7 : Packaging Information                            |     |

|                                                              |     |

| Section 8 : Revision History                                 |     |

--Preliminary, Confidential, Proprietary--

## Data Sheet

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

### 1.2 Functions

The M1543C is a high integration bridge between PCI and ISA bus, providing full PCI and ISA compatible functions. The M1543C has integrated the following functions :

- (1) Super I/O with Fast IR : 1 Floppy Disk Controller, 1 Parallel Port, 2 Serial Ports, 1 Dedicated Pins of COM Port for Infrared Transmission to support IrDA 1.0 (SIR), IrDA 1.1 (MIR and FIR), and Sharp-IR specification.

- (2) System Peripherals (ISP) (2 x 82C59, 1 x 82C54), advanced features (Type F) in the DMA controller (2 X 82C37).

- (3) Serial Interrupt & Distributed DMA protocol support.

- (4) 2 Steerable IRQs and 1 Programmable Chip Select for Plug-and-Play Support.

- (5) 2-channel dedicated IDE Master Controller with Ultra-33 specification.

- (6) The ACPI (Advanced Configuration and Power Interface) specification support.

- (7) Deep flexible green function and provides the best solution for the best green system.

- (8) PS2 Keyboard/Mouse controller with Hotkey support.

- (9) System Management Bus (SMB).

- (10) 3 OpenHCI 1.0a USB ports for best AGP system support.

- (11) Dedicated and extended GPIO signals support.

- (12) PCI 2.1 (Delayed Transaction & Passive Release) specification support.

- M1543C can connect to the ALi Pentium North Bridge (M1521/M1531/M1541) and also the ALi Pentium II North Bridge (M1621) to provide the best system solution. The following includes more function description.

The built-in Mega I/O in M1543C is the most advanced Super I/O controller solution to basic IBM PC, XT, AT peripherals. It incorporates three full function universal asynchronous receiver/ transmitters (UARTs) (Two for COM1/COM2 and One is dedicated for IR support), a Parallel Port with various mode support, and a Floppy Disk Controller (FDC) incorporating high performance internal data separator with send/receive 16 bytes FIFOs. The serial ports support two high performance 16450/16550 compatible UARTs with send/receive 16 bytes FIFOs and a programmable baud rate generator. For the complete system architecture and specification, M1543C has the dedicated pins and COM port for the IR support, which means, the motherboard still can support two serial ports outside and have the IR support at the same time. The wireless communications supported by M1543C includes IrDA 1.0 (SIR), IrDA 1.1 (MIR and FIR), and Sharp-IR. The Parallel Port features basic functions such as standard mode, enhanced mode, and high speed mode and is compliant to SPP, PS/2, EPP, ECP, and 1284 standard. The Parallel Port also includes protection circuit against damage caused when printer is powered up, or is operated at higher voltages. The Floppy Disk Controller can support up to 1 Mbps data transfer, three-mode driver, and swappable drives A & B. Furthermore, M1543C also has high performance power management for FDC, UARTs and Parallel Port to meet green requirement.

One eight byte bi-directional line buffer is provided for ISA/DMA Master memory read/write. One 32-bit wide posted write buffer is provided for PCI memory write & I/O write (for Audio) cycles to the ISA bus. M1543C also provides a PCI to ISA IRQ routing table, and level to edge trigger transfer. Furthermore, M1543C supports Serial Interrupt and Distributes DMA for Open Architecture Specification.

The chip provides 2 extra IRQ lines and 1 programmable chip select for motherboard Plug-and-Play functions. The interrupt lines can be routed to any of the available ISA interrupts.

The on-chip IDE controller supports two separate IDE connectors for up to 4 IDE devices providing an interface for IDE hard disks and CD ROMs. The Ultra DMA specification (which supports the 33M bytes per second transfer rate) has been implemented in this IDE controller. The ATA bus pins & the smart deep Buffer (16 x 32-bit Read Ahead and Posted Write) are all dedicated for separate channel to improve the reliability and the performance of IDE Master. Dedicated Pins and Buffers are also the best implementation for today's concurrent OS and application to reduce overhead and achieve the best performance. The IDE controller also supports Tri-state IDE signals for Swap Bay support.

The M1543C supports Super Green for Intel and Intel compatible CPUs. It implements SMI or SCI (System Controller Interrupt) to meet the ACPI specification. It also meets the requirement for Microsoft's OnNow Design Initiative. The M1543C supports powerful power management for power saving including On, Standby, Sleeping, Suspend, Soft Off, Mechanical Off state. To control the CPU power consumption, it provides CPU clock control (STPCLKJ). The STPCLKJ can be active (low) or inactive (high) in turn by throttling control. Also, the M1543C can support the most flexible system clock design : it can be programmed to stop the CPU Clock, and PCI Clock. The PBSRAM (Pipelined Burst SRAM) doze mode is also supported.

### M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

The M1543C is a highly integrated chip including PS2 Keyboard/Mouse with Hotkey support, SM Bus, 3 OpenHCI 1.0a USB ports (One can be used for AGP slot, and the other two for external connections), and the dedicated and extended GPIO (General Purpose Input/Output) pins. M1543C supports the Hotkey function in the keyboard. Users can define the special function key to make the system entering or leaving different operation mode, for example, put the system into sleep or wake up the system, even force the system into Soft-Off mode. For the best AGP system implementation, M1543C has a dedicated USB port to connect to AGP slot and supports two AGP IRQ inputs to route to any available ISA interrupt pins. Also, for the more demanding GPIO pins in modern motherboard design, M1543C supports extended GPIO pins through external logic. It can extend up to 16 GPI signals and 16 GPO signals. For the best system performance, M1543C supports all the PCI 2.1 specification including Delayed Transaction & Passive Release. The system designer can use this chip to implement the best green and cost/performance system.

### 1.3 System Architecture & Functional Block Diagram

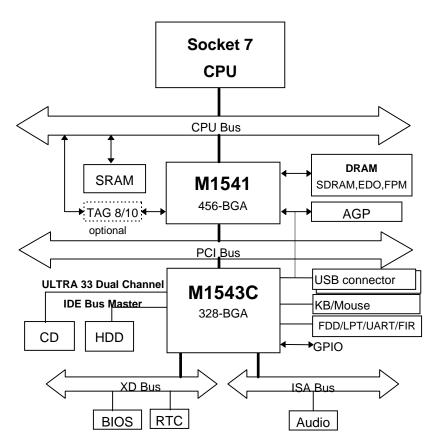

Figure 1.1 shows the system block diagram of Aladdin-V with M1543C. Aladdin-V is the best socket-7 chipset which can support 100MHz CPU bus and 2X AGP to achieve the best system & 3D Graphic performance. Through the high integration of M1543C, user can build a motherboard with the features of Super I/O (FDC, Parallel Port, and COM Ports), IR (SIR, MIR, FIR, and Sharp-IR), USB, Ultra-33 IDE, PS2 Keyboard/Mouse, Hotkey function, ACPI, GPIO, and deep green function with the minimized cost.

Figure 1.1 Aladdin V System Block Diagram with M1543C

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

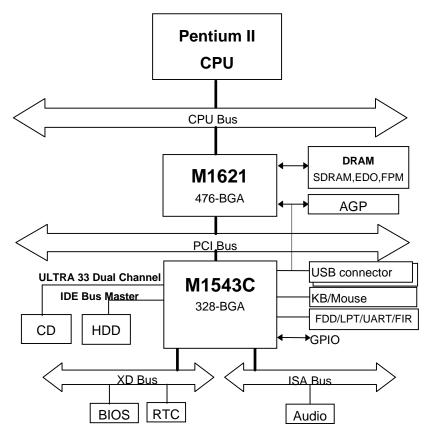

Figure 1.2 shows the system block diagram of Aladdin Pro II with M1543C. Aladdin Pro II is the best Pentium II chipset which can support 100MHz CPU bus and 2X AGP to achieve the best system & 3D Graphic performance. Through the high integration of M1543C, user can build a motherboard with the features of Super I/O (FDC, Parallel Port, and COM Ports), IR (SIR, MIR, FIR, and Sharp-IR), USB, Ultra-33 IDE, PS2 Keyboard/Mouse, Hotkey function, ACPI, GPIO, and deep green function with the minimized cost.

Figure 1.2 Aladdin Pro II System Block Diagram with M1543C

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

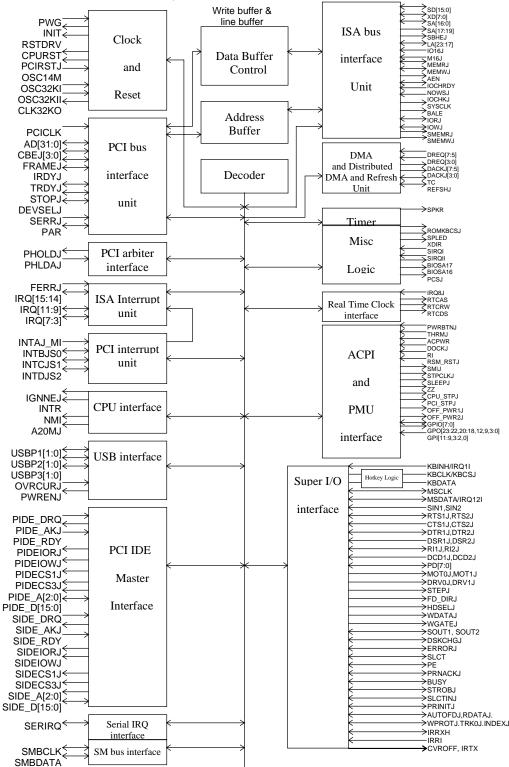

Figure 1.3 shows the internal function block diagram of M1543C.

### 1.4 Differences between M1543C and M1543

This section summarizes the differences between M1543C and M1543. Table below lists the major function differences :

| Function                 | M1543C                      | M1543     |

|--------------------------|-----------------------------|-----------|

| Extended GPIO            | 16 GPIs & 16 GPOs           | None      |

| IDE Smart Buffer Size    | 32 DWords                   | 20 DWords |

| USB Ports                | 3 Ports                     | 2 Ports   |

| COM Ports                | 3 Ports                     | 2 Ports   |

| IR Support               | SIR, MIR, FIR, and Sharp-IR | SIR only  |

| Keyboard Hotkey Function | Yes                         | No        |

The following show the more detailed information regarding the differences :

(1) Pin I/O Change :

| Signal Name<br>(Location) | M1543 | M1543C |

|---------------------------|-------|--------|

| DSKCHGJ (T3)              |       | I/O    |

| SOUT1 (W6)                | 0     | I/O    |

| CLK32KO (M19)             | 0     | I/O    |

(2) New Hardware Setting Pins :

| Signal Name | Pull-High                | Pull-Low                               |

|-------------|--------------------------|----------------------------------------|

| (Location)  |                          |                                        |

| CLK32KO     | 32K test mode, this mode | Normal mode, this mode must be used in |

| (M19)       | is only for test only.   | normal operation.                      |

| PCSJ        | Normal mode              | Hotkey enable, this mode is programmed |

| (D15)       |                          | as Power PC mode in M1543.             |

(3) SD/GPIO[7:0] Usage When TC is Pull-high :

When TC is pull-high, GPIO[7:0] are chosen. But it can be assigned as another function through register programming. Please refer to the following table :

| Signal Name | As Function   | Register Setting          |

|-------------|---------------|---------------------------|

| (Location)  |               |                           |

| SD/GPIO[7]  | PWR_EN (O)    | M1543C Index-72h Bit6 = 1 |

| (Y11)       | GPIO[7] (I/O) | M1543C Index-72h Bit6 = 0 |

| SD/GPIO[6]  | Reserved      | M1543C Index-75h Bit6 = 1 |

| (W11)       | GPIO[6] (I/O) | M1543C Index-75h Bit6 = 0 |

| SD/GPIO[5]  | USBP2- (I/O)  | M5237 Index-40h Bit26 = 1 |

| (Y12)       | GPIO[5] (I/O) | M5237 Index-40h Bit26 = 0 |

| SD/GPIO[4]  | USBP2+ (I/O)  | M5237 Index-40h Bit26 = 1 |

| (W12)       | GPIO[4] (I/O) | M5237 Index-40h Bit26 = 0 |

| SD/GPIO[3]  | CVROFF (O)    | M1543C Index-6Dh Bit4 = 1 |

| (Y13)       | GPIO[3] (I/O) | M1543C Index-6Dh Bit4 = 0 |

| SD/GPIO[2]  | IRRX (I)      | M1543C Index-6Dh Bit4 = 1 |

| (W13)       | GPIO[2] (I/O) | M1543C Index-6Dh Bit4 = 0 |

| SD/GPIO[1]  | IRRXH (I/O)   | M1543C Index-6Dh Bit4 = 1 |

| (U13)       | GPIO[1] (I/O) | M1543C Index-6Dh Bit4 = 0 |

| SD/GPIO[0]  | IRTX (O)      | M1543C Index-6Dh Bit4 = 1 |

| (T13)       | GPIO[0] (I/O) | M1543C Index-6Dh Bit4 = 0 |

Data Sheet

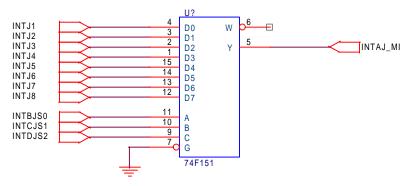

(4) AGP Interrupts Inputs :

User can connect AGP two Interrupts (AGP\_INTAJ and AGP\_INTBJ) pins to IRQ[14]/AGP\_INTAJ(G17) & IRQ[15]/AGP\_INTBJ(H17) pins and use M1543C Index-4Bh Bits[7:0] to route these two interrupts to any available ISA Interrupts. The following table shows the register setting for pin function selection :

| Signal Name (Location)  | M1543C Index-78h Bit0 = 0 | M1543C Index-78h Bit0 = 1 |

|-------------------------|---------------------------|---------------------------|

| IRQ[14]/AGP_INTAJ (G17) | IRQ[14]                   | AGP_INTAJ                 |

| IRQ[15]/AGP_INTBJ (H17) | IRQ[15]                   | AGP_INTBJ                 |

(5) Suspend Region:

Put two pins: IRQ[10]/KBDATA (N18), LA[21]/KBCLK (M17)into Suspend region for Hotkey support.

(6) Hotkey Function:

When PCSJ is pull-low, the Hotkey function is enabled. IRQ[10]/KBDATA (N18) and LA[21]/KBCLK (M17) will become KBDATA and KBCLK for the Hotkey function support. KBDATA/IRQ[10] (U12) and LA[21]/KBCLK (M17) will become IRQ[10] and LA[21] for ISA slot. That is why M1543C puts these two pins into Suspend region. The following table shows the pin function difference :

| Signal Name (Location) | PCSJ pull-high                | PCSJ pull-low                |

|------------------------|-------------------------------|------------------------------|

|                        | (Hotkey function is disabled) | (Hotkey function is enabled) |

| IRQ[10]/KBDATA (N18)   | IRQ[10]                       | KBDATA                       |

| LA[21]/KBCLK (M17)     | LA[21]                        | KBCLK                        |

| KBDATA/IRQ[10] (U12)   | KBDATA                        | IRQ[10]                      |

| KBCLK/LA[21] (U11)     | KBCLK                         | LA[21]                       |

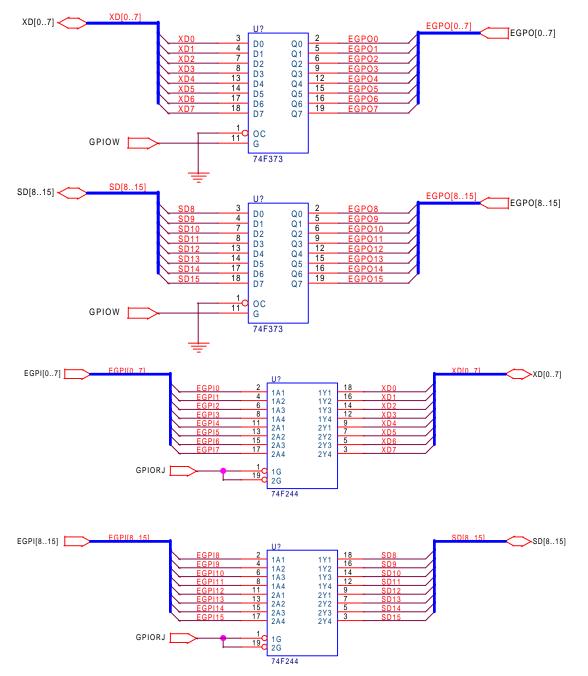

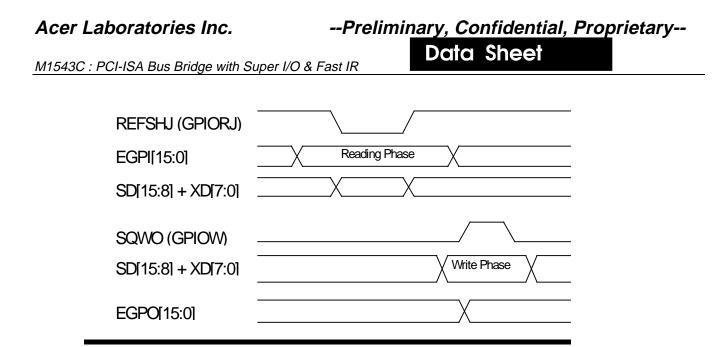

(7) Extended GPIO Pins (16 Bits Input and 16 Bits Output):

For this function support, external two F373s and two F244s must be used. And pin REFRSHJ is used as GPIORJ function (no register setting needed) to control F244 output enable, SQWO must be chosen as GPIOW function (through register setting) to control F373 Latch input. The following table shows the SQWO pin function selection:

| M1543C register Index-5Ah Bits[9:8] | Pin SQWO/GPIOW/GPO[9] (E15) function selection |

|-------------------------------------|------------------------------------------------|

| 00                                  | SQWO                                           |

| 01                                  | GPIOW                                          |

| 10                                  | GPO[9]                                         |

| 11                                  | GPO[9]                                         |

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

The following figure shows the external circuit implementation and timing for extended GPIO :

(8) M1543C can release IRQ12 resource when PS2 Mouse is not enabled (Internal Keyboard is enabled as AT Keyboard only). M1543 cannot release IRQ12 at the same configuration.

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

### Section 2 : Pin Description

### 2.1 Pinout Diagram

|   | 1            | 2            | 3            | 4            | 5            | 6           | 7           | 8          | 9           | 10          | 11           | 12          | 13          | 14          | 15           | 16          | 17               | 18           | 19           | 20          |

|---|--------------|--------------|--------------|--------------|--------------|-------------|-------------|------------|-------------|-------------|--------------|-------------|-------------|-------------|--------------|-------------|------------------|--------------|--------------|-------------|

| Α | AD<br>21     | AD<br>20     | AD<br>19     | AD<br>16     | IRDY<br>J    | SER<br>RJ   | AD<br>14    | AD<br>10   | AD6         | AD1         | PHO<br>LDJ   | PCIR<br>EQJ | USB<br>P1-  | RTC<br>DS   | ROMK<br>BCSJ | XD2         | XD5              | SD<br>15     | SD<br>14     | SD<br>13    |

| В | CBE<br>J3    | AD<br>23     | AD<br>22     | AD<br>17     | FRA<br>MEJ   | STO<br>PJ   | AD<br>15    | AD<br>11   | AD7         | AD2         | PHL<br>DAJ   | USB<br>CLK  | USB<br>P0+  | RTC<br>RW   | XD0          | XD3         | XD6              | SD<br>12     | DRE<br>Q7    | SD<br>11    |

| С | AD<br>26     | AD<br>25     | AD<br>24     | AD<br>18     | CBE<br>J2    | DEV<br>SELJ | CBE<br>J1   | AD<br>12   | CBE<br>J0   | AD3         | PCI_<br>STPJ | OVC<br>RJ   | USB<br>P0-  | RTC<br>AS   | XD1          | XD4         | XD7              | DAC<br>KJ7   | SD<br>10     | DRE<br>Q6   |

| D | AD<br>29     | AD<br>28     | AD<br>27     | AD<br>30     | AD<br>31     | TRD<br>YJ   | PAR         | AD<br>13   | AD8         | AD4         | CPU_<br>STPJ | SIRQ<br>I   | BIOS<br>A17 | XDIR        | PCS<br>J     | SER<br>IRQ  | SPK<br>R         | SD9          | DAC<br>KJ6   | SD8         |

| E | PIDE<br>CS3J | PIDE<br>CS1J | PIDE<br>A2   | INTA<br>J_MI | INTB<br>JS0  | INTC<br>JS1 | PCI<br>RSTJ | PCI<br>CLK | AD9         | AD5         | AD0          | USB<br>P1+  | SIRQ<br>II  | BIOS<br>A16 | SQW<br>O     | THR<br>MJ   | SPL<br>ED        | DRE<br>Q5    | MEM<br>WJ    | DAC<br>KJ5  |

| F | PIDE<br>A0   | PIDE<br>A1   | PIDE<br>DAKJ | INTD<br>JS2  | PIDE<br>RDY  | VCC<br>_B   |             |            |             | M154        | 13C          |             |             | VCC<br>_A   | VCC<br>_E    | KBIN<br>H   | MEM<br>RJ        | DRE<br>Q0    | LA17         | DAC<br>KJ0  |

| G | PIDE<br>IORJ | PIDEI<br>OWJ | PIDE<br>DRQ  | PIDE<br>D15  | PIDE<br>D0   | VCC<br>_A   |             |            |             |             |              |             |             |             | VCC<br>_ 3C  | LA<br>18    | IRQ<br>14        | INIT         | A20<br>MJ    | FER<br>RJ   |

| Η | PIDE<br>D14  | PIDE<br>D1   | PIDE<br>D13  | PIDE<br>D2   | PIDE<br>D12  |             |             |            |             |             |              |             | _           |             |              | LA<br>19    | IRQ<br>15        | SMIJ         | NMI          | INTR        |

| J | PIDE<br>D3   | PIDE<br>D11  | PIDE<br>D4   | PIDE<br>D10  | PIDE<br>D5   |             |             |            | GND         | GND         | GND          | GND         |             |             |              | LA<br>20    | SLE<br>EPJ       | STP<br>CLKJ  | IGN<br>NEJ   | CPU<br>RST  |

| К | PIDE<br>D9   | PIDE<br>D6   | PIDE<br>D8   | PIDE<br>D7   | SIDE<br>CS3J |             |             |            | GND         | GND         | GND          | GND         |             |             |              | ZZ          | OFF_<br>PWR<br>1 | RSM_<br>RSTJ | SUST<br>AT1J | ACP<br>WR   |

| L | SIDE<br>CS1J | SIDE<br>A2   | SIDE<br>A0   | SIDE<br>A1   | SIDE<br>DAKJ |             |             |            | GND         | GND         | GND          | GND         |             |             |              | SMB<br>DATA | OFF_P<br>WR2     | DOC<br>KJ    | IRQ8<br>J    | PWR<br>BTNJ |

| Μ | SIDE<br>RDY  | SIDE<br>IORJ | SIDE<br>IOWJ | SIDE<br>DRQ  | SIDE<br>D15  |             |             |            | GND         | GND         | GND          | GND         |             |             |              | SMB<br>CLK  | LA21             | RI           | CLK3<br>2KO  | PWG         |

| N | SIDE<br>D0   | SIDE<br>D14  | SIDE<br>D1   | SIDE<br>D13  | SIDE<br>D2   |             |             |            |             |             |              |             | _           |             | VDD<br>_5S   | IRQ<br>11   | LA22             | IRQ<br>10    | OSC<br>32KII | OSC<br>32KI |

| Ρ | SIDE<br>D12  | SIDE<br>D3   | SIDE<br>D11  | SIDE<br>D4   | DIRJ         | VCC<br>_A   |             |            |             |             |              |             |             |             | VCC<br>_C    | LA23        | IO16<br>J        | SBH<br>EJ    | M16J         | OSC<br>14M  |

| R | SIDE<br>D10  | SIDE<br>D5   | SIDE<br>D9   | MOT<br>1J    | DRV<br>0J    | VDD<br>_5   | VCC<br>_A   |            |             |             |              |             |             | VCC<br>_3A  | VCC<br>_A    | BAL<br>E    | тс               | SA0          | SA1          | SA2         |

| Т | SIDE<br>D6   | SIDE<br>D8   | DSK<br>CHGJ  | DRV<br>1J    | MOT<br>0J    | DEN<br>SEL  | DCD<br>1J   | PD3        | ACK<br>J    | RST<br>DRV  | MS<br>CLK    | MS<br>DATA  | SD0         | SA19        | DAC<br>KJ3   | DAC<br>KJ2  | SA6              | SA3          | SA4          | SA5         |

| U | SIDE<br>D7   | HD<br>SELJ   | RDA<br>TAJ   | INDE<br>XJ   | DCD<br>2J    | DSR<br>1J   | STR<br>OBJ  | PD4        | BUS<br>Y    | ERR<br>ORJ  | KB<br>CLK    | KB<br>DATA  | SD1         | SME<br>MRJ  | SA17         | IRQ3        | IRQ5             | SA8          | SA7          | IRQ4        |

| ۷ | WPR<br>OTJ   | TRK<br>0J    | WGA<br>TEJ   | DTR<br>2J    | RI1J         | DTR<br>1J   | PD0         | PD5        | PE          | INITJ       | IRQ9         | DRE<br>Q2   | NO<br>WSJ   | AEN         | IORJ         | SA15        | DRE<br>Q1        | SA10         | IRQ6         | SA9         |

| W | WDA<br>TAJ   | STE<br>PJ    | RTS2<br>J    | SOU<br>T2    | CTS<br>1J    | SOU<br>T1   | PD1         | PD6        | SLC<br>T    | SLC<br>TINJ | SD6          | SD4         | SD2         | SME<br>MWJ  | SA18         | DRE<br>Q3   | SA14             | SYS<br>CLK   | SA11         | IRQ7        |

| Y | RI2J         | CTS<br>2J    | DSR<br>2J    | SIN2         | RTS<br>1J    | SIN1        | PD2         | PD7        | AUTO<br>FDJ | IOCH<br>KJ  | SD7          | SD5         | SD3         | IOCH<br>RDY | IOW<br>J     | SA16        | DAC<br>KJ1       | SA13         | REFR<br>SHJ  | SA12        |

Figure 2-1. Pinout Diagram (Top View)

|   | 1           | 1            | 1            | 1            |             |              |                | 1           | r —         |              | r —         | 1           |            |             |             |              |              |              |              | <del></del>  |

|---|-------------|--------------|--------------|--------------|-------------|--------------|----------------|-------------|-------------|--------------|-------------|-------------|------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|

|   | 20          | 19           | 18           | 17           | 16          | 15           | 14             | 13          | 12          | 11           | 10          | 9           | 8          | 7           | 6           | 5            | 4            | 3            | 2            | 1            |

| Α | SD<br>13    | SD<br>14     | SD<br>15     | XD5          | XD2         | ROMK<br>BCSJ | RTC<br>DS      | USB<br>P1-  | PCIR<br>EQJ | PHO<br>LDJ   | AD1         | AD6         | AD<br>10   | AD<br>14    | SER<br>RJ   | IRD<br>YJ    | AD<br>16     | AD<br>19     | AD<br>20     | AD<br>21     |

| в | SD<br>11    | DRE<br>Q7    | SD<br>12     | XD6          | XD3         | XD0          | RTC<br>RW      | USB<br>P0+  | USB<br>CLK  | PHL<br>DAJ   | AD2         | AD7         | AD<br>11   | AD<br>15    | STO<br>PJ   | FRA<br>MEJ   | AD<br>17     | AD<br>22     | AD<br>23     | CBE<br>J3    |

| С | DRE<br>Q6   | SD1<br>0     | DAC<br>KJ7   | XD7          | XD4         | XD1          | RTC<br>AS      | USB<br>P0-  | OVC<br>RJ   | PCI_<br>STPJ | AD3         | CBE<br>J0   | AD<br>12   | CBE<br>J1   | DEV<br>SELJ | CBE<br>J2    | AD<br>18     | AD<br>24     | AD<br>25     | AD<br>26     |

| D | SD8         | DAC<br>KJ6   | SD9          | SPK<br>R     | SER<br>IRQ  | PCS<br>J     | XDI<br>R       | BIOS<br>A17 | SIR<br>QI   | CPU_<br>STPJ | AD4         | AD8         | AD<br>13   | PAR         | TRD<br>YJ   | AD<br>31     | AD<br>30     | AD<br>27     | AD<br>28     | AD<br>29     |

| Е | DAC<br>KJ5  | MEM<br>WJ    | DRE<br>Q5    | SP<br>LED    | THR<br>MJ   | SQ<br>WO     | BIOS<br>A16    | SIR<br>Q II | USB<br>P1+  | AD0          | AD5         | AD9         | PCI<br>CLK | PCI<br>RSTJ | INTC<br>JS1 | INTB<br>JS0  | INTA<br>J_MI | PID<br>E A2  | PIDE<br>CS1J | PIDE<br>CS3J |

| F | DAC<br>KJ0  | LA1<br>7     | DRE<br>Q0    | ME<br>MRJ    | KBI<br>NH   | VCC<br>_E    | VCC<br>_A      |             |             | M15          | 43C         |             |            |             | VCC<br>_B   | PIDE<br>RDY  | INTD<br>JS2  | PIDE<br>DAKJ | PID<br>E A1  | PIDE<br>A0   |

| G | FER<br>RJ   | A20<br>MJ    | INIT         | IRQ<br>14    | LA1<br>8    | VCC<br>_ 3C  |                | 1           |             |              |             |             |            |             | VCC<br>_A   | PID<br>E D0  | PIDE<br>D15  | PIDE<br>DRQ  | PIDE<br>IOWJ | PIDE<br>IORJ |

| Н | INT<br>R    | NMI          | SMIJ         | IRQ<br>15    | LA1<br>9    |              | 1              |             |             |              |             |             |            |             |             | PIDE<br>D12  | PID<br>ED2   | PIDE<br>D13  | PID<br>E D1  | PIDE<br>D14  |

| J | CPU<br>RST  | IGN<br>NEJ   | STP<br>CLKJ  | SLE<br>EPJ   | LA2<br>0    |              |                |             | GND         | GND          | GND         | GND         |            |             |             | PID<br>E D5  | PIDE<br>D10  | PID<br>E D4  | PIDE<br>D11  | PIDE<br>D3   |

| к | ACP<br>WR   | SUST<br>AT1J | RSM_<br>RSTJ | OFF_P<br>WR1 | ZZ          |              |                |             | GND         | GND          | GND         | GND         |            |             |             | SIDE<br>CS3J | PID<br>E D7  | PID<br>E D8  | PID<br>ED6   | PIDE<br>D9   |

| L | PWR<br>BTNJ | IRQ<br>8J    | DOC<br>KJ    | OFF_P<br>WR2 | SMB<br>DATA |              |                |             | GND         | GND          | GND         | GND         |            |             |             | SIDE<br>DAKJ | SID<br>EA1   | SID<br>E A0  | SID<br>E A2  | SIDE<br>CS1J |

| М | PW<br>G     | CLK3<br>2KO  | RI           | LA<br>21     | SMB<br>CLK  |              |                |             | GND         | GND          | GND         | GND         |            |             |             | SIDE<br>D15  | SIDE<br>DRQ  | SIDE<br>IOWJ | SIDE<br>IORJ | SIDE<br>RDY  |

| Ν | OSC<br>32KI | OSC<br>32KII | IRQ<br>10    | LA2<br>2     | IRQ<br>11   | VDD<br>_5S   |                |             |             |              | •           |             |            |             |             | SID<br>ED2   | SIDE<br>D13  | SID<br>E D1  | SIDE<br>D14  | SIDE<br>D0   |

| Ρ | OSC<br>14M  | M16<br>J     | SBH<br>EJ    | IO16<br>J    | LA<br>23    | _C           |                |             |             |              |             |             |            |             | VCC<br>_A   | DIRJ         | SID<br>ED4   | SIDE<br>D11  | SID<br>ED3   | SIDE<br>D12  |

| R | SA2         | SA1          | SA0          | TC           | BAL<br>E    | VCC<br>_A    | VCC<br>_3A     |             |             |              |             |             |            | VCC<br>_A   | VDD<br>_5   | DRV<br>0J    | MOT<br>1J    | SID<br>E D9  | SID<br>ED5   | SIDE<br>D10  |

| т | SA5         | SA4          | SA3          | SA6          | DAC<br>KJ2  | DAC<br>KJ3   | SA1<br>9       | SD0         | MS<br>DATA  | MS<br>CLK    | RST<br>DRV  | ACK<br>J    | PD3        | DCD<br>1J   | DEN<br>SEL  | MOT<br>0J    | DRV<br>1J    | DSK<br>CHGJ  | SID<br>E D8  | SIDE<br>D6   |

| U | IRQ<br>4    | SA7          | SA8          | IRQ<br>5     | IRQ<br>3    | SA<br>17     | SME<br>MRJ     | SD1         | KB<br>DATA  | KB<br>CLK    | ERR<br>ORJ  | BUS<br>Y    | PD4        | STR<br>OBJ  | DSR<br>1J   | DCD<br>2J    | IND<br>EXJ   | RDA<br>TAJ   | HD<br>SELJ   | SIDE<br>D7   |

| ۷ | SA9         | IRQ<br>6     | SA<br>10     | DRE<br>Q1    | SA<br>15    | IORJ         | AEN            | NO<br>WSJ   | DRE<br>Q2   | IRQ<br>9     | INIT<br>J   | PE          | PD5        | PD0         | DTR<br>1J   | RI1J         | DTR<br>2J    | WGA<br>TEJ   | TRK<br>0J    | WPR<br>OTJ   |

| w | IRQ<br>7    | SA<br>11     | SYS<br>CLK   | SA1<br>4     | DRE<br>Q3   | SA1<br>8     | SME<br>MW<br>J | SD2         | SD4         | SD6          | SLC<br>TINJ | SLC<br>T    | PD6        | PD1         | SOU<br>T1   | CTS<br>1J    | SOU<br>T2    | RTS<br>2J    | STE<br>PJ    | WDA<br>TAJ   |

| Y | SA<br>12    | REFR<br>SHJ  | SA<br>13     | DAC<br>KJ1   | SA<br>16    | IOW<br>J     | IOCH<br>RDY    | SD3         | SD5         | SD7          | IOC<br>HKJ  | AUT<br>OFDJ | PD7        | PD2         | SIN1        | RTS<br>1J    | SIN2         | DSR<br>2J    | CTS<br>2J    | RI2J         |

Figure 2-2. Bottom View

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

### 2.2 Pin Description Table :

| Pin Name         | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock & Reset II |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PWG              | I<br>Group C<br>Schmitt      | <b>Power-Good Input.</b> This signal comes from the power supply to indicate that power is available and stable. M1543C will use this signal to generate reset sequence for the system. The de-assertion of this input will enable the leakage control circuit between Soft-off (Suspend to Disk) resume circuit and no power circuit.                                                                                                                                 |

| PCICLK           | I<br>Group B                 | <b>PCI Clock for Internal PCI Interface.</b> This is an input PCI clock, it should always be running at ON, STANDBY, SLEEP (Power-On Suspend) state. When CLKRUNJ is active, this clock should always be running. Internal PCI state machine and ISA state machine will use this clock.                                                                                                                                                                                |

| OSC14M           | l<br>Group C                 | <b>14.318Mhz Clock Input.</b> This input clock will be used for Power Management timer, M8254 timer, SM Bus base frequency and ISA state machine. M1543C has moved this pin to Group C.                                                                                                                                                                                                                                                                                |

| OSC32KI          | I<br>Group C                 | <b>32 KHz Oscillator Input 1.</b> This is a crystal input 1 from a 32.768 KHz Quartz Crystal. The M1543C will generate the 32 KHz clock for the internal Suspend circuit and output the clock from the CLK32KO to DRAM Suspend Refresh Circuit in North Bridge. If a Crystal is not used, an external 32 KHz clock input should be connected to this pin.                                                                                                              |

| OSC32KII         | I<br>Group C                 | <b>32 KHz Oscillator Input 2.</b> This is a crystal input 2 from a 32.768 KHz Quartz Crystal. The M1543C will generate the 32 KHz clock for the internal Suspend circuit and output the clock from the CLK32KO to DRAM Suspend Refresh Circuit in North Bridge. If a Crystal is not used, this pin should be floated.                                                                                                                                                  |

| CLK32KO          | I/O<br>Group C<br>2.4/2.4 mA | <b>32 KHz Clock Output for DRAM Refresh.</b> At ON, STANDBY, SLEEP (Power On Suspend), SUSPEND (Suspend to DRAM) states, the output will send to Memory controller in North Bridge to support DRAM refresh clock. At Soft off and Suspend to Disk states, the output will drive low to avoid leakage current. This pin is also used as 32K test mode when pulled high. In normal operation, it must not be pulled high. This pin has a 40K internal pull-low resistor. |

| USBCLK           | l<br>Group B                 | <b>48 MHz USB Clock Input.</b> This clock will send to USB state machine to generate USB signals.                                                                                                                                                                                                                                                                                                                                                                      |

| PCI Bus Interfac | ce :                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PCIRSTJ          | O-Group B<br>12/16 mA        | <b>PCI Bus Reset.</b> This is an output signal to reset the entire PCI Bus. This signal will be asserted during system reset and is a logic invert of RSTDRV.                                                                                                                                                                                                                                                                                                          |

| AD[31:0]         | I/O<br>Group B<br>12/16 mA   | <b>Address and Data Multiplexed Bus.</b> During the first clock of a PCI transaction, AD[31:0] contain a physical address. During subsequent clocks, AD[31:0] contain data.                                                                                                                                                                                                                                                                                            |

| CBEJ[3:0]        | I/O-Group B<br>12/16 mA      | <b>Bus Command and Byte Enable.</b> During address phase, CBEJ[3:0] define the Bus Command. During the data phase, CBEJ[3:0] define the Byte Enables.                                                                                                                                                                                                                                                                                                                  |

| FRAMEJ           | I/O -Group B<br>12/16 mA     | <b>Cycle Frame.</b> Cycle Frame is driven by current initiator to indicate the beginning and duration of a PCI access.                                                                                                                                                                                                                                                                                                                                                 |

| TRDYJ            | I/O -Group B<br>12/16 mA     | <b>Target Ready.</b> Target Ready indicates the target's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                                                                |

| IRDYJ            | I/O-Group B<br>12/16 mA      | <b>Initiator Ready.</b> Initiator Ready indicates the initiator's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                                                       |

| STOPJ            | I/O-Group B<br>12/16 mA      | <b>Cycle Stop Request.</b> Cycle Stop indicates the target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                   |

| DEVSELJ          | I/O<br>Group B<br>12/16 mA   | <b>Device Select.</b> This signal indicates that the target device has decoded the address as its own cycle. This pin is an output pin when M1543C acts as a PCI slave, has decoded address as its own cycle including subtractive decoding.                                                                                                                                                                                                                           |

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

| Pin Name         | Туре                                | Description                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Bus Interfac | * -                                 |                                                                                                                                                                                                                                                                                                                                                                                 |

| SERRJ            | I -Group B                          | <b>System Error.</b> This signal may be pulsed active by any agent that detects a system error condition. When SERRJ is sampling low, M1543C will assert NMI to generate non-maskable interrupt to CPU.                                                                                                                                                                         |

| PAR              | I/O<br>Group B<br>12/16 mA          | <b>Parity Signal.</b> PAR is an Even Parity and is calculated on AD[31:0] and CBEJ[3:0]. When M1543C acts as a PCI master, it drives PAR one PCI clock after address phase for read/write transaction and one PCI clock after data phase for write transaction. When the M1543C acts as a target, it drives PAR one PCI clock after data phase for PCI master read transaction. |

| PHLDAJ           | I<br>Group B                        | PCI Bus Ownership Acknowledge. When PCI bus arbiter asserts this pin, M1543C has owned the PCI bus.                                                                                                                                                                                                                                                                             |

| PHOLDJ           | I/O<br>Group B<br>7.2/7.2 mA        | <b>PCI Bus Ownership Request.</b> M1543C requests the ownership of the PCI bus from the PCI bus arbiter on the North Bridge. M1543C will assert this signal on behalf of the ISA Master, DMA Device, IDE Master, and the USB Master. This signal is also used as USB test mode when it is pulled low. In normal operation, it must be pulled high.                              |

| INTAJ_MI         | l<br>Group B                        | <b>PCI INTA.</b> PCI interrupt input A or PCI interrupt polling input. M1543C can support<br>up to 8 PCI Interrupts routing by using a 74F181 to do the polling. This pin is a<br>multi-function pin: it connects to PCI INTAJ when 4 PCI Interrupts are supported,<br>or connects to the 74F181 encoded output to support the 8 PCI Interrupts polling<br>mode.                |

| INTBJS0          | I/O<br>Group B<br>Schmitt<br>4/4 mA | <b>PCI INTB.</b> PCI interrupt input B or polling select_0 output. M1543C can support<br>up to 8 PCI Interrupts routing by using a 74F181 to do the polling. This pin is a<br>multi-function pin: it connects to PCI INTBJ when 4 PCI Interrupts are supported,<br>or connects to the 74F181 selection input 0 to support the 8 PCI Interrupts polling<br>mode.                 |

| INTCJS1          | I/O<br>Group B<br>Schmitt<br>4/4 mA | <b>PCI INTC.</b> PCI interrupt input C or polling select_1 output. M1543C can support<br>up to 8 PCI Interrupts routing by using a 74F181 to do the polling. This pin is a<br>multi-function pin: it connects to PCI INTCJ when 4 PCI Interrupts are supported,<br>or connects to the 74F181 selection input 1 to support the 8 PCI Interrupts polling<br>mode.                 |

| INTDJS2          | I/O<br>Group B<br>Schmitt<br>4/4 mA | <b>PCI INTD.</b> PCI interrupt input D or polling select_2 output. M1543C can support<br>up to 8 PCI Interrupts routing by using a 74F181 to do the polling. This pin is a<br>multi-function pin: it connects to PCI INTDJ when 4 PCI Interrupts are supported,<br>or connects to the 74F181 selection input 2 to support the 8 PCI Interrupts polling<br>mode.                 |

| CPU interface :  | ·                                   |                                                                                                                                                                                                                                                                                                                                                                                 |

| INIT             | O<br>Group E<br>2.4/2.4 mA          | <b>CPU Initialize Interrupt.</b> CPU cold & warm reset. When CPU is Pentium II (XDIR is pulled low), this signal is low active. Otherwise (XDIR is pulled high), this signal is high active. When power on, KBC RC, port 92 RC, shutting down all will trigger INIT active.                                                                                                     |

| CPURST           | O-Group E<br>2.4/2.4 mA             | <b>CPU Cold Reset.</b> When power turns on, this reset signal will be asserted, and then will become de-asserted until 4 ms after PWG becomes high.                                                                                                                                                                                                                             |

| IGNNEJ           | O-Group E<br>2.4/2.4 mA             | <b>Ignore Error.</b> This pin is used as the ignore numeric coprocessor error and connects to CPU.                                                                                                                                                                                                                                                                              |

| INTR             | O-Group E<br>2.4/2.4 mA             | <b>Interrupt Request to CPU.</b> This is the interrupt signal generated by the internal 8259 and should connect to CPU INTR as a maskable interrupt.                                                                                                                                                                                                                            |

| NMI              | O-Group E<br>2.4/2.4 mA             | <b>Non-maskable Interrupt to CPU.</b> This is generated by the ISA Parity error (IOCHKJ assertion), PCI Parity error or DRAM Parity error (SERRJ assertion), and the other internal error event. This output should connect to CPU NMI as a non-maskable interrupt.                                                                                                             |

| A20MJ            | O-Group E<br>2.4/2.4 mA             | CPU A20 Mask. This is the CPU Address line A20 mask signal.                                                                                                                                                                                                                                                                                                                     |

| FERRJ/<br>IRQ13  | I<br>Group E                        | <b>Floating Point Error.</b> FERRJ input to generate IRQ13. When coprocessor interface is disabled through configuration register Index-43h bit 6 setting, the function of this pin is IRQ13.                                                                                                                                                                                   |

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR

| Pin Name                                                                            | Туре                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISA Bus Interface                                                                   | :                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IRQ[15]/<br>AGP_INTBJ,<br>IRQ[14]/<br>AGP_INTAJ,<br>IRQ[11],<br>IRQ[9],<br>IRQ[7:3] | I/O<br>Group A<br>Schmitt<br>9.6/9.6 mA | <b>Interrupt Request.</b> The Interrupt Request lines are directly from the ISA Bus, from the PCI Interrupt Routing, or from the steerable Interrupt pins. IRQ14 & IRQ15 can be connected to AGP two Interrupts AGP_INTAJ and AGP_INTBJ. Through M1543C register Index-4Bh Bits[7:0], they can also route to any available Interrupt lines.                                                                                                                                                                                                                                                                                                                                                                                            |

| IRQ[10]/<br>KBDATA                                                                  | I/O<br>Group C<br>Schmitt<br>9.6/9.6 mA | <b>Interrupt Request Line 10 or Keyboard Data.</b> This pin is a multi-function pin. When pin PCSJ is pulled high which means Hotkey function is disabled, this pin is IRQ[10] as the Interrupt Request Line 10. When pin PCSJ is pulled low which means Hotkey function is enabled, this pin will become KBDATA and should                                                                                                                                                                                                                                                                                                                                                                                                            |

| RSTDRV                                                                              | O-Group A<br>12/16mA                    | <ul> <li>connect to Keyboard. (please see 5.4.1)</li> <li><b>ISA Bus Reset.</b> This output is used to reset the ISA Bus and the system device. This pin will be active if the system reset is needed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SD[15:8]                                                                            | I/O-Group A<br>12/12 mA                 | <b>ISA High Byte Slot Data Bus.</b> These pins should connect to the ISA High Byte Slot Data Bus. These pins can also be used to extend GPI. Please refer to section 1.4 for more detailed information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

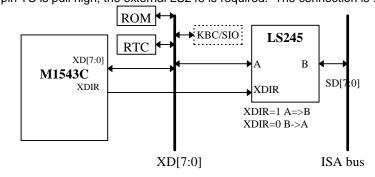

| XD[7:0]                                                                             | I/O<br>Group A<br>12/12 mA              | <b>XD Data Bus.</b> When the SD[7:0] pins are defined as GPIO[7:0] pins, these pins can be used to drive SD[7:0] if TTL LS245 is used as a buffer. The M1543C signal XDIR will control this buffer. Also these pins can also be used to extend GPIO signals. Please refer to section 1.4 for more detailed implementation.                                                                                                                                                                                                                                                                                                                                                                                                             |

| SD[7]/<br>GPIO[7]/<br>PWR_EN                                                        | I/O<br>Group A<br>12/12 mA              | <b>ISA Low Byte Slot Data Bus Line 7 or General Purpose I/O or USB Power Enable.</b> This pin is a multi-function pin selected by hardware and software setting. When pin TC is pulled low, SD[7] is selected. No external LS245 TTL is required to support SD[7:0] bus. When pin TC is pulled high, GPIO[7]/PWR_EN functions are selected. In this hardware configuration, external SD[7:0] bus is supported by the XD[7:0] bus through a LS245 TTL. GPIO[7] or PWR_EN are chosen through M1543C register Index-72h bit6 setting. When this bit is reset as 0, GPIO[7] is chosen for green or system event control. When this bit is set as 1, PWR_EN is chosen to control the USB Power enable.                                      |

| SD[6]/<br>GPIO[6]                                                                   | I/O<br>Group A<br>12/12 mA              | <b>ISA Low Byte Slot Data Bus Line 6 or General Purpose I/O.</b> This pin is a multi-<br>function pin selected by hardware setting. When pin TC is pulled low, SD[6] is<br>selected. No external LS245 TTL is required to support SD[7:0] bus. When pin TC<br>is pulled high, GPIO[6] is selected for green or system event control. M1543C<br>register Index-75h bit6 must be reset as 0 for GPIO[6] support. In this hardware<br>configuration, external SD[7:0] bus is supported by the XD[7:0] bus through a<br>LS245 TTL.                                                                                                                                                                                                         |

| SD[5]/<br>GPIO[5]/<br>USBP2-                                                        | I/O<br>Group A<br>12/12 mA              | ISA Low Byte Slot Data Bus Line 5 or General Purpose I/O or USB Port2 Data<br>Signal. This pin is a multi-function pin selected by hardware and software setting.<br>When pin TC is pulled low, SD[5] is selected. No external LS245 TTL is required to<br>support SD[7:0] bus. When pin TC is pulled high, GPIO[5]/USBP2- functions are<br>selected. In this hardware configuration, external SD[7:0] bus is supported by the<br>XD[7:0] bus through a LS245 TTL. GPIO[5] or USBP2- are chosen through M5237<br>register Index-40h bit26 setting. When this bit is reset as 0, GPIO[5] is chosen for<br>green or system event control. When this bit is set as 1, USBP2- is chosen to<br>support USB Port2 data signal.               |

| SD[4]/<br>GPIO[4]/<br>USBP2+                                                        | I/O<br>Group A<br>12/12 mA              | <b>ISA Low Byte Slot Data Bus Line 4 or General Purpose I/O or USB Port2 Data</b><br><b>Signal.</b> This pin is a multi-function pin selected by hardware and software setting.<br>When pin TC is pulled low, SD[4] is selected. No external LS245 TTL is required to<br>support SD[7:0] bus. When pin TC is pulled high, GPIO[4]/USBP2+ functions are<br>selected. In this hardware configuration, external SD[7:0] bus is supported by the<br>XD[7:0] bus through a LS245 TTL. GPIO[4] or USBP2+ are chosen through M5237<br>register Index-40h bit26 setting. When this bit is reset as 0, GPIO[4] is chosen for<br>green or system event control. When this bit is set as 1, USBP2+ is chosen to<br>support USB Port2 data signal. |

Data Sheet

| Pin Name                     | Туре                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ISA Bus Interfac             | ISA Bus Interface :        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SD[3]/<br>GPIO[3]/<br>CVROFF | I/O<br>Group A<br>12/12 mA | ISA Low Byte Slot Data Bus Line 3 or General Purpose I/O or Infrared Mode<br>Switching. This pin is a multi-function pin selected by hardware and software<br>setting. When pin TC is pulled low, SD[3] is selected. No external LS245 TTL is<br>required to support SD[7:0] bus. When pin TC is pulled high, GPIO[3]/CVROFF<br>functions are selected. In this hardware configuration, external SD[7:0] bus is<br>supported by the XD[7:0] bus through a LS245 TTL. GPIO[3] or CVROFF are<br>chosen through M1543C register Index-6Dh bit4 setting. When this bit is reset as<br>0, GPIO[3] is chosen for green or system event control. When this bit is set as 1,<br>CVROFF is chosen to support Infrared. This pin is used in IBM like module to<br>control the speed of the module.                                                                                                                                                          |  |  |

| SD[2]/<br>GPIO[2]/<br>IRRX   | I/O<br>Group A<br>12/12 mA | ISA Low Byte Slot Data Bus Line 2 or General Purpose I/O or Infrared<br>Receive. This pin is a multi-function pin selected by hardware and software<br>setting. When pin TC is pulled low, SD[2] is selected. No external LS245 TTL is<br>required to support SD[7:0] bus. When pin TC is pulled high, GPI0[2]/IRRX<br>functions are selected. In this hardware configuration, external SD[7:0] bus is<br>supported by the XD[7:0] bus through a LS245 TTL. GPI0[2] or IRRX are chosen<br>through M1543C register Index-6Dh bit4 setting. When this bit is reset as 0,<br>GPI0[2] is chosen for green or system event control. When this bit is set as 1,<br>IRRX is chosen to support Infrared. This pin is used as Infrared serial data input<br>signal.                                                                                                                                                                                        |  |  |

| SD[1]/<br>GPIO[1]/<br>IRRXH  | I/O<br>Group A<br>12/12 mA | ISA Low Byte Slot Data Bus Line 1 or General Purpose I/O or Infrared<br>Control Signal. This pin is a multi-function pin selected by hardware and<br>software setting. When pin TC is pulled low, SD[1] is selected. No external LS245<br>TTL is required to support SD[7:0] bus. When pin TC is pulled high,<br>GPIO[1]/IRRXH functions are selected. In this hardware configuration, external<br>SD[7:0] bus is supported by the XD[7:0] bus through a LS245 TTL. GPIO[1] or<br>IRRXH are chosen through M1543C register Index-6Dh bit4 setting. When this bit<br>is reset as 0, GPIO[1] is chosen for green or system event control. When this bit is<br>set as 1, IRRXH is chosen to support Infrared. In HP like transceiver module, this<br>is the high speed receiver signal input (1 to 4 Mb/s). In IBM like transceiver<br>module, this is an output signal to control the SD/MODE signal which will control<br>the speed of the module. |  |  |

| SD[0]/<br>GPIO[0]/<br>IRTX   | I/O<br>Group A<br>12/12 mA | ISA Low Byte Slot Data Bus Line 0 or General Purpose I/O or Infrared<br>Transmit. This pin is a multi-function pin selected by hardware and software<br>setting. When pin TC is pulled low, SD[0] is selected. No external LS245 TTL is<br>required to support SD[7:0] bus. When pin TC is pulled high, GPI0[0]/IRTX<br>functions are selected. In this hardware configuration, external SD[7:0] bus is<br>supported by the XD[7:0] bus through a LS245 TTL. GPI0[0] or IRTX are chosen<br>through M1543C register Index-6Dh bit4 setting. When this bit is reset as 0,<br>GPI0[0] is chosen for green or system event control. When this bit is set as 1,<br>IRTX is chosen to support Infrared. This pin is used as Infrared serial data output<br>signal.                                                                                                                                                                                      |  |  |

| SA[19:17]                    | O-Group A<br>12/12 mA      | <b>ISA Slot Address Bus A19-A17.</b> These pins should connect to the ISA System Address Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SA[16:0]                     | I/O-Group A<br>12/12 mA    | <b>ISA Slot Address Bus A16-A0.</b> These pins should connect to the ISA System Address Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| SBHEJ                        | I/O -Group A<br>12/12 mA   | <b>ISA Byte High Enable.</b> This pin should connect to the ISA System Byte High Enable pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

M1543C : PCI-ISA Bus Bridge with Super I/O & Fast IR