### M1523B: PCI-to-ISA Bus Bridge

### The shaded areas in this document highlight the differences between the M1523 and the M5123B.

### **Section 1: Introduction**

#### 1.1 Features

- Provides a bridge between the PCI bus and ISA bus

- PCI interface

- Supports PCI Master and Slave Interface

- Supports PCI Master and Slave initiated termination

- PCI specification 2.1 Compliant (Delay transaction support)

- Buffers

- 8-byte bidirectional Line Buffers are provided for DMA/ISA Memory Read/Write cycles to PCI Bus.

- 32-bit Posted Write Buffer is provided for PCI Memory Write and I/O data write (for sound card) to ISA bus.

- Provides steerable PCI interrupts for PCI device plugand-play

- Up to 8 PCI interrupts routing

- Level to edge trigger transfer

- Enhanced DMA Controller

- Provides 7 programmable channels, 4 for 8-bit data size, 3 for 16-bit data size

- 32-bit addressability

- Provides Compatible DMA transfers

- Provides Type F transfers

- Interrupt Controller

- Provides 14 interrupt channels

- Independently programmable Level/Edge triggered channels

- Counter/Timers

- Provides 8254 compatible timers for System timer, Refresh Request, Speaker Output use

- Keyboard controller

- Built-in PS2/AT Keyboard controller

- The specific I/O is used to save the external TTL buffer

- Distributed DMA support

- 7 DMA channels can be arbitrarily programmed as distributed channel

- Serialized IRQ support

- Quiet /Continuous mode

- 17 IRQ/Data frames

- Programmable START frame pulse width

- Plug-and-Play Port supports

- 1 programmable chip select

- 2 Steerable Interrupt Request lines

- PMU interface

- Supports CPU SMM mode, SMI feature

- Supports programmable stop clock throttle

- Supports the APM control

- Provides External Suspend mode Switch/Turbo switch/Ring in switch

- Provides 4 system states for power saving (On, Doze, Standby, Suspend)

- Provides 3 timers from 1 second to 300 minutes to individually monitor VGA, MODE, IN status

Supports RTC alarm wake up control

- IDE interface

- Built-in PCI IDE master controller

- Supports PIO modes up to mode 5 timings, and multiword DMA mode 0, 1, 2

- 8 x 32-bit pre-read & posted write buffers

- Dedicated pins for ATA interface

- Supports up to 256 KB ROM size decode

- Supports Universal Serial Bus interface

- Supports 2 USB ports

- OpenHCI specification 1.0a compliant

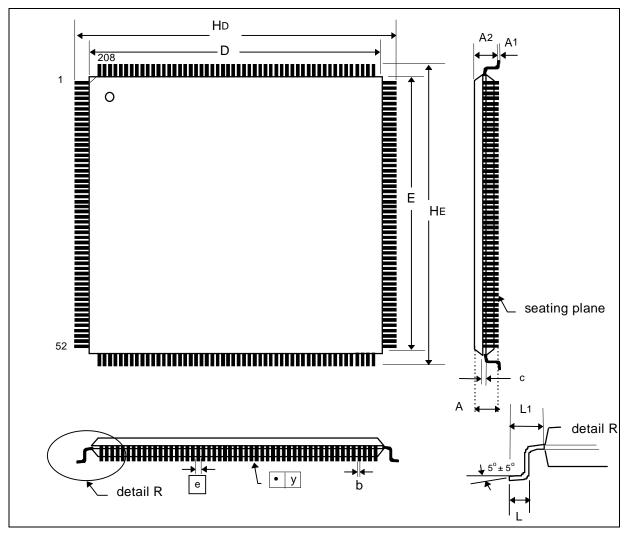

- 208-pin PQFP package

### Table of Contents:

| Section 1: Introduction                        | . 1  |

|------------------------------------------------|------|

| 1.1 Features of M1523B                         |      |

| 1.2 Functions                                  | . 3  |

|                                                |      |

| Section 2: Pin Description                     | . 4  |

| 2.1 Pin Diagram                                | . 4  |

| 2.2 Pin Description Table                      |      |

| 2.3 Numerical Pin List                         |      |

| 2.4 Alphabetical Pin List                      | . 11 |

| 2.5 Hardware Setup Control                     |      |

| Section 3: Function Description                | . 14 |

| 3.1 PCI Command Set                            |      |

| 3.2 Description of PCI Slave                   | . 14 |

| 3.3 PCI Master                                 | . 14 |

| 3.4 Parity Support                             | . 15 |

| 3.5 Address Decoding                           | . 15 |

| 3.6 IDE Master Controller                      |      |

| 3.7 Power Management                           | . 16 |

| Section 4: Configuration Registers             | . 17 |

| 4.1 Register Description                       |      |

| 4.2 DMA Register Description                   | . 57 |

| 4.3 Timer Unit Register Description            |      |

| 4.4 Interrupt Unit Register Description        | . 58 |

| 4.5 NMI Registers                              | . 59 |

| 4.6 Fast RC/Gate - A20 Registers               |      |

| 4.7 ISA Compatible Registers Summary           | . 61 |

| Section 5: Programming Guide                   | . 63 |

| 5.1 PMU Programming Guide                      |      |

| 5.2 PCI - Interrupt Mapping Programming Guide  | . 65 |

| Section 6: Electrical Characteristics          | . 66 |

| 6.1 DC Specifications                          |      |

| 6.2 AC Specifications                          |      |

| Section 7: Packaging Information               | . 69 |

| Section 8: Differences between M1523A & M1523B | . 70 |

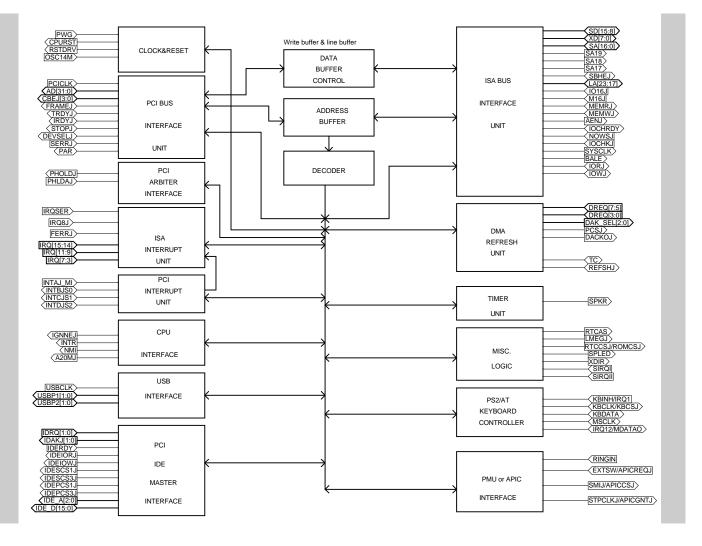

#### 1.2 Functions

The M1523B is a bridge between PCI and ISA bus, providing full PCI and ISA compatible functions. The M1523B has Integrated System Peripherals (ISP) on chip and provides advanced features in the DMA controller. The keyboard controller and IDE Master Controller are also included in this chip. Furthermore, this chip supports the Advanced Programmable Interrupt controller (APIC) interface.

One eight byte bi-directional line buffer is provided for ISA/DMA Master memory read/writes. One 32-bit wide posted write buffer is provided for PCI memory write cycles to the ISA bus. Provides a PCI to ISA IRQ routing table, and level to edge trigger transfer.

The chip provides 2 extra IRQ lines and 1 programmable chip select for motherboard Plug-and-Play functions. The interrupt lines can be routed to any of the available ISA interrupts.

The on-chip IDE controller supports two IDE connectors for up to 4 IDE devices providing an interface for IDE hard disks and CD ROMs. The ATA bus pins are dedicated to improve the performance of IDE Master.

The M1523B supports Super Green for Intel and Intel compatible CPUs. It implements programmable hardware events, software event and external switches (for suspend/turbo/ring-in). The M1523B provides CPU clock control (STPCLKJ). The STPCLKJ can be active (low) or inactive (high) in turn by throttling control.

### Section 2 : Pin Description

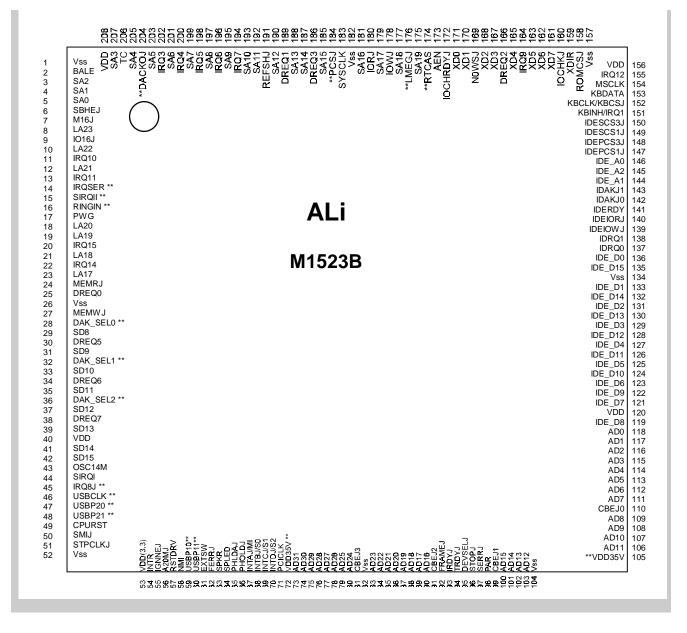

### 2.1 Pin Diagram

Note : \*\* Pin Changes

Figure 2-1. Pinout Diagram

### 2.2 Pin Description Table:

| Pin Name        | Pin No.                                             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------|-----------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock & Reset   | •                                                   |      | · ·                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PWG             | 17                                                  | I    | <b>Power-Good Input.</b> This signal comes from the power supply to indicate that power is available and stable.                                                                                                                                                                                                                                                                              |  |

| CPURST          | 49                                                  | 0    | CPU RESET includes Cold & Warm reset 3.3V signal (connected to CPU INIT)                                                                                                                                                                                                                                                                                                                      |  |

| RSTDRV          | 57                                                  | 0    | CPU cold reset. 3.3V signal (connected to CPU RESET)                                                                                                                                                                                                                                                                                                                                          |  |

| OSC14M          | 43                                                  | 1    | 14.318Mhz clock input. This is used for 8254 timer clock.                                                                                                                                                                                                                                                                                                                                     |  |

| PCI Interface   |                                                     |      |                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PCICLK          | 71                                                  | 1    | PCI clock for internal PCI interface.                                                                                                                                                                                                                                                                                                                                                         |  |

| AD[31:0]        | 73-80,<br>83-90,<br>100-104,<br>106-109,<br>111-118 | I/O  | Address and Data are multiplexed on PCI bus. During the first clock of a PCI transaction, AD[31-0] contains a physical address. During subsequent clocks, AD[31-0] contains data.                                                                                                                                                                                                             |  |

| C/BEJ[3:0]      | 81,91,<br>99,110                                    | I/O  | <b>Bus Command and Byte enable.</b> During address phase, CBEJ[3:0] define the Bus Command. During data phase, CBEJ[3:0] define the Byte Enables.                                                                                                                                                                                                                                             |  |

| FRAMEJ          | 92                                                  | I/O  | <b>Cycle Frame</b> is driven by current initiator to indicate the beginning and duration of an access.                                                                                                                                                                                                                                                                                        |  |

| DEVSELJ         | 95                                                  | I/O  | <b>Device Select</b> . This indicates that the target device has decoded the address as its own cycle. This pin is an output pin when the M1523B acts as a PCI slave that has decoded address as its own cycle including subtractive decoding.                                                                                                                                                |  |

| IRDYJ           | 93                                                  | I/O  | <b>Initiator Ready</b> indicates the initiator's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                               |  |

| TRDYJ           | 94                                                  | I/O  | <b>Target Ready</b> indicates the target's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                     |  |

| STOPJ           | 96                                                  | I/O  | <b>Stop</b> indicates to the M1523B is requesting a master to stop the current transaction.                                                                                                                                                                                                                                                                                                   |  |

| PAR             | 98                                                  | I/O  | <b>Parity signal.</b> PAR is even parity and is calculated on AD[31:0] and CBEJ[3:0<br>When the M1523B acts as a PCI master, it drives PAR one PCI clock after<br>address phase for a read/write transaction and one PCI clock after data phase<br>for a write transaction. When the M1523B acts as target, it drives PAR one PC<br>clock after data phase for a PCI master read transaction. |  |

| SERRJ           | 97                                                  | I    | <b>System Error</b> may be pulsed active by any agent that detects a system error condition. When SERRJ is sampled low, the M1523B will assert NMI to interrupt the CPU.                                                                                                                                                                                                                      |  |

| PCI Interrupt U | nit                                                 |      |                                                                                                                                                                                                                                                                                                                                                                                               |  |

| INTAJ_MI        | 67                                                  | 1    | PCI interrupt input A or PCI interrupt polling input.                                                                                                                                                                                                                                                                                                                                         |  |

| INTBJ           | 68                                                  | I/O  | PCI interrupt input B or polling select_0 output.                                                                                                                                                                                                                                                                                                                                             |  |

| INTCJ           | 69                                                  | I/O  | PCI interrupt input C or polling select_1 output.                                                                                                                                                                                                                                                                                                                                             |  |

| INTDJ           | 70                                                  | I/O  | PCI interrupt input D or polling select_2 output.                                                                                                                                                                                                                                                                                                                                             |  |

| PCI Arbiter     |                                                     |      |                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PHOLDJ          | 66                                                  | 0    | M1523B requests the ownership of the PCI bus.                                                                                                                                                                                                                                                                                                                                                 |  |

| PHLDAJ          | 65                                                  | I    | <b>PCI Hold Acknowledge</b> . When this pin is asserted, the M1523B owns the PCI bus.                                                                                                                                                                                                                                                                                                         |  |

### Pin Description Table (continued)

| Pin Name                              | Pin No.                                                                                            | Туре | Description                                                                                                                                                                                                                                                                                                        |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU Interface (3.3                    | V)                                                                                                 |      |                                                                                                                                                                                                                                                                                                                    |  |

| IGNNEJ                                | 55                                                                                                 | 0    | Ignore Numeric Error. This pin is used as the ignore numeric coprocessor error.                                                                                                                                                                                                                                    |  |

| INTR                                  | 54                                                                                                 | 0    | <b>Interrupt request to CPU.</b> This is the interrupt signal generated by the internal 8259.                                                                                                                                                                                                                      |  |

| NMI                                   | 58                                                                                                 | 0    | Non-maskable interrupt. This is non-maskable interrupt request to CPU.                                                                                                                                                                                                                                             |  |

| A20MJ                                 | 56                                                                                                 | 0    | CPU A20 Mask. This is the Address line 20 mask signal.                                                                                                                                                                                                                                                             |  |

| ISA Interface                         |                                                                                                    | -    |                                                                                                                                                                                                                                                                                                                    |  |

| FERRJ/IRQ13                           | 62                                                                                                 | I    | <b>Floating point error.</b> FERRJ input to generate IRQ13. When the coprocessor interface is disabled in configuration port 43h bit 6, the function of this pin is IRQ13.                                                                                                                                         |  |

| IRQ12/MDATAO                          | 155                                                                                                | В    | <b>Mouse Interrupt request input/Mouse data output</b> when internal PS/2 keyboard is disabled, this pin is mouse interrupt input. Otherwise, this pin is mouse data output.                                                                                                                                       |  |

| IRQ[15:14],<br>IRQ[11:9],<br>IRQ[7:3] | 20,22,13,<br>11,164,<br>194,196,<br>200,202                                                        | Ι    | Interrupt Request signals.                                                                                                                                                                                                                                                                                         |  |

| SD[15:8]                              | 42,41,39,<br>37,35,33,<br>31,29                                                                    | I/O  | ISA high byte Slot Data bus. These lines are system data lines.                                                                                                                                                                                                                                                    |  |

| XD[7:0]                               | 161-163,<br>165,167,<br>168,<br>170-171                                                            | I/O  | <b>External Data bus</b> lines are connected to SD[7:0] by an external TTL LS245, whose direction is controlled by the M1523B output signal XDIR.                                                                                                                                                                  |  |

| SA19                                  | 175                                                                                                | 0    | ISA Slot Address Bus A19.                                                                                                                                                                                                                                                                                          |  |

| SA18                                  | 177                                                                                                | 0    | ISA Slot Address Bus A18.                                                                                                                                                                                                                                                                                          |  |

| SA17                                  | 179                                                                                                | 0    | ISA Slot Address Bus A17.                                                                                                                                                                                                                                                                                          |  |

| SA[16:0]                              | 181, 185,<br>187, 188,<br>190, 192,<br>193, 195,<br>197, 199,<br>201, 203,<br>205, 207,<br>3, 4, 5 | I/O  | <b>ISA Slot Address bus.</b> These lines are addresses connected to slot address.                                                                                                                                                                                                                                  |  |

| SBHEJ                                 | 6                                                                                                  | I/O  | <b>ISA slot Byte high enable.</b> In a CPU or PCI master cycle, this signal is generated by BE3J-BE0J and the chip's internal control circuit. In a DMA cycle, it is generated by internal 8237. In a refresh cycle, it is generated by the internal refresh circuits. It is an input signal for ISA master cycle. |  |

| LA[23:17]                             | 8,10,12,<br>18,19,21,<br>23                                                                        | I/O  | <b>ISA Latched Address bus.</b> They are input during ISA master cycle.                                                                                                                                                                                                                                            |  |

| IO16J                                 | 9                                                                                                  | I    | <b>ISA 16-bit I/O device indicator.</b> This signal indicates the I/O device supports 16-bit transfers.                                                                                                                                                                                                            |  |

| M16J                                  | 7                                                                                                  | I/O  | <b>ISA 16-bit memory device indicator.</b> This signal indicates the memory device supports 16-bit transfers.                                                                                                                                                                                                      |  |

| MEMRJ                                 | 24                                                                                                 | I/O  | <b>ISA memory read.</b> This signal is an input during ISA master cycle.                                                                                                                                                                                                                                           |  |

| MEMWJ                                 | 27                                                                                                 | I/O  | <b>ISA memory write.</b> This signal is an input during ISA master cycle.                                                                                                                                                                                                                                          |  |

### Pin Description Table (continued)

| Pin Name             | Pin No.   | Туре   | Description                                                                                           |  |

|----------------------|-----------|--------|-------------------------------------------------------------------------------------------------------|--|

| ISA Interface        |           | -      |                                                                                                       |  |

| AEN                  | 173       | 0      | ISA I/O address enable. Active high signal during DMA cycle to prevent I/O                            |  |

|                      |           |        | device from misinterpreting the DMA cycle as valid I/O cycle.                                         |  |

| IOCHRDY              | 172       | I/O    | <b>ISA system ready.</b> This signal is an output during ISA/DMA master cycle.                        |  |

| NOWSJ                | 169       | I      | ISA zero wait-state for input. This signal terminates the CPU to ISA                                  |  |

|                      | _         |        | command instantly.                                                                                    |  |

| IOCHKJ               | 160       | 1      | <b>ISA parity error.</b> M1523B will generate NMI to CPU when this signal is                          |  |

| 0.10.01.17           |           | -      | asserted.                                                                                             |  |

| SYSCLK               | 183       | 0      | ISA system clock. This signal provides clocking function to ISA bus.                                  |  |

| BALE                 | 2         | 0      | <b>Bus Address Latch Enable.</b> BALE is active throughout DMA and ISA master and refresh cycles.     |  |

| IORJ                 | 180       | I/O    | ISA I/O read. This signal is an input during ISA master cycle.                                        |  |

| IOWJ                 | 178       | I/O    | ISA I/O write. This signal is an input during ISA master cycle.                                       |  |

| LMEGJ                | 176       | 0      | Low Megabyte. This pin indicates an ISA address below 1 Mbyte.                                        |  |

| RTCAS                | 174       | 0      | RTC Address Strobe. This pin is active when ISA I/O address 70h or 72h                                |  |

|                      |           |        | are decoded.                                                                                          |  |

| DREQJ[7:5]           | 38,34,30, | Ι      | DMA request signals. These are DMA request input signals.                                             |  |

| DREQJ[3:0]           | 186,166,  |        |                                                                                                       |  |

|                      | 189,25    | -      |                                                                                                       |  |

| DAK_SEL[2:0]         | 36,32,28, | 0      | These pins are DAK_SEL[2:0](O) (connected to external multiplexer's select                            |  |

| PCSJ,<br>DACKOJ      | 184,      |        | inputs), PCSJ(O) (programmable chip select), DACKOJ(O) (connected to                                  |  |

| DACKUJ               | 204       |        | external multiplexer's chip enable).                                                                  |  |

| ТС                   | 206       | 0      | DMA end of process. Hardware setting option:                                                          |  |

|                      |           | -      | Pull low : Support external I/O APIC mode                                                             |  |

|                      |           |        | Pull high : Not support external I/O APIC                                                             |  |

| REFSHJ               | 191       | I/O    | <b>ISA Refresh cycle.</b> This signal is input during ISA master cycles, but an output                |  |

|                      |           |        | during other cycles.                                                                                  |  |

| Timer                |           |        |                                                                                                       |  |

| SPKR                 | 43        | 0      | Speaker output. Hardware setting option :                                                             |  |

|                      |           |        | Pull low: Enable Internal KBC                                                                         |  |

|                      |           |        | Pull high: Disable Internal KBC                                                                       |  |

| Miscellaneous        | 44        |        |                                                                                                       |  |

| SPLED                | 44        | 0      | Speed LED output. This signal must be pulled low.                                                     |  |

| ROMCSJ               | 158       | 0      | <b>ROM &amp; RTC chip select.</b> This signal must be pulled high for normal operation.               |  |

| XDIR                 | 159       | 0      | X-bus direction control. Hardware setting option: must be pulled high.                                |  |

| KBINH/ IRQ1          | 151       | I      | KB inhibit input when the internal KBC is enabled                                                     |  |

|                      | 450       | 1/0    | IRQ1 input when the internal KBC is disabled                                                          |  |

| KBCLK/ KBCSJ         | 152       | I/O    | KB interface CLK when the internal KBC is enabled<br>KB Chip Select when the internal KBC is disabled |  |

| KBDATA               | 153       | 0      | KB interface Data when the internal KBC is enabled                                                    |  |

| MSCLK                | 153       | 0      | Mouse clock output when the internal KBC is enabled.                                                  |  |

| RINGIN               | 16        |        | RING INPUT of PMU function.                                                                           |  |

| SIRQI                | 44        |        | Steerable IRQ input 1                                                                                 |  |

| SIRQII               | 15        | 1      | Steerable IRQ input 2                                                                                 |  |

| IRQ8J                | 45        | 1      | RTC Interrupt input                                                                                   |  |

|                      | 14        | B      |                                                                                                       |  |

| IROSER               |           |        | Serialized IRQ pin.                                                                                   |  |

| IRQSER<br>USBCI K    |           | 1      |                                                                                                       |  |

| USBCLK<br>USBP1[1:0] | 46 59, 60 | I<br>B | Universal serial bus 48 MHz clock pin.<br>Universal serial bus data set 1, USBP1[1]=D+, USBP1[0]=D-   |  |

### Pin Description Table (continued)

| Pin Name             | Pin No.                                                                                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|---------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Manageme       | nt                                                                                          |      |                                                                                                                                                                                                                                                                                                                                                                          |

| EXTSW/<br>APICREQJ   | 61                                                                                          | 1    | <b>External SMI switch or APIC request input.</b> EXTSW is a falling edge triggered input to the M1523B showing that an external device is requesting the system to enter SMM mode. An external pullup resistor should be placed on this signal if it is not used or it is not guaranteed to be always driven. When external APIC mode is enabled, this pin is APICREQJ. |

| SMIJ/ APICCSJ        | 50                                                                                          | 0    | <b>SMM interrupt or APIC chip select</b> . a synchronous output that is asserted by the M1523B in response to one of many enabled hardware or software events. When external APIC mode is enabled, this pin is APICCSJ.                                                                                                                                                  |

| STPCLKJ/<br>APICGNTJ | 51                                                                                          | 0    | <b>Stop CPU clock request or APIC grant output</b> . STPCLKJ is connected directly to the CPU and is synchronous with PCI clock. When external APIC mode is enabled, this pin is APICGNTJ.                                                                                                                                                                               |

| IDE Interface        |                                                                                             |      |                                                                                                                                                                                                                                                                                                                                                                          |

| IDRQ[1:0]            | 138-137                                                                                     | 1    | IDE DRQ request for IDE master.                                                                                                                                                                                                                                                                                                                                          |

| IDAKJ[1:0]           | 143-142                                                                                     | 0    | IDE DACKJ for IDE master.                                                                                                                                                                                                                                                                                                                                                |

| IDERDY               | 141                                                                                         | 1    | IDE ready.                                                                                                                                                                                                                                                                                                                                                               |

| IDEIORJ              | 140                                                                                         | 0    | IDE IORJ command.                                                                                                                                                                                                                                                                                                                                                        |

| IDEIOWJ              | 139                                                                                         | 0    | IDE IOWJ command.                                                                                                                                                                                                                                                                                                                                                        |

| IDESCS1J             | 149                                                                                         | 0    | IDE chip select for secondary channel 0                                                                                                                                                                                                                                                                                                                                  |

| IDESCS3J             | 150                                                                                         | 0    | IDE chip select for secondary channel 1                                                                                                                                                                                                                                                                                                                                  |

| IDEPCS1J             | 147                                                                                         | 0    | IDE chip select for primary channel 0                                                                                                                                                                                                                                                                                                                                    |

| IDEPCS3J             | 148                                                                                         | 0    | IDE chip select for primary channel 1                                                                                                                                                                                                                                                                                                                                    |

| IDE_A[2:0]           | 145,144,<br>146                                                                             | 0    | IDE ATA address bus.                                                                                                                                                                                                                                                                                                                                                     |

| IDE_D[15:0]          | 135,132,<br>130,128,<br>126,124,<br>122,119,<br>121,123,<br>125,127,<br>129,131,<br>133,136 | Ι/Ο  | IDE ATA data bus.                                                                                                                                                                                                                                                                                                                                                        |

| VCC & Vss            |                                                                                             |      |                                                                                                                                                                                                                                                                                                                                                                          |

| VCC3                 | 53                                                                                          | Р    | Vcc 3.3V                                                                                                                                                                                                                                                                                                                                                                 |

| VDD35                | 72,105                                                                                      | Р    | <b>VDD 3.3V/5V.</b> PCI bus output is 3.3V, if VDD35 is 3.3 volts, 3.8V if VDD35 is 5 volts.                                                                                                                                                                                                                                                                             |

| VCC5                 | 40, 72,<br>105, 120,<br>156, 208                                                            | Р    | VCC 5.0V(VDD)                                                                                                                                                                                                                                                                                                                                                            |

| Vss                  | 1, 26,<br>52, 82,<br>104, 134,<br>157, 182                                                  | Ρ    | Vss or Ground.                                                                                                                                                                                                                                                                                                                                                           |

### 2.3 Numerical Pin List

| Pin No. | Туре   | Pin Name |

|---------|--------|----------|

| 1       | P      | Vss      |

| 2       | 0      | BALE     |

| 3       | В      | SA2      |

| 4       | В      | SA1      |

| 5       | В      | SA0      |

| 6       | В      | SBHEJ    |

| 7       | В      | M16J     |

| 8       | B      | LA23     |

| 9       | 1      | IO16J    |

| 10      | B      | LA22     |

| 11      | 1      | IRQ10    |

| 12      | B      | LA21     |

| 13      | ī      | IRQ11    |

| 14      | В      | IRQSER   |

| 15      | 1      | SIRQII   |

| 16      | 1      | RINGIN   |

| 17      | 1      | PWG      |

| 18      | B      | LA20     |

| 19      | B      | LA19     |

| 20      | I      | IRQ15    |

| 20      | B      | LA18     |

| 22      | 1      | IRQ14    |

| 22      | B      | LA17     |

| 23      | В      | MEMRJ    |

|         |        |          |

| 25      | I<br>P | DREQ0    |

| 26      | -      | VSS      |

| 27      | B      | MEMWJ    |

| 28      | 0      | DAK_SEL0 |

| 29      | В      | SD8      |

| 30      | 1      | DREQ5    |

| 31      | B      | SD9      |

| 32      | 0      | DAK_SEL1 |

| 33      | В      | SD10     |

| 34      |        | DREQ6    |

| 35      | B      | SD11     |

| 36      | 0      | DAK_SEL2 |

| 37      | В      | SD12     |

| 38      | -      | DREQ7    |

| 39      | В      | SD13     |

| 40      | Р      | VDD      |

| 41      | В      | SD14     |

| 42      | В      | SD15     |

| 43      | 1      | OSC14M   |

| 44      | 1      | SIRQI    |

| 45      | 1      | IRQ8J    |

| 46      | 1      | USBCLK   |

| 47      | В      | USBP20   |

| 48      | В      | USBP21   |

| 49      | 0      | CPURST   |

| 50      | 0      | SMIJ     |

| Pin No. | Туре | Pin Name     |

|---------|------|--------------|

| 51      | 0    | STPCLKJ      |

| 52      | P    | VSS          |

| 53      | P    | VDD3V        |

| 54      | 0    | INTR         |

| 55      | 0    | IGNNEJ       |

| 56      | 0    | A20MJ        |

| 57      | 0    | RSTDRV       |

| 58      | 0    | NMI          |

|         | В    | USBP10       |

| 59      | -    |              |

| 60      | В    | USBP11       |

| 61      | 1    | EXTSW        |

| 62      | 1    | FERRJ        |

| 63      | В    | SPKR         |

| 64      | В    | SPLED        |

| 65      | 1    | PHLDAJ       |

| 66      | В    | PHOLDJ       |

| 67      | 1    | INTAJ/MI     |

| 68      | В    | INTBJ/S0     |

| 69      | В    | INTCJ/S1     |

| 70      | В    | INTDJ/S2     |

| 71      | 1    | PCICLK       |

| 72      | Р    | VDD35V       |

| 73      | В    | AD31         |

| 74      | В    | AD30         |

| 75      | В    | AD29         |

| 76      | B    | AD28         |

| 77      | B    | AD27         |

| 78      | B    | AD26         |

| 79      | B    | AD20<br>AD25 |

|         | B    | AD23<br>AD24 |

| 80      | В    | CBEJ3        |

| 81      |      |              |

| 82      | P    | VSS          |

| 83      | В    | AD23         |

| 84      | В    | AD22         |

| 85      | В    | AD21         |

| 86      | В    | AD20         |

| 87      | В    | AD19         |

| 88      | В    | AD18         |

| 89      | В    | AD17         |

| 90      | В    | AD16         |

| 91      | В    | CBEJ2        |

| 92      | В    | FRAMEJ       |

| 93      | В    | IRDYJ        |

| 94      | В    | TRDYJ        |

| 95      | В    | DEVSELJ      |

| 96      | В    | STOPJ        |

| 97      | 1    | SERRJ        |

| 98      | B    | PAR          |

| 99      | B    | CBEJ1        |

|         | B    | AD15         |

| 100     | D    | ADIO         |

#### Numerical Pin List (continued)

| Numerical F |      |                    |

|-------------|------|--------------------|

| Pin No.     | Туре | Pin Name           |

| 101         | В    | AD14               |

| 102         | В    | AD13               |

| 103         | В    | AD12               |

| 104         | Р    | VSS                |

| 105         | Р    | VDD35V             |

| 106         | В    | AD11               |

| 107         | В    | AD10               |

| 108         | В    | AD9                |

| 109         | В    | AD8                |

| 110         | В    | CBEJ0              |

| 111         | В    | AD7                |

| 112         | В    | AD6                |

| 113         | В    | AD5                |

| 114         | В    | AD4                |

| 115         | В    | AD3                |

| 116         | B    | AD2                |

| 117         | B    | AD1                |

| 118         | B    | AD0                |

| 119         | B    | IDE D8             |

| 120         | P    | VDD                |

| 121         | B    | IDE_D7             |

| 122         | B    | IDE_D9             |

| 123         | В    | IDE_D6             |

| 124         | В    | IDE_D10            |

| 125         | B    | IDE_D5             |

| 126         | B    | IDE_D11            |

| 127         | B    | IDE_D4             |

| 128         | B    | IDE_D12            |

| 129         | B    | IDE_D3             |

| 130         | B    | IDE_D13            |

| 130         | B    | IDE_D13            |

| 132         | B    | IDE_D14            |

| 133         | B    | IDE_D1             |

| 133         | P    | VSS                |

| 135         | B    | IDE_D15            |

| 136         | B    | IDE_DIS            |

| 137         | I    | IDRQ0              |

| 137         |      | IDRQ1              |

|             | -    |                    |

| 139         | 0    | IDEIOWJ<br>IDEIORJ |

| 140         |      | IDERDY             |

| 141         | 1    |                    |

| 142         | 0    | IDAKJ0             |

| 143         | 0    | IDAKJ1             |

| 144         | 0    | IDE_A1             |

| 145         | 0    | IDE_A2             |

| 146         | 0    | IDE_A0             |

| 147         | 0    | IDEPCS1J           |

| 148         | 0    | IDEPCS3J           |

| 149         | 0    | IDESCS1J           |

| 150         | 0    | IDESCS3J           |

| Туре |                                                                                                                                                                                                                                                                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | KBINH/IRQ1                                                                                                                                                                                                                                                                                |

| В    | KBCLK/KBCSJ                                                                                                                                                                                                                                                                               |

| 0    | KBDATA                                                                                                                                                                                                                                                                                    |

| 0    | MSCLK                                                                                                                                                                                                                                                                                     |

| В    | IRQ12/MDATAO                                                                                                                                                                                                                                                                              |

|      | VDD                                                                                                                                                                                                                                                                                       |

| Р    | VSS                                                                                                                                                                                                                                                                                       |

| 0    | ROMCSJ                                                                                                                                                                                                                                                                                    |

| 0    | XDIR                                                                                                                                                                                                                                                                                      |

| 1    | IOCHKJ                                                                                                                                                                                                                                                                                    |

| В    | XD7                                                                                                                                                                                                                                                                                       |

| В    | XD6                                                                                                                                                                                                                                                                                       |

| В    | XD5                                                                                                                                                                                                                                                                                       |

| 1    | IRQ9                                                                                                                                                                                                                                                                                      |

| В    | XD4                                                                                                                                                                                                                                                                                       |

| 1    | DREQ2                                                                                                                                                                                                                                                                                     |

| В    | XD3                                                                                                                                                                                                                                                                                       |

|      | XD2                                                                                                                                                                                                                                                                                       |

| 1    | NOWSJ                                                                                                                                                                                                                                                                                     |

| В    | XD1                                                                                                                                                                                                                                                                                       |

|      | XD0                                                                                                                                                                                                                                                                                       |

|      | IOCHRDYJ                                                                                                                                                                                                                                                                                  |

|      | AEN                                                                                                                                                                                                                                                                                       |

|      | RTCAS                                                                                                                                                                                                                                                                                     |

|      | SA19                                                                                                                                                                                                                                                                                      |

|      | LMEGJ                                                                                                                                                                                                                                                                                     |

|      | SA18                                                                                                                                                                                                                                                                                      |

|      | IOWJ                                                                                                                                                                                                                                                                                      |

|      | SA17                                                                                                                                                                                                                                                                                      |

|      | IORJ                                                                                                                                                                                                                                                                                      |

|      | SA16                                                                                                                                                                                                                                                                                      |

|      | VSS                                                                                                                                                                                                                                                                                       |

|      | SYSCLK                                                                                                                                                                                                                                                                                    |

|      | PCSJ                                                                                                                                                                                                                                                                                      |

|      | SA15                                                                                                                                                                                                                                                                                      |

|      | DREQ3                                                                                                                                                                                                                                                                                     |

|      | SA14                                                                                                                                                                                                                                                                                      |

|      | SA13                                                                                                                                                                                                                                                                                      |

|      | DREQ1                                                                                                                                                                                                                                                                                     |

| -    | SA12                                                                                                                                                                                                                                                                                      |

|      | REFSHJ                                                                                                                                                                                                                                                                                    |

|      | SA11                                                                                                                                                                                                                                                                                      |

|      | SA10                                                                                                                                                                                                                                                                                      |

| -    | IRQ7                                                                                                                                                                                                                                                                                      |

|      | SA9                                                                                                                                                                                                                                                                                       |

|      | IRQ6                                                                                                                                                                                                                                                                                      |

|      | SA8                                                                                                                                                                                                                                                                                       |

|      | IRQ5                                                                                                                                                                                                                                                                                      |

|      | SA7                                                                                                                                                                                                                                                                                       |

| I    | IRQ4                                                                                                                                                                                                                                                                                      |

|      | B         P         O         I         B         B         I         B         I         B         I         B         I         B         I         B         B         B         B         B         B         B         B         B         B         B         B         B         B |

#### Numerical Pin List (continued)

| Pin No. | Туре | Pin Name |

|---------|------|----------|

| 201     | В    | SA6      |

| 202     | 1    | IRQ3     |

| 203     | В    | SA5      |

| 204     | 0    | DACKOJ   |

| 205     | В    | SA4      |

| 206     | 0    | TC       |

| 207     | В    | SA3      |

| 208     | Р    | VDD      |

### 2.4 Alphabetical Pin List

| Pin No. | Туре | Pin Name   |

|---------|------|------------|

| 56      | O    | A20MJ      |

| 118     | В    | AD0        |

| 117     | B    | AD1        |

| 116     | B    | AD2        |

| 115     | В    | AD2<br>AD3 |

| 115     | B    | AD3<br>AD4 |

| 114     | B    | AD4<br>AD5 |

| 112     | B    | AD5<br>AD6 |

|         |      |            |

| 111     | B    | AD7        |

| 109     | B    | AD8        |

| 108     | B    | AD9        |

| 107     | B    | AD10       |

| 106     | B    | AD11       |

| 103     | B    | AD12       |

| 102     | B    | AD13       |

| 101     | B    | AD14       |

| 100     | В    | AD15       |

| 90      | B    | AD16       |

| 89      | B    | AD17       |

| 88      | B    | AD18       |

| 87      | B    | AD19       |

| 86      | В    | AD20       |

| 85      | В    | AD21       |

| 84      | В    | AD22       |

| 83      | В    | AD23       |

| 80      | В    | AD24       |

| 79      | В    | AD25       |

| 78      | В    | AD26       |

| 77      | В    | AD27       |

| 76      | В    | AD28       |

| 75      | В    | AD29       |

| 74      | В    | AD30       |

| 73      | В    | AD31       |

| 173     | 0    | AEN        |

| 2       | 0    | BALE       |

| 110     | В    | CBEJ0      |

| 99      | В    | CBEJ1      |

| 91      | В    | CBEJ2      |

| 81      | В    | CBEJ3      |

| 49      | 0    | CPURST     |

| 204     | 0    | DACKOJ     |

| 28      | 0    | DAK_SEL0   |

| 32      | 0    | DAK_SEL1   |

| 36      | 0    | DAK_SEL2   |

| 95      | В    | DEVSELJ    |

| 25      | 1    | DREQ0      |

| 189     | 1    | DREQ1      |

| 166     | 1    | DREQ2      |

| 186     | 1    | DREQ3      |

| 30      |      | DREQ5      |

### Alphabetical Pin List (continued)

| Pin No. | Туре | Pin Name |

|---------|------|----------|

| -       |      |          |

| 34      |      | DREQ6    |

| 38      |      | DREQ7    |

| 61      | -    | EXTSW    |

| 62      |      | FERRJ    |

| 92      | В    | FRAMEJ   |

| 142     | 0    | IDAKJ0   |

| 143     | 0    | IDAKJ1   |

| 146     | 0    | IDE_A0   |

| 144     | 0    | IDE_A1   |

| 145     | 0    | IDE_A2   |

| 136     | В    | IDE_D0   |

| 133     | В    | IDE_D1   |

| 124     | В    | IDE_D10  |

| 126     | В    | IDE_D11  |

| 128     | В    | IDE_D12  |

| 130     | В    | IDE_D13  |

| 132     | В    | IDE_D14  |

| 135     | В    | IDE_D15  |

| 131     | В    | IDE_D2   |

| 129     | В    | IDE_D3   |

| 127     | В    | IDE_D4   |

| 125     | В    | IDE_D5   |

| 123     | В    | IDE_D6   |

| 121     | В    | IDE_D7   |

| 119     | В    | IDE_D8   |

| 122     | В    | IDE_D9   |

| 140     | 0    | IDEIORJ  |

| 139     | 0    | IDEIOWJ  |

| 147     | 0    | IDEPCS1J |

| 148     | 0    | IDEPCS3J |

| 141     | 1    | IDERDY   |

| 149     | 0    | IDESCS1J |

| 150     | 0    | IDESCS3J |

| 137     | 1    | IDRQ0    |

| 138     | 1    | IDRQ1    |

| 55      | 0    | IGNNEJ   |

| 67      | 1    | INTAJ/MI |

| 68      | B    | INTBJ/S0 |

| 69      | В    | INTCJ/S1 |

| 70      | B    | INTDJ/S2 |

| 54      | 0    | INTR     |

| 9       | 1    | IO16J    |

| 160     | 1    | IOCHKJ   |

| 172     | B    | IOCHRDYJ |

| 180     | B    | IORJ     |

| 178     | B    | IOWJ     |

| 93      | B    | IRDYJ    |

| 202     | I    | IRQ3     |

|         |      | IRQ3     |

| 200     |      |          |

| Pin No. | Туре | Pin Name     |

|---------|------|--------------|

| 198     | 1    | IRQ5         |

| 196     | 1    | IRQ6         |

| 194     | 1    | IRQ7         |

| 45      | 1    | IRQ8J        |

| 164     | 1    | IRQ9         |

| 11      | 1    | IRQ10        |

| 13      | 1    | IRQ11        |

| 155     | B    | IRQ12/MDATAO |

| 22      | 1    | IRQ14        |

| 20      |      | IRQ15        |

| 14      | B    | IRQSER       |

| 152     | B    | KBCLK/KBCSJ  |

| 153     | 0    | KBDATA       |

|         | I I  | KBINH/IRQ1   |

| 151     | -    |              |

| 23      | B    | LA17         |

| 21      |      | LA18         |

| 19      | B    | LA19         |

| 18      | В    | LA20         |

| 12      | В    | LA21         |

| 10      | В    | LA22         |

| 8       | В    | LA23         |

| 176     | 0    | LMEGJ        |

| 7       | В    | M16J         |

| 24      | В    | MEMRJ        |

| 27      | В    | MEMWJ        |

| 154     | 0    | MSCLK        |

| 58      | 0    | NMI          |

| 169     | I    | NOWSJ        |

| 43      | I    | OSC14M       |

| 98      | В    | PAR          |

| 71      | 1    | PCICLK       |

| 184     | 0    | PCSJ         |

| 65      | 1    | PHLDAJ       |

| 66      | В    | PHOLDJ       |

| 17      | 1    | PWG          |

| 191     | B    | REFSHJ       |

| 16      | I    | RINGIN       |

| 158     | 0    | ROMCSJ       |

| 57      | 0    | RSTDRV       |

| 174     | 0    | RTCAS        |

| 5       | B    | SA0          |

| 4       | B    | SA0<br>SA1   |

| 3       | B    | SA2          |

| 207     | B    | SA3          |

| 207     | В    | SA3<br>SA4   |

|         |      |              |

| 203     | B    | SA5          |

| 201     | B    | SA6          |

| 199     | B    | SA7          |

| 197     | В    | SA8          |

### Alphabetical Pin List (continued)

| Pin No. | Туре | Pin Name |

|---------|------|----------|

| 195     | В    | SA9      |

| 193     | В    | SA10     |

| 192     | В    | SA11     |

| 190     | В    | SA12     |

| 188     | В    | SA13     |

| 187     | В    | SA14     |

| 185     | В    | SA15     |

| 181     | В    | SA16     |

| 179     | 0    | SA17     |

| 177     | 0    | SA18     |

| 175     | 0    | SA19     |

| 6       | В    | SBHEJ    |

| 33      | В    | SD10     |

| 35      | В    | SD11     |

| 37      | В    | SD12     |

| 39      | В    | SD13     |

| 41      | В    | SD14     |

| 42      | В    | SD15     |

| 29      | В    | SD8      |

| 31      | В    | SD9      |

| 97      | 1    | SERRJ    |

| 44      | 1    | SIRQI    |

| 15      | 1    | SIRQII   |

| 50      | 0    | SMIJ     |

| 63      | В    | SPKR     |

| 64      | В    | SPLED    |

| 96      | В    | STOPJ    |

| 51      | 0    | STPCLKJ  |

| 183     | 0    | SYSCLK   |

| 206     | 0    | ТС       |

| Pin No. | Туре | Pin Name |

|---------|------|----------|

| 94      | В    | TRDYJ    |

| 46      | 1    | USBCLK   |

| 59      | В    | USBP10   |

| 60      | В    | USBP11   |

| 47      | В    | USBP20   |

| 48      | В    | USBP21   |

| 40      | Р    | VDD      |

| 120     | Р    | VDD      |

| 156     | Р    | VDD      |

| 208     | Р    | VDD      |

| 72      | Р    | VDD35V   |

| 105     | Р    | VDD35V   |

| 53      | Р    | VDD3V    |

| 1       | Р    | VSS      |

| 26      | Р    | VSS      |