### M1489/M1487: 486 PCI Chip Set

#### Features

M1489 (Cache-Memory PCI controller) M1487 (ISA Bus Controller)

#### Supported CPUs

- Supports AMD 486D4 and X5, Intel 486, P24T, P24D, DX4, SL-Enhanced, Cyrix M7, UMC U5 and AMD AM486DXL CPUs in 25, 33, 40, 50, 66, 100 and 133 MHz 3V/5V CPU interface

- Supports CPU L1 writeback

- Supports Cyrix's linear addressing mode

#### L2 Cache Controller

- Write Back cache with standard SRAM

- 8 Tag Bits, always force Dirty or 7 Tag Bits, 1 Dirty bit

- Supports cache size of 128K to 1M with 32Kx8, 64Kx8, 128Kx8

- Supports 2-1-1-1 read burst timing

- Write hit 0 wait support

#### **DRAM** Controller

- Supports 5V/3V EDO DRAM

- Flexible DRAM type & Timing support

- Supports up to 128M bytes, 4-bank DRAM size

- Supports hidden refresh and RAS only normal refresh

#### **Built in RTC & KBC**

- Built in 128 byte RTC & MC14069

- Built in KBC & 7406

#### **Built in IDE Controller**

- Dedicated IDE pins, concurrent with PCI bus

- 4x32 bits Read-Ahead buffer and Write-Post buffer support

- Supports through ATA PIO mode 3, 4 harddisk

#### PCI Local bus

- Synchronous 20, 25, 33 MHz PCI clock

- Supports PCI rev 2.0 with 4 PCI devices, 3 slot PCI masters, 1 slot PCI slave

- Supports 4 PCI interrupt steering input

- Supports CPU to PCI 4 layer DWord write buffer

- Supports PCI to memory 8 layer DWord write buffer

- Supports PCI parity

#### Power Management

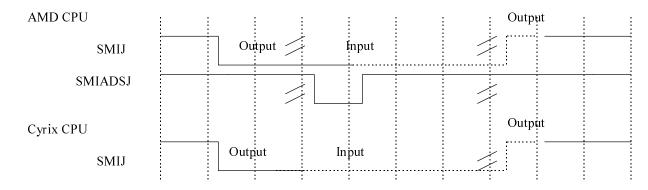

- Deep Green SMM, SMI

- Suspend switch support, Green mode state is LED indicated

- CLKCTR clock generator control

#### **Process/Packing**

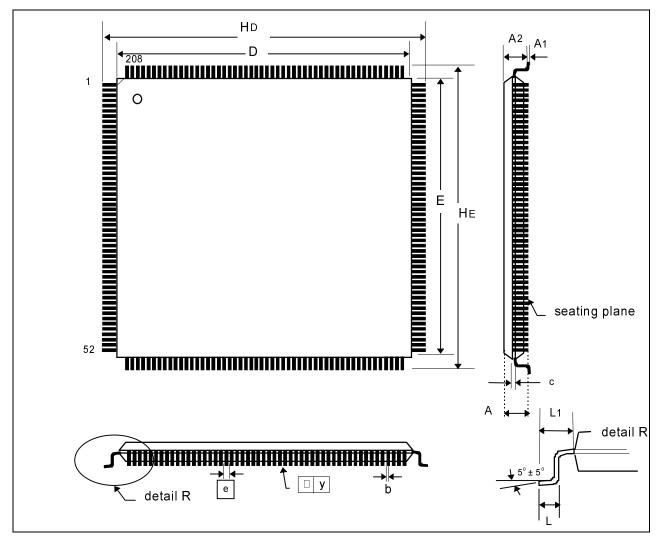

- M1489 0.6μ, 208-pin PQFP

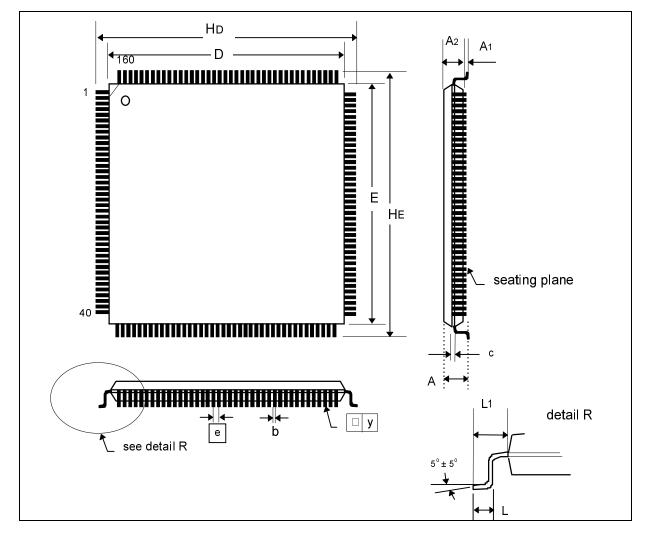

- M1487 0.6µ, 160-pin PQFP

### **Table of Contents**

| Section1: Introduction                                                                                     | 3   |

|------------------------------------------------------------------------------------------------------------|-----|

| <ul> <li>1.2 System Block Diagram</li> <li>1.3 Function Description</li> <li>1.3 Block Diagrams</li> </ul> | 5   |

| Section 2: Pin Description                                                                                 | 7   |

| 2.1 Pin Diagrams                                                                                           | 7   |

| 2.2 Pin Description Table                                                                                  | 9   |

| 2.3 M1489 Numerical Pin List                                                                               |     |

| 2.4 M1489 Alphabetical Pin List                                                                            |     |

| 2.5 M1487 Numerical Pin List                                                                               |     |

| 2.6 M1487 Alphabetical Pin List                                                                            | 24  |

| 2.7 Hardware Setup Control                                                                                 |     |

| 2.8 M1489/M1487 Hardware Reference Manual                                                                  | 27  |

| Section 3: Functional Description                                                                          | 30  |

| Section 4: Configuration Registers                                                                         | 34  |

| Section 5: Software Programming Guide                                                                      | 94  |

| Section 6: Design Issues                                                                                   | 107 |

| Section 7: Electrical Characteristics                                                                      | 133 |

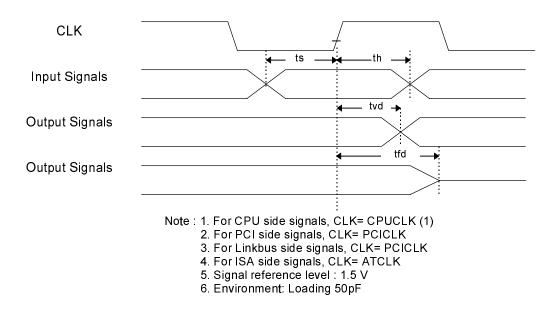

| 7.1 M1489 AC Characteristics                                                                               |     |

| 7.2 M1487 AC Characteristics                                                                               |     |

| 7.3 DC Characteristics                                                                                     | 138 |

| Section 8: Packaging Information                                                                           | 139 |

| Appendix A: BIOS Guide                                                                                     | 141 |

### Section 1: Introduction

ALi's M1489/M1487 PCI chipset is the most cost effective PCI solution available. M1489/M1487 enables top-tobottom PCI in 486 CPU systems, offering superior price/performance for mainstream PCI-ISA systems.

M1489/M1487 highly integrates the DRAM controller, L2 cache controller, Host, PCI, and ISA interface, as well as the standard ISA functions: DMA controller, interrupt controller, timer/counter, RTC (Real Time Clock), and keyboard controller. Additionally, M1489/M1487 incorporates the high performance Local Bus IDE allowing a system designer to implement Local bus IDE with no additional cost. M1489/M1487 is a highly integrated solution requiring minimized TTL components, enabling PCI-ISA designs at costs equal to or lower than comparable VL Bus designs.

M1489 (Cache Memory PCI Controller: CMP) integrates the L2 cache controller and the DRAM controller. The cache controller supports write-back cache policies and cache size from 128K to 1M byte in an interleaved or noninterleaved configuration. The DRAM controller interfaces DRAM to the Host bus, PCI bus, and Link bus. M1489 can support EDO 3/5V DRAM, standard DRAM, and flexible timing select. M1489 also integrates intelligent Host to PCI, PCI to Host buffer to achieve high performance. Also, M1489 provides the high performance Local Bus IDE interface. M1487 (ISA Bridge Controller: IBC) provides the bridge between the ISA bus, PCI bus, and Host bus. IBC integrates the common I/O functions found in today's ISA based systems: a seven channel DMA, two 82C59 interrupt controllers, 8254 timer/ counter, deep green function, and control logic for NMI generation. IBC also has built-in 128 bytes RTC, MC14069, KBC, and 7406. IBC also provides the decode for external BIOS.

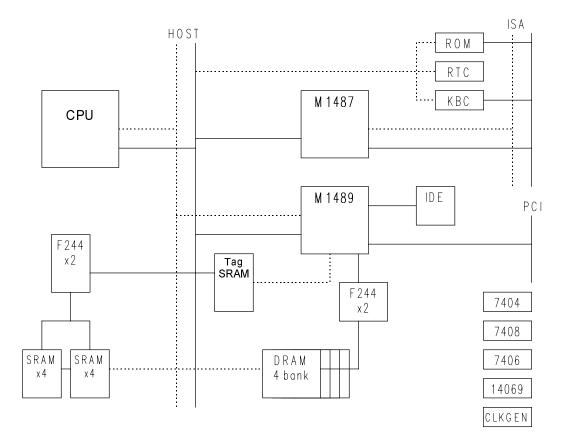

### 1.2 System Block Diagram

### **1.3 Function Description**

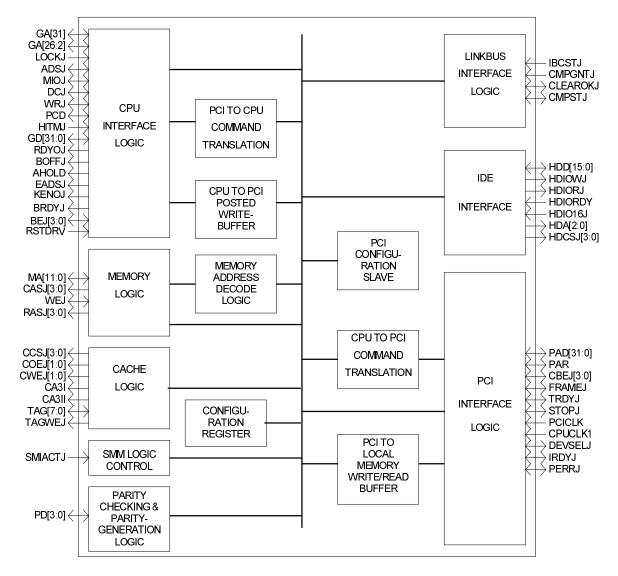

### Internal Block Diagram M1489

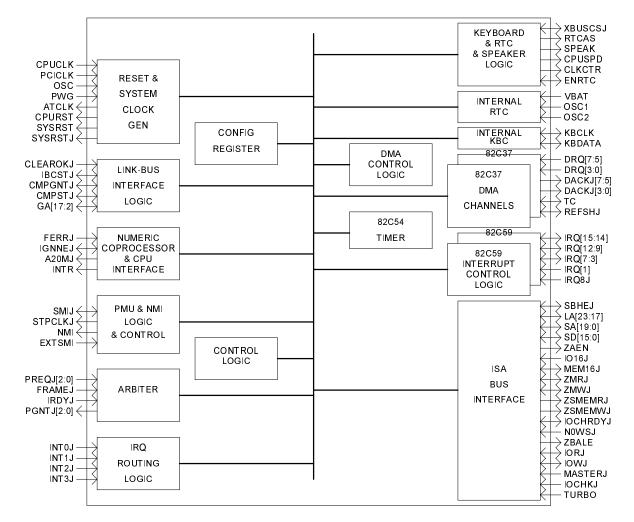

#### Internal Block Diagram M1487

### Section 2: Pin Description

### 2.1 Pin Diagram (M1489)

| $N N N N N N N N N N \rightarrow \rightarrow$ |                                   |                                         |

|-----------------------------------------------|-----------------------------------|-----------------------------------------|

| 000000000000                                  |                                   | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ |

| ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~       | 0 0 4 3 2 4 0 8 7 6 5 4 3 2 4 0 9 | V 8 0 0 1 0 4 7 0 7 8 0 0 1 0 4 7 0 7 8 |

|                                               |                                   |                                         |

| 4           | TAG5                 | GND9        | TAG7 | TAG2       | TAGO | CCSJ3/PD3 | COEJO |          | CCSJ2/PD2 | CA3II | CWF.I1   | COEJ1 | CCSJ0/PE | HITMJ | PCD   |      | MIO    | ADSJ   | GA26          | GA25 | VCC6 | GA24 | GA23    | GA22   | GA20  | GA19  | GA18 | GA5 | GA6  | GA7  | GND8 | GA8  | GA14     | GA12 | GA10 | GA11 | GA16 | GA17  | GA2  | GND7             | 156        |

|-------------|----------------------|-------------|------|------------|------|-----------|-------|----------|-----------|-------|----------|-------|----------|-------|-------|------|--------|--------|---------------|------|------|------|---------|--------|-------|-------|------|-----|------|------|------|------|----------|------|------|------|------|-------|------|------------------|------------|

| 1<br>2<br>3 | TAG5<br>TAG4<br>TAG3 |             |      |            |      | ä         |       |          | 22        |       | 1        |       | 8        |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | IBCSTJ<br>IPGNTJ | 155<br>154 |

| 4           | TAGWE                | J           |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       | CLE  | EAROKJ           | 153        |

| 5<br>6      | GD0<br>GD1           |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       | (    | CMPSTJ<br>PAD31  | 152<br>151 |

| 7<br>8      | GD2<br>GD3           |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD29<br>PAD27   | 150<br>149 |

| 9           | GD4                  |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD25            | 148        |

| 10<br>11    | GD5<br>GD7           |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | CBEJ3<br>PAD23   | 147<br>146 |

| 12          | GD6                  |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD21            | 145        |

| 13<br>14    | GD8<br>GD9           |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | VCC5<br>PAD19    | 144<br>143 |

| 15<br>16    | GD10<br>GD11         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD17<br>CBEJ2   | 142<br>141 |

| 17          | GD12                 |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | IRDYJ            | 140        |

| 18<br>19    | GD13<br>GD15         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       | D    | EVSELJ<br>PERRJ  | 139<br>138 |

| 20          | GD14                 |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | CBEJ1            | 137        |

| 21<br>22    | GD16<br>VCC1         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD14<br>PAD12   | 136<br>135 |

| 23<br>24    | GD17<br>GD18         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        | N             | 1.   | 48   | 20   | )       |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD10<br>PAD3    | 134<br>133 |

| 25          | GD19                 |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        | •      | ••            | •    | Т    |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD1             | 132        |

| 26<br>27    | GD20<br>GD21         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       | F    | RSTDRV<br>VCC4   | 131<br>130 |

| 28          | GD23                 |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       | С    | PUCLK1           | 129        |

| 29<br>30    | GD22<br>GD24         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | GND6<br>PCICLK   | 128<br>127 |

| 31<br>32    | GD25<br>GD26         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD8<br>PAD5     | 126<br>125 |

| 33          | GD27                 |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD7             | 124        |

| 34<br>35    | GND1<br>GD28         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | CBEJ0<br>PAD0    | 123<br>122 |

| 36<br>37    | GD29<br>GD30         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD6<br>PAD2     | 121<br>120 |

| 37<br>38    | GD30<br>GD31         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD2<br>PAD4     | 119        |

| 39<br>40    | RDYOJ<br>BRDYJ       |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD9<br>PAD11    | 118<br>117 |

| 41          | BOFFJ                |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD13            | 116        |

| 42<br>43    | AHOLD<br>EADSJ       |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD15<br>PAR     | 115<br>114 |

| 44          | KENOJ                |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | STOPJ            | 113        |

| 45<br>46    | BEJ3<br>BEJ1         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       | F    | TRDYJ<br>FRAMEJ  | 112<br>111 |

| 47<br>48    | BEJ0<br>BEJ2         |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD16<br>PAD18   | 110<br>109 |

| 49          | MA7                  |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD20            | 108        |

| 50<br>51    | MA6<br>MA5           |             |      |            |      |           |       |          |           |       |          |       |          |       |       |      |        |        |               |      |      |      |         |        |       |       |      |     |      |      |      |      |          |      |      |      |      |       |      | PAD22<br>PAD24   | 107<br>106 |

| 52          | VCC2                 |             |      |            |      |           |       |          | ~         | _     |          |       | _        |       | _     | ī    | ≣      | Ξ      | Ξ             |      |      | H    | E :     | Ξ      | Ξ.    | -     | -    | -   |      | -    | -    |      | -        |      |      |      |      | -     | _    | PAD26            | 105        |

|             |                      | MA4<br>GND2 | MA3  | MA1<br>MA2 | MAO  | MA11      | MA10  | MA8      | CASJ3     | CASJ2 | CASI0    | WEJ   | RASJ3    | RASJ1 | RASJO | GND3 | HDCSJO | HDCSJ3 | HUAU<br>DCSJ2 | VCC3 | HDA1 |      | HDIORDY | HDIORJ | HDD15 | HDD14 | HDDO |     | GND4 |      |      | HDD3 | HDD10    | HDD9 | HDD5 | HDD8 |      | PAD30 | GND5 |                  |            |

| •           |                      | 53<br>53    | 55   | 56         | 58   | 59        | 60    | 62<br>61 | 63        | 64    | 6.5<br>5 | 67    | 68       | £0    | 71    | 73   | 74     | 75     | 76            | 78   | 79   | 81   | 82      | 83 4   | 84 85 | 86    | 87   | 88  | 90   | 91 2 | 3 83 | 94   | 95<br>95 | 97   | 86   | 99   | 101  | 102   | 104  |                  | -          |

### Pin Diagram (M1487)

|                                                                                                                                                                                                            |                                                                                                                                | 160  | 159    | 158      | 157      | 156   | 155    | 154    | 153   | 152 | 151    | 150    | 149    | 148        | 140  | 145   | 144   | 143   | 142    | 141  | 140    | 139      | 138       | 137   | 136  | 1<br>3 с<br>л 4 | 134 | 133      | 2 | 131 | 129    | 128     | 127    | 126    | 125     | 124   | 123   | 122   | 121 |                                                                      |                                                                                                                     |                                                                                                                                                     |                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|--------|----------|----------|-------|--------|--------|-------|-----|--------|--------|--------|------------|------|-------|-------|-------|--------|------|--------|----------|-----------|-------|------|-----------------|-----|----------|---|-----|--------|---------|--------|--------|---------|-------|-------|-------|-----|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|                                                                                                                                                                                                            |                                                                                                                                | GND6 | SBHEJ  | REFSH.   | SA2      | SA3   | SA4    | SA5    | SA15  | SA6 | SA7    | SA8    | SA9    | SA10       | SAIZ | SA16  | VCC4  | SA17  | SA18   | SA19 | ZAEN   | IOCHRDYJ | GND5      | SD0   | SD1  |                 |     | SD4      |   |     | IOCHKJ | GND4    | SD10   | SD11   | SD12    | SD13  | SD14  | SD15  | SD9 |                                                                      |                                                                                                                     |                                                                                                                                                     |                                                                         |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14                                                                                                                                    | VCC5<br>NOWSJ<br>IRQ8J<br>SA1<br>KBCLK<br>KBDATA<br>SA0<br>SA14<br>SA13<br>GND7<br>IRQ1<br>VBAT<br>PWG<br>OSC1                 |      |        |          |          |       |        |        |       |     |        |        |        |            |      |       |       |       |        |      | ,      | 2        |           |       |      |                 |     |          |   |     |        |         |        |        |         |       |       |       | ſ   | I<br>I<br>I<br>I<br>MEN<br>I<br>C<br>DA                              | (CC3<br>SD8<br>_A17<br>_A18<br>_A19<br>_A20<br>_A21<br>_A22<br>_A23<br>M16J<br>D16J<br>RQ7<br>CK7<br>RQ6            | 120<br>118<br>117<br>116<br>115<br>112<br>111<br>112<br>111<br>110<br>108<br>108                                                                    | 9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>9<br>8                     |

| <ol> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>24</li> <li>25</li> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> </ol> | OSC2<br>FERRJ<br>IGNNEJ<br>NMI<br>SMIJ<br>CPURST<br>STCLKJ<br>A20MJ<br>INTR<br>GA4<br>GA5<br>GA6<br>GA7<br>GA13<br>GA8<br>GA14 |      |        |          |          |       |        |        |       |     |        |        |        |            |      |       | Γ     | M     | 1      | 4    | 18     | 37       | 7         |       |      |                 |     |          |   |     |        |         |        |        |         |       |       |       |     | DA<br>DA<br>DA<br>IR<br>IR<br>IR<br>IR<br>IR<br>IR<br>IR<br>IR<br>IR | CK6<br>RQ5<br>CK5<br>RQ0<br>CK0<br>Q14<br>Q15<br>Q12<br>Q12<br>Q12<br>Q12<br>Q12<br>Q12<br>Q12<br>Q12<br>Q12<br>Q12 | 106<br>105<br>104<br>103<br>102<br>101<br>100<br>99<br>98<br>97<br>96<br>97<br>96<br>97<br>96<br>97<br>96<br>97<br>96<br>97<br>97<br>97<br>97<br>97 | 6<br>5<br>4<br>3<br>2<br>1<br>0<br>9<br>8<br>7<br>6<br>5<br>4<br>3<br>2 |

| 31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40                                                                                                                                                   | GA9<br>GA12<br>GA10<br>GA11<br>GA15<br>GA16<br>GA17<br>GA3<br>GA2<br>VCC6                                                      | GND1 | IBCSTJ | CMPGNT.I | CLEAROKJ | CMPST | PCICLK | FRAMEJ | IRDYJ | OSC | PREQJO | PGNTJ1 | PGNTJO |            |      | INT2J | INTOJ | INT3J | INT 1J | VCC1 | CPUCLK | GND2     | SYSRST    | TURBO |      |                 |     |          |   |     | CLKCTR | XBUSCSJ | EXTSMI | CPUSPD | ZSMEMWJ | r Moi | RTCAS | r MWZ |     | I<br>DA<br>DA<br>DA<br>I<br>AST                                      | RQ5<br>RQ6<br>RQ7<br>RQ1<br>CK1<br>RQ3<br>CK3<br>RQ9<br>TERJ<br>CK3<br>RQ9                                          | 9<br>90<br>88<br>87<br>86<br>85<br>84<br>83<br>82<br>83<br>84<br>83                                                                                 | 0<br>9<br>8<br>7<br>6<br>5<br>4<br>3<br>2                               |

|                                                                                                                                                                                                            |                                                                                                                                | 41   | 42     | 43       | 4        | 45    | 46     | 47     | 48    | 49  | 50     | 51     | 52     | л с<br>З I | 2 0  | 56    | 57    | 58    | 59     | 60   | 61     | 62       | 63 .<br>G | 64    | 65 0 | 66              | 57  | 80<br>80 | 3 | 3 2 | 72     | 73      | 74     | 75     | 76      | 77    | 78    | 79    | 80  |                                                                      |                                                                                                                     |                                                                                                                                                     |                                                                         |

### 2.2 Pin Description Table

#### Table 2-1. M1489 Pin Description Table

| Name              | Number              | Туре | Description                                                                                                                                                                                                                                                                                                                        |

|-------------------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU Interfa       | ce                  |      |                                                                                                                                                                                                                                                                                                                                    |

| GA[31]            | 181                 | 1/0  | Address 31. This is the processor address line 31. It is used to recognize PCI or BIOS. It is input for CPU cycles and is driven low during ISA/DMA Master cycles.                                                                                                                                                                 |

| GA[26:24]         | 184, 183,<br>180    | I/O  | Address[26:24]. These addresses decode the accessed targets. They are inputs for CPU cycles and is driven low for PCI/DMA/ISA Master and REFRESH cycles.                                                                                                                                                                           |

| GA[23:2]          | 179-169,<br>167-157 | I/O  | Address[23:2]. These addresses are connected to CPU addresses. They decode for accessed targets. They are inputs for CPU, and are driven output for PCI/DMA/ISA Master and REFRESH cycles.                                                                                                                                         |

| BEJ[3:0]          | 45,48<br>46,47      | I/O  | <b>Byte Enable</b> . These are the byte enable signals for the data bus. These signals are ignored during the local memory read access cycles, and the data of all bytes will be treated as enable to access when write. In the PCI/DMA/ISA MASTER accesses cycles, these byte enable signals will be driven by M1489 to host bus. |

| ADSJ              | 186                 | I/O  | Address Strobe. The address status indicates that a new valid bus cycle is currently being driven by the CPU. In the PCI/ DMA/ ISA Master access cycles, this signal will be driven by M1489 to host bus.                                                                                                                          |

| MIOJ,<br>DCJ, WRJ | 187, 188,<br>189    | I/O  | <b>Memory or I/O, Data or Code, Write or Read</b> . The memory/input-output, write/read, and data/code lines are the CPU bus cycle definition pins. In the PCI/DMA/ISA Master access cycles, these signals will be driven by M1489 to host bus.                                                                                    |

| RDYOJ             | 39                  | 0    | Ready Out. The non-burst ready output indicates that the current bus cycle is<br>complete.                                                                                                                                                                                                                                         |

| BRDYOJ            | 40                  | 0    | <b>Burst Ready Out</b> . The burst ready output performs the same function during a burst cycle that RDYOJ performs during a non-burst cycle.                                                                                                                                                                                      |

| PCD               | 190                 | I/O  | <b>Page Cache Disable</b> . The page cache disable pin indicates that the current CPU bus cycle is non-cacheable. This signal is not available in the Intel L1 write-back system.                                                                                                                                                  |

| LOCKJ             | 185                 | 1    | Lock. The bus lock pin indicates that the current CPU bus cycle is locked.                                                                                                                                                                                                                                                         |

| HITMJ             | 191                 | 1    | <b>Hit Modify</b> . The hit modified cache pin is asserted to indicate that a hit to a modified data cache occurred. This signal pin is only available in write-back processor system.                                                                                                                                             |

| GD[31:0]          | 38~5                | I/O  | Data Bus [31:0]. These are the 32 data lines.                                                                                                                                                                                                                                                                                      |

| BOFFJ             | 41                  | 0    | Backoff. This backoff signal pin is used to force the processor floating its bus in the next clock.                                                                                                                                                                                                                                |

| AHOLD             | 42                  | 0    | Address Hold Request. This is the address hold request signal to processor.                                                                                                                                                                                                                                                        |

| EADSJ             | 43                  | 0    | <b>External Address Strobe</b> . This signal indicates that a valid external address has been driven onto the CPU address pins to be used for cache snooping cycle.                                                                                                                                                                |

| KENOJ             | 44                  | 0    | Cache Enable Output. This is the cache enable signal to CPU.                                                                                                                                                                                                                                                                       |

| RSTDRV            | 131                 | 1    | Chip Initiation. This signal is used to initialize the M1489 chip internal state machines and registers.                                                                                                                                                                                                                           |

| CPUCLK1           | 129                 | 1    | CPU bus Clock                                                                                                                                                                                                                                                                                                                      |

### M1489 Pin Description Table (continued)

| Name                  | Number                | Туре   | Description                                                                                                                                                                                                                                                                                                            |

|-----------------------|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Co             | ntrol                 |        |                                                                                                                                                                                                                                                                                                                        |

| RASJ[3:0]             | 68~71                 | 0      | <b>Low Address Strobe</b> . These are the memory module row address strobe signals.<br>The RASJ0 applies to bank 0 memory module and RASJ1 applies to bank 1, RASJ2<br>applies to bank2, and the RASJ3 applies to bank3.                                                                                               |

| CASJ[3:0]             | 63~66                 | 0      | <b>Column Address Strobe</b> . These are the memory module column address strobe signals. The CASJ0 applies to byte 0, CASJ1 applies to byte 1, CASJ2 applies to byte 2, and CASJ3 applies to byte 3.                                                                                                                  |

| MA[11:0]              | 49-51,<br>54-62       | I/O    | <b>Memory Address</b> . These are the memory address signals. These signals will change to PWCNTL0-PWCNTL11( power control signals ) during the power-control output cycle. These pins will be input polarity during the power-on reset period for initializing the power-control default value of the internal ports. |

| MWEJ                  | 67                    | 1/0    | Memory Write Enable. This is the memory write enable signal.                                                                                                                                                                                                                                                           |

|                       | ontroller int         | erface |                                                                                                                                                                                                                                                                                                                        |

| COEJ[1:0]             | 194, 201              | 0      | <b>Cache Output Enable</b> . These are the cache output enable signals with which the single chip can control the external 2 bank cache system. The COEJ0 applies to the bank 0 cache and COEJ1 applies to the bank 1.                                                                                                 |

| CWEJ<br>[1:0]         | 196, 200              | 0      | <b>Cache Write Enable</b> . These are the cache write enable signals. The CWEJ0 applies to bank 0 cache and the CWEJ1 applies to bank 1 cache.                                                                                                                                                                         |

| CCSJ[3:0]<br>/PD[3:0] | 202, 198,<br>195, 193 | 1/0    | <b>Cache Chip Select</b> . These are the cache system chip select signals. These pins can also be used as DRAM parity data bytes [3:0] through hardware configuration.                                                                                                                                                 |

| TAGWEJ                | 4                     | 0      | Tag Write Enable. This is the tag RAM write enable signal.                                                                                                                                                                                                                                                             |

| TAG[7:0]              | 203~207,<br>1~3       | 1/0    | Tag Data. These are the cache tag data bits.                                                                                                                                                                                                                                                                           |

| A3I                   | 199                   | 0      | Cache Address 3. This is the cache address line 3 for bank 0 cache.                                                                                                                                                                                                                                                    |

| A3II                  | 197                   | 0      | Cache Address 3. This is the cache address line 3 for bank 1 cache.                                                                                                                                                                                                                                                    |

| SMM Signa             | I                     |        |                                                                                                                                                                                                                                                                                                                        |

| SMIACTJ               | 192                   | 1      | <b>System Management Interrupt Active</b> . This signal is an active low input indicating that the processor is operating at SMM.                                                                                                                                                                                      |

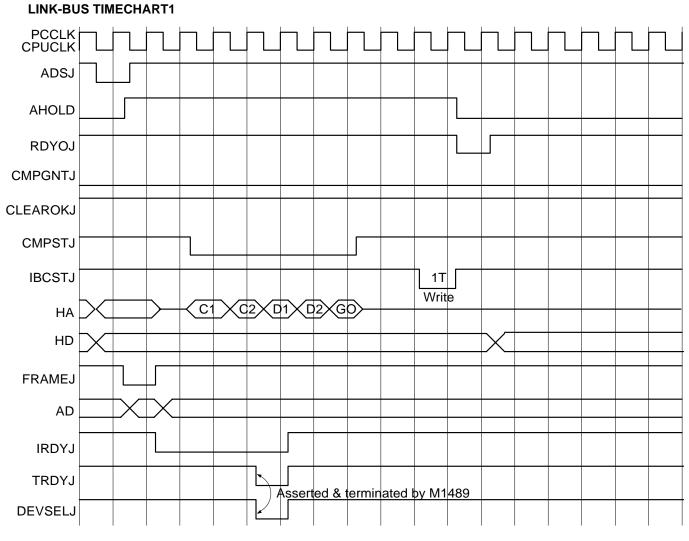

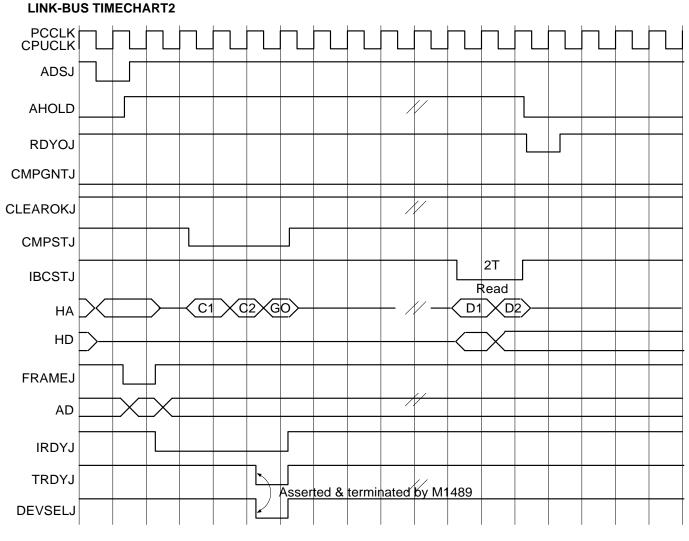

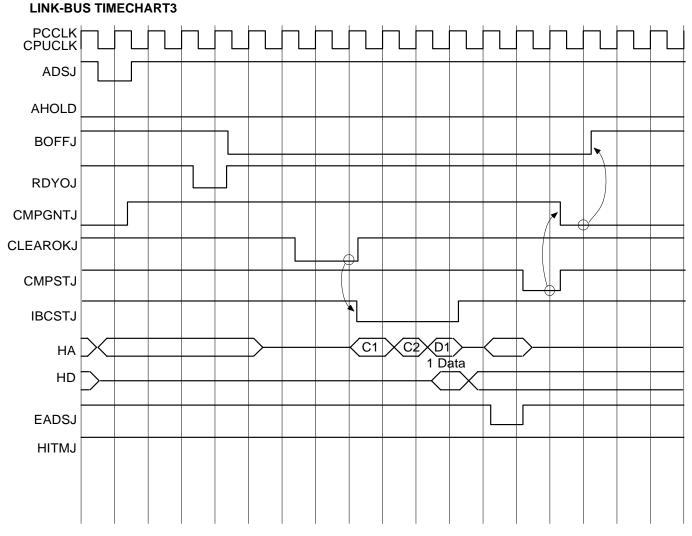

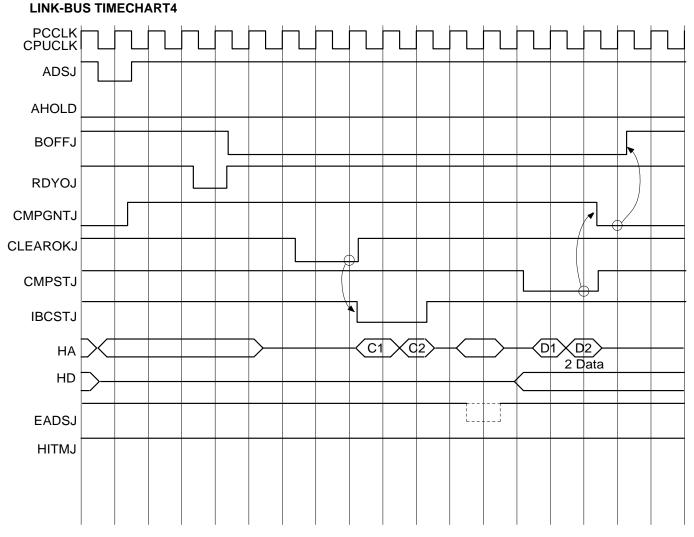

| Linkbus Int           | erface                |        |                                                                                                                                                                                                                                                                                                                        |

| CLEAROK<br>J          | 153                   | В      | <b>CMP(M1489) Internal Buffers Cleared OK</b> . This signal is used to indicate the CMP internal buffers usage status and the PCI slave devices respondent action.                                                                                                                                                     |

| CMPGNTJ               | 154                   | 1      | <b>CMP Grant signal</b> . It indicates to the CMP/CPU that access to the system resource and bus ownership has been granted.                                                                                                                                                                                           |

| CMPSTJ                | 152                   | В      | <b>CMP Status Ready</b> . This signal is used to indicate the CMP's status or data has been ready and valid on the link-bus.                                                                                                                                                                                           |

| IBCSTJ                | 155                   | 1      | IBC Status Ready. This signal is used to indicate the IBC's status or data has been ready and valid on the link-bus.                                                                                                                                                                                                   |

### M1489 Pin Description Table (continued)

| Name           | Number              | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDE Interfa    |                     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HDD[15:0]      | 85~101              | В    | <b>Disk Data[15:0]</b> . These are the 16-bit data bus which connects to the IDE drives.<br>HDD[7:0] define the lowest data byte while HDD[15:8] define the most significant data<br>byte. The HDD bus is normally in a high-impedance state and is driven by the M1489<br>only during the HDIOWJ command pulse.                                                                                                                                      |

| HDIOWJ         | 84                  | 0    | <b>Disk I/O Write Command</b> . This is an active low output which enables data to be written to the IDE drive.                                                                                                                                                                                                                                                                                                                                       |

| HDIORJ         | 83                  | 0    | <b>Disk I/O Read Command</b> . This is an active low output which enables data to be read from the IDE drive.                                                                                                                                                                                                                                                                                                                                         |

| HDIORDY<br>J   | 82                  | 1    | <b>Disk Ready</b> . This is an input which is sampled at the clock rising edge at the programmed end of the command cycle. If HDIORDYJ is sampled high, the command is terminated. If it is sampled low the command cycle is extended. HDIORDYJ will be sampled with every positive CLK edge until it is tested high. Once sampled high, the command will end normally. Note that an external 1K-Ohm pull-up resistor is recommended for this signal. |

| HDIO16J        | 81                  | I    | <b>Disk Chip Select 16</b> . This is an active-low input which indicates that the disk drive is ready to perform a 16-bit data transfer. The signal connects directly to the ATA connector and is typically driven active during IDE controller transfers to the drive's 1F0h data port. Note that an external 1K-Ohm pull-up resister is recommended for this signal.                                                                                |

| HDA[2:0]       | 79,8077             | 0    | <b>Disk Address[2:0]</b> . These are normally outputs to the ATA connector for register selection in the drives. These signals are decoded from the GA[2] and BEJ[3:0] inputs.                                                                                                                                                                                                                                                                        |

| HDCSJ[3:<br>0] | 75,76<br>73,74      | 0    | <b>Disk Chip Select</b> . These are active low outputs which are used to select control/command block registers in the drives.                                                                                                                                                                                                                                                                                                                        |

| PCI Interfa    | ce                  | •    |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PAD[31:0]      | 102~151             | 1/0  | Address and Data Multiplexed pins. During the first clock of a PCI transaction<br>PAD[31:0] contain a physical address(32 bits). During subsequent clocks PAD[31:0]<br>contain data.                                                                                                                                                                                                                                                                  |

| PAR            | 114                 | 1/0  | <b>Parity bit</b> . Parity is even parity across AD[31:00] and CBE#[3:0]. The M1489 generates parity bit (1)when it acts as a PCI slave in PCI master read cycle data phase, or (2)when it acts as a PCI master in CPU write cycle address and data phase, or (3)when it acts as a PCI master in CPU read cycle address phase.                                                                                                                        |

| CBEJ[3:0]      | 147,141,<br>137,123 | 1/0  | <b>Byte Enables</b> . These signals indicate active bytes during read and write cycle.<br>These pins are outputs when PCI master cycle. Otherwise, these pins are inputs.                                                                                                                                                                                                                                                                             |

| FRAMEJ         | 111                 | I/O  | <b>Cycle Frame</b> . It indicates the beginning and duration of a PCI access. This pin is output when M1489 acts as a PCI master. This pin is input when M1489 acts as a PCI slave.                                                                                                                                                                                                                                                                   |

| TRDYJ          | 112                 | 1/0  | Target Ready.It indicates the target's (selected device's) ability to complete the<br>current data phase of the transaction.TRDYJ is used in conjunction with IRDYJ.This pin is output when M1489 acts as a slave, and input when M1489 acts as a<br>master.                                                                                                                                                                                          |

| STOPJ          | 113                 | I/O  | <b>Stop</b> . It indicates the current Target is requesting the Master to stop the current transaction. This pin is output in PCI master cycle when multiple data transfer is disabled, and input when PCI slave requests to stop current cycle.                                                                                                                                                                                                      |

| PCICLK         | 127                 | 11   | PCI system Clock                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### M1489 Pin Description Table (continued)

| Name              | Number                                         | Туре   | Description                                                                                                                                                                                                             |

|-------------------|------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Interfa       | ce                                             |        |                                                                                                                                                                                                                         |

| DEVSELJ           | 139                                            | 1/0    | <b>Device select</b> . It indicates the target device has decoded the address as its own cycle. This pin is output when M1489 acts as a PCI slave, and input when M1489 acts as a PCI master.                           |

| IRDYJ             | 140                                            | 1/0    | <b>Initiator Ready</b> . It indicates the PCI bus master's ability to complete the current data phase of the transaction. This pin is output when M1489 acts as a PCI master, and input when M1489 acts as a PCI slave. |

| PERRJ             | 138                                            | 1/0    | <b>Parity Error</b> . It may be pulsed by any selected device which detects a data parity error. M1489 combines SERRJ and PERRJ to create error event to M1487 to generate NMI.                                         |

| Power             |                                                |        |                                                                                                                                                                                                                         |

| Vcc[1],<br>Vcc[6] | 22,182                                         | (3/5V) | System 5V power supply signals for 5V/5V- tolerance CPU system. Or, system 3.3V power supply signals for pure 3.3V interface CPU system.                                                                                |

| Vcc[2:5]          | 52,78,<br>130,144                              |        | System 5V power supply signals.                                                                                                                                                                                         |

| GND[1:9]          | 34, 53, 72,<br>90, 104,<br>128,156,<br>168,208 |        | System Ground level signals.                                                                                                                                                                                            |

#### Table 2-2. M1487 Pin Description Table

| Name         | Number       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock & res  | et interface |      |                                                                                                                                                                                                                                                                                                                                                                                              |

| CPUCLK       | 61           | 1    | CPU bus Clock                                                                                                                                                                                                                                                                                                                                                                                |

| PCICLK       | 46           | 1    | PCI bus Clock                                                                                                                                                                                                                                                                                                                                                                                |

| OSC          | 49           | 1    | 14.318MHz Input. This is a clock input signal.                                                                                                                                                                                                                                                                                                                                               |

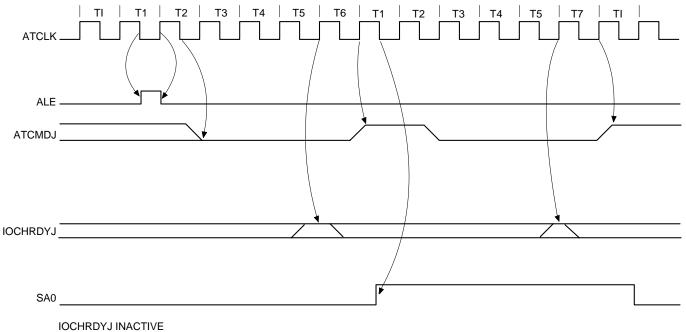

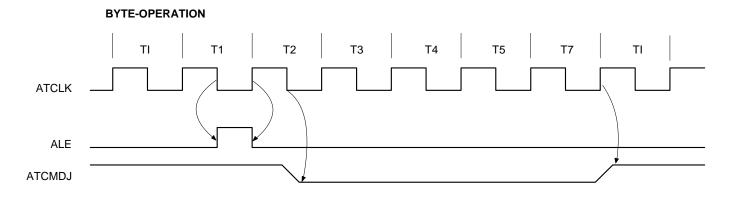

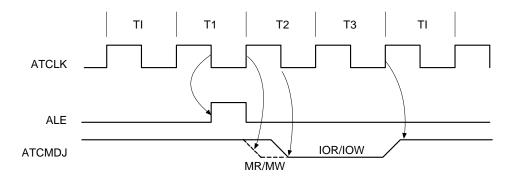

| ATCLK        | 70           | 0    | System Clock Output. This is AT clock output signal. This clock can be set to CPUCLK divided by 3,4,5,6,8 or 7.16 MHz.                                                                                                                                                                                                                                                                       |

| PWG          | 13           | 1    | <b>Power Good</b> . This input signal is a Schmitt trigger pad signal. It comes from the power supply to indicate that power is available and stable.                                                                                                                                                                                                                                        |

| CPURST       | 20           | 0    | CPU Reset. This signal resets the CPU processor.                                                                                                                                                                                                                                                                                                                                             |

| SYSRST       | 63           | 0    | Cold Reset. System cold reset.                                                                                                                                                                                                                                                                                                                                                               |

| SYSRSTJ      | 81           | 0    | Cold Reset. The signal is the inversed cold reset.                                                                                                                                                                                                                                                                                                                                           |

| CPU interfa  | се           |      | · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                  |

| A20MJ        | 22           | 0    | Address 20 Mask. This is the Address line 20 mask signal.                                                                                                                                                                                                                                                                                                                                    |

| INTR         | 23           | 0    | Interrupt Request. This is the interrupt signal generated by the internal 8259. It is synchronized with CPUCLK.                                                                                                                                                                                                                                                                              |

| FERRJ        | 16           | 1    | Floating Point Error                                                                                                                                                                                                                                                                                                                                                                         |

| IGNNEJ       | 17           | В    | Ignore Numeric Error                                                                                                                                                                                                                                                                                                                                                                         |

| NMI          | 18           | 0    | Non-Maskable Interrupt. This is the non-maskable interrupt request signal.                                                                                                                                                                                                                                                                                                                   |

| SMIJ         | 19           | В    | System Management Interrupt. This signal invokes the System Management Mode(SMM).                                                                                                                                                                                                                                                                                                            |

| STPCLKJ      | 21           | 0    | Stop Clock Request. This signal indicates that a request to Intel processor has been made to turn off its CLK input.                                                                                                                                                                                                                                                                         |

| ISA bus inte | erface       |      |                                                                                                                                                                                                                                                                                                                                                                                              |

| IO16J        | 110          | 1    | External 16-Bit I/O Chip Select. This is the 16-bit I/O devices select indicating signal.                                                                                                                                                                                                                                                                                                    |

| MEM16J       | 111          | В    | External 16-Bit Memory Chip Select. This is the 16 bit memory devices select indicating signal.                                                                                                                                                                                                                                                                                              |

| ZMRJ         | 67           | В    | <b>Memory Read</b> . This signal is an input in master cycle but an output in other cycles. In CPU ISA cycles, this signal is driven by chip internal control circuits. In DMA cycles, this signal is driven by the internal DMA controllers. In refresh cycles, this signal is driven by the internal refresh circuits. In master cycles, this signal is driven by external master devices. |

| ZMWJ         | 79           | В    | Memory Write. This signal is an input in master cycle but an output in other cycles.<br>In CPU ISA cycles, this signal is driven by chip internal control circuits. In DMA cycles,<br>this signal is driven by the internal DMA controllers. In master cycles, this signal is<br>driven by external master devices.                                                                          |

| ZSMEMRJ      | 66           | 0    | <b>System Memory Read</b> . This is a tri-state output signal. It is driven low only when the system executes a below 1 Mbyte ISA memory read cycle. Otherwise, it is a tri-state status.                                                                                                                                                                                                    |

| ZSMEMW<br>J  | 76           | 0    | <b>System Memory Write</b> . This is a tri-state output signal. It is driven low only when the system executes a below 1 Mbyte ISA memory write cycle. Otherwise, it is a tri-state status.                                                                                                                                                                                                  |

### M1487 Pin Description Table (continued)

| Name         | Number          | Туре | Description                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISA bus int  | erface          |      |                                                                                                                                                                                                                                                                                                                                                                          |

| IOCHRDY<br>J | 139             | В    | <b>I/O Channel Ready</b> . This input signal is used to extend the ISA command width for the CPU and DMA cycles. In memory access events, this signal is output polarity pending the ISA MST/DMA cycle until the linkbus system finishes the data transferred access.                                                                                                    |

| NOWSJ        | 2               | 1    | <b>ISA Bus Zero-Wait State</b> . This is the ISA device zero-wait state indicator signal. This signal terminates the CPU ISA command immediately.                                                                                                                                                                                                                        |

| ZBALE        | 68              | 0    | Buffer Address Latch Enable. This is the buffered address latch enable signal. A high pulse with half ATCLK is generated at the beginning of CPU ISA cycle for the external devices to latch the system address. During the CPU bus releasing to ISA system cycle, this signal is kept at a high level status.                                                           |

| IORJ         | 69              | В    | <b>I/O Read</b> . This signal is an input in master cycle but is output in other cycles. In CPU ISA cycles, this signal is driven by chip internal control circuits. In DMA cycles, this signal is driven by the internal DMA controllers. In master cycles, this signal is driven by the external master devices.                                                       |

| IOMÌ         | 77              | В    | <b>I/O Write</b> . This signal is an input in master cycle but is output in other cycles. In CPU ISA cycles, this signal is driven by chip internal control circuits. In DMA cycles, this signal is driven by the internal DMA controllers. In master cycles, this signal is driven by the external master devices.                                                      |

| MASTERJ      | 82              | 1    | Master. This is ISA master access indicating signal.                                                                                                                                                                                                                                                                                                                     |

| ZAEN         | 140             | 0    | Address Enable. This is the address enable signal. In CPU or master cycle, this signal is driven low to enable the external devices to decode the I/O address. In other cycles, this signal is driven high to inhibit I/O address decoding.                                                                                                                              |

| SBHEJ        | 159             | В    | Slot Byte High Enable. This is the system byte high enable signal. In CPU cycle, this signal is generated by BE3J-BE0J and the chip internal control circuit. In DMA cycle, it is generated by internal 8237. In refresh cycle, it is generated by the internal refresh circuits. In master cycle, it is an input polarity signal and is driven by the master device.    |

| LA[23:17]    | 112~118         | В    | Latch Address[23:17]. These addresses are connected to slot address. They are input during ISA MASTER cycle.                                                                                                                                                                                                                                                             |

| SA[19:17]    | 141~143         | В    | <b>Slot Address[19:17]</b> . These addresses are connected to slot address. They are tri-<br>state during ISA MASTER cycle and driven low as refresh cycle.                                                                                                                                                                                                              |

| SA[16:2]     | 145~157,<br>8,9 | В    | <b>Slot Address[16:2]</b> . These addresses are connected to slot addresses. They are input for ISA MASTER cycle and driven output for CPU, DMA, PCI MASTER and REFRESH cycles.                                                                                                                                                                                          |

| SA[1]        | 4               | В    | <b>Slot Address 1</b> . This is the system address line 1 signal. In CPU cycle, this signal is generated by BE3J-BE0J and the chip internal control circuit. In DMA cycle, it is generated by the internal 8237. In refresh cycle, it is generated by the internal refresh circuits. In master cycle, it is an input polarity signal and is driven by the master device. |

| SA[0]        | 7               | В    | <b>Slot Address 0</b> . This is the system address line 0 signal. In CPU cycle, this signal is generated by BE3J-BE0J and the chip internal control circuit. In DMA cycle, it is generated by the internal 8237. In refresh cycle, it is generated by the internal refresh circuits. In master cycle, it is an input polarity signal and is driven by the master device. |

### M1487 Pin Description Table (continued)

| Name                                  | Number                              | Тур      | Description                                                                                                                                                                                                                                                                              |

|---------------------------------------|-------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISA bus int                           | orfaco                              | е        |                                                                                                                                                                                                                                                                                          |

| SD[15:0]                              | 119,                                | В        | Slot Data Bus. These are the system data lines.                                                                                                                                                                                                                                          |

|                                       | 121~127,                            |          |                                                                                                                                                                                                                                                                                          |

|                                       | 130~137                             | <u> </u> |                                                                                                                                                                                                                                                                                          |

| REFRESH<br>J                          | 158                                 | В        | <b>Refresh</b> . The signal is input polarity at master cycle, but it is output pin at other cycles.                                                                                                                                                                                     |

| IOCHCKJ                               | 129                                 | 1        | I/O Channel Check. This connects to I/O slot channel check.                                                                                                                                                                                                                              |

| DRQ[7:5],<br>DRQ[3:0]                 | 109,107,<br>105,89,<br>91,87,103    |          | <b>DMA Request Input</b> . This are the DMA request input signals.                                                                                                                                                                                                                       |

| DACKJ<br>[7:5],<br>DACKJ<br>[3:0]     | 108,106,<br>104,84,<br>94,86,102    | 0        | <b>DMA Acknowledge Output</b> . These are DACK demultiplex select signals.                                                                                                                                                                                                               |

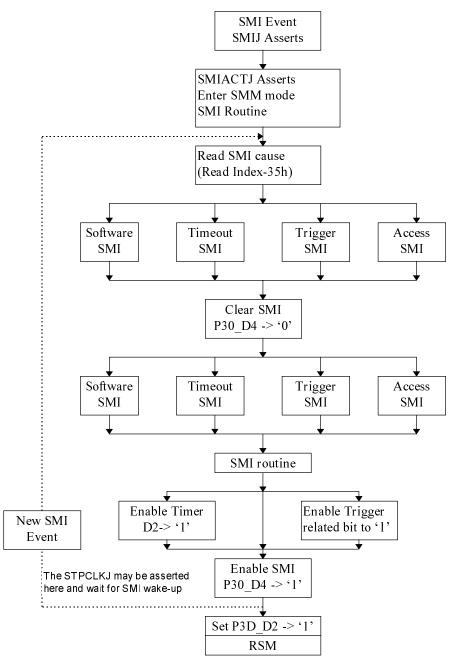

| тс                                    | 95                                  | В        | Terminal Count. This is the DMA channel terminal count indicating signal.                                                                                                                                                                                                                |