### DESCRIPTION

The ES1788 *Audio*Drive<sup>®</sup> is a mixed-signal single-chip solution that adds 16-bit stereo sound and FM music synthesis to personal computers. It includes an embedded microprocessor, a 20-voice ESFM<sup>™</sup> music synthesizer, 16-bit stereo wave ADC and DAC, 16bit stereo music DAC, MPU-401 UART mode serial port, dual game ports, hardware master volume control, two serial port interfaces to external DSP and external wavetable music synthesizer, DMA control logic with FIFO, and ISA bus inferface logic. There are three stereo inputs (typically line, CD Audio, and auxiliary line) and a mono microphone input to an internal preamp. All of this on a single chip that can be designed into a motherboard, add-on card, or integrated into other peripheral cards such as Fax/Modem, VGA, LAN, I/O, etc.

The ES1788 *Audio*Drive<sup>®</sup> can record, compress, and play back voice, sound, and music with built-in 6-channel mixer controls. Using two high-performance DMA channels, the ES1788 supports full-duplex analog operation for simultaneous record and playback. The ESFM<sup>™</sup> synthesizer has extended capabilities within native mode operation providing superior sound and power-down capabilities. The ES1788 is register compatible to OPL3<sup>™</sup>.

The MPU-401 serial port is for interfacing with an external MIDI device. The dual game port supports two joysticks both having X,Y resistor value settings and two pushbutton switches. The PC speaker volume can be modified by software. Two software address selection modes allow for motherboard Plug and Play configuration.

A DSP serial interface allows an external DSP to take over DAC or ADC resources. A wavetable serial port allows the ES1788 to interface with either the ES689 or ES690 wavetables. I/O address, DMA, and interrupt selection can be controlled through system software.

Advanced power management features include suspend/resume from disk or host-independent self-timed power-down and automatic wake-up.

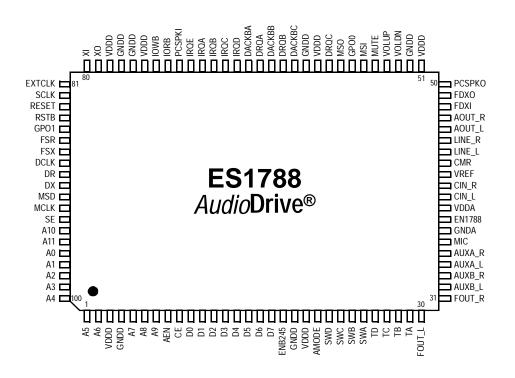

The ES1788 *Audio*Drive<sup>®</sup> is available in an industry-standard 100pin Plastic Quad Flat Pack (PQFP) package.

### APPLICATIONS

- PC Audio

- PC Games

- Business Audio

- Multimedia PCs

- Music Synthesis

### FEATURE HIGHLIGHTS

- Single, high-performance, mixed-signal, 16-bit stereo VLSI chip for digital audio

- High-quality, 20-voice ESFM<sup>™</sup> music synthesizer; patents pending

- Patented ESPCM<sup>®</sup> compression

### **Record and Playback Features**

- Record, compress, and play back voice, sound, and music

- Programmable sample rate from 4 kHz to 44.1 kHz for record and playback

- · 3-button hardware volume control for up, down, and mute

- Mixer controlled record and playback with programmable logarithmic volume controls

#### Inputs and Outputs

- MIDI serial port compatible with MPU-401 UART mode

- ESS high-performance integrated dual game port

- Address decode for joysticks

- Programmed I/O and demand transfer DMA

- Software address mapping, DMA and IRQ selections for motherboard Plug and Play

- Wavetable serial port interface to ES689/ES690 for direct access to the music DAC

- PC speaker input/output with volume control

- Serial port interface to external DSP optionally controls fullduplex analog operation

#### Mixer Features

- 6-channel stereo mixer inputs for line, auxiliary A (CD audio), auxiliary B, digital audio (wave files), music synthesizer, plus a mono channel mixer input for microphone

- 4-channel record mixer with stereo inputs for line, auxiliary A (CD audio), auxiliary B, plus a mono input for microphone

- Programmable 6-bit (64 step) logarithmic master volume control

#### Power

- Advanced power management with self-timed power-down, automatic wake-up, and suspend/resume to and from disk

- Supports 3.3 or 5.0 V operation

### Compatibility

- Supports PC games in Sound Blaster<sup>™</sup> and Sound Blaster<sup>™</sup> Pro and OPL3 FM synthesizers

- Supports Microsoft<sup>®</sup> Windows<sup>™</sup>, Windows NT<sup>™</sup>, Windows for Workgroups<sup>™</sup>, Windows<sup>®</sup>95 and Windows Sound System<sup>®</sup>

- Supports IBM<sup>®</sup> OS/2<sup>®</sup>

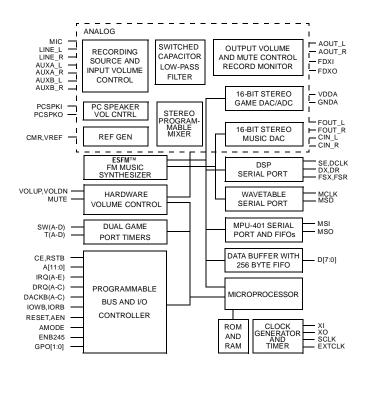

## **BLOCK DIAGRAM**

method is selected

### PINOUT

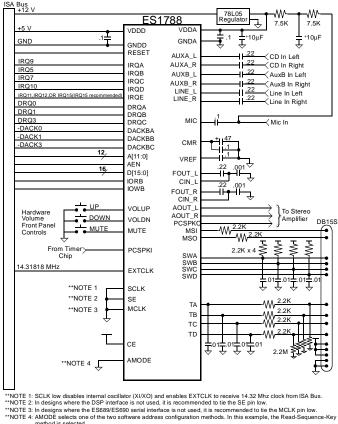

# TYPICAL APPLICATION

# **DIGITAL PIN DESCRIPTIONS**

| Name       | I/O | Description                                                                                                                                                                                                                                                         |  |  |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDDD       | I   | Digital supply voltage (3.0V to 5.5V).                                                                                                                                                                                                                              |  |  |

| GNDD       | I   | Digital ground.                                                                                                                                                                                                                                                     |  |  |

| VOLDN      | I   | Active-low volume decrease button input.                                                                                                                                                                                                                            |  |  |

| VOLUP      | I   | Active-low volume increase button input.                                                                                                                                                                                                                            |  |  |

| MUTE       | I   | Active-low mute toggle button input.                                                                                                                                                                                                                                |  |  |

| GPO0       | 0   | Output that is set low by external reset and thereaf-<br>ter controlled by bit 0 of port 2x7h. Available to sys-<br>tem software for power management or other<br>applications.                                                                                     |  |  |

| GPO1       | 0   | Output that is set high by external reset and thereaf-<br>ter controlled by bit 1 of port 2x7h. Available to sys-<br>tem software for power management or other<br>applications.                                                                                    |  |  |

| MSI        | I   | MIDI serial input. Either MPU-401 or SoundBlaster<br>formats. Schmitt trigger input with internal pull-up<br>resistor.                                                                                                                                              |  |  |

| MSO        | 0   | MIDI serial data output.                                                                                                                                                                                                                                            |  |  |

| RESET      | I   | Active-high reset from ISA bus.                                                                                                                                                                                                                                     |  |  |

| RSTB       | 0   | Inverted RESET output.                                                                                                                                                                                                                                              |  |  |

| SCLK       | I   | Clock selection output:<br>0: Clock from EXTCLK input<br>1: Clock from crystal connection to pins XI and XO                                                                                                                                                         |  |  |

| EXTCLK     | I   | 14.32 MHz clock input from ISA bus. Duty cycle must be 40%-60%. No connection if SCLK=1.                                                                                                                                                                            |  |  |

| хо         | 0   | Crystal oscillator output.                                                                                                                                                                                                                                          |  |  |

| ХІ         | I   | Crystal oscillator input. No connection if SCLK=0.                                                                                                                                                                                                                  |  |  |

| CE         | I   | Input with internal pull-up. Active-high chip enable.<br>When low, all IRQ and DRQ outputs become high<br>impedance, and AEN is forced high internally,<br>thereby disabling the I/O activity to/from the<br>ES1788.                                                |  |  |

| IORB       | I   | Active-low read strobe from ISA bus.                                                                                                                                                                                                                                |  |  |

| IOWB       | I   | Active-low write strobe from ISA bus.                                                                                                                                                                                                                               |  |  |

| A[9:0]     | I   | Address inputs from ISA bus.                                                                                                                                                                                                                                        |  |  |

| A[11:10]   | I   | Address inputs from ISA bus. The ES1788 requires<br>these pins to be low for all address decodes. These<br>pins have an internal pull-down device enabled<br>when input signal AMODE=0. In this case they can<br>float(ES688 compatible designs).                   |  |  |

| AEN        | I   | Active-low address enable from ISA bus.                                                                                                                                                                                                                             |  |  |

| D[7:0]     | I/O | Bidirectional data bus. These pins have weak pull-<br>up devices to prevent these inputs from floating<br>when not driven.                                                                                                                                          |  |  |

| ENB245     | 0   | Active-low output when the ES1788 is being read o<br>written to. Intended to be connected to the enable<br>control of an external 74LS245.                                                                                                                          |  |  |

| SW(A-D)    | I   | Four (A,B,C,D) active-low joystick switch setting<br>inputs. These SW pins have an internal 2k ohm pu<br>up resistor which is pulled to ground by the switch<br>on each joystick. The joystick port is typically at<br>address 201.                                 |  |  |

| T(A-D)     | I/O | Four (A,B,C,D) joystick timer pins. These pins con-<br>nect to the X,Y positioning variable resistors for the<br>two joysticks.                                                                                                                                     |  |  |

| AMODE      | I   | Input pin with pull-down device. The ES1788 is dis-<br>abled following a hardware reset and must be con-<br>figured by one of two methods (optioned by<br>AMODE) of software address selection:<br>0: Read-Sequence-Key method<br>1: System-Control-Register method |  |  |

| DACKB(A-C) | I   | Three (A,B,C) active-low DMA acknowledge inputs from the ISA bus.                                                                                                                                                                                                   |  |  |

| Name     | I/O | Description                                                                                                                                                                                                                                                                                                                                         |  |  |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IRQ(A-D) | 0   | Four (A,B,C,D) active-high interrupt requests to the<br>ISA bus. Unselected IRQ outputs are high imped-<br>ance. IRQs are software configurable.                                                                                                                                                                                                    |  |  |

| IRQE     | 0   | Active-high interrupt request to the ISA bus.<br>Reserved for MPU-401 or hardware volume contri                                                                                                                                                                                                                                                     |  |  |

| DRQ(A-C) | 0   | Three (A,B,C) active-high DMA requests to the<br>bus. Unselected DRQ outputs are high impeda<br>When DMA is not active, the selected DRQ out<br>has a pull-down device that holds the DRQ line<br>tive unless another device that shares the same<br>DRQ line can source enough current to make ti<br>DRQ line active. DRQs are software configurab |  |  |

| PCSPKI   | I   | Normally low digital PC speaker signal input. This<br>signal is converted to an analog signal with volum<br>control and appears on analog output PCSPKO.                                                                                                                                                                                            |  |  |

| FSR      | I   | Input with internal pull-down. Frame sync for receiv data from external DSP. Programmable for active-high or active-low.                                                                                                                                                                                                                            |  |  |

| FSX      | I   | Input with internal pull-down. Frame sync for tran<br>mit request from external DSP. Programmable for<br>active-high or active-low.                                                                                                                                                                                                                 |  |  |

| DCLK     | I   | Input with internal pull-down. Serial data clock fro<br>external DSP. Typically 2.048 MHz.                                                                                                                                                                                                                                                          |  |  |

| DR       | I   | Input with internal pull-down. Data receive pin from external DSP.                                                                                                                                                                                                                                                                                  |  |  |

| DX       | 0   | Tri-state output. Data transmit to external DSP. H impedance when not transmitting.                                                                                                                                                                                                                                                                 |  |  |

| MSD      | I   | Input with internal pull-down. Music serial data fr<br>external ES689 or ES690 Wavetable Music Synt<br>sizer.                                                                                                                                                                                                                                       |  |  |

| MCLK     | I   | Input with internal pull-down. Music serial clock fr<br>external ES689 or ES690 Wavetable Music Synt<br>sizer.                                                                                                                                                                                                                                      |  |  |

| SE       | I   | Input with internal pull-down. Active-high to enable serial mode, i.e., enables an external DSP to contro analog resources of the ES1788 through the DSP serial interface.                                                                                                                                                                          |  |  |

# DIGITAL CHARACTERISTICS

| Symbol | Parameter                                                | Min | Мах | Unit | Conditions                            |

|--------|----------------------------------------------------------|-----|-----|------|---------------------------------------|

| VIH1   | Input high voltage: All<br>except GPI1                   | 2.0 |     | V    | VDDD=min                              |

| VIH2   | Input high voltage: GPI1                                 | 3.0 |     | V    | VDDD=min                              |

| VIL    | Input low voltage                                        |     | 0.8 | V    | VDDD=max                              |

| VOL1   | Output low voltage: All<br>except D[7:0], DRQx,<br>IRQx  |     | 0.4 | V    | IOL=4mA,<br>VDDD=min                  |

| VOH1   | Output high voltage: All<br>except D[7:0], DRQx,<br>IRQx | 2.4 |     | V    | IOH=-3mA,<br>VDDD=max                 |

| VOL2   | Output low voltage:<br>D[7:0], DRQx, IRQx                |     | 0.4 | V    | IOL=16mA,<br>VDDD=min                 |

| VOH2   | Output high voltage:<br>D[7:0], DRQx, IRQx               | 2.4 |     | V    | IOH=-12mA,<br>VDDD=max                |

| VOL3   | Output low voltage:<br>Select DRQx when DMA<br>inactive  |     | 0.4 | V    | IOL=0.8 mA                            |

| ICC1   | VDDD active                                              |     | 60  | mA   | VDDD=max<br>osc. rate at<br>14.32 MHz |

| ICC2   | VDDA active                                              |     | 60  | mA   | VDDA=max                              |

# ANALOG PIN DESCRIPTIONS

| Name              | I/O | Description                                                                                                                                                                                                                                                                                                                 |  |  |

|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDDA              | I   | Analog supply voltage (4.5 to 5.5 V). Should be greater than or equal to VDDD-0.3 V.                                                                                                                                                                                                                                        |  |  |

| GNDA              | -   | Analog ground.                                                                                                                                                                                                                                                                                                              |  |  |

| MIC               | -   | Microphone input. MIC has an internal pullup resistor to CMR.                                                                                                                                                                                                                                                               |  |  |

| LINE_L,<br>LINE_R | -   | Line inputs left and right. LINE_L, LINE_R have inter-<br>nal pullup resistors to CMR.                                                                                                                                                                                                                                      |  |  |

| AUXA_L,<br>AUXA_R | -   | Auxiliary inputs left and right. AUXA_L, AUXA_R have<br>internal pullup resistors to CMR. Normally intended for<br>connection to an internal or external CD-ROM analog<br>output.                                                                                                                                           |  |  |

| AUXB_L,<br>AUXB_R | Ι   | Auxiliary inputs left and right. AUXB_L, AUXB_R have internal pullup resistors to CMR. Normally intended for connection to an external music synthesizer or other line-level music source.                                                                                                                                  |  |  |

| FDXO              | 0   | Normally connected to CMR via an internal resistor.<br>Can be programmed to connect internal to FOUT_R<br>pin during DSP serial mode.                                                                                                                                                                                       |  |  |

| FDXI              | Ι   | Input with internal pullup to CMR. Alternate input to left channel filter stage in DSP serial mode.                                                                                                                                                                                                                         |  |  |

| FOUT_L,<br>FOUT_R | 0   | Filter outputs left and right. AC-coupled externally to CIN_L, CIN_R to remove DC offsets. These outputs have internal series resistors of about 5k ohms. Capacitors to analog ground on these pins can be used to create a low-pass filter pole that removes switching noise introduced by the switched-capacitor filters. |  |  |

| CIN_L,<br>CIN_R   | I   | Capacitive coupled inputs left and right. These inputs<br>have internal pull-up resistors to CMR of approxi-<br>mately 50k ohms.                                                                                                                                                                                            |  |  |

| VREF              | 0   | Reference generator resistor divider output. Should b bypassed to analog ground with 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                 |  |  |

| CMR               | 0   | Buffered reference output. Should be bypassed to analog ground with a 47 $\mu$ Felectrolytic capacitor with a 0.1 $\mu$ F capacitor in parallel.                                                                                                                                                                            |  |  |

| AOUT_L,<br>AOUT_R | 0   | Line-level stereo outputs, left and right.                                                                                                                                                                                                                                                                                  |  |  |

| PCSPKO            | 0   | Analog output of PCSPKI with volume control.                                                                                                                                                                                                                                                                                |  |  |

| EN1788            | Ι   | Analog VDD.                                                                                                                                                                                                                                                                                                                 |  |  |

## SERVICE AND SUPPORT

- Evaluation Kit

- Manufacturing Kit

- Reference Design

ESS Technology, Inc. 48401 Fremont Blvd. Fremont, CA 94538 Tel: 510-226-1088 Fax: 510-492-1098

# ANALOG CHARACTERISTICS

| Parameter              | Pins                                                      | Min  | Тур  | Max          | Unit                     |

|------------------------|-----------------------------------------------------------|------|------|--------------|--------------------------|

| Reference<br>voltage   | CMR, VREF                                                 |      | 2.25 |              | Volts<br>(VDDA<br>=5.0V) |

| Input<br>impedance     | LINE_L, LINE_R,<br>AUXA_L, AUXA_R,<br>AUXB_L, AUXB_R, MIC | 30k  |      | 100k         | Ohms                     |

|                        | CIN_L, CIN_R                                              | 35k  | 50k  | 65k          | Ohms                     |

| Output<br>impedance    | FOUT_L, FOUT_R                                            | 3.5k | 5k   | 6.5k         | Ohms                     |

|                        | AOUT_L, AOUT_R max<br>load for full-scale output<br>range |      | 5k   |              | Ohms                     |

| Input voltage<br>range | MIC                                                       | 10   |      | 125          | mVp-p                    |

|                        | LINE_L, LINE_R,<br>AUXA_L, AUXA_R,<br>AUXB_L, AUXB_R      | 0.5  |      | VDDA<br>-0.5 | Volts                    |

| Output voltage range   | AOUT_L, AOUT_R<br>full-scale output range                 | 0.5  |      | VDDA<br>-1.0 | Volts                    |

| Gain                   | Mic preamp                                                |      | 26   |              | dB                       |

## MAXIMUM RATINGS

| Rating                      | Symbol | Value         |  |

|-----------------------------|--------|---------------|--|

| Analog supply voltage       | VDDA   | -0.3 to 7.0 V |  |

| Digital supply voltage      | VDDD   | -0.3 to 7.0 V |  |

| Input voltage               | VIN    | -0.3 to 7.0 V |  |

| Operating temperature range | TA     | 0 to 70 °C    |  |

| Storage temperature range   | TSTG   | -50 to 125 °C |  |

## **BUNDLED SOFTWARE AND DRIVERS**

- AudioRack<sup>™</sup>

- Bundled Drivers for:

- Microsoft Windows 3.1

- Microsoft Windows for Workgroups

- Microsoft Windows NT

- Microsoft Windows95

- IBM OS/2

(P) U.S. Patent 4,214,125 and others, other patents pending.

All specifications are subject to change without prior notice.

ESPCM<sup>®</sup> and *Audio*Drive<sup>®</sup> are registered trademarks of ESS Technology, Inc.

*Audio*Rack<sup>™</sup> is a trademark of ESS Technology, Inc.

All other trademarks are owned by their respective holders.

Document Number: SAM0067 REV: B