# Intel<sup>®</sup> 631xESB/632xESB I/O Controller Hub (ESB2)

**Specification Update**

October 2009

The Intel® 631xESB/632xESB I/O Controller Hub may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

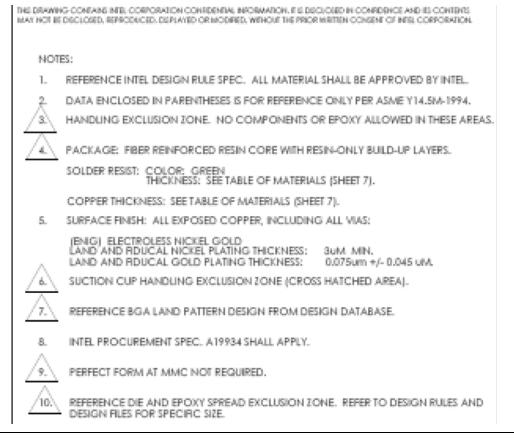

Document Number: 313075-007

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

2

\*Other names and brands may be claimed as the property of others.

Copyright © 2006-2009, Intel Corporation

## Contents

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 6  |

| Summary Table of Changes     | 7  |

| dentification Information    | 14 |

| Errata                       | 17 |

| Specification Changes        | 47 |

| Specification Clarifications | 48 |

| Documentation Changes        | 49 |

# **Revision History**

| Version | Description                                                                                                                                                                                                                                                          | Date          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| -001    | Initial Release                                                                                                                                                                                                                                                      | May 2006      |

| -002    | <ul> <li>Updated Component Marketing Information Table</li> <li>Change code name ESB2 to product name Intel® 631xESB/<br/>632xESB I/O Controller Hub</li> <li>Added Errata 96</li> <li>Added TPM support description</li> <li>Other Documentation Changes</li> </ul> | August 2006   |

| -003    | <ul><li>Added Errata 97-98</li><li>Added Documentation Changes</li></ul>                                                                                                                                                                                             | February 2007 |

| -004    | <ul> <li>Added S-Spec information</li> <li>Added Erratum 99</li> <li>Added Documentation Changes item 12-14</li> </ul>                                                                                                                                               | April 2007    |

| -005    | <ul><li>Added Errata 100</li><li>Added Documentation Changes 10-13 and renumbered ordering</li></ul>                                                                                                                                                                 | July 2007     |

| -006    | <ul><li>Added Erratum 101</li><li>Added Documentation Change 19</li></ul>                                                                                                                                                                                            | January 2008  |

| -007    | <ul> <li>Updated Erratum 101</li> <li>Deleted Erratum 102 and Updated Erratum 68 (same erratum)</li> <li>Added Erratum 103-111</li> </ul>                                                                                                                            | October 2009  |

This is an update to the specifications in the documents listed in the Affected Documents and Related Documents tables. It is a compilation of device and document errata and specification clarifications/changes, and is intended for hardware system manufacturers and software developers.

Information types defined in the Nomenclature section of this document are consolidated into this document and are no longer published in other documents. This document may also contain previously unpublished information.

#### **Affected Documents**

| Document Title                                        | Document<br>Number |

|-------------------------------------------------------|--------------------|

| Intel® 631xESB / 632xESB I/O Controller Hub Datasheet | 313082-001         |

#### **Related Documents**

| Document Title                                                                 | Document<br>Number |

|--------------------------------------------------------------------------------|--------------------|

| Intel® 631xESB / 632xESB I/O Controller Hub Thermal/Mechanical Design<br>Guide | 313073-001         |

#### Nomenclature

**S-Spec Number** is a five-digit code used to identify products. Products are differentiated by their unique characteristics, e.g., core speed, package type, etc. as described in the identification information table. Read all notes associated with each S-Spec number.

**Errata** are design defects or errors. These may cause the ESB2 behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes/Clarifications** are modifications to the current published specifications. These changes will be incorporated in the next release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in the next release of the specification.

*Note:* Errata remain in the specification update throughout the product's life cycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications, and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation.

# Summary Table of Changes

The tables included in this section indicate the errata, specification changes/ clarifications, or documentation changes that apply to the Intel® 631xESB/632xESB I/ O Controller Hub. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted.

#### **Codes Used in Summary Table**

#### **Stepping/Version**

X: Applies to this stepping.

Blank: Fixed in listed stepping or does not exist in listed stepping.

#### **Status**

**Doc:** Document change or update will be implemented.

No Fix - Root caused to a silicon issue that will not be fixed.

Plan Fix - Root caused to a silicon issue and will be fixed in a future stepping.

Fixed - Root cased to a silicon issue and has been fixed in a subsequent stepping.

#### Row

Change bar to left of table row indicates that this item is either new or modified from the previous version of this document.

#### **Errata**

| Number | 631x<br>632xE<br>Cont<br>H | el®<br>ESB/<br>SB I/O<br>roller<br>ub<br>oping | Status | SKUs<br>(optional) | ERRATA                                                                                                                               |

|--------|----------------------------|------------------------------------------------|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|        | A-0                        | A-1                                            |        |                    |                                                                                                                                      |

| 1      | х                          |                                                | Fixed  | All                | Unable to write to byte 2 of PCIXPM_PMCSR register when Byte Enables (BE) not 0xF                                                    |

| 2      | х                          | х                                              | No Fix | All                | Poisoned PCI Express* Transaction Layer Packet (TLP) causes error to be logged in PCIX Bridge                                        |

| 3      | х                          | x                                              | No Fix | All                | Downstream PCI Express* interface not logging header for PCI<br>Express* unsupported requests when detected at receiver              |

| 4      | х                          | х                                              | No Fix | All                | PCI Express* Replay timer is not frozen in Recover State                                                                             |

| 5      | х                          | х                                              | No Fix | All                | PCI Express* 2 ms "fail-safe" timer to exit from hot-reset doesn't work                                                              |

| 6      | х                          | x                                              | No Fix | All                | Some inbound PCI Express* transactions that require master abort are logged incorrectly                                              |

| 7      | х                          | х                                              | No Fix | All                | Default value used to calculate L0s exit latency is incorrect.                                                                       |

| 8      | х                          |                                                | Fixed  | All                | Wrong and illegal negotiated width value can be reported for downstream PCI Express* ports                                           |

| 9      | х                          | х                                              | No Fix | All                | HPCCTL register incorrectly located in configuration space                                                                           |

| 10     | х                          |                                                | Fixed  | All                | Max Payload Size register field has wrong default                                                                                    |

| 11     | х                          | х                                              | No Fix | All                | Cache Line Size register should be type RW                                                                                           |

| 12     | х                          |                                                | Fixed  | All                | SATA AHCI version register value incorrect                                                                                           |

| 13     | х                          | х                                              | No Fix | All                | SATA EB buffer overflow should set ERR.E bit instead of ERR.M bit                                                                    |

| 14     | х                          |                                                | Fixed  | All                | Output of the JTAG IDCODE register is a constant '1'                                                                                 |

| 15     | х                          |                                                | Fixed  | All                | Upstream Port captures incorrect value in Device Capabilities register when receives Set_slot_pwr Message                            |

| 16     | х                          |                                                | Fixed  | All                | Incorrect SET_SLOT_PWR Message data payload on Intel® 631xESB/<br>632xESB I/O Controller Hub external downstream ports               |

| 17     | х                          |                                                | Fixed  | All                | Reading LAN PCI function BARS can return incorrect values                                                                            |

| 18     | х                          |                                                | Fixed  | All                | BMC acting as Fast Management Link Master, asserting the FLBINTEX signal can cause loss of synchronization between master and slave. |

| 19     | х                          |                                                | Fixed  | All                | Broadcast Packets Transmitted Counter may wrongly count flow control packets                                                         |

| 20     | х                          | x                                              | No Fix | All                | Good Packets Received Counter may be incorrect due to Link disconnect                                                                |

| 21     | х                          | x                                              | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - FML hold time violation per specification                                            |

| 22     | х                          | х                                              | No Fix | All                | Packets with Symbol error may be counted as good packets                                                                             |

| 23     | х                          |                                                | Fixed  | All                | RNBC counter is not correct                                                                                                          |

| 24     | х                          |                                                | Fixed  | All                | gtx_clk is driven from the crystal in MII 100/10 mode is not synchronized to 125 MHz internal clock.                                 |

| 25     | х                          |                                                | Fixed  | All                | ESI link has no de-emphasis                                                                                                          |

| 26     | х                          | х                                              | No Fix | All                | SATA Default Tx Drive Strength set too High at Gen1/Gen2                                                                             |

| 27     | х                          |                                                | Fixed  | All                | Test port pins that are used for straps are not sampled correctly at PE RESET                                                        |

| Number | Intel®<br>631xESB/<br>632xESB I/O<br>Controller<br>Hub<br>Stepping |     | 31xESB/<br>2xESB I/O<br>ontroller<br>Hub Status |     | ERRATA                                                                                                                                                                                       |

|--------|--------------------------------------------------------------------|-----|-------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | A-0                                                                | A-1 |                                                 |     |                                                                                                                                                                                              |

| 28     | х                                                                  | х   | No Fix                                          | All | PATA config space disappears when secondary IO decode is turned on in native mode                                                                                                            |

| 29     | х                                                                  |     | Fixed                                           | All | PCI Express* lanes not driving to correct level                                                                                                                                              |

| 30     | х                                                                  |     | Fixed                                           | All | IDE setting SRST (software reset) doesn't set the BSY bit.                                                                                                                                   |

| 31     | х                                                                  |     | Fixed                                           | All | MAC Transmission of Preamble violates 802.3 specification.                                                                                                                                   |

| 32     | х                                                                  | x   | No Fix                                          | All | SATA Gen2 Driver current lower than expected.                                                                                                                                                |

| 33     | х                                                                  | х   | No Fix                                          | All | PCI Express* Link Control Register requires word write to update.                                                                                                                            |

| 34     | х                                                                  |     | Fixed                                           | All | PCI Express* downstream ports flag inbound 4K memory read as malformed Transaction Layer Packet (TLP).                                                                                       |

| 35     | х                                                                  |     | Fixed                                           | All | PCI Express* Hot Plug: HPCCTL register not sticky.                                                                                                                                           |

| 36     | x                                                                  |     | Fixed                                           | All | PCI Express* Hot Plug: HPCCTL Start-of-day Power Fault not latched for port B in two single-byte mode.                                                                                       |

| 37     | x                                                                  |     | Fixed                                           | All | Intel® 631xESB/632xESB I/O Controller Hub unable to enter the PCI Express* Power Management Link States L0s, L1 and L2 on ports PE1, PE2, and Intel® 631xESB/632xESB I/O Controller Hub LAN. |

| 38     | х                                                                  |     | Fixed                                           | All | PCI Express* Hot-Plug: Hot swap to lower link width fails.                                                                                                                                   |

| 39     | х                                                                  | x   | No Fix                                          | All | PCI Express* port PEO Link layer should drop Data Link Layer Packets (DLLPs) with unknown encoding type.                                                                                     |

| 40     | x                                                                  | x   | No Fix                                          | All | Intel® 631xESB/632xESB I/O Controller Hub does not ignore a PCI Express* Null Packet on port PEO.                                                                                            |

| 41     | x                                                                  | x   | No Fix                                          | All | Intel® 631xESB/632xESB I/O Controller Hub sending less than the minimum number of Power Management Acknowledgments (PMAKs) to SATA.                                                          |

| 42     | x                                                                  | x   | No Fix                                          | All | Advanced Host Controller Interface (AHCI): Improper length register device-to-host FIS.                                                                                                      |

| 43     | x                                                                  |     | Fixed                                           | All | Standard Hot-Plug Controller (SHPC) Message Signaled Interrupt (MSI) is lost/corrupted after PCI config access to 0x78 or 0x7C.                                                              |

| 44     | х                                                                  | х   | No Fix                                          | All | PCI Express* Extended Tag Capability Bit.                                                                                                                                                    |

| 45     | x                                                                  | x   | No Fix                                          | All | Command register Bus Number field attribute not PCI compliant for the PCI-X bridge.                                                                                                          |

| 46     | х                                                                  |     | Fixed                                           | All | PxSERR errors are logged during BIOS initialization when running at 3Gbps on a small percentage of parts                                                                                     |

| 47     | х                                                                  |     | Fixed                                           | All | Intel® 631xESB/632xESB I/O Controller Hub LAN: When the IDE is disabled by firmware all the BARs return 7F.                                                                                  |

| 48     | x                                                                  | x   | No Fix                                          | All | PCI Express* Link Training Status and State Machine (LTSSM) on PE1<br>and PE2 incorrectly sends TS1-PAD-PAD in<br>Configuration.Linkwidth.Start.                                             |

| 49     | х                                                                  |     | Fixed                                           | All | Non-Hot Plug Presence Detect bit not set on PCI Express* ports PE1 and PE2.                                                                                                                  |

| 50     | х                                                                  | х   | No Fix                                          | All | Intel® 631xESB/632xESB I/O Controller Hub LAN not handling Lock<br>Transactions as Unsupported Requests per PCI Express* spec.                                                               |

| 51     | х                                                                  | х   | No Fix                                          | All | Downstream PCI Express* bridges are inaccessible if secondary bus number misconfigured.                                                                                                      |

| 52     | х                                                                  | х   | No Fix                                          | All | Advanced Host Controller Interface (AHCI) Host Bus Adapter (HBA)<br>BSY bit set when recovering from fatal error.                                                                            |

| 53     | х                                                                  | х   | No Fix                                          | All | Noise on PCI Express* TX coming out of Electrical Idle                                                                                                                                       |

| Number | 631x<br>632xE<br>Contr<br>Hu<br>Step | el®<br>ESB/<br>SBI/O<br>roller<br>ub<br>pping | Status | SKUs<br>(optional) | ERRATA                                                                                                                                                 |

|--------|--------------------------------------|-----------------------------------------------|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | A-0                                  | A-1                                           |        |                    |                                                                                                                                                        |

| 54     | х                                    | х                                             | No Fix | All                | IDE VIL not meeting spec                                                                                                                               |

| 55     | х                                    | х                                             | No Fix | All                | JTAG read data corrupted when concurrent config access                                                                                                 |

| 56     | х                                    |                                               | Fixed  | All                | Standard Hot-Plug Controller (SHPC) Hot-Plug PM_PME Requestor ID not correct.                                                                          |

| 57     | х                                    | х                                             | No Fix | All                | PCI Express* Completion timer not halting in L1                                                                                                        |

| 58     | х                                    | х                                             | No Fix | All                | Split-Lock cycle to LPC space resulting in FSB timeout and IERR                                                                                        |

| 59     | х                                    | х                                             | No Fix | All                | PCI Express* SKP/InitFCx Contention                                                                                                                    |

| 60     | х                                    | х                                             | No Fix | All                | Upstream PCI Express* Ports (PE3 & PE4) enter the L1 link state when all downstream devices are NOT in the d3hot power management state.               |

| 61     | х                                    | х                                             | Closed | All                | Interrupt Disable attribute does not correspond to implementation for upstream PCI Express* bridge.                                                    |

| 62     | х                                    | x                                             | Closed | All                | Max Read Request Size config default not PCI compliant for all PCI Express* ports.                                                                     |

| 63     | х                                    | х                                             | No Fix | All                | Under certain conditions, inbound prefetched PCI read requests may return wrong data to the requestor.                                                 |

| 64     | х                                    | х                                             | No Fix | All                | USB 2.0 Transmit Ring-Back failure.                                                                                                                    |

| 65     | x                                    | x                                             | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Cannot read from EEPROM by parallel access on some EEPROMS.                                             |

| 66     | х                                    | х                                             | No Fix | All                | PCI-X clock falling edge slew rate fails spec into test load                                                                                           |

| 67     | х                                    | х                                             | No Fix | All                | Flow Control Completion Data credits may incorrectly update based on length field                                                                      |

| 68     | х                                    | х                                             | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Missed packets or flow control                                                                          |

| 69     | х                                    | х                                             | No Fix | All                | Poisoned TLP generated on PCI Express* MSI hot plug interrupt                                                                                          |

| 70     | ×                                    | x                                             | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Certain values of last ip_option may corrupt RSS decision                                               |

| 71     |                                      | х                                             | No Fix | All                | PCI Express* Hot-Plug interrupt not sent simultaneously with PM_PME                                                                                    |

| 72     | х                                    | х                                             | No Fix | All                | SATA protocol errors detected in PxSERR register during boot                                                                                           |

| 73     | x                                    | х                                             | No Fix | All                | Intel $\circledast$ 631xESB/632xESB I/O Controller Hub LAN: Invalid commas on the Serdes interface corrupts the data integrity of the preceding packet |

| 74     | х                                    | х                                             | No Fix | All                | SATA BSY timeout after Standby Immediate and SRST (after 1ms)                                                                                          |

| 75     | х                                    | х                                             | No Fix | All                | Unsolicited COMINIT while FIS posting pending will corrupt the FIS posting cycle                                                                       |

| 76     | х                                    | х                                             | No Fix | All                | Link Down at Upstream PCI Express* is resulting in failure of training on the Downstream PCI Express*                                                  |

| 77     | х                                    | х                                             | No Fix | All                | Link Control Retrain Link bit not reading 0 when slot is empty                                                                                         |

| 78     | х                                    | х                                             | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Return loss in SERDES                                                                                   |

| 79     | х                                    | х                                             | No Fix | All                | A PCI Express* Downstream ports detect correctable errors while running LOs                                                                            |

| 80     | х                                    | х                                             | No Fix | All                | PCI-Express* Hot-Plug slot disable when downstream link is in L0s or L1 can hang the system                                                            |

| Number         | 631x<br>632xE<br>Cont<br>H | el®<br>ESB/<br>SB I/O<br>roller<br>ub<br>oping | Status            | SKUs<br>(optional) | ERRATA                                                                                                                                                                                     |

|----------------|----------------------------|------------------------------------------------|-------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | A-0                        | A-1                                            |                   |                    |                                                                                                                                                                                            |

| 81             | x                          | х                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Link fail in middle of Rx packet might cause data corruption                                                                                |

| 82             | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - Does not resent pause packet                                                                                                               |

| 83             | x                          | x                                              | No Fix            | All                | Intel $\ensuremath{\circledast}$ 631xESB/632xESB I/O Controller Hub LAN - Ethernet frame length issues                                                                                     |

| 84             | х                          | х                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - IDE BAR4 offset 2                                                                                                                          |

| 85             | x                          | x                                              | No Fix            | All                | Intel $\ensuremath{^{\circ}}$ 631xESB/632xESB I/O Controller Hub LAN - FML - clock extending on the stop cycle                                                                             |

| 86             | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - SERDES is unable to acquire synchronization from ordered sets beginning with /K28.1/ and /K28.7                                            |

| 87             | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - Formed and invalid /C/ code handling                                                                                                       |

| 88             | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - False detection of an idle_match condition                                                                                                 |

| 89             | x                          | x                                              | No Fix            | All                | Intel ${\ensuremath{\mathbb R}}$ 631xESB/632xESB I/O Controller Hub LAN - Ability Match and Acknowledge Match                                                                              |

| 90             | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - ROM FW - Bus may hang when Master reads more bytes than slave reported                                                                     |

| 91             | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - ROM FW - SOL Timeout character control byte in EEPROM image does not function                                                              |

| 92             | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN - ROM FW - BMC fragments that are sent through 2 different SMBUS ports are sent over LAN as a single packet                                  |

| 93             | x                          | x                                              | No Fix            | All                | Intel $\ensuremath{\mathbb{B}}$ 631xESB/632xESB I/O Controller Hub LAN - Time until Jam is longer than it should be                                                                        |

| 94             | x                          | x                                              | No Fix            | All                | Configuration cycle failure when targeting PCI Express* PE1 and PE2 while PM L1 entry sequence is in process                                                                               |

| 95             | x                          | x                                              | No Fix            | All                | PCI Express* ports may gate PM L1 entry based on lack of Flow Control Credit availability                                                                                                  |

| 96             | х                          | х                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub SATA Signal Voltage Level                                                                                                                        |

| 97             | x                          | x                                              | No Fix            | All                | Link control register bit 3 in PCI Express Capability table should be read-only and always return 0 for switch ports                                                                       |

| 98             | х                          | х                                              | No Fix            | All                | Device control register bit 8 should be read-writable if Extended Tag<br>Field Support is indicated                                                                                        |

| 99             | х                          | х                                              | No Fix            | All                | CPU IERR during POST and CPU IERR with hang at OS prompt                                                                                                                                   |

| 100            | х                          | х                                              | No Fix            | All                | ESB2 PCIe switch mis-formats TLPs with ECRC destined to the MCH                                                                                                                            |

| 101            | х                          | х                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Enabling RSS in the Middle of Received Packets May Stop Receive Flow                                                                        |

| <del>102</del> | ×                          | ×                                              | <del>No Fix</del> | All                | Missed RX Packets                                                                                                                                                                          |

| 103            | х                          | х                                              | No Fix            | All                | PCI Express* Replay                                                                                                                                                                        |

| 104            | x                          | x                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: A PHY Register<br>Access via the in-band 82563EB/82564EB Dual/Single-PHY (Kumeran)<br>Interface May Be Executed As A Read of PHY Register 0 |

| 105            | x                          | х                                              | No Fix            | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Overwrites Transmit Descriptors in Internal Buffer                                                                                          |

| Number | Intel®<br>631xESB/<br>632xESB I/O<br>Controller<br>Hub<br>Stepping |     | Status | SKUs<br>(optional) | ERRATA                                                                                                                                                            |

|--------|--------------------------------------------------------------------|-----|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | A-0                                                                | A-1 |        |                    |                                                                                                                                                                   |

| 106    | х                                                                  | х   | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Receive Packet delayed When Using RDTR or RADV Register                                                            |

| 107    | х                                                                  | х   | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: PCIe Missing Replay<br>due to Recovery During TLP Transmission                                                     |

| 108    | х                                                                  | х   | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: Missing Interrupt Following ICR Read                                                                               |

| 109    | х                                                                  | х   | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: PCIe Completion with CA or UR Status is Considered Malformed                                                       |

| 110    | х                                                                  | х   | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: LED Stays on When SerDes is Powered Down                                                                           |

| 111    | х                                                                  | х   | No Fix | All                | Intel® 631xESB/632xESB I/O Controller Hub LAN: PCIe Reception of<br>Completion That Should be Dropped May Occasionally Result in Device<br>Hang or Incorrect Data |

## **Specification Changes**

| Number | SPECIFICATION CHANGES |

|--------|-----------------------|

| 1      | N/A                   |

|        |                       |

#### **Specification Clarifications**

| Number | SPECIFICATION CHANGES                       |

|--------|---------------------------------------------|

| 1      | PCI Downstream Device Disable Clarification |

|        |                                             |

#### **Documentation Changes**

| Number | DOCUMENTATION CHANGES                    |

|--------|------------------------------------------|

| 1      | Content updated to Section 25.1.34       |

| 2      | Content updated to Section 25.2.34       |

| 3      | Content updated to Section 25.3.32       |

| 4      | Content updated to Section 25.4.33       |

| 5      | Content updated to Section 25.5.35       |

| 6      | Content updated to Section 25.6.33       |

| 7      | Content updated to Table4-1              |

| 8      | Content added to Section 5.25            |

| 9      | Content modified to section 23.1.34      |

| 10     | Content updated to Table6-1 and Table6-2 |

| 11     | Content updated to Table6-8              |

## Documentation Changes (Continued)

| Number | DOCUMENTATION CHANGES                                                                                                      |

|--------|----------------------------------------------------------------------------------------------------------------------------|

| 12     | Content updated to Table2-32                                                                                               |

| 13     | Content updated to Section13.6.1.64                                                                                        |

| 14     | Clear figures updated to Figure 9-1 to Figure 9-4                                                                          |

| 15     | Added Table6-20 Intel® 631xESB/632xESB I/O Controller Hub Absolute Maximum Ratings                                         |

| 16     | Section 8.1, changed pin AA36 name from "Reserved" to "PHY_POWER_DOWN", changed pin AB36 name from "Reserved" to "PHYRST#" |

| 17     | Section 8.2, changed pin AA36 name from "Reserved" to "PHY_POWER_DOWN", changed pin AB36 name from "Reserved" to "PHYRST#" |

| 18     | Input Signal Behavior Clarifications                                                                                       |

| 19     | APM_CNT and APM_STS Registers                                                                                              |

# **Identification Information**

#### **Component Identification via Programming Interface**

The Intel® 631xESB/632xESB I/O Controller Hub can be identified by the following register contents:

| Stepping | Vendor ID <sup>a</sup> | Device ID <sup>b</sup> | Revision Number <sup>c</sup> |

|----------|------------------------|------------------------|------------------------------|

| A-0      | 8086h                  | 244Eh                  | D8h                          |

| A-1      | 8086h                  | 244Eh                  | D9h                          |

Notes:

a. The Vendor ID corresponds to bits 15:0 of the Vendor ID Register located at offset 00 - 01h in the PCI function 0 configuration space.

b. The Device ID corresponds to bits 15:0 of the Device ID Register located at offset 02 - 03h in the PCI function 0 configuration space.

c. The Revision Number corresponds to bits 7:0 of the Revision ID Register located at offset 08h in the PCI function 0 configuration space.

#### **Component Marking Information**

The Intel® 631xESB/632xESB I/O Controller Hub stepping can be identified by the following component markings:

| Stepping     | S-Spec | SKU                               | Top Marking | Notes      |

|--------------|--------|-----------------------------------|-------------|------------|

| A-1, leaded  | QJ89   | Intel® 6321ESB I/O Controller Hub | NQ80003ES2  | Sample     |

| A-1, Pb free | QJ90   | Intel® 6321ESB I/O Controller Hub | QG80003ES2  | Sample     |

| A-1, leaded  | QJ93   | Intel® 6311ESB I/O Controller Hub | NQ80003ES2  | Sample     |

| A-1, Pb free | QJ94   | Intel® 6311ESB I/O Controller Hub | QG80003ES2  | Sample     |

| A-1, leaded  | SL97P  | Intel® 6321ESB I/O Controller Hub | NQ80003ES2  | Production |

| A-1, Pb free | SL97Q  | Intel® 6321ESB I/O Controller Hub | QG80003ES2  | Production |

| A-1, leaded  | SL97M  | Intel® 6311ESB I/O Controller Hub | NQ80003ES2  | Production |

| A-1, Pb free | SL97N  | Intel® 6311ESB I/O Controller Hub | QG80003ES2  | Production |

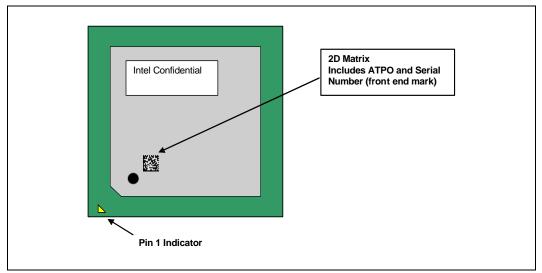

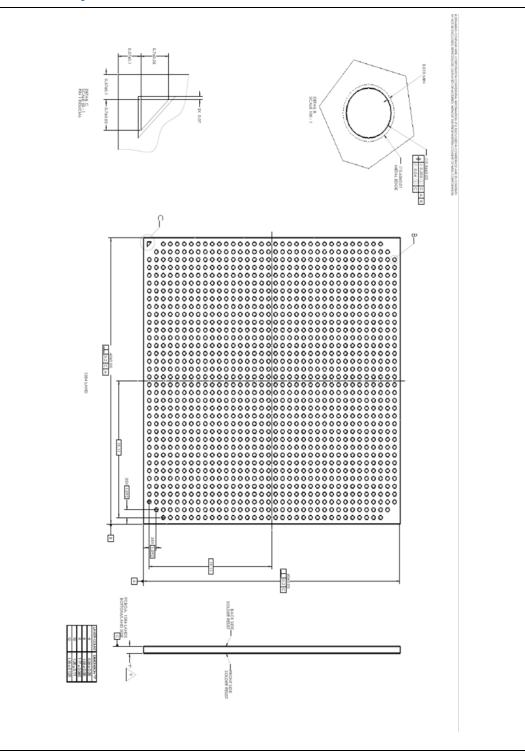

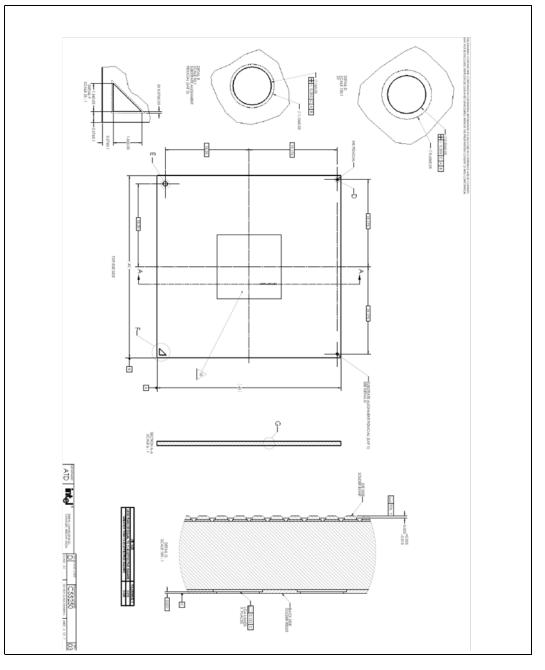

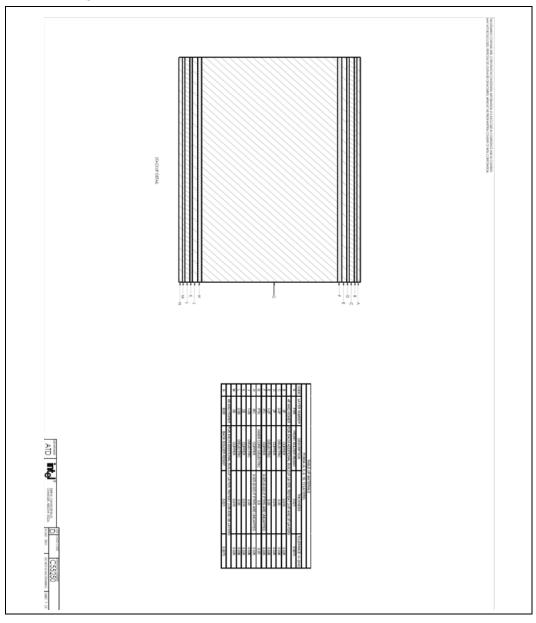

#### Figure 1. Top-Side Marking Example

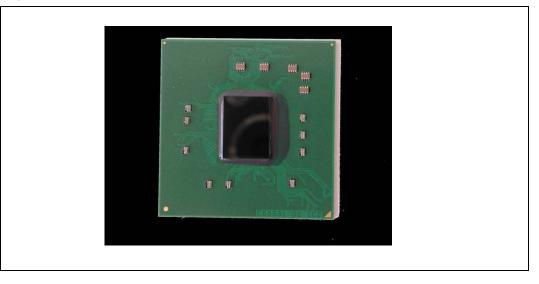

#### Figure 2. Top-Side Photo

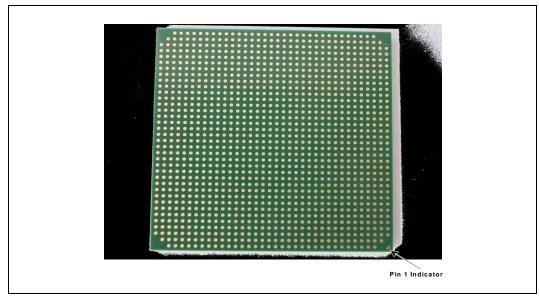

#### Figure 3. Bottom-Side Photo

# Errata

#### 1. Unable to write to byte 2 of PCIXPM\_PMCSR register when Byte Enables (BE) not 0xF

- Problem: Register PCIXPM\_PMCSR (Bm:D0:F3 offset 0x70) in the upstream function control registers (PE3 and PE4) requires full word reads or writes. Partial word reads or writes return 0s.

- Implication: Failure was encountered while running the power management capability test provided in PCI-SIG test suite.

- Workaround: Software may try to write to clear the status bit without affecting D state. To do this (given this bug), a read of register would need to happen first before the write to ensure nothing affects the Dstate.

Status: Fixed

#### 2. Poisoned PCI Express\* Transaction Layer Packet (TLP) causes error to be logged in PCIX Bridge

- Problem: Configuration transactions (both type 0 and type 1) with poisoned TLP targeting either downstream PCI Express\* port or upstream PCI Express\* port (ports PE1 through PE4) cause error to be logged incorrectly. The error is logged in the PCIX Bridge interface (function 3); not PCI Express\* interfaces as expected. Since the cycle is poisoned (EP bit set), the cycle will already be logged at the source of the transaction.

- Implication: Some error handling routines might get confused.

- Workaround: Error handling software must comprehend this issue.

- Status: No Fix

#### 3. Downstream PCI Express\* interface not logging header for PCI Express\* unsupported requests when detected at receiver

- Problem: Downstream PCI Express\* interface (PE1 and PE2) is not logging the header for unsupported request (URREQ) transactions detected at receiver side. Certain illegal inbound transactions are not fully logged as "unsupported requests." While the status bits are set correctly and error messages are generated correctly, the header log is not set. The following illegal transactions are affected: Vendor Defined Type 0 Message routed by ID targeting Intel® 631xESB/632xESB I/O Controller Hub internal bus. PM active state NAK message with TC = 000. Vendor Defined Messages with routing set to "Terminate at receiver. Messages with routing "terminate at receiver" with encodings not defined in Spec. Receive Set\_Slot\_Power\_Limit message inbound with tc = 000. Messages except PME\_TO\_ACK with routing as "Gather and route to RC. Messages with reserved routing fields

- Implication: This bug violates the PCI Express\* Specification. It is also in the compliance checklist: SYS.2.7#20 - If an unsupported request is received the receiver must log the header of the TLP that caused the error in the header log register if the register is currently invalid. This bug violates the PCI Express\* Specification but is not expected to cause any functional failures.

Workaround: NA Status: No Fix

#### 4. PCI Express\* Replay timer is not frozen in Recover State

- Problem: The PCI Express\* Replay Timer is a fail-safe timer defined in the PCI Express\* Specification such that if a link does not receive an Ack or Nack within a predefined time, it assumes it received a Nack and resends the packet(s). According to the PCI Express\* spec (section 3.5.2.1) the Replay Timer should be frozen during link retraining. The bug is that in Intel® 631xESB/632xESB I/O Controller Hub, the Replay Timer continues counting during link retraining. This means Intel® 631xESB/632xESB I/O Controller Hub can retry a transaction after retraining sooner than it should (bug exists in PE1 though PE4 PCI Express\* ports).

- Implication: This bug violates the PCI Express\* Specification but is not expected to cause any functional failures.

- Workaround: NA

- Status: No Fix

## 5. PCI Express\* 2 ms "fail-safe" timer to exit from hot-reset doesn't work

- Problem: The 2 ms timeout signal transition from Hot-reset to Detect doesn't occur when LTSSM is in hot reset. When a PCI Express\* link is put in hot reset, the specification defines a 2 ms timeout timer as a "fail-safe" exit mode from hot reset. See PCI Express\* 1.0a specification section 4.2.6.10, page 199: "Otherwise, after a 2 ms timeout next state is Detect". In Intel® 631xESB/632xESB I/O Controller Hub, the timer doesn't work. The upstream PCI Express\* port (PE4) correctly exits hot reset when the hot reset condition is removed and the bus goes into electrical idle. The downstream PCI Express\* ports (PE1 and PE2) correctly exit hot reset when warm reset goes inactive.

- Implication: This bug violates the PCI Express\* Specification but is not expected to cause any functional failures. The 2 ms is a fail-safe defined in the specification.

- Workaround: NA

- Status: No Fix

## 6. Some inbound PCI Express\* transactions that require master abort are logged incorrectly

- Problem: For specific inbound transactions on PCI Express\* that require a "master abort" response, Intel® 631xESB/632xESB I/O Controller Hub is logging in upstream PCI Express\* port that it replied with a master abort when that logging is not required. The specific cases are those in which the inbound transaction is master aborted by the PCI Express\* downstream port before the transaction reaches the internal switch, but it is logged as though it reached the internal switch before getting master aborted. These are the specific cases: Loopback addresses. BME (bus master enable) disabled. I/O transactions. Config transactions.

- Implication: Although the downstream PCI Express\* agent logs that it received a master abort, it doesn't cause a failure to also log this in Intel® 631xESB/632xESB I/O Controller Hub (upstream port interface).

Workaround: NA

Status: No Fix

#### 7. Default value used to calculate LOs exit latency is incorrect.

Problem: The downstream PCI Express\* links can operate in either common-clock mode or in non-common-clock mode. When the first PCI Express\* port is in non-common-clock

Errata

mode and the second PCI Express\* port is in common-clock mode; then when the<br/>second port exits from LOs to LO it will always go into recovery.Implication:Takes longer to get into LOWorkaround:BIOS Workaround: Refer to latest Intel® 631xESB/632xESB I/O Controller Hub BIOS<br/>spec update.Status:No Fix

## 8. Wrong and illegal negotiated width value can be reported for downstream PCI Express\* ports

Problem: For the PCI Express\* downstream ports (PE1 and PE2), incorrect negotiated link width values can be reported in the following situations: Link goes into recovery and "fails-down" to a smaller width. PCI Express\* hot-plug occurs with a different width adapter. Any renegotiation after reset with a different link width. Legal "negotiated width" values for PCI Express\* downstream ports are: x8: 01000, x4: 00100, x1: 00001. If a fail-down occurs during recovery, one of the following illegal values can occur: x8 to x4: 01100 (appears as x12), x8 to x4 to x1: 01101 (undefined), x8 to x1: 01001 (undefined). The other side of the link is not affected and should report the correct width.

- Implication: It is a PCI Express\* compliance failure to report wrong and undefined negotiated link width values.

- Workaround: NA

- Status: Fixed

#### 9. HPCCTL register incorrectly located in configuration space

- Problem: The HPCCTL (Hot Plug Controller Control Register) is located at offset 90 in the configuration space.

- Implication: This register is invisible in normal system configuration.

- Workaround: BIOS Workaround: Details in latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

- Status: No Fix

#### 10. Max Payload Size register field has wrong default

- Problem: Per the PCI Express\* Specification, the "Max Payload Size" of the "Device Control Register" should default to 000b (for 128 bytes max payload size). Intel® 631xESB/ 632xESB I/O Controller Hub silicon default for both upstream and downstream PCI Express\* interfaces is 001b (for 256 bytes). Max Payload Size is a RW value that is set by BIOS after checking the "Supported Max Payload Size" capability (a RO bit) in the "Device Capability Register" for each function in the hierarchy. Legal values for Max Payload Size in Intel® 631xESB/632xESB I/O Controller Hub are "0" (128 bytes) or "1" (256 bytes). There is no problem setting the bit to either 0 or 1 because Intel® 631xESB/632xESB I/O Controller Hub is a switch and only passes through large packets; Intel® 631xESB/632xESB I/O Controller Hub does not generate them. Affects ports PE1 through PE4.

- Implication: This is a PCI Express\* Specification violation. The PCI-SIG provided PCI Express\* Compliance Test will report failure.

Workaround: NA

Status: Fixed

#### 11. Cache Line Size register should be type RW

- Problem: Per the PCI Specifications, "Cache Line Size (CLS) Register" should default to type "RW" but in the IOxAPIC configuration space it is type "RO". The CLS register is not used in IOxAPIC, but for compatibility with legacy PCI the register is defined to be RW. The CLS register for all the other functions in Intel® 631xESB/632xESB I/O Controller Hub is correctly set to RW.

- Implication: This is a PCI Specification\* violation. The PCI-SIG provided Compliance Test will report failure with IOxAPIC enabled. This bug violates the PCI Express\* Specification but is not expected to cause any functional failures

Workaround: NA.

Status: No Fix

#### 12. SATA AHCI version register value incorrect

- Problem: Index/Data pair scheme was added to AHCI 1.1 specification; Intel® 631xESB/ 632xESB I/O Controller Hub implements the Index/Data pair scheme but the SATA AHCI version register has a value of 0001000h indicating AHCI spec 1.0.

- Implication: BIOS reading SATA AHCI register will not know that Intel® 631xESB/632xESB I/O Controller Hub supports Index-Data pair.

- Workaround: BIOS workaround: See latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

- Status: Fixed

#### 13. SATA EB buffer overflow should set ERR.E bit instead of ERR.M bit

- Problem: Intel® 631xESB/632xESB I/O Controller Hub erroneously sets PxSERR: [M] (Recovered Communication Error) when the internal elasticity buffer experiences an overflow or if a miss-align is detected after PhyRDY is detected. A miss-align may happen during resume from the Partial or Slumber link PM states and will cause the M-bit to be erroneously set.

- Implication: As a result of M-bit setting while resuming, the host will set the Interface Non-Fatal Error Status (INFS) bit since it happens while the interface has no Frame Information Structure being transferred or received. INFS is expected to be recoverable by S/W (mostly ignored) and should not have an impact to subsequent command execution. No restart of the controller is needed in this case.

Workaround: NA Status: No Fix

#### 14. Output of the JTAG IDCODE register is a constant '1'

Problem: When performing a JTAG IDCODE instruction the output of the IDCODE register of other devices that appear before the Intel® 631xESB/632xESB I/O Controller Hub in the chain will be a constant '1' instead of the actual contents of the IDCODE register. Therefore, it is impossible to read the contents of the IDCODE register.

Implication: Cannot read IDCODE correctly.

Workaround: There are four possible workarounds for A0 1) Don't do a JTAG IDCODE instruction on Intel® 631xESB/632xESB I/O Controller Hub 2) Put Intel® 631xESB/632xESB I/O Controller Hub JTAG in BYPASS mode 3) Physically bypass Intel® 631xESB/632xESB I/

O Controller Hub JTAG via board strappings 4) Put Intel® 631xESB/632xESB I/O Controller Hub first in the JTAG chain.

Status:

Fixed

## 15. Upstream Port captures incorrect value in Device Capabilities register when receives Set\_slot\_pwr Message

Problem: When Intel® 631xESB/632xESB I/O Controller Hub Switch Upstream Port (PE3 or PE4) receives a SET\_SLOT\_PWR Message, it does not capture the data payload correctly. The data payload provides the Slot Power Limit Scale and Slot Power Limit Value to be stored in Device Capabilities register (Intel® 631xESB/632xESB I/O Controller Hub upstream port, offset 0x48 [27:26], [25:18]). Due to this bug, software that reads Device Capabilities register will receive incorrect values for Slot Power Limit Scale and Value.

Implication: Impact considered low since Intel® 631xESB/632xESB I/O Controller Hub does not support any slot power budgeting in IO. Intel® 631xESB/632xESB I/O Controller Hub is non-compliant in this situation though, since if doesn't support slot power budgeting, it should return all 0's for these values in Device Capabilities but it doesn't

Workaround: NA

Status: Fixed.

#### 16. Incorrect SET\_SLOT\_PWR Message data payload on Intel® 631xESB/ 632xESB I/O Controller Hub external downstream ports

- Problem: Intel® 631xESB/632xESB I/O Controller Hub external downstream ports (PE1, PE2) send incorrect values for data payload of SET\_SLOT\_PWR Message. The Slot Capabilities Register (offset 0x58) Slot Power Limit Scale [16:15], and Slot Power Limit Value [14:7] contain the values that should map to data payload [9:8][7:0] respectively. The mapping is incorrect which results in the payload bits [9:0] being 0's. PCI Express\* 1.0a spec in Section 6.9 states that switch downstream ports must not transmit a value lower than lowest value specified by electromechanical spec for slot's form factor. In this case, the payload is transmitting a value of 0.

- Implication: PCI Express\* specification compliance issue. Possible functional issue; compatibility. Possible worst case is that a PCI Express\* adapter would exceed power budget but SW would think it is fine.

Workaround: NA

Status: Fixed

#### 17. Reading LAN PCI function BARS can return incorrect values

Problem: The functions LANO and LAN1 each have 3 BARS (MEM, FLASH, and IO). There are two cases that result in bad decoding: 1) If memory BAR (BARO) of LANO or LAN1 is not initialized, then any access to any function will be directed to BARO of the same function. 2) If memory BARs of both LAN functions are enabled and flash BAR (BAR1) of LANO or LAN1 is disabled then any access to any function will be directed to BAR1 of the same function.

Implication: BARS may contain incorrect values.

Workaround: BIOS Workaround: Must fully initialize LANO and LAN1 functions.

Status: Fixed

## 18. BMC acting as Fast Management Link Master, asserting the FLBINTEX signal can cause loss of synchronization between master and slave.

- Problem: When the Intel® 631xESB/632xESB I/O Controller Hub FML port is configured to work as an FML master, the slave may stop the master by pulling down the FLBINTEX pin. The FML e-spec allows asserting FLBINTEX (active low) 53nsec after the last SMBCLK falling edge. Intel® 631xESB/632xESB I/O Controller Hub can stand only 49nsec. If the slave device asserts the FLBINTEX after 49nsec, the synchronization between master and slave will be lost.

- Implication: This transaction will probably be repeated forever, depending on the application in the slave device. Most known FML slave devices assert FLBINTEX early enough for Intel® 631xESB/632xESB I/O Controller Hub to sample.

Workaround: NA

Status: Fixed

## 19. Broadcast Packets Transmitted Counter may wrongly count flow control packets

- Problem: All flow control packets that are sent after host transmission of broadcast packet till host transmission of non-broadcast packet are wrongly counted by BPTC (Broadcast Packets Transmitted Count) counter.

- Implication: BPTC counter may be incorrect.

Workaround: NA

Status: Fixed

## 20. Good Packets Received Counter may be incorrect due to Link disconnect

- Problem: Good Packets Received Counter (GPRC) statistics counters may count a packet interrupted by Link disconnect. This packet should not be counted due to CRC error

- Implication: The Good Packets Received Counter (GPRC) may show a slightly higher number than expected upon the rare events of link disconnect. This counter is only used for statistics, the exact number is not significant.

Workaround: NA

Status: No Fix

## 21. Intel® 631xESB/632xESB I/O Controller Hub LAN - FML hold time violation per specification

- Problem: The FML specification defines the hold time for the FML inputs as Ons from the falling edge of the clock. When Intel® 631xESB/632xESB I/O Controller Hub LAN is in master mode (in which it generates the clock to the slave), hold time of 2ns should be provided in order for the Intel® 631xESB/632xESB I/O Controller Hub to sample the data correctly.

- Implication: Since the Intel® 631xESB/632xESB I/O Controller Hub drives the clock, and the slave identifies a falling edge of the clock before it drives the data, hold time of Ons is not realistic and would not happen in a real system.

#### Workaround: NA

Status: No Fix

Errata

#### 22. Packets with Symbol error may be counted as good packets

Problem: When a symbol error occurs just after start of packet, the packet is rejected, but the GPRC counter counts this packet as good packet and the RXERRC Counter doesn't count it as a bad packet.

Implication: The implication of this bug is that it will cause both counters values to be slightly inaccurate. This bug is not expected to cause any functional failures.

Workaround: NA

Status: No Fix

#### 23. RNBC counter is not correct

- Problem: This counter is intended to count the number of packets received when no host memory buffer is available. When in muliple recieve queue mode, the counter may count false events and may not count real events

- Implication: The implication of this bug is that the value of RNBC register does not reflect the number of packets received with no available host buffer.

Workaround: NA

Status: Fixed

## 24. gtx\_clk is driven from the crystal in MII 100/10 mode is not synchronized to 125 MHz internal clock.

- Problem: Kumeran block communicates with the MAC using MII/ GMII interface. The MII and Kumeran clocks should be balanced as there is no synchronization level. As designed, the external reference clock supports two input frequencies: 25 MHz and 62.5 MHz. When the external reference clock's input frequency is 25 MHz, GTX\_CLK, an internal GMII signal, is driven from the reference clock's input and thus not synchronized to the 125 MHz clock that is used.

- Implication: The implication of this bug is that only the 62.5 MHz crystal mode can be used with Kumeran until this bug is fixed (i.e. no support for 25Mhz crystal).

- Workaround: NA

- Status: Fixed

#### 25. ESI link has no de-emphasis

- Problem: De-emphasis is when the 1st bit of a series of bits in a serial data stream is driven to a slightly higher level (for a 1) than the succeeding same type bits (or a slightly lower level for a 0). Verified de-emphasis registers setting for ESI link on Intel® 631xESB/ 632xESB I/O Controller Hub; they are all set to 0 which is disabled (de-emphasis off). De-emphasis should be set on by default when in AC coupled full-swing mode.

- Implication: Signal integrity could be degraded.

Workaround: BIOS Workaround: See latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

Status: Fixed

#### 26. SATA Default Tx Drive Strength set too High at Gen1/Gen2

Problem: Drive strength default settings for Intel® 631xESB/632xESB I/O Controller Hub are too high; causing Vdiffp-p to violate specification.

Implication: Spec violation.

Workaround: BIOS Workaround: See latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

Status: No Fix

## 27. Test port pins that are used for straps are not sampled correctly at PE RESET

- Problem: When Intel® 631xESB/632xESB I/O Controller Hub LAN is in ARC JTAG state, i.e. the ARC debugger is connected through the JTAG interface, the test port bits 2, 3, 6, and 7are constantly driving out "0". Upon assertion of PERST# these pins become inputs and should sample the test port strap value which should be "1". The problem is that the pull-up resistor changes the pin value slowly resulting in a "0" value sampled, and causing glitches on the internal BMC clock.

- Implication: The BMC behavior is unpredictable.

- Workaround: Board workaround add tri-state buffer that will strongly drive a "1" when PERST# is asserted.

Status: Fixed

## 28. PATA config space disappears when secondary IO decode is turned on in native mode

- Problem: When the following values are programmed into the PATA (Bus 0h Dev 1Fh Function 1h), the first eight bytes (offset 00h to 07h) of the PCI Configuration space disappear and show the value of 7Fh. Write 07h to offset 04h, write 80h to offset 41h, write 80h to offset 43h, write 8Fh to offset 09h. It seems that the secondary IO decode interferes with the configuration space on config read. The config write still seems to decode correctly.

- Implication: Possible problems with IDE driver, causing an inability to boot the IDE drive.

- Workaround: BIOS Workaround: See latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

- Status: No Fix

#### 29. PCI Express\* lanes not driving to correct level

- Problem: PCI Express\* downstream ports not driving to correct level. ~900mVp-p on lane 0. All other lanes showing about 300mVp-p. PE1 and PE2 configured as x8:Lane 0 = normal amplitude (~900mVp-p); Lanes 1-7 = low amplitude (~300mVp-p). PE1 and PE2 configured as separated x4s:Lane 0 of PE1 and Lane 0 of PE2 = normal amplitude (~900mVp-p); Lanes 1-3 of PE1 and Lanes 1-3 of PE2 = low amplitude (~300mVp-p).

- Implication: This bug violates the PCI Express\* Specification but is not expected to cause any functional failures.

- Workaround: NA

Status: Fixed

#### 30. IDE setting SRST (software reset) doesn't set the BSY bit.

Problem: Setting SRST doesn't set the BSY bit. According to the IDE spec, when Host asserts IDE SRST command, the BSY bits in IDE Status registers should be set but they are not.

Errata

| Implication: | The IDE driver in windows may disable the IDE function. |

|--------------|---------------------------------------------------------|

| Workaround:  | NA                                                      |

| Status:      | Fixed                                                   |

#### 31. MAC Transmission of Preamble violates 802.3 specification.

Problem: In 100FD/HD and 100FD/HD, the DUT transmits only 6 bytes of Preamble instead of 7 bytes. This behavior violates 802.3 spec.

Implication: This is a compliance issue, should not have any affect on network behavior. These packets are received correctly by the link partner.

Workaround: NA

Status: Fixed

#### 32. SATA Gen2 Driver current lower than expected.

| Problem:     | Serial ATA Gen2 main driver current measurements are lower than expected. |

|--------------|---------------------------------------------------------------------------|

| Implication: | Possible eye violations.                                                  |

| Workaround:  | BIOS workaround - see BIOS spec update.                                   |

| Status:      | No Fix                                                                    |

#### 33. PCI Express\* Link Control Register requires word write to update.

Problem: A one byte configuration write at Bm: D0: F3 offset 57h to set slot clock configuration bit fails to update. A word (two bytes) write to set slot clock configuration bit works fine. Affects ports PE1 though PE4.

Implication:Both offsets 56h and 57h must be written to at the same time for a write to take place.Workaround:BIOS Workaround: See latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

Status: No Fix

## 34. PCI Express\* downstream ports flag inbound 4K memory read as malformed Transaction Layer Packet (TLP).

Problem: PCI Express\* downstream ports (PE1 and PE2) flag inbound 4K memory read requests as malformed TLP. The downstream ports will log the malformed TLP error and discard the memory read requests. This condition could occur if downstream devices can generate read requests up to 4KB.

- Implication: Inbound 4K memory read request will fail and the downstream device will lose flow control credit.

- Workaround: BIOS Workaround: See latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

- Status: Fixed.

#### Errata

#### 35. PCI Express\* Hot Plug: HPCCTL register not sticky.

Problem: The HPCCTL register (Hot Plug Controller Control Register at offset 0x90 in the configuration space) is not sticky across power cycles, but the Slot Capabilities register for Hot-Plug Capable is read/write once sticky (RWOS). Affects ports PE1 and PE2.

Implication: This prevents the correct PCA955x device type from being selected on a warm reset.

Workaround: NA.

Status: Fixed

## 36. PCI Express\* Hot Plug: HPCCTL Start-of-day Power Fault not latched for port B in two single-byte mode.

Problem: When configured for two (dual) single-byte PCA9554 (or PCA9554A) mode, the Intel® 631xESB/632xESB I/O Controller Hub does not latch a start-of-day power fault on port B. Affects ports PE1 and PE2.

Implication: Software would not be aware of a potential start-of-day power-fault and thus would not be able to notify the user why the device in the slot was not working.

Workaround: NA.

Status: Fixed

#### 37. Intel® 631xESB/632xESB I/O Controller Hub unable to enter the PCI Express\* Power Management Link States L0s, L1 and L2 on ports PE1, PE2, and Intel® 631xESB/632xESB I/O Controller Hub LAN.

- Problem: Intel® 631xESB/632xESB I/O Controller Hub LAN device and PCI Express\* downstream ports PE1, PE2 are not able to transition into the L0s, L1 or L2 power management link states. The Intel® 631xESB/632xESB I/O Controller Hub does not issue an acknowledge message to devices on PE1, PE2, or Intel® 631xESB/632xESB I/ O Controller Hub LAN that are requesting to go into any of the power management link states.

- Implication: 1) ASPM LOs enable register does not enable transmitters to transition into the LOs state on PE1, PE2 PCI Express\* links, and Intel® 631xESB/632xESB I/O Controller Hub LAN . 2) PE1, PE2, and Intel® 631xESB/632xESB I/O Controller Hub LAN links may not enter the L1 and L2 states resulting in a system hang. 3) The system can lock up when attempting to go into S3, S4, or S5. 4) System may hang when the operating system or device driver transitions PCI Express\* endpoints attached to PE1, PE2, or Intel® 631xESB/632xESB I/O Controller Hub LAN ports into the D3 Hot state. 5)Interchanging pre-installed Windows\* OS images between Greencreek LE and Blackford LE based systems may cause a system hang due to device re-discovery and installation which may insert system devices into the D3 Hot state.

- Workaround: Partial BIOS workaround for S5. See latest Intel® 631xESB/632xESB I/O Controller Hub BIOS spec update.

- Status: Fixed

#### 38. PCI Express\* Hot-Plug: Hot swap to lower link width fails.

Problem: Hot-swapping to a lower link width fails on the PCI Express\* ports PE1 and PE2. Failure only occurs for changes to lower link widths, changes to higher widths do not fail.

Implication: Will not be able to hot-swap to lower link width.

Workaround: NA.

Status: Fixed.

## **39.** PCI Express\* port PEO Link layer should drop Data Link Layer Packets (DLLPs) with unknown encoding type.