# Intel<sup>®</sup> Xeon<sup>™</sup> Processor and Intel<sup>®</sup> 860 Chipset Platform

**Design Guide**

Document Number: 298252-004

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Xeon™ processor and Intel<sup>®</sup> 860 chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel, Intel logo, Pentium, Intel NetBurst, and Intel Xeon are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright<sup>©</sup> Intel Corporation 2001-2002

### **Contents**

| 1 | Introd                                                           | uction                                           |                                                                     | 19       |  |  |  |

|---|------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|----------|--|--|--|

|   | 1.1                                                              | Related                                          | Documentation                                                       | 20       |  |  |  |

|   | 1.2                                                              |                                                  | tions and Terminology                                               |          |  |  |  |

|   | 1.3                                                              |                                                  | Overview                                                            |          |  |  |  |

|   | 1.0                                                              | 1.3.1                                            | Processor Overview                                                  |          |  |  |  |

|   |                                                                  | 1.3.2                                            | Intel® 860 Chipset                                                  |          |  |  |  |

|   |                                                                  |                                                  | 1.3.2.1 Memory Controller Hub (MCH)                                 |          |  |  |  |

|   |                                                                  |                                                  | 1.3.2.2 I/O Controller Hub 2 (Intel® ICH2)                          | 27       |  |  |  |

|   |                                                                  |                                                  | 1.3.2.3 Memory Repeater Hub for Direct RDRAM* Device (Intel® MRH-R) |          |  |  |  |

|   |                                                                  |                                                  | 1.3.2.4 PCI 64-Bit Hub (Intel® P64H)                                | 28       |  |  |  |

|   |                                                                  | 1.3.3                                            | Bandwidth Summary                                                   |          |  |  |  |

|   |                                                                  | 1.3.4                                            | System Configurations                                               |          |  |  |  |

|   | 1.4                                                              | Platform                                         | ı Initiatives                                                       |          |  |  |  |

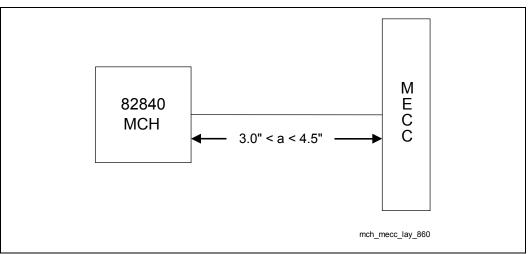

|   |                                                                  | 1.4.1                                            | Memory Expansion Card (MEC) and Connector (MECC)                    | 30       |  |  |  |

|   |                                                                  | 1.4.2                                            | Intel® 860 Chipset MCH                                              | 30       |  |  |  |

|   |                                                                  |                                                  | 1.4.2.1 Direct RDRAM* Device Interface                              |          |  |  |  |

|   |                                                                  |                                                  | 1.4.2.2 Accelerated Graphics Port (AGP)                             | 30       |  |  |  |

|   |                                                                  | 1.4.3                                            | Intel® ICH2                                                         | 31       |  |  |  |

|   |                                                                  |                                                  | 1.4.3.1 Integrated LAN Controller                                   |          |  |  |  |

|   |                                                                  |                                                  | 1.4.3.2 Audio Codec '97 (AC'97) 6-Channel Support                   | 32       |  |  |  |

|   |                                                                  |                                                  | 1.4.3.3 Low Pin Count (LPC) Interface                               |          |  |  |  |

|   |                                                                  |                                                  | 1.4.3.4 Ultra ATA                                                   | 33       |  |  |  |

|   |                                                                  | 1.4.4                                            | 1.4.3.5 Universal Serial Bus (USB)                                  |          |  |  |  |

|   | 1 5                                                              |                                                  | Manageability                                                       |          |  |  |  |

|   | 1.5                                                              | 1.5.1                                            | n Compliance                                                        |          |  |  |  |

|   |                                                                  | _                                                | PC 99/2001                                                          |          |  |  |  |

| 2 | Comp                                                             | •                                                | out                                                                 |          |  |  |  |

|   | 2.1 Intel <sup>®</sup> Xeon™ Processor Component Quadrant Layout |                                                  |                                                                     |          |  |  |  |

|   | 2.2                                                              | 2.2 Intel® 860 Chipset Component Quadrant Layout |                                                                     |          |  |  |  |

| 3 | Platfo                                                           | rm Stack-                                        | Up and Placement Overview                                           | 43       |  |  |  |

|   | 3.1                                                              |                                                  | Component Placement                                                 |          |  |  |  |

|   | 3.2                                                              |                                                  | ay System Stack-Up                                                  |          |  |  |  |

|   | 0.2                                                              | 3.2.1                                            | Design Recommendations                                              |          |  |  |  |

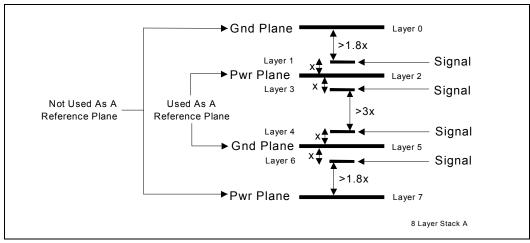

|   |                                                                  | 0.2.1                                            | 3.2.1.1 Stack-Up Option A                                           |          |  |  |  |

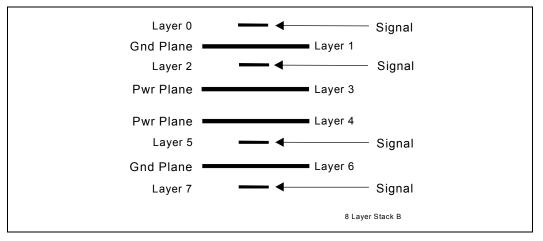

|   |                                                                  |                                                  | 3.2.1.2 Stack-Up Option B                                           |          |  |  |  |

|   |                                                                  | 3.2.2                                            | Design Considerations                                               |          |  |  |  |

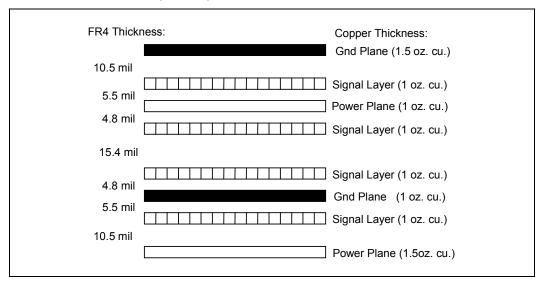

|   |                                                                  |                                                  | 3.2.2.1 Stack-Up Example A                                          |          |  |  |  |

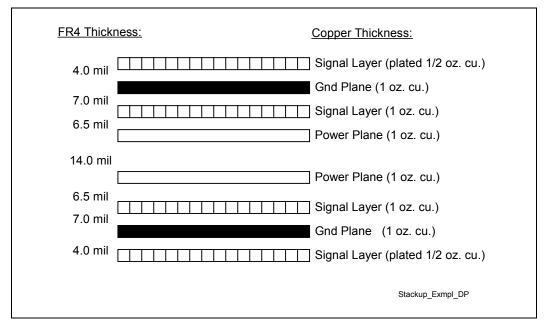

|   |                                                                  |                                                  | 3.2.2.2 Stack-Up Example B                                          | 48       |  |  |  |

| 4 | Platfo                                                           | rm Clock I                                       | Routing Guidelines                                                  | 51       |  |  |  |

|   | 4.1                                                              | Routina                                          | Guidelines for Host Clocks                                          | 52       |  |  |  |

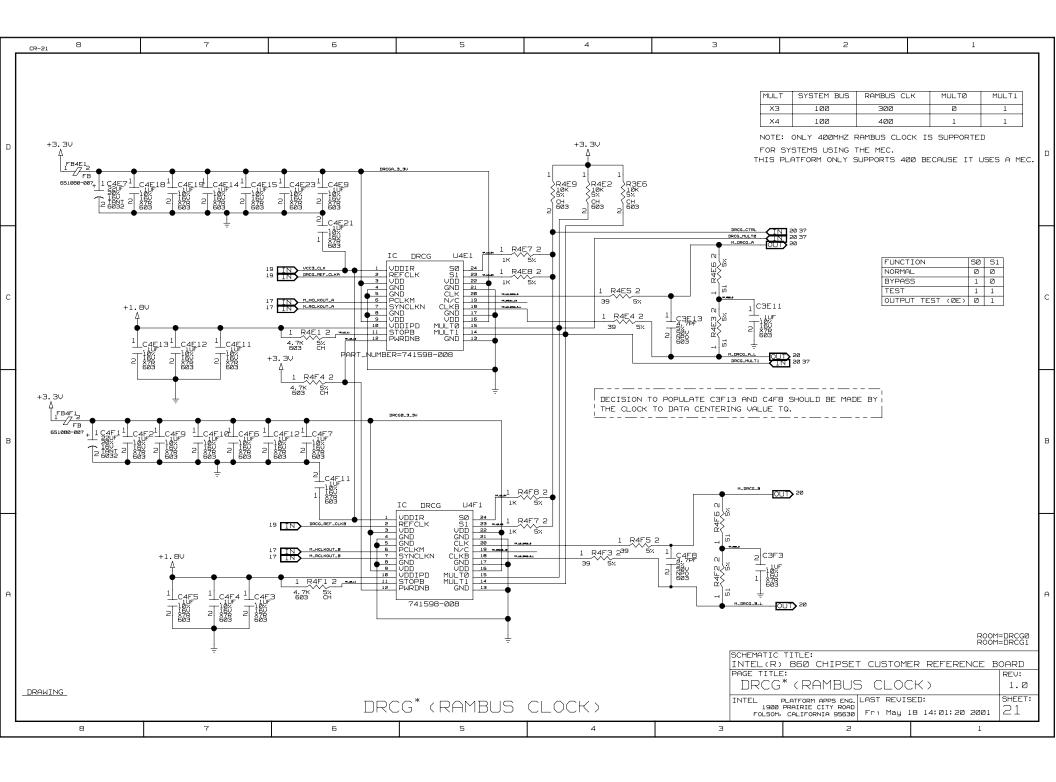

|   | 4.2                                                              | -                                                | Guidelines for Direct Rambus* Clock Generators (DRCG Devices).      |          |  |  |  |

|   | <b>⊤.∠</b>                                                       |                                                  | CKy SKS to DRCG: Reference Clocks                                   | 57<br>57 |  |  |  |

|   |     | 4.2.2       |              | DRCG* Device: Phase Aligning Clocks                   | 58  |

|---|-----|-------------|--------------|-------------------------------------------------------|-----|

|   |     | 4.2.3       | DRCG* I      | Device Signals to Rambus* Channels                    | E0  |

|   |     |             | 4.2.3.1      | z/400 MHz Clocks)  Trace Length Recommendations       | 58  |

|   |     |             | 4.2.3.1      | Topology Considerations                               |     |

|   |     |             | 4.2.3.3      |                                                       | 01  |

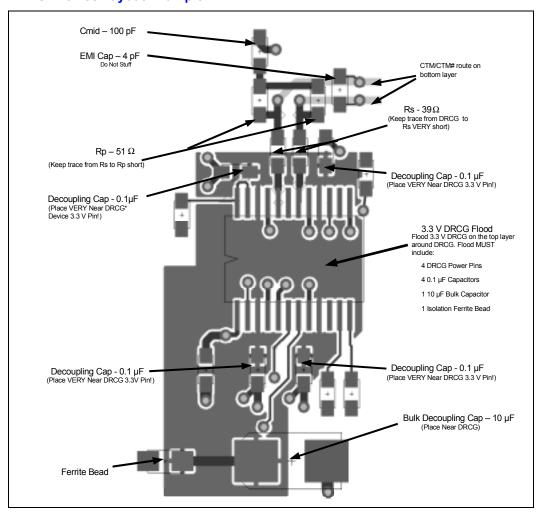

|   |     | 4.2.4       |              | Device Impedance Matching Circuit                     | 62  |

|   |     | 4.2.5       | DRCG* I      | Device Layout Example                                 | 64  |

|   | 4.3 |             |              | s for 66 MHz and 33 MHz Clocks                        |     |

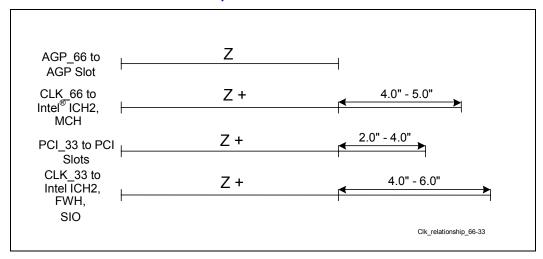

|   | 4.0 | 4.3.1       |              | 33 MHz Clock Relationships                            |     |

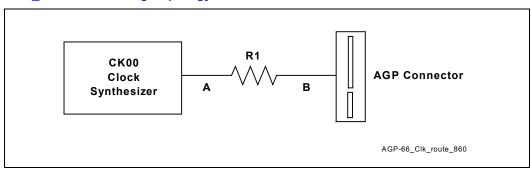

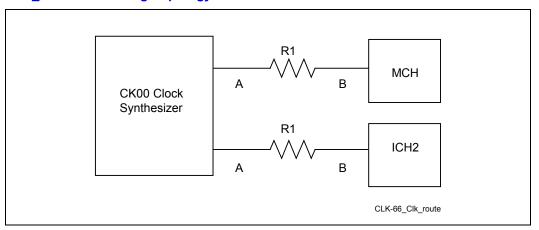

|   |     | 4.3.2       |              | Clock Routing Length Guidelines                       |     |

|   |     | 4.3.3       |              | Clock Routing Length Guidelines                       |     |

|   |     | 4.3.4       |              | 4H PCI Clock Routing Guidelines                       |     |

|   |     |             | 4.3.4.1      | Intel® P64H PCI 33 MHz Clock Routing Guidelines       | 68  |

|   |     |             | 4.3.4.2      |                                                       | 69  |

| _ | 0   | D D.        | 41           | -                                                     |     |

| 5 | •   |             | •            |                                                       |     |

|   | 5.1 | Return      | Path         |                                                       | 72  |

|   | 5.2 | Serpen      | tine Routing | g                                                     | 73  |

|   | 5.3 | System      | Bus Decoi    | upling Requirements                                   | 73  |

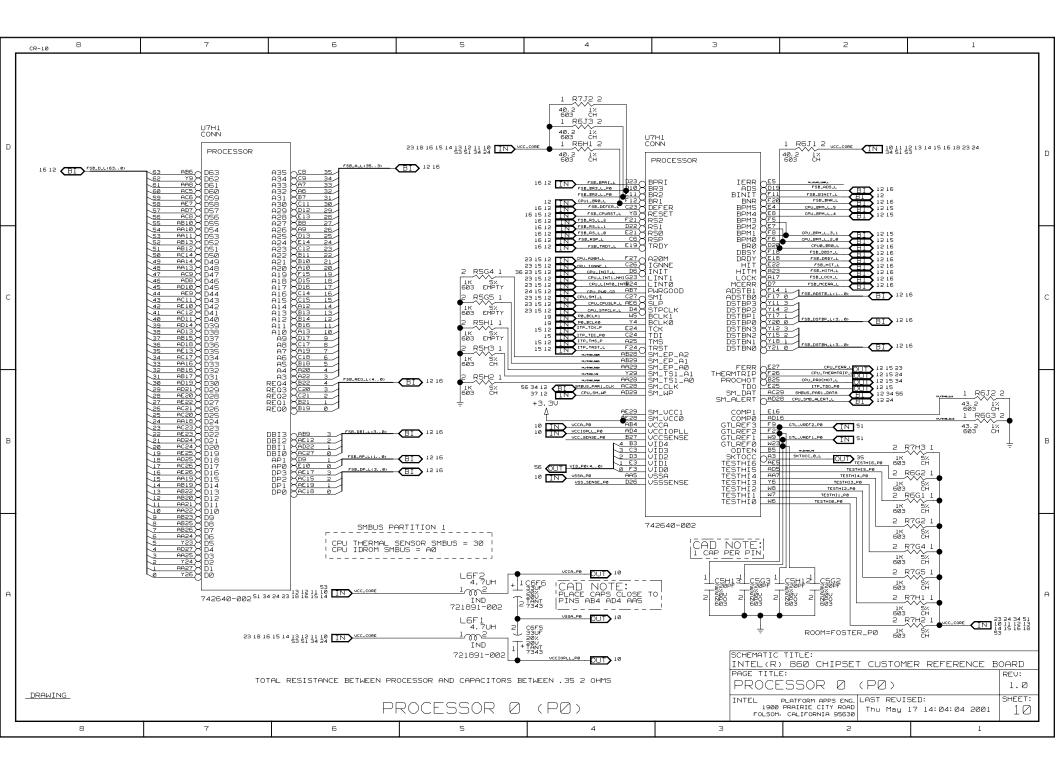

|   |     | 5.3.1       | Processo     | or I/O Decoupling Requirements                        | 74  |

|   | 5.4 | Dual Pr     |              | onfiguration                                          |     |

|   |     | 5.4.1       |              | Guidelines for Source Synchronous Signals             |     |

|   |     |             | 5.4.1.1      | 4X Group (DSTBN[3:0]#, DSTBP[3:0]#, D[63:0]#,         |     |

|   |     |             |              | DBI[3:0]#):                                           | 79  |

|   |     |             | 5.4.1.2      | 2X Group (ADSTB[1:0]#, A[35:3]#, REQ[4:0]#)           |     |

|   |     |             | 5.4.1.3      | Common Clock                                          | 81  |

|   |     |             | 5.4.1.4      | Wired-OR Signals (BINIT#, BNR#, HIT#, HITM#,          |     |

|   |     |             |              | MCERR#)                                               | 81  |

|   |     | 5.4.2       |              | Guidelines for Asynchronous GTL+ and Other System Bus |     |

|   |     |             |              | Taraban A Assarbance OTI - Obsarb Disarbanta          | 83  |

|   |     |             | 5.4.2.1      | Topology 1: Asynchronous GTL+ Signals Driven by the   | 0.4 |

|   |     |             | 5.4.2.2      | Processor                                             | 64  |

|   |     |             | 5.4.2.2      | ChipsetChipset                                        | 97  |

|   |     |             | 5.4.2.3      | Topology 3: VID[4:0]                                  |     |

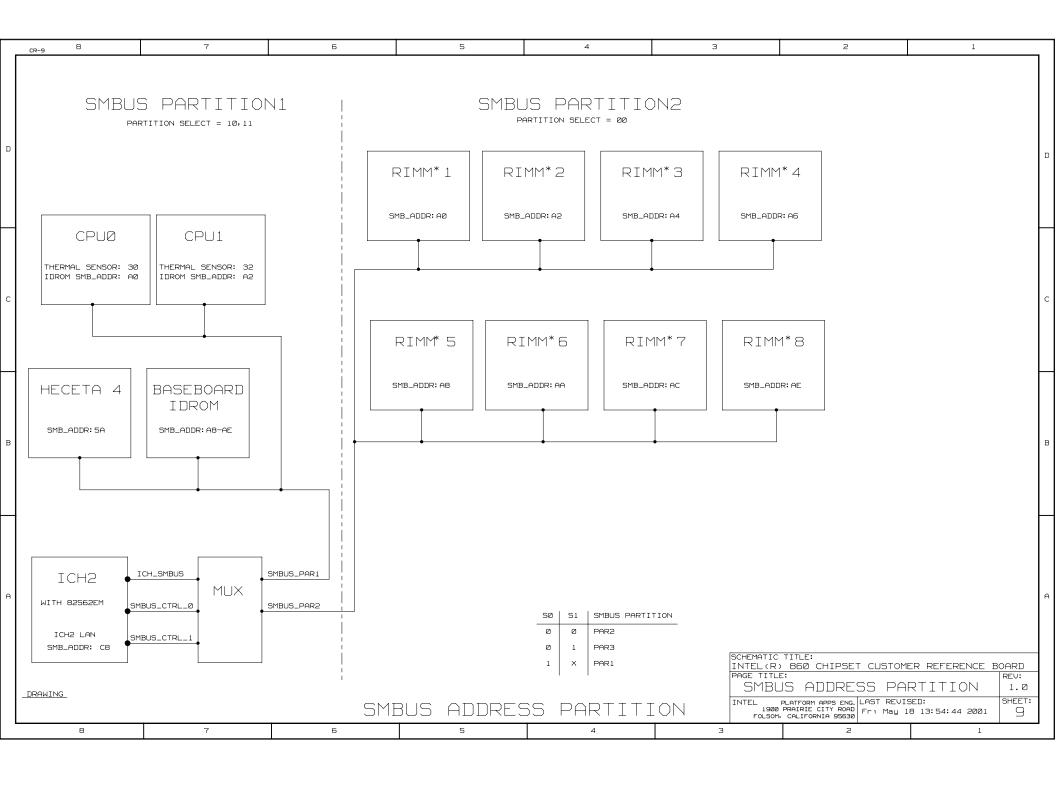

|   |     |             | 5.4.2.4      | Topology 4: SMBus Signals                             |     |

|   |     |             | 5.4.2.5      | Topology 5: BR[3:0]# Signals                          |     |

|   |     |             | 5.4.2.6      | Topology 6: COMP[1:0] Signals                         |     |

|   |     |             | 5.4.2.7      | Topology 7: ODTEN Signal                              |     |

|   |     |             | 5.4.2.8      | Topology 8: TESTHI[6:0] Signals                       |     |

|   |     |             | 5.4.2.9      | Topology 9: SKTOCC# Signal                            |     |

|   | 5.5 | MCH S       |              | Interface                                             |     |

|   |     | 5.5.1       |              | stem Bus I/O Decoupling Recommendations               |     |

| 6 | Mem | ory Interfa | ce Routing   |                                                       | 97  |

|   | 6.1 | Rambu       | s* Channel   | Overview                                              | 97  |

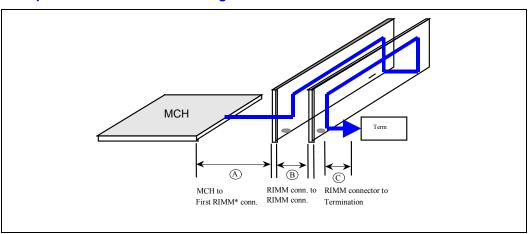

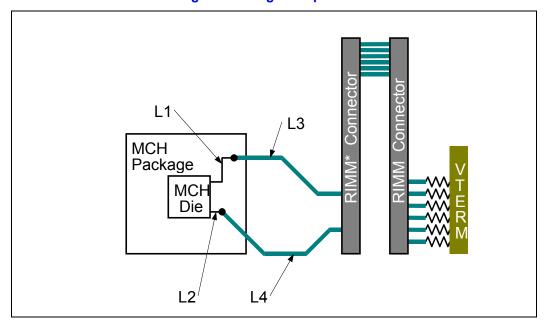

|   | 6.2 |             |              | th MEC/MECC (Inner Laver Routing)                     |     |

|   | 6.3    | Rambus* (    | Channel Routing Guidelines                                                          | 99           |

|---|--------|--------------|-------------------------------------------------------------------------------------|--------------|

|   |        | 6.3.1 F      | Rambus* Signaling Level (RSL) Signals                                               | 100          |

|   |        | 6.3.2 F      | Rambus Signaling Level (RSL) Channel Compensation                                   | 102          |

|   |        | 6            | 3.3.2.1 Package Trace Compensation                                                  |              |

|   |        |              | (RSL and Clocking Signals)                                                          |              |

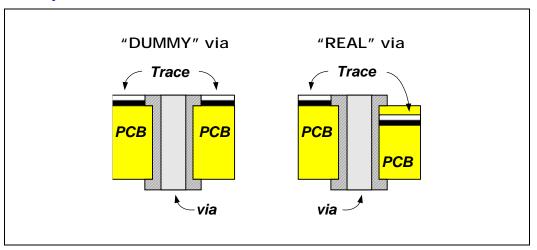

|   |        |              | 3.3.2.2 Via Compensation                                                            |              |

|   |        |              | 3.3.2.3 Differential Clock Compensation                                             | 105          |

|   |        | 6            | S.3.2.4 Signal Layer Alteration for RIMM* Connector Pin                             |              |

|   |        |              | Compensation                                                                        | 105          |

|   |        |              | 8.3.2.5 RIMM* Connector Impedance Compensation                                      |              |

|   |        | 6.3.3 F      | RSL Signal Termination                                                              | 110          |

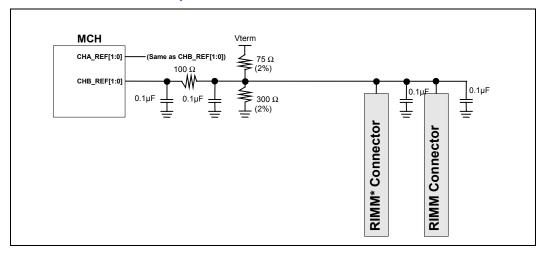

|   |        |              | Direct RDRAM* Device Reference Voltage                                              |              |

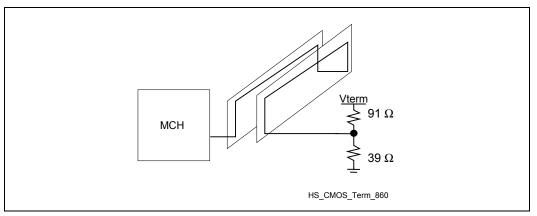

|   |        |              | High Speed CMOS Routing                                                             |              |

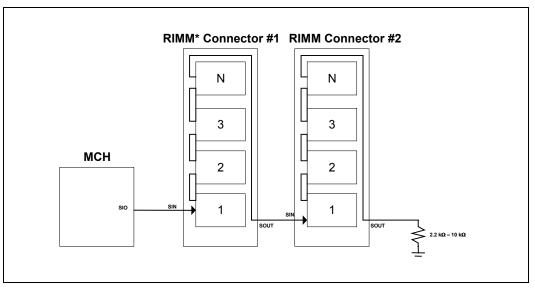

|   |        |              | SIO Routing                                                                         |              |

|   |        |              | Suspend-to-RAM Shunt Transistor                                                     |              |

|   | 6.4    | 1.8 V RAC    | Solution Solution                                                                   | 116          |

| 7 | AGP    | nterface Rou | uting                                                                               | 119          |

| • |        |              | <u> </u>                                                                            |              |

|   | 7.1    |              | ing Guidelines                                                                      |              |

|   |        |              | 1X Timing Domain Signal Routing Guidelines                                          |              |

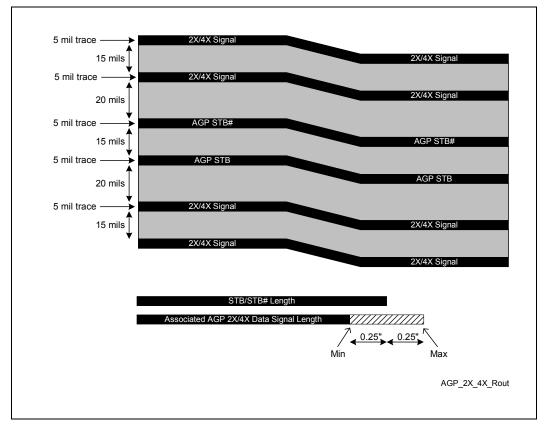

|   |        |              | 2X/4X Timing Domain Signal Routing Guidelines                                       |              |

|   |        | -            |                                                                                     | 121          |

|   |        | ,            | 7.1.2.2 Trace Lengths Greater Than 6 Inches and Less Than 7.25 Inches               | 122          |

|   |        | 7.1.3 A      | AGP Interfaces Trace Length Summary                                                 |              |

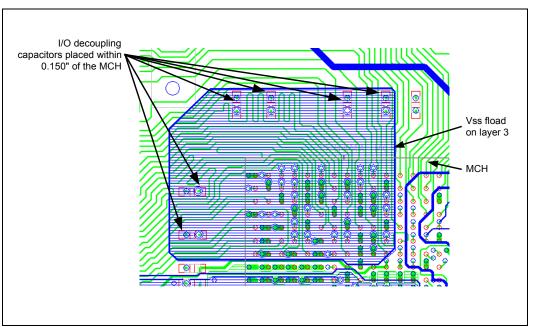

|   |        |              | /O Decoupling Guidelines                                                            |              |

|   |        |              | Signal Power/Ground Referencing Recommendations                                     | 125          |

|   |        |              | VDDQ and TYPEDET#                                                                   |              |

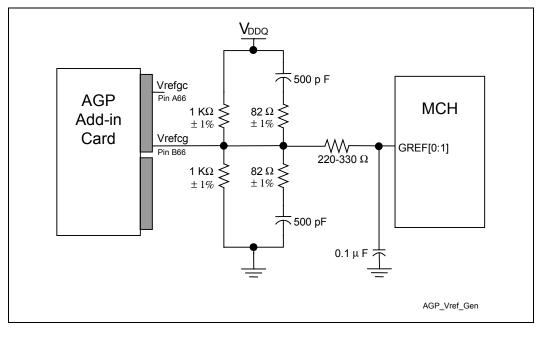

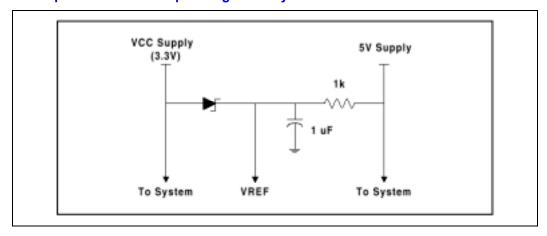

|   |        |              | V <sub>REF</sub> Generation                                                         |              |

|   |        |              | MCH AGP Interface Buffer Compensation                                               |              |

|   |        |              | AGP Pull-Ups/Pull-Downs on AGP Signals                                              |              |

|   |        |              | AGP Signal Voltage Tolerance List                                                   |              |

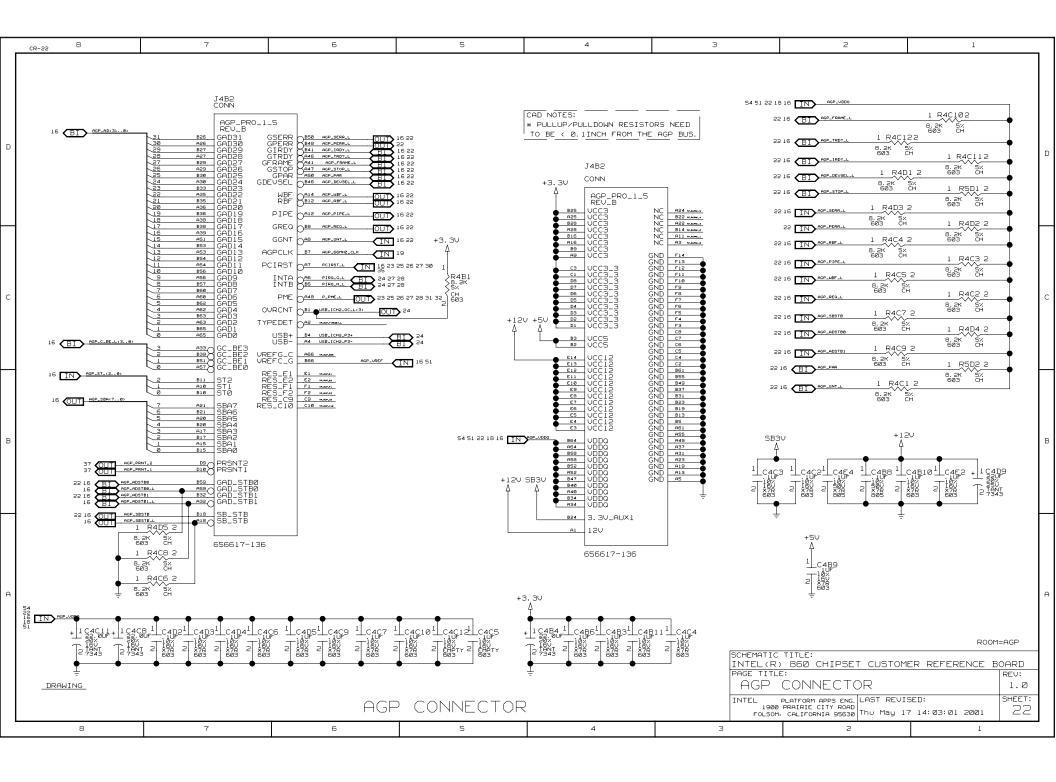

|   |        |              | AGP Connector                                                                       |              |

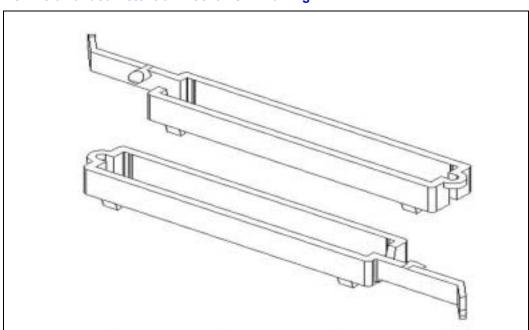

|   | 7.2    |              | ersal Retention Mechanism (RM)                                                      |              |

|   |        |              | ,                                                                                   |              |

| 8 | Hub II | nterface     |                                                                                     | 133          |

|   | 8.1    | PCI 33 MF    | 1z Guidelines                                                                       | 134          |

|   | 8.2    |              | dz Guidelines                                                                       |              |

|   | 8.3    |              | Interface Routing Guidelines                                                        |              |

|   | 0.5    |              | 3-Bit Hub Interface Data Signals                                                    |              |

|   |        |              | 3-Bit Hub Interface Strobe Signals                                                  |              |

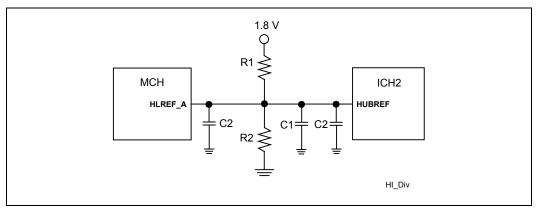

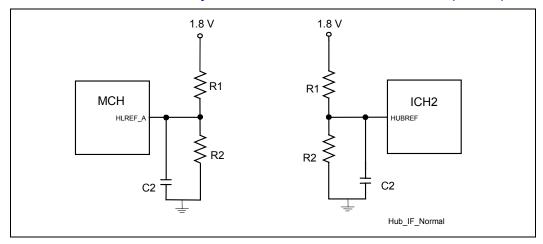

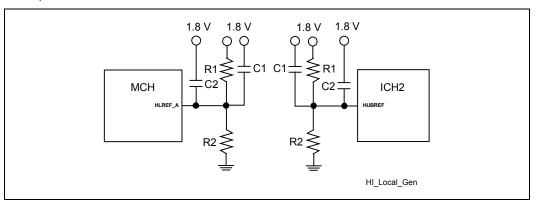

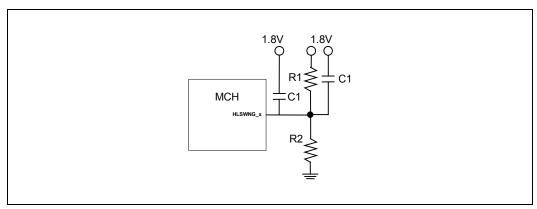

|   |        |              | 3-Bit Hub Interface Strobe SignalsB-Bit Hub Interface HIREF Generation/Distribution |              |

|   |        |              | 3-Bit Hub Interface Compensation                                                    |              |

|   |        |              | 3-Bit Hub Interface Decoupling Guidelines                                           | 139          |

|   | 8.4    |              | Interface Routing Guidelines                                                        |              |

|   | 0.4    |              | 16-Bit Hub Interface Data Signals                                                   |              |

|   |        |              | 16-Bit Hub Interface Strobe Signals                                                 |              |

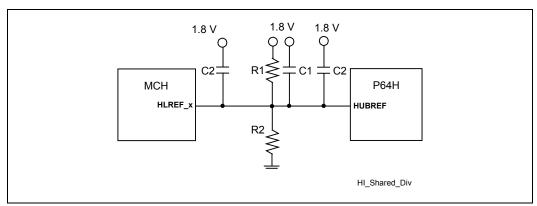

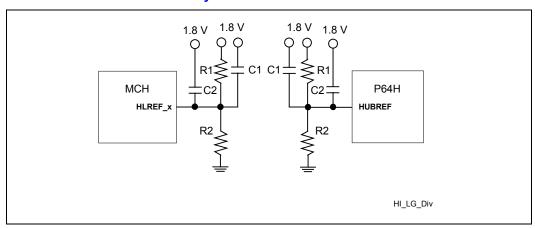

|   |        |              | 16-Bit Hub Interface HIREF Generation/Distribution                                  |              |

|   |        |              | 16-Bit Hub Interface Compensation Reference Voltage                                 | 170          |

|   |        |              | Generation/Distribution                                                             | 141          |

|   |        |              | 16-Bit Hub Interface Resistive Compensation                                         |              |

|   |        |              | 16-Bit Hub Interface Decoupling Guidelines                                          |              |

|   |        |              | 16-Bit Trace Length Compensation                                                    |              |

|   |        |              |                                                                                     | <del>-</del> |

|   |                                         | 8.4.8       | Unused 16-Bit Hub Interfaces                               | 143 |

|---|-----------------------------------------|-------------|------------------------------------------------------------|-----|

| 9 | I/O Co                                  | ontroller H | lub 2 (Intel <sup>®</sup> ICH2)                            | 145 |

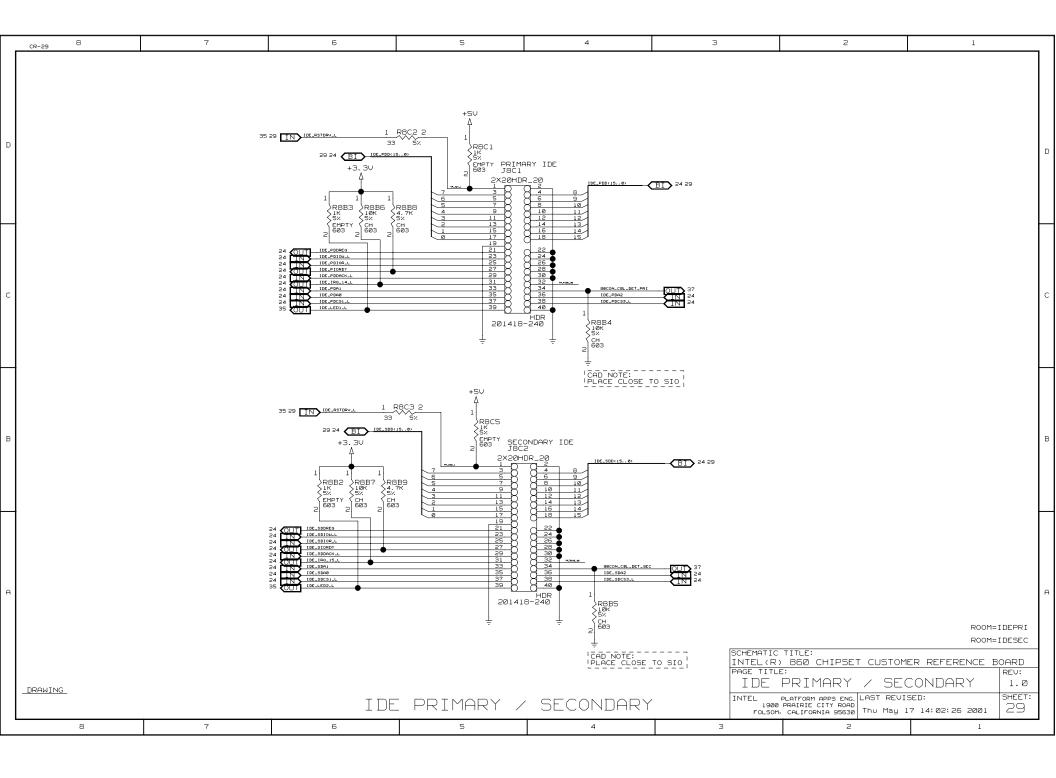

|   | 9.1                                     | IDE Inte    | erface                                                     | 145 |

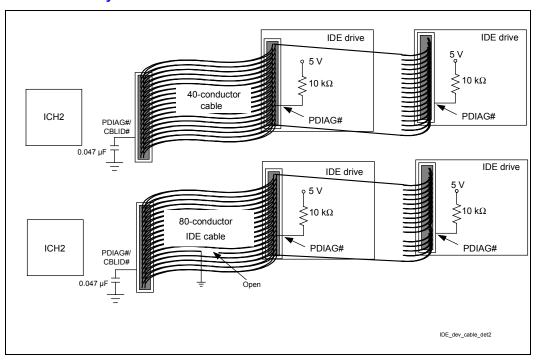

|   | • • • • • • • • • • • • • • • • • • • • | 9.1.1       | IDE Cable                                                  |     |

|   |                                         | 9.1.2       | Cable Detection for Ultra ATA/66 and Ultra ATA/100         |     |

|   |                                         | 0.1.2       | 9.1.2.1 Host/Device-Side Detection                         |     |

|   |                                         |             | 9.1.2.2 Device-Side Cable Detection                        |     |

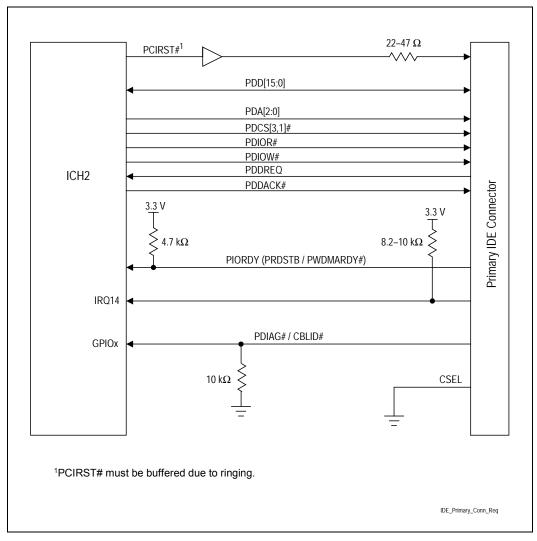

|   |                                         | 9.1.3       | Primary IDE Connector Requirements                         |     |

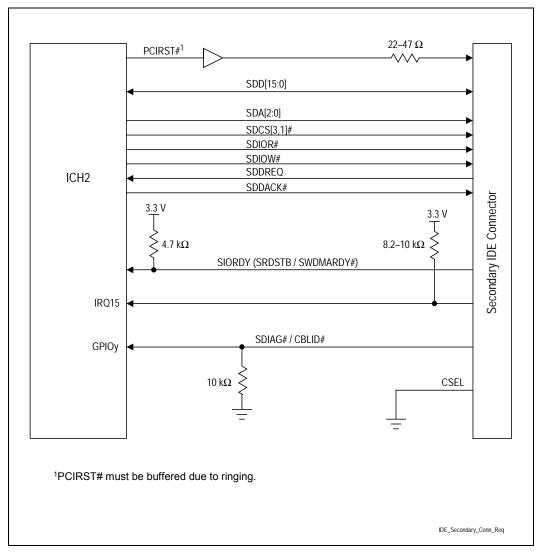

|   |                                         | 9.1.4       | Secondary IDE Connector Requirements                       |     |

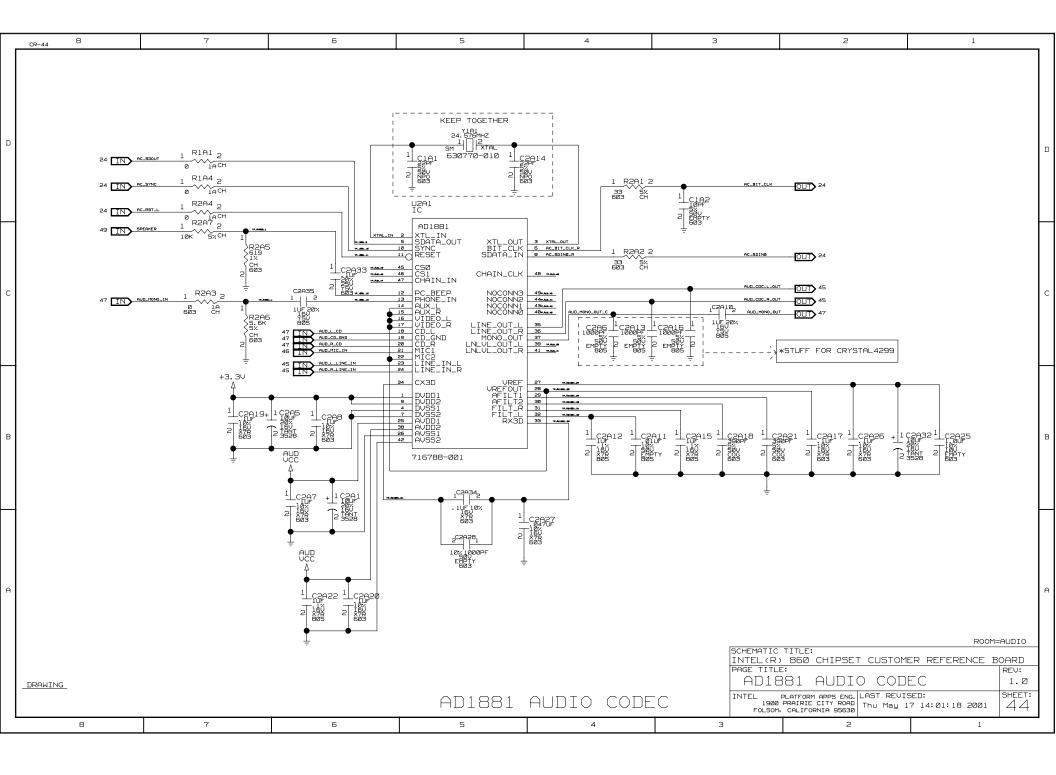

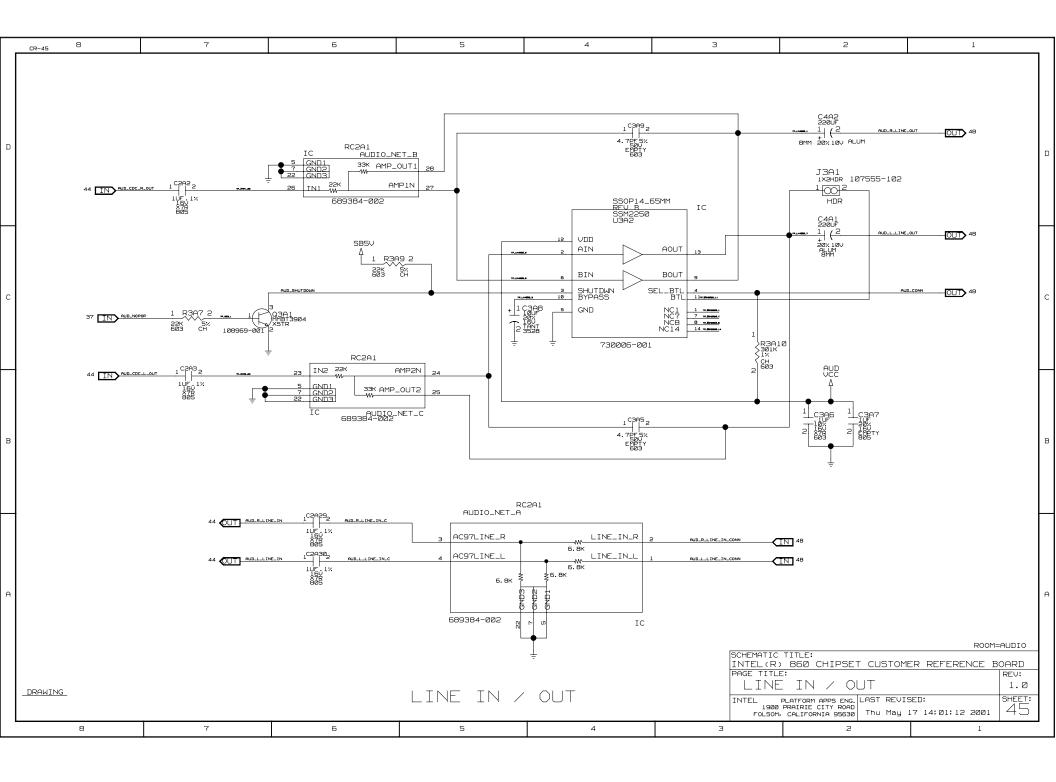

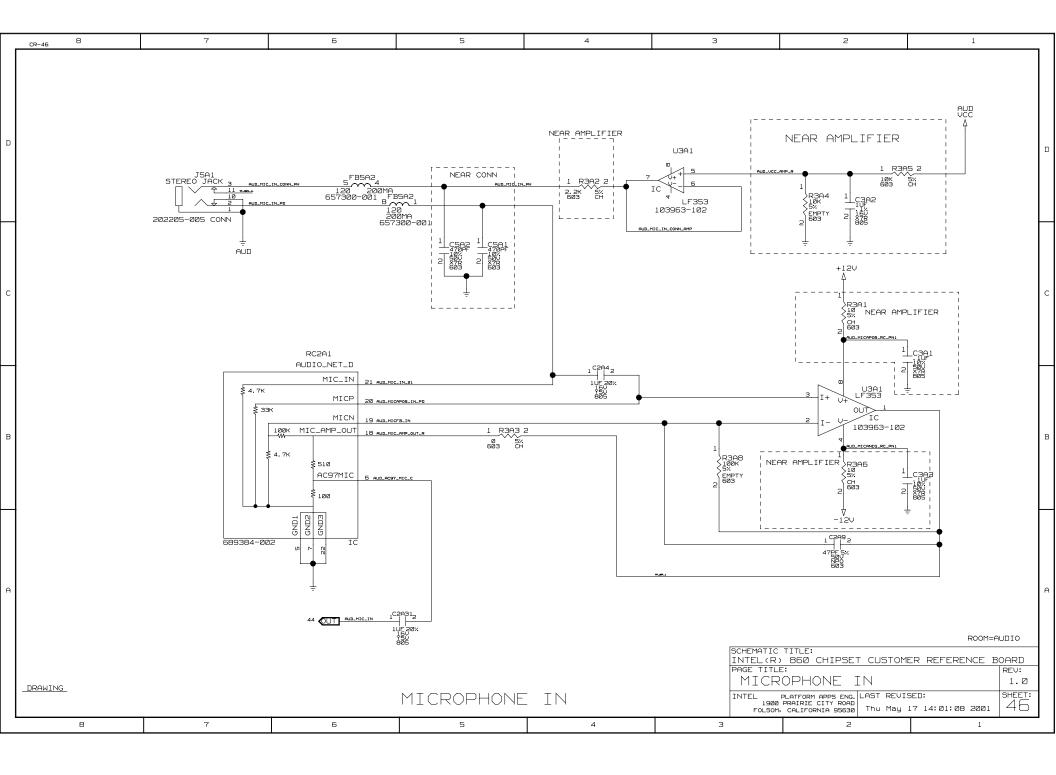

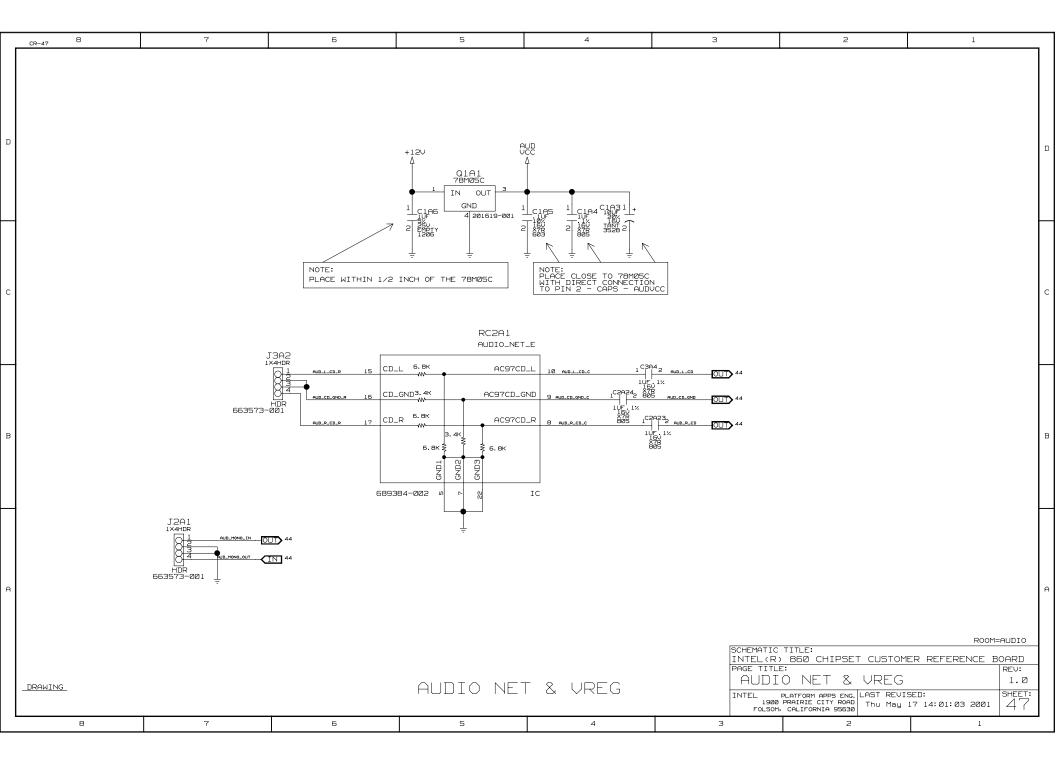

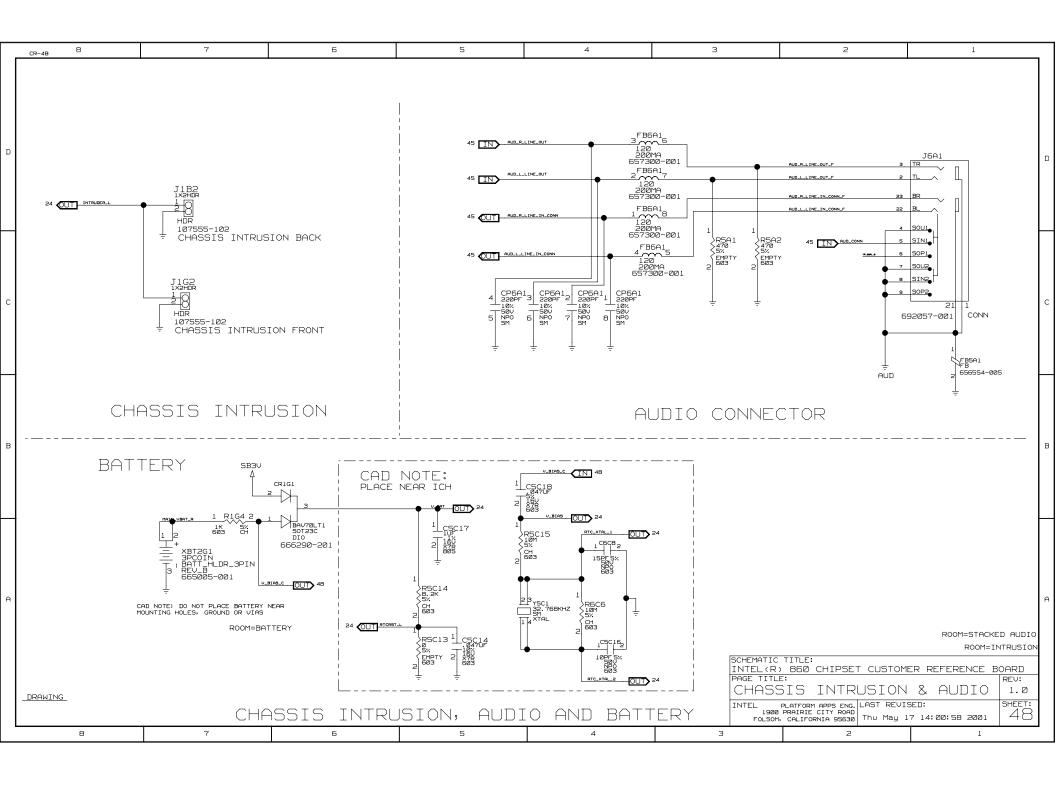

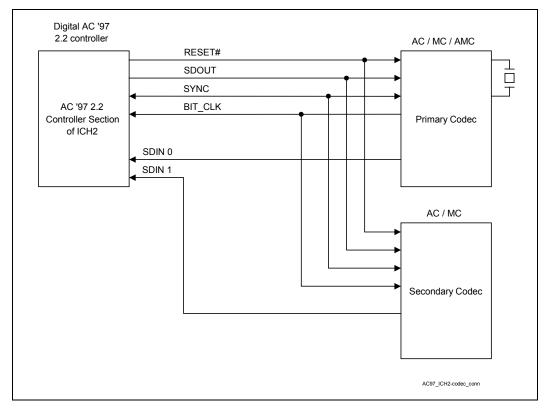

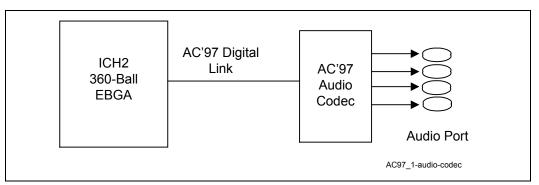

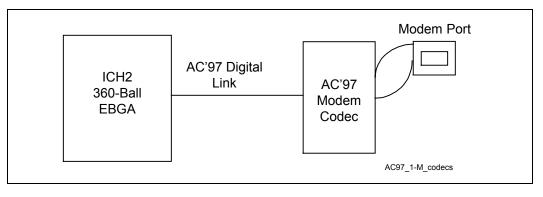

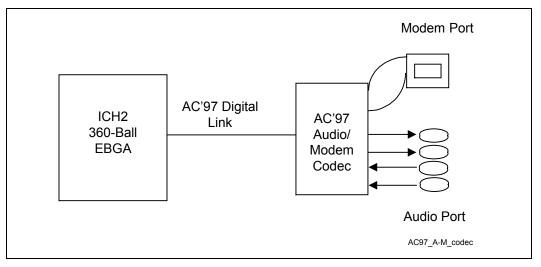

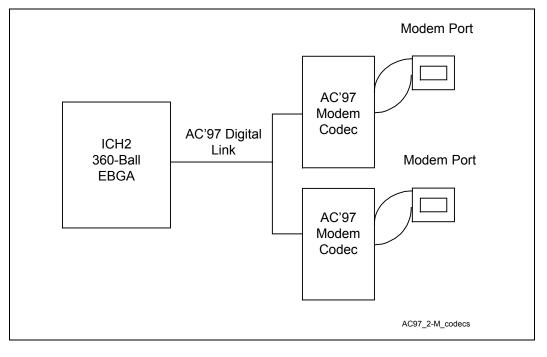

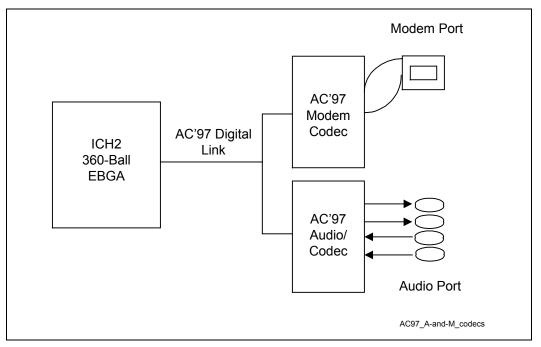

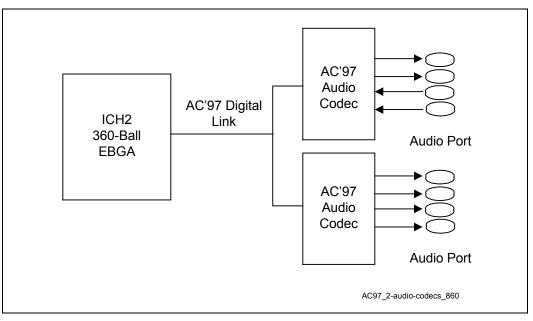

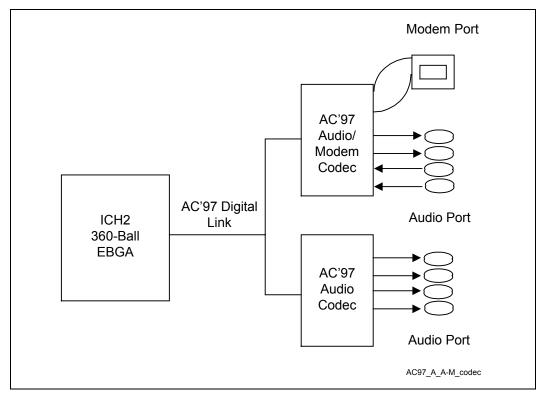

|   | 9.2                                     |             | Codec '97 (AC'97)                                          |     |

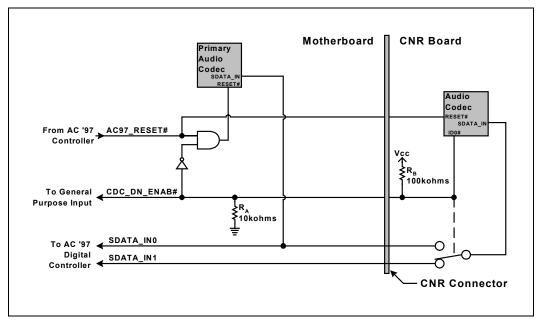

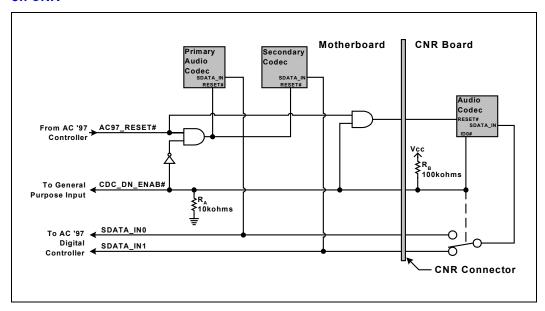

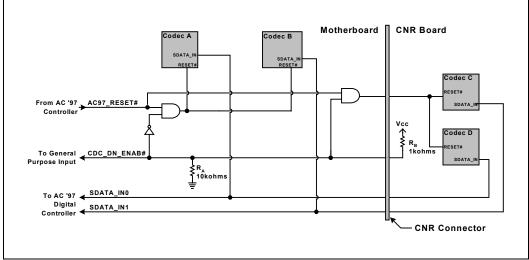

|   | 0.2                                     | 9.2.1       | AC'97 Audio Codec Detect Circuit and Configuration Options |     |

|   |                                         | 9.2.2       | Valid Codec Configurations                                 |     |

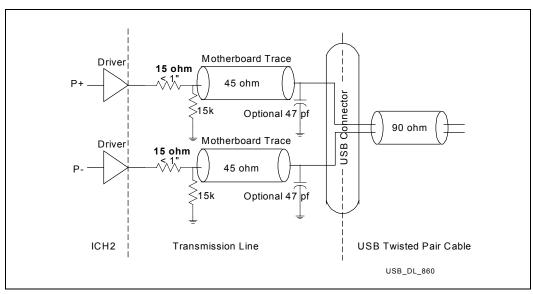

|   | 9.3                                     | -           | uidelines                                                  |     |

|   |                                         |             |                                                            |     |

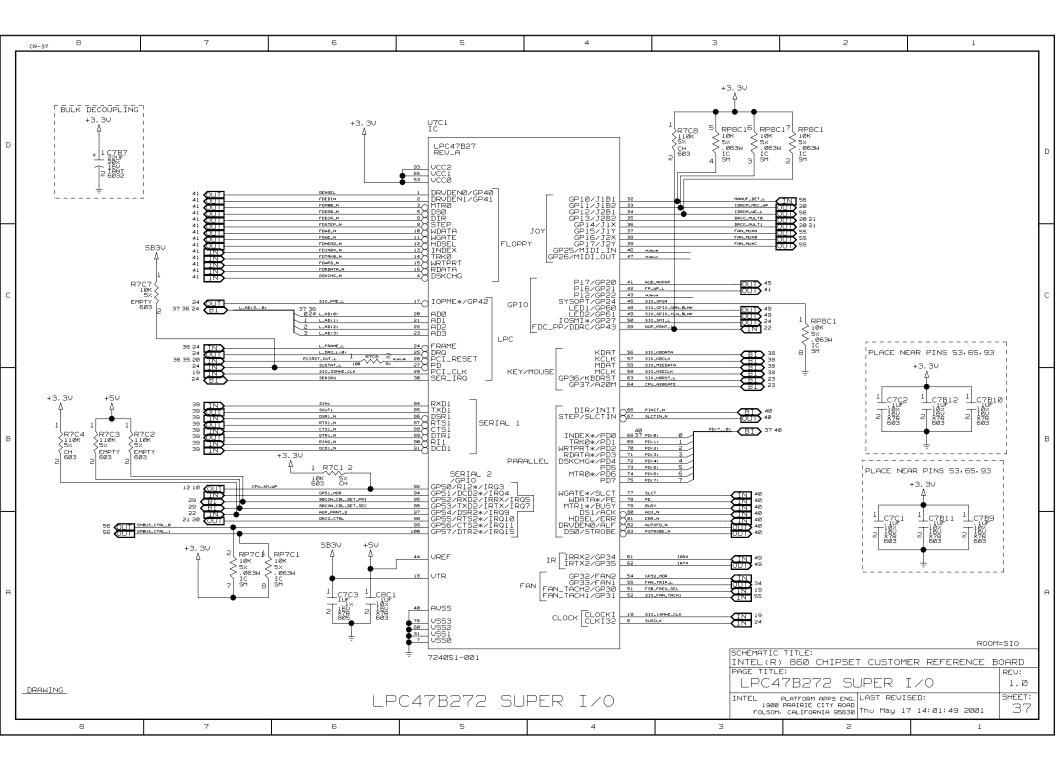

|   | 9.4                                     |             | C Design Recommendations                                   |     |

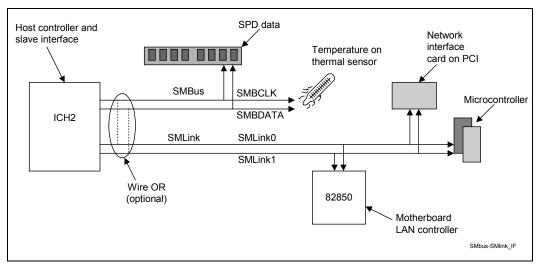

|   | 9.5                                     |             | /SMLink Interface                                          |     |

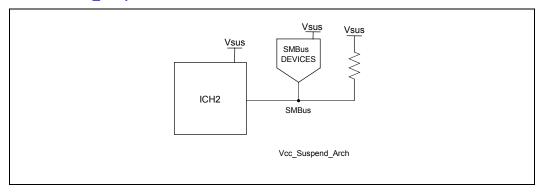

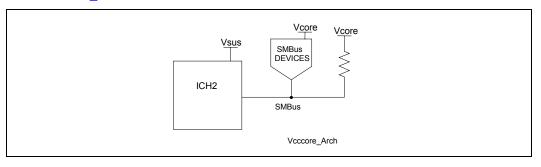

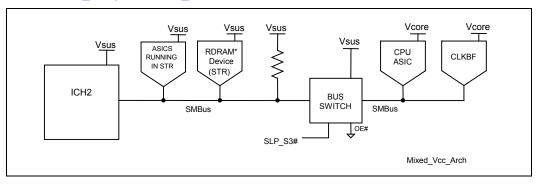

|   |                                         | 9.5.1       | SMBus Architecture and Design Considerations               | 164 |

|   |                                         |             | 9.5.1.1 SMBus Design Considerations                        |     |

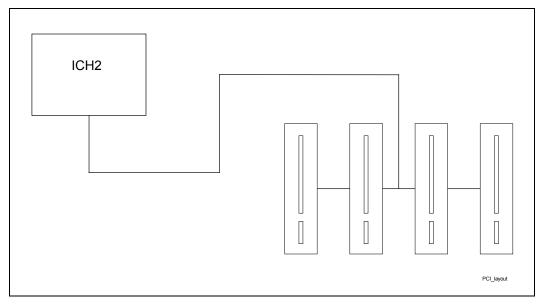

|   | 9.6                                     | PCI         |                                                            | 167 |

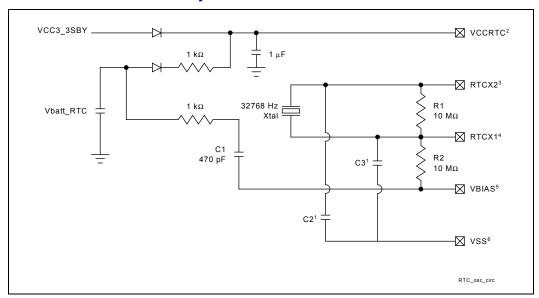

|   | 9.7                                     | RTC         |                                                            | 168 |

|   |                                         | 9.7.1       | RTC Crystal                                                | 168 |

|   |                                         | 9.7.2       | External Capacitors                                        |     |

|   |                                         | 9.7.3       | RTC Layout Considerations                                  |     |

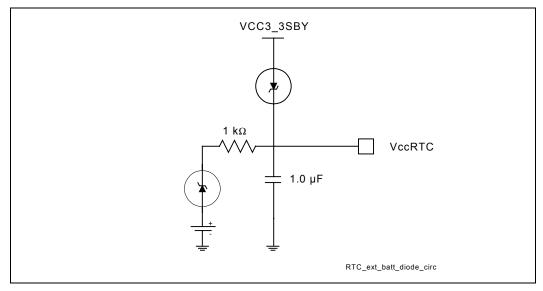

|   |                                         | 9.7.4       | RTC External Battery Connection                            | 169 |

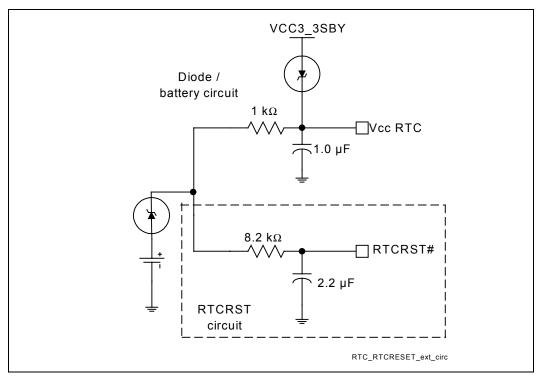

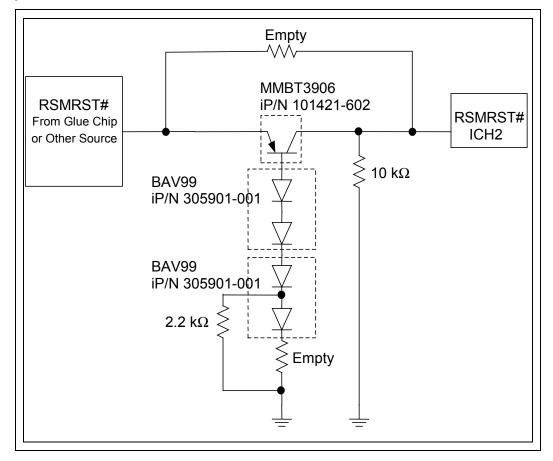

|   |                                         | 9.7.5       | RTC External RTCRST Circuit                                |     |

|   |                                         | 9.7.6       | RTC Routing Guidelines                                     | 172 |

|   |                                         | 9.7.7       | VBIAS DC Voltage and Noise Measurements                    | 172 |

|   |                                         | 9.7.8       | Power-Well Isolation Control                               |     |

|   |                                         | 9.8.9       | Power Supply PS ON Considerations                          |     |

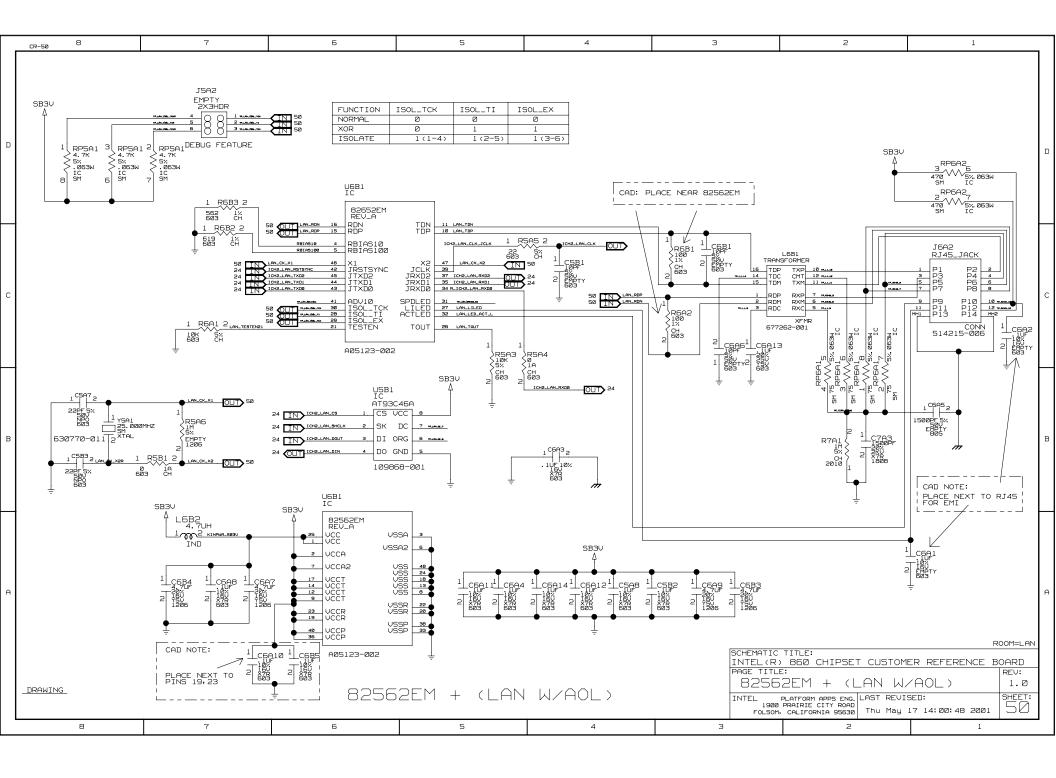

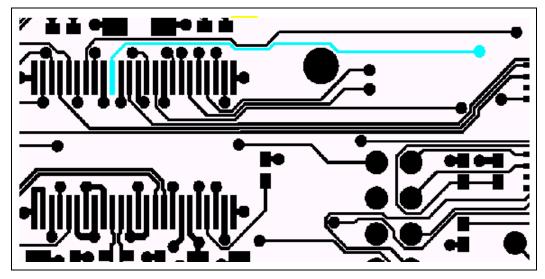

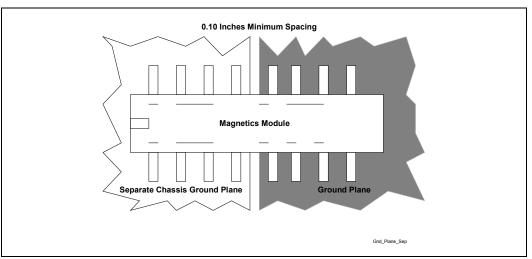

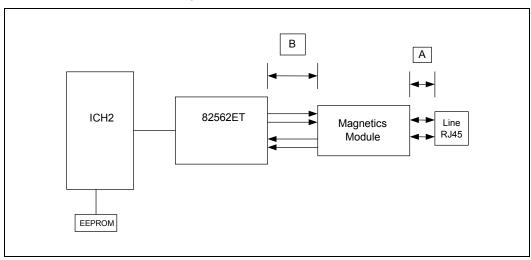

|   | 9.8                                     | LAN La      | yout Guidelines                                            |     |

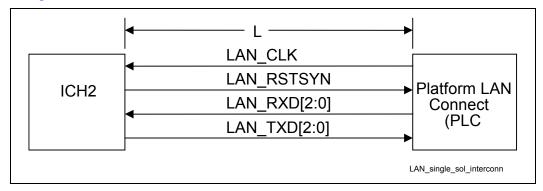

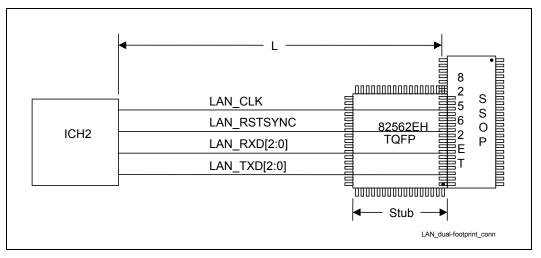

|   |                                         | 9.8.1       | Intel® ICH2—LAN Interconnect Guidelines                    |     |

|   |                                         | 0.0.1       | 9.8.1.1 Bus Topologies                                     |     |

|   |                                         |             | 9.8.1.2 Point-to-Point Interconnect                        |     |

|   |                                         |             | 9.8.1.3 Signal Routing and Layout                          |     |

|   |                                         |             | 9.8.1.4 Crosstalk Consideration                            |     |

|   |                                         |             | 9.8.1.5 Impedances                                         |     |

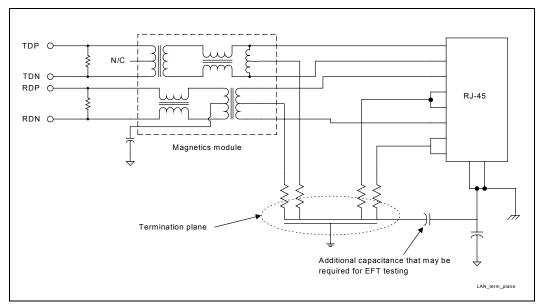

|   |                                         |             | 9.8.1.6 Line Termination                                   |     |

|   |                                         | 9.8.2       | General LAN Routing Guidelines and Considerations          |     |

|   |                                         |             | 9.8.2.1 General Trace Routing Considerations               |     |

|   |                                         |             | 9.8.2.2 Trace Geometry and Length                          |     |

|   |                                         |             | 9.8.2.3 Power and Ground Connections                       |     |

|   |                                         |             | 9.8.2.4 Common Physical Layout Issues                      |     |

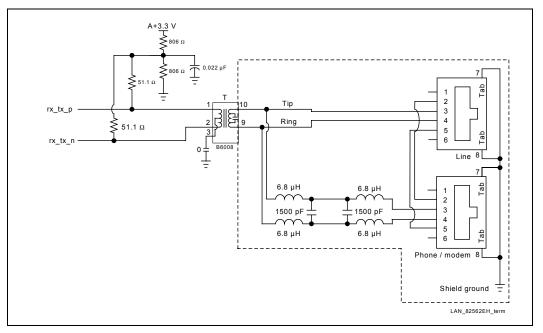

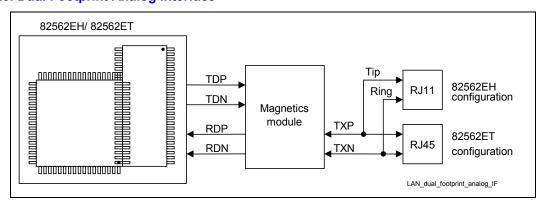

|   |                                         | 9.8.3       | Intel® 82562EH Home/PNA Guidelines                         | 184 |

|   |                                         |             | 9.8.3.1 Power and Ground Connections                       |     |

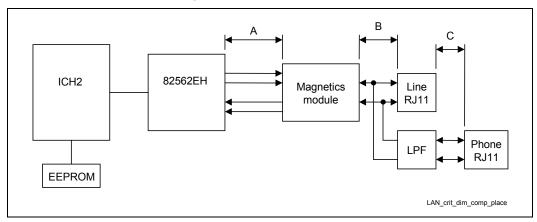

|   |                                         |             | 9.8.3.2 Guidelines for Intel® 82562EH Component Placement  | 184 |

|   |                                         |             | 9.8.3.3 Crystals and Oscillators                           |     |

|   |                                         |             | 9.8.3.4 Phoneline HPNA Termination                         |     |

|   |                                         |             | 9.8.3.5 Critical Dimensions                                |     |

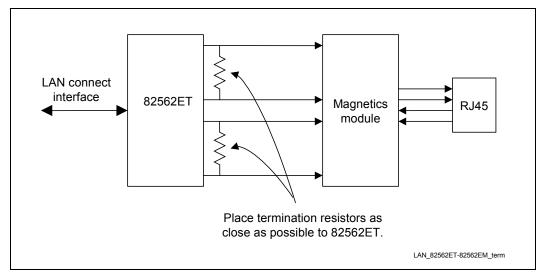

|   |                                         | 9.8.4       | Intel® 82562ET/EM Guidelines                               | 187 |

|   |                                         |             | 9.8.4.1 Guidelines for Intel® 82562ET/EM Component         |     |

|   |                                         |             | Placement                                                  | 187 |

|   |                                         |             | 9.8.4.2 Crystals and Oscillators                           |     |

|    |                      | 9.8.4.3 Intel <sup>®</sup> 82562ET/EM Termination Resistors<br>9.8.4.4 Critical Dimensions |     |

|----|----------------------|--------------------------------------------------------------------------------------------|-----|

|    |                      | 9.8.4.5 Reducing Circuit Inductance                                                        |     |

|    |                      | 9.8.4.6 Terminating Unused Connections                                                     |     |

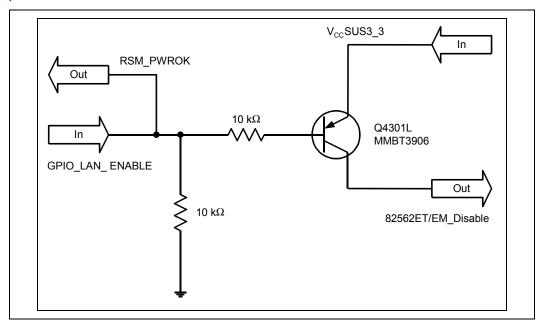

|    |                      | 9.8.5 Intel® 82562 ET/EM Disable Guidelines                                                | 191 |

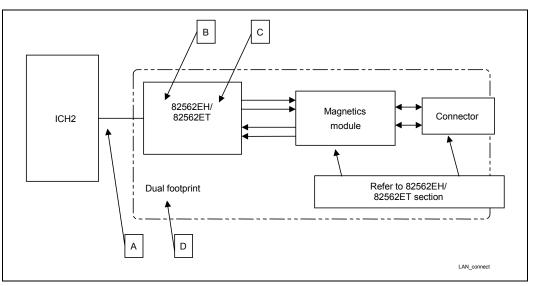

|    |                      | 9.8.6 Intel® 82562ET / Intel® 82562EH Dual Footprint Guidelines                            | 192 |

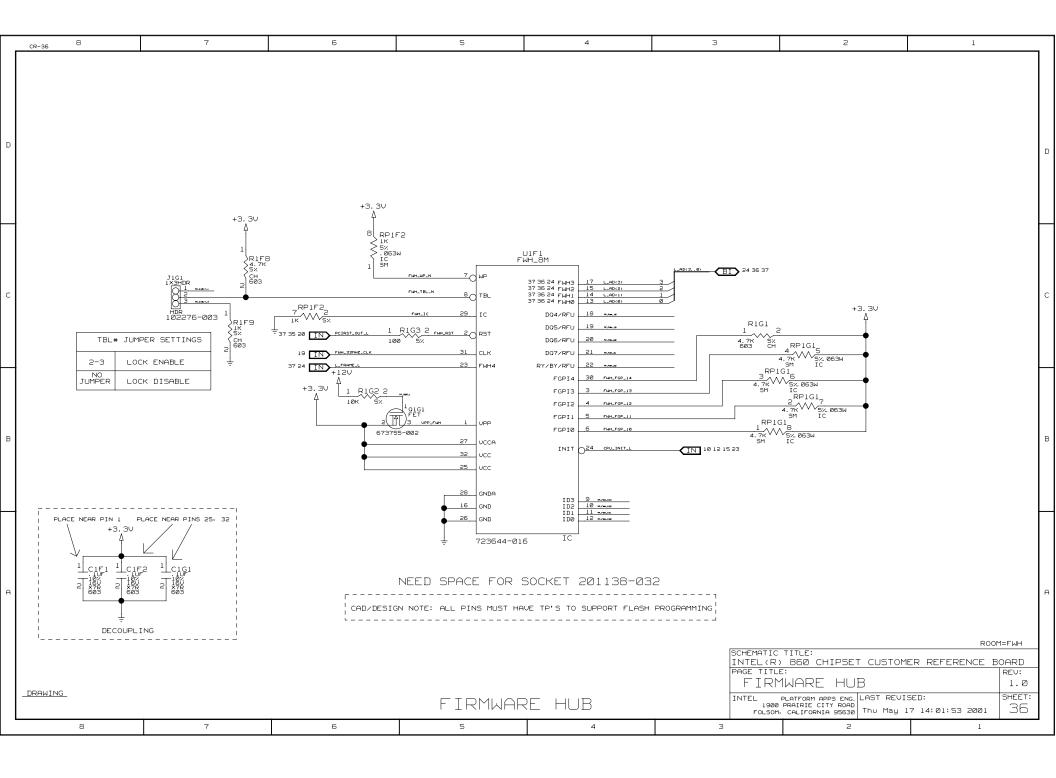

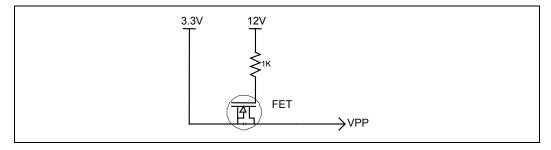

|    | 9.9                  | FWH Guidelines                                                                             | 193 |

|    |                      | 9.9.1 FWH Decoupling                                                                       | 194 |

|    |                      | 9.9.2 In Circuit FWH Programming                                                           |     |

|    |                      | 9.9.3 FWH Vpp Design Guidelines                                                            |     |

|    | 9.10                 | Intel® ICH2 Decoupling Recommendations                                                     |     |

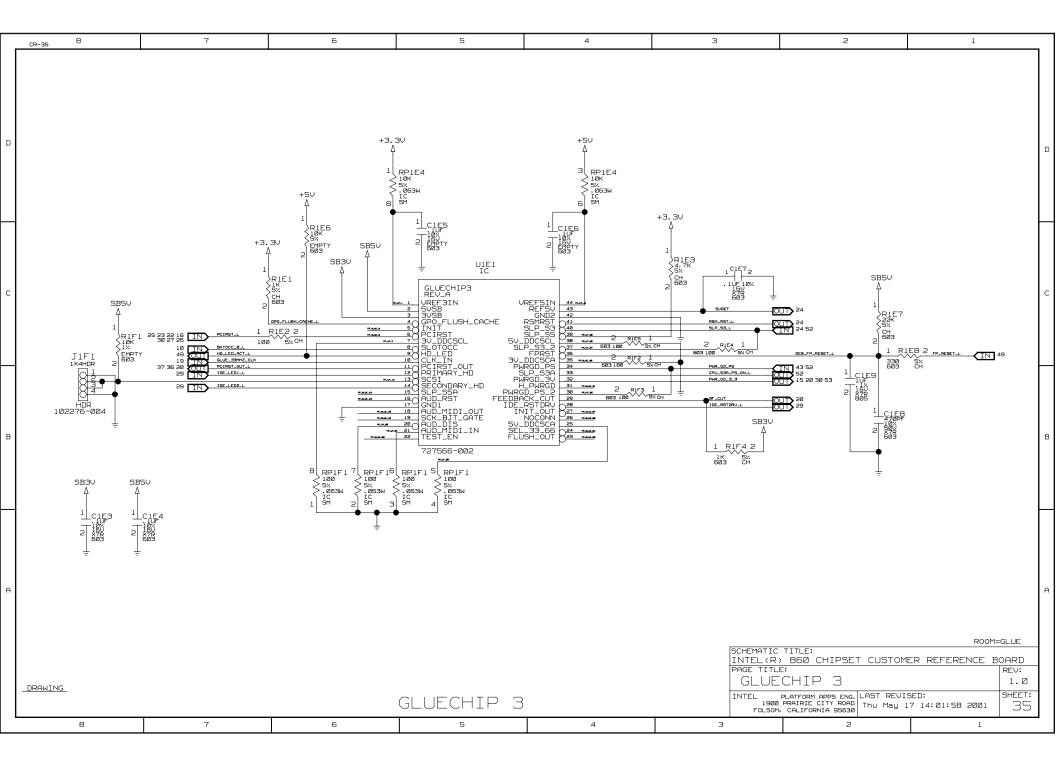

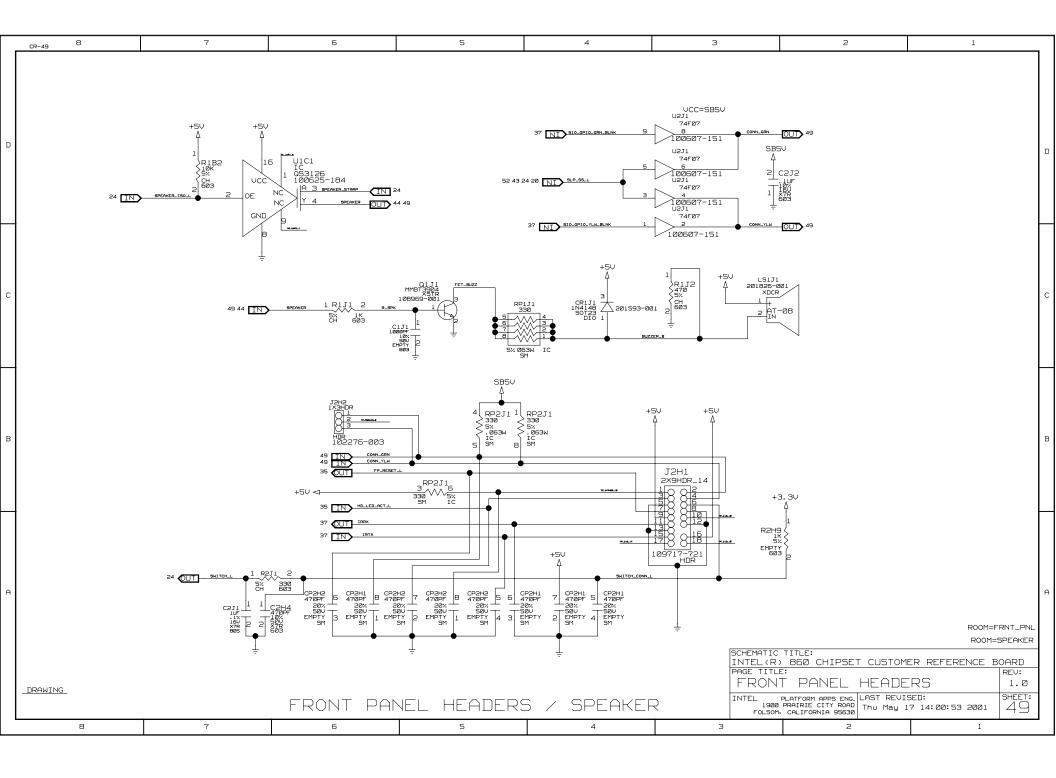

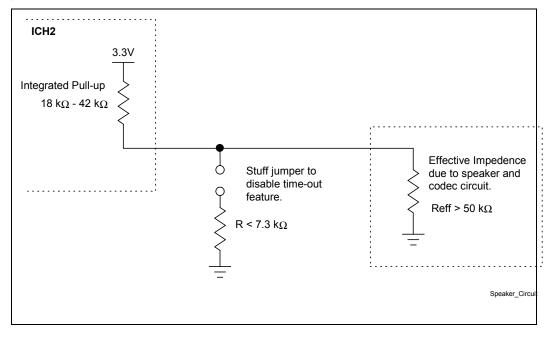

|    | 9.11                 | Glue Chip 3 (Intel <sup>®</sup> ICH2 Glue Chip)                                            |     |

|    | 9.12                 | SPKR Pin Consideration                                                                     |     |

|    | 9.13                 | 1.8 V and 3.3 V Power Sequence Requirement                                                 | 198 |

|    | 9.14                 | ICH2 V5REF and VCC3_3 Sequencing Requirement                                               | 199 |

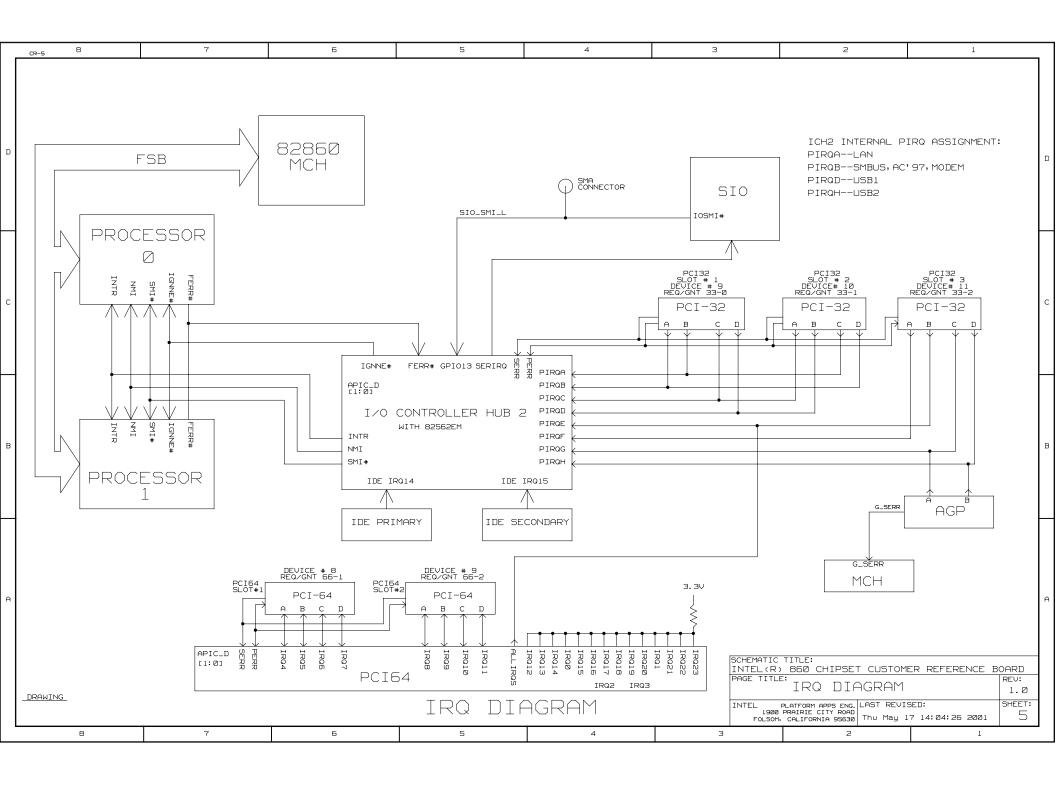

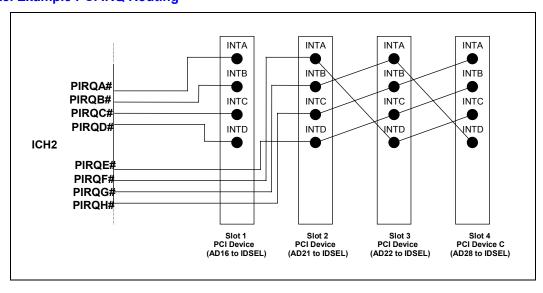

|    | 9.15                 | PIRQ Routing                                                                               | 200 |

| 10 | EMID                 | esign Guidelines                                                                           | 203 |

| 10 |                      |                                                                                            |     |

|    | 10.1                 | Terminology                                                                                |     |

|    | 10.2                 | Basic EMI Theory                                                                           |     |

|    | 10.3                 | EMI Regulations and Certifications                                                         |     |

|    | 10.4                 | EMI Design Considerations                                                                  |     |

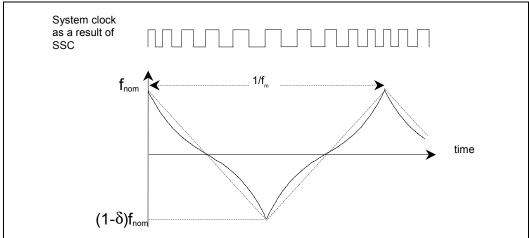

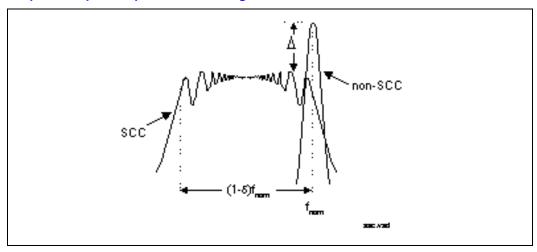

|    |                      | 10.4.1 Spread Spectrum Clocking (SSC)                                                      |     |

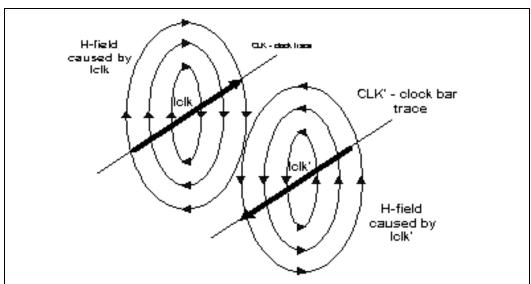

|    |                      | 10.4.2 Differential Clocking                                                               |     |

|    |                      | 10.4.3 PCI Bus Clock Control                                                               |     |

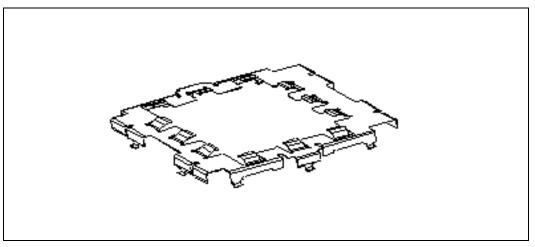

|    |                      | 10.4.5 Faraday Cages                                                                       |     |

|    |                      | 10.4.6 EMI Test Capabilities                                                               |     |

| 11 | Mecha                | anical and EMI Design Considerations                                                       |     |

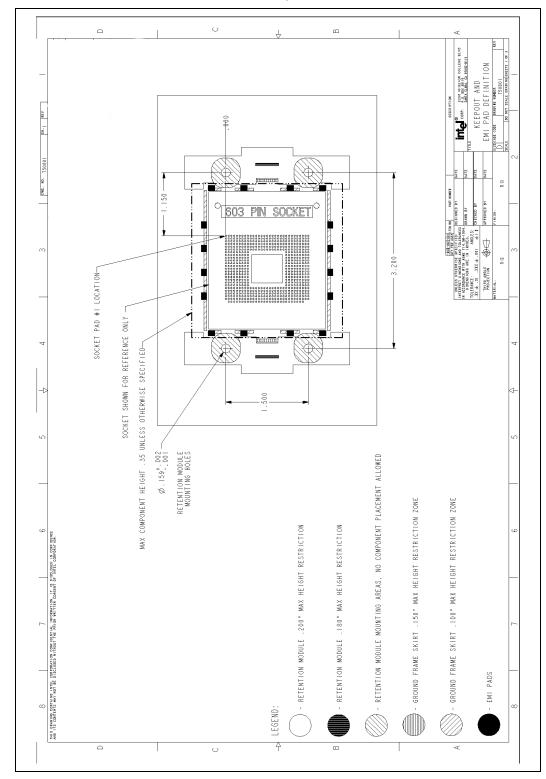

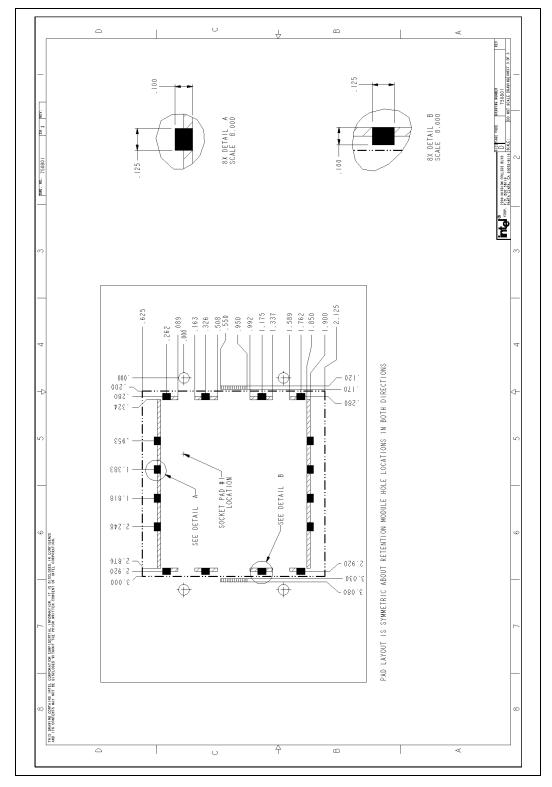

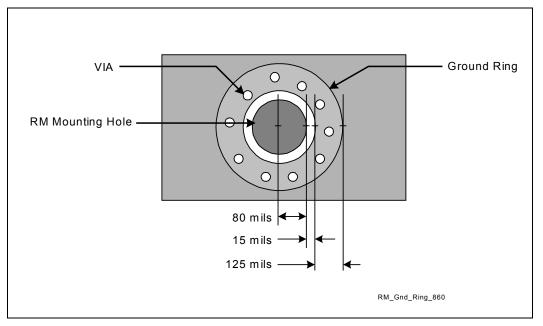

|    | 11.1                 | Retention Mechanism Placement and Keepouts                                                 |     |

|    | 11.1                 | Electromagnetic Interference Considerations                                                |     |

|    |                      | -                                                                                          |     |

| 12 | Intel <sup>®</sup> : | Xeon™ Processor Power Distribution Guidelines                                              | 217 |

|    | 12.1                 | Introduction                                                                               | 217 |

|    | 12.2                 | Terminology                                                                                | 217 |

|    | 12.3                 | Power Delivery Overview                                                                    | 218 |

|    | 12.4                 | Processor Power Delivery Ingredients                                                       |     |

|    | 12.5                 | System Design                                                                              |     |

|    |                      | 12.5.1 Multiple Voltages                                                                   |     |

|    |                      | 12.5.2 Voltage Sequencing                                                                  |     |

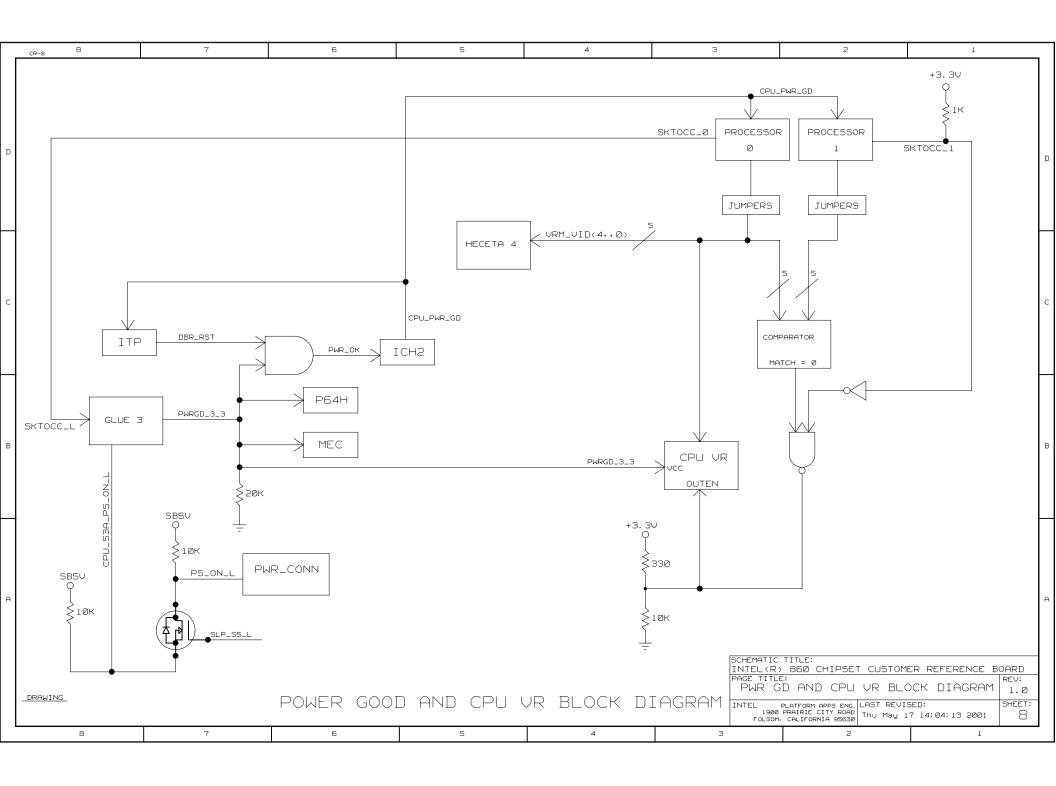

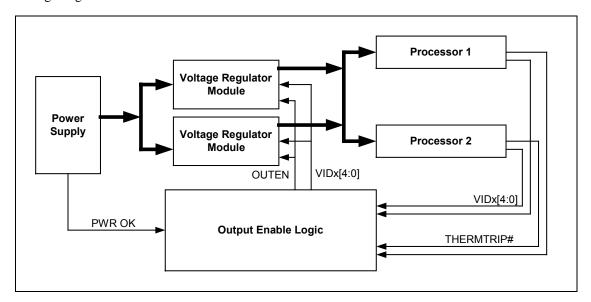

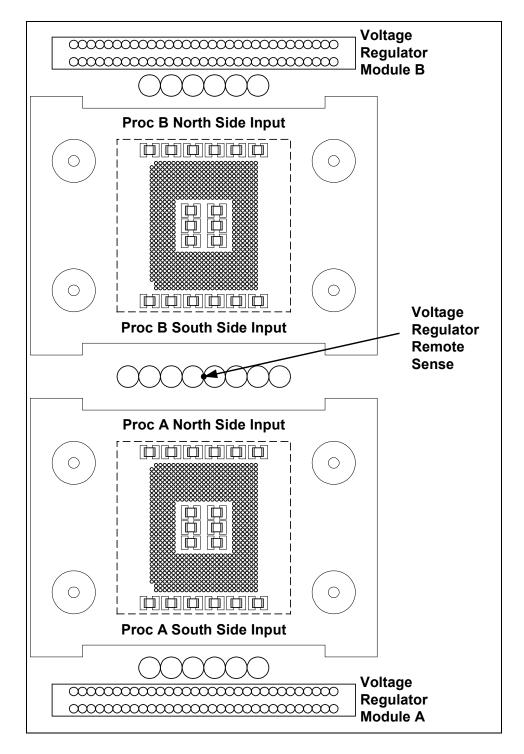

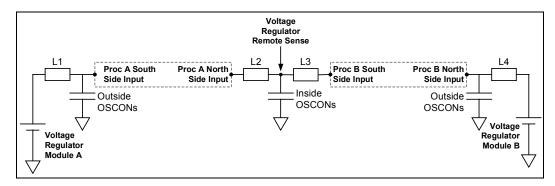

|    |                      | 12.5.3 Block Diagrams with Voltage Regulator Modules                                       |     |

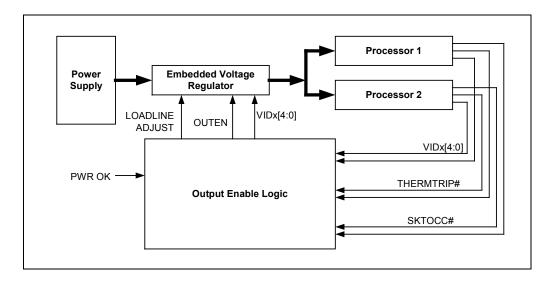

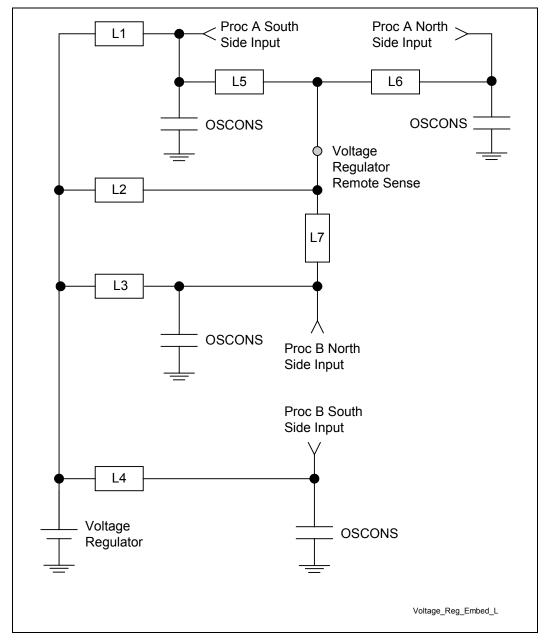

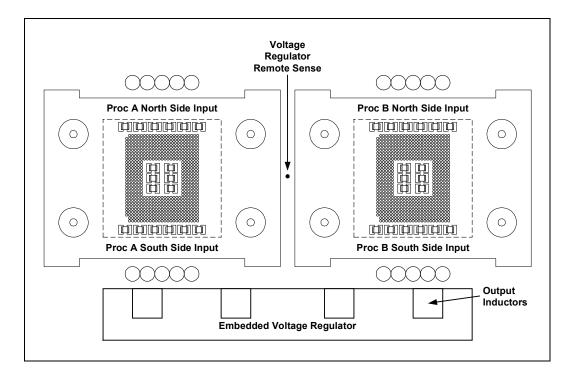

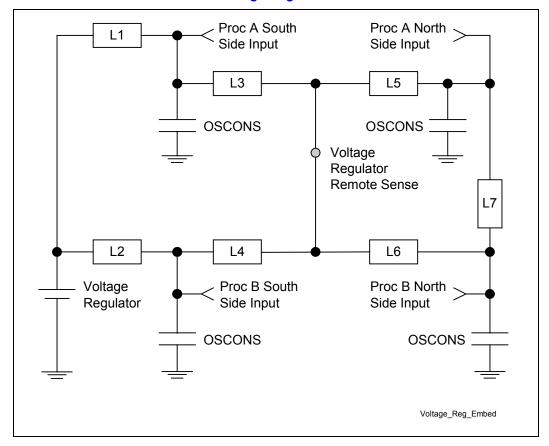

|    |                      | 12.5.4 Block Diagram with Embedded Voltage Regulator                                       |     |

|    | 12.6                 | Processor Load                                                                             |     |

|    |                      | 12.6.1 Processor Current Requirements                                                      |     |

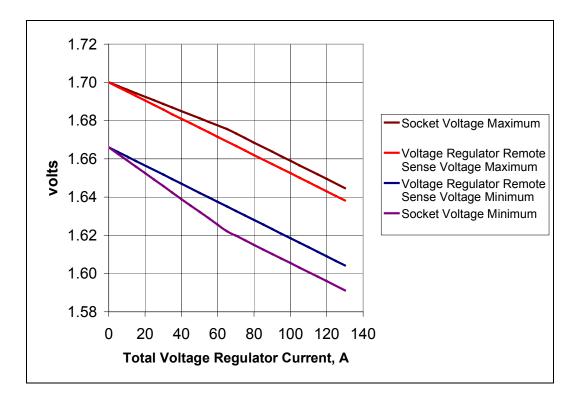

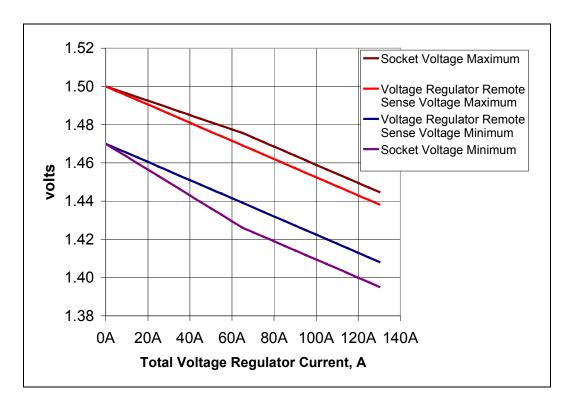

|    |                      | 12.6.2 Processor Voltage Tolerance                                                         |     |

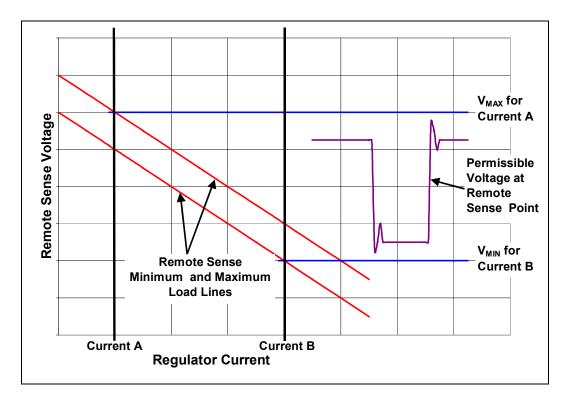

|    |                      | 12.6.3 Voltage Regulation Load Lines                                                       |     |

|    | 12.7                 | Voltage RegulatorVoltage Regulation Load Line Equations                                    |     |

|    | 12.7                 | Voltage Regulator Design                                                                   |     |

|    | 12.0                 | voltage i regulator Design                                                                 | 234 |

|    | 12.9   | Voltage Regulator System Matching                           | 234                                   |

|----|--------|-------------------------------------------------------------|---------------------------------------|

|    |        | 12.9.1 Voltage Regulator Output                             | 234                                   |

|    | 12.10  | Voltage Regulator Input                                     | 234                                   |

|    | 12.11  | Voltage Regulator Cooling                                   | 235                                   |

|    | 12.12  |                                                             |                                       |

|    | 12.13  | Voltage Regulator Module ISHARE Connection                  |                                       |

|    | 12.14  | Voltage Regulator Module OUTEN Connection                   |                                       |

|    | 12.15  | Power Planes                                                |                                       |

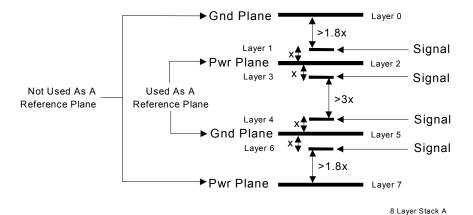

|    | 12.13  | 12.15.1 Layer Stack-Up                                      |                                       |

|    |        | 12.15.2 Sheet Inductance/Resistance and Emission Effects of | 230                                   |

|    |        | Power Plane                                                 | 237                                   |

|    | 12.16  | Decoupling Capacitors                                       |                                       |

|    | 12.10  | 12.16.1 Decoupling Technology and Transient Response        |                                       |

|    |        | 12.16.2 Location of High-Frequency Decoupling               |                                       |

|    |        | 12.16.3 Location of Bulk Decoupling                         |                                       |

|    |        | 12.16.4 Decoupling Recommendation                           |                                       |

|    |        | 12.16.5 Component Placement and Modeling                    |                                       |

|    |        | 12.16.6 Component Models                                    |                                       |

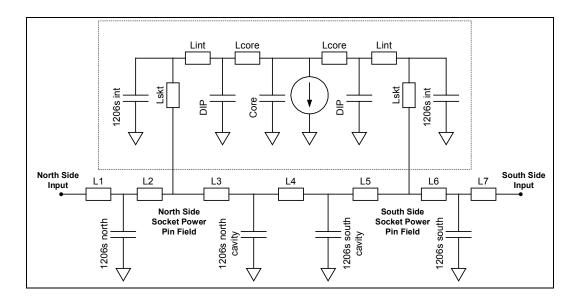

|    |        | 12.16.7 Processor Socket-Package Lump Model                 |                                       |

|    | 12.17  | Validation Testing                                          | 252                                   |

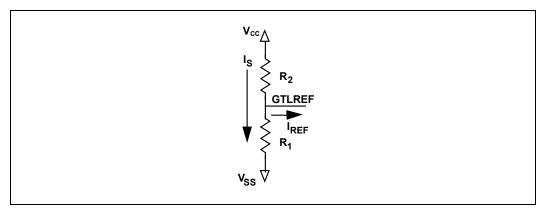

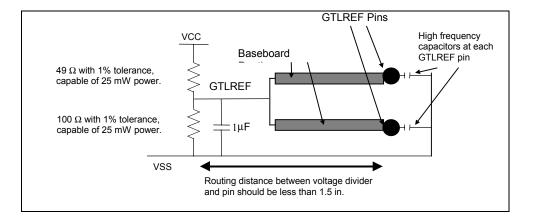

|    |        | 12.17.1 Generating and Distributing GTLREF[3:0]             |                                       |

|    |        | 12.17.2 GTLREF [3:0]                                        |                                       |

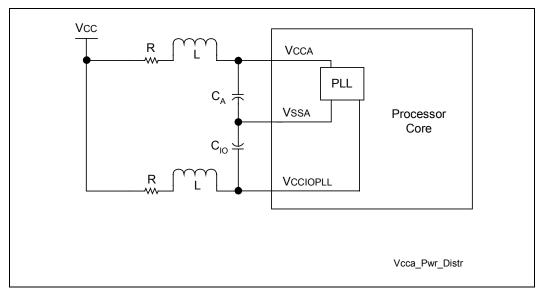

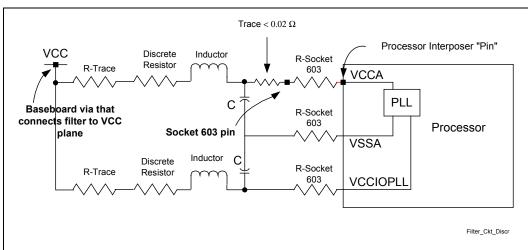

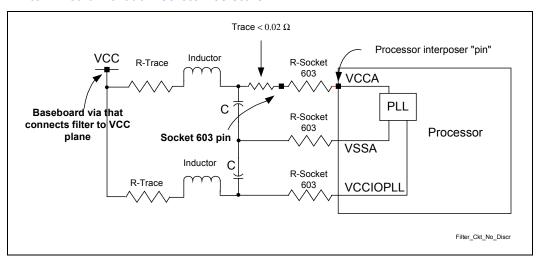

|    |        | 12.17.3 Filter Specifications for VCCA, VCCIOPLL, and VSSA  | 255                                   |

| 13 | Chipse | et Power Distribution Guidelines                            | 261                                   |

|    | 13.1   | Definitions                                                 |                                       |

|    | 13.2   | Power Management                                            |                                       |

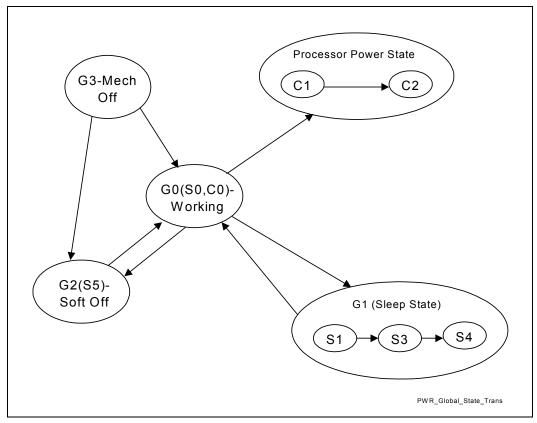

|    | 10.2   | 13.2.1 ACPI Hardware Model                                  |                                       |

|    |        | 13.2.2 Thermal Design Power                                 |                                       |

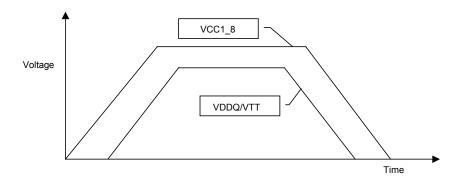

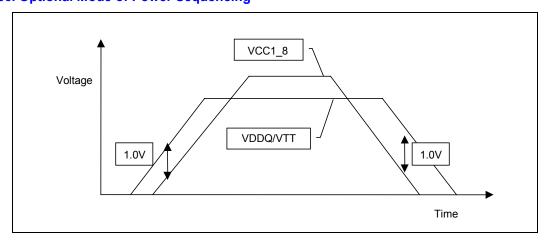

|    | 13.3   | Intel® 860 Chipset MCH Power Sequencing Requirement         |                                       |

|    | 13.4   | Vterm/Vdd Power Sequencing Requirement                      |                                       |

|    | 13.5   | ICH2 5VREF and VCC3.3 Sequencing Requirement                |                                       |

|    |        | ·                                                           |                                       |

| 14 | Metho  | dology for Determining Topology and Routing Guidelines      |                                       |

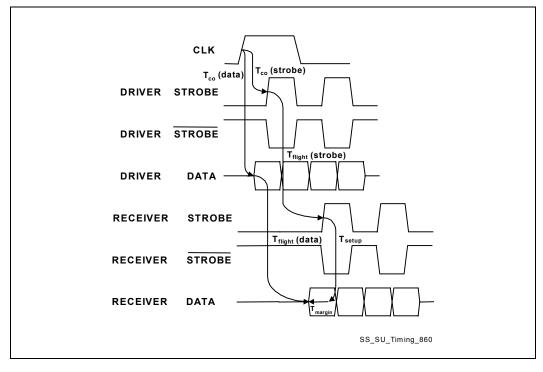

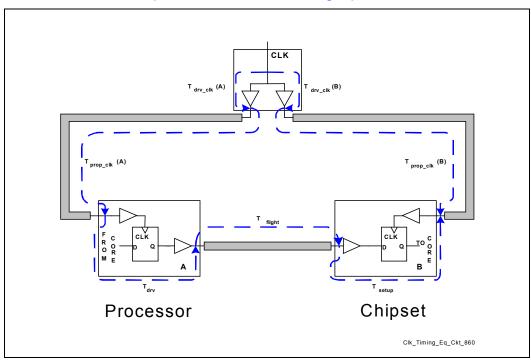

|    | 14.1   | Timing Methodology                                          |                                       |

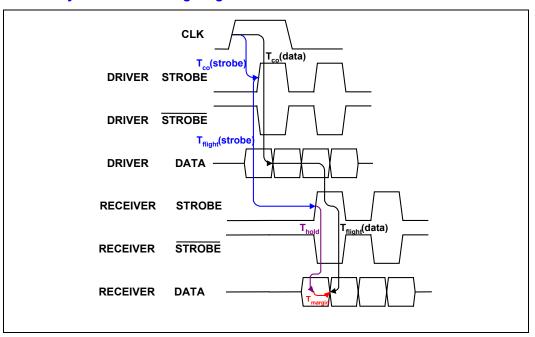

|    |        | 14.1.1 Source Synchronous                                   |                                       |

|    |        | 14.1.1.1 Setup Time                                         |                                       |

|    |        | 14.1.1.2 Hold Time                                          |                                       |

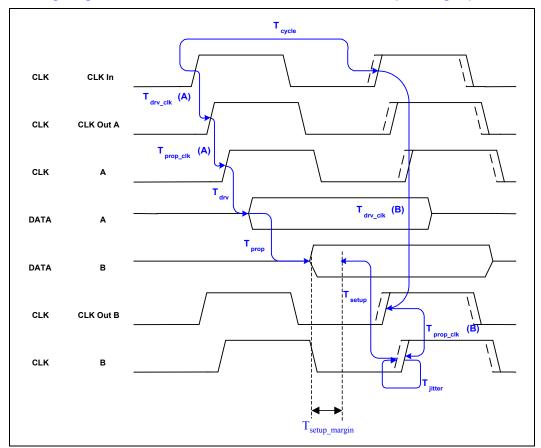

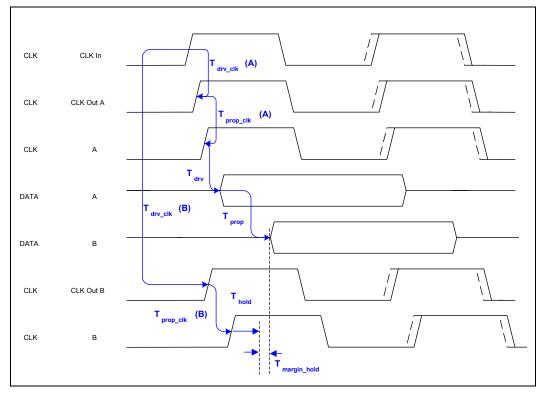

|    |        | 14.1.2 Common clock                                         |                                       |

|    |        | 14.1.2.1 Setup Margin                                       |                                       |

|    |        | 14.1.2.2 Hold Margin                                        |                                       |

|    | 440    | 14.1.3 Timing Spreadsheet                                   |                                       |

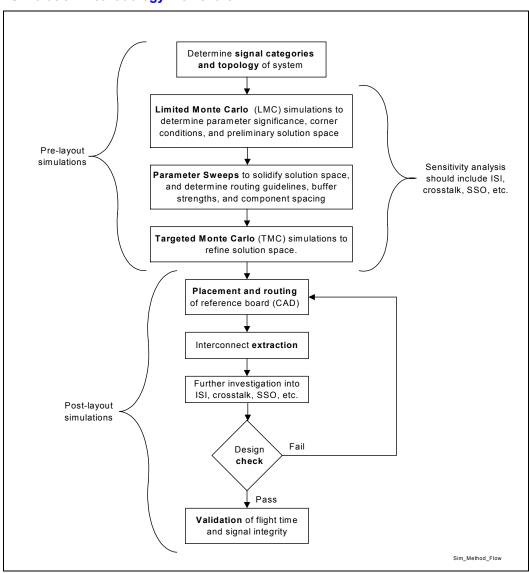

|    | 14.2   | Simulation Methodology                                      |                                       |

|    |        | 14.2.1 Design Optimization                                  |                                       |

|    |        | 14.2.2 Signal Categories and Topology Options               |                                       |

|    |        | 14.2.3 Sensitivity Analysis                                 |                                       |

|    |        | 14.2.4 Signal Quality Metrics                               |                                       |

|    |        | 14.2.4.1 Noise Margin                                       |                                       |

|    |        | 14.2.5 Timing Metrics                                       |                                       |

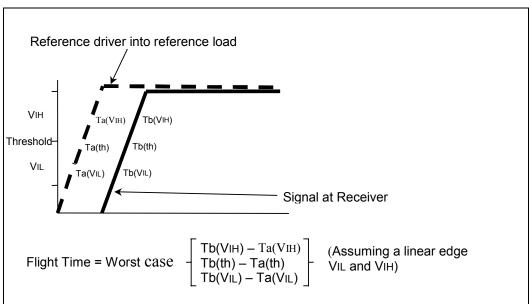

|    |        | 14.2.5.1 Setup Flight Time                                  |                                       |

|    |        |                                                             | · · · · · · · · · · · · · · · · · · · |

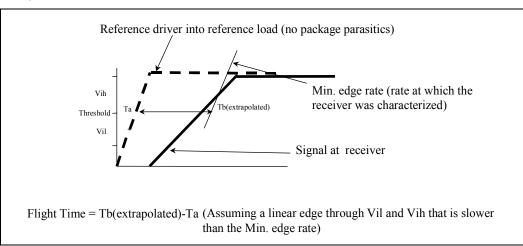

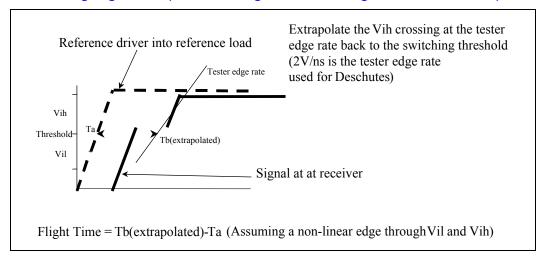

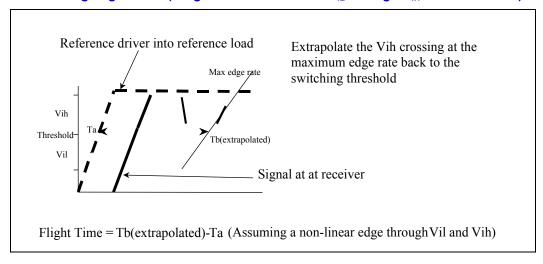

|     |        |                    | 14.2.5.2  | Calculating Flight Time for Signals with Corrupt Signal   |     |

|-----|--------|--------------------|-----------|-----------------------------------------------------------|-----|

|     |        |                    | 14.2.5.3  | QualityIncorporating Package Effects into the Flight Time |     |

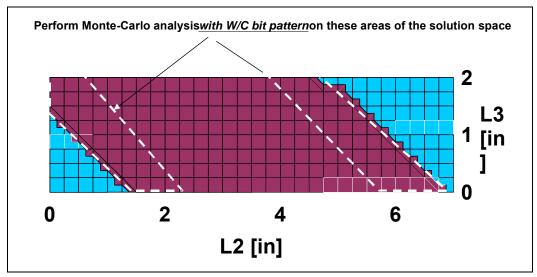

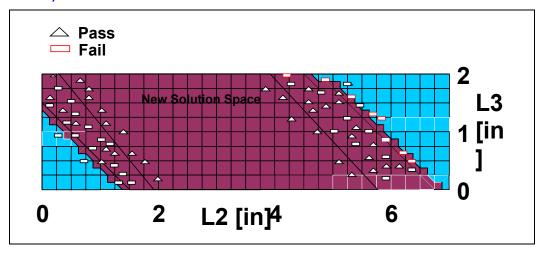

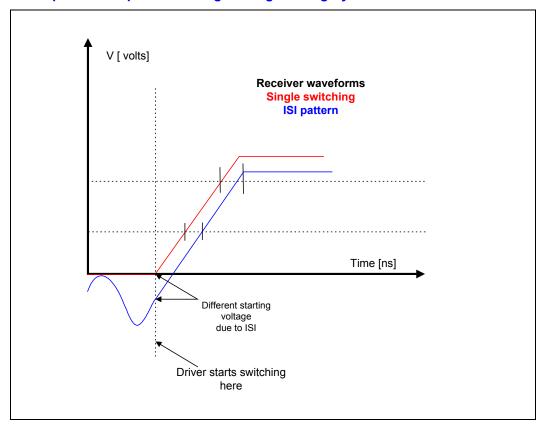

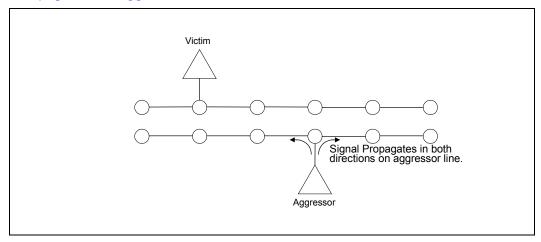

|     |        | 14.2.6             |           | Sweeps and Monte Carlo Analysis                           |     |

|     |        |                    |           | Parameter Sweeps                                          |     |

|     |        |                    |           | Final Solution Space                                      |     |

| 15  | Syster | m Theory.          |           |                                                           | 283 |

| . • | 15.1   | •                  |           |                                                           |     |

|     | 15.2   |                    |           | rence                                                     |     |

|     | 15.2   | •                  |           | TO T                  |     |

| 16  |        |                    |           | nes                                                       |     |

| 47  |        |                    | _         |                                                           |     |

| 17  |        |                    |           |                                                           | 291 |

|     | 17.1   |                    |           | ssor and Intel Xeon Processor with 512 KB L2 Cache        | 201 |

|     | 17.2   |                    |           | ct Rambus* Clock Generator Checklist                      |     |

|     | 17.2   |                    |           | ICH Checklist                                             |     |

|     | 17.3   |                    | •         | IOTI OTIEGNIST                                            |     |

|     | 17.4   |                    |           | st                                                        |     |

|     | _      |                    |           | wn/ Intel <sup>®</sup> MRH-R Checklist                    |     |

|     | 17.6   |                    |           | MIV INTEL MIRH-R CHECKIIST                                |     |

|     | 17.7   | 17.7.1             |           | ace                                                       |     |

|     |        | 17.7.1             |           | ace                                                       |     |

|     |        | 17.7.2             |           | ace                                                       |     |

|     |        | 17.7.4             |           | Interface                                                 |     |

|     |        | 17.7.5             |           | Interface                                                 |     |

|     |        | 17.7.6             |           | nterface                                                  |     |

|     |        | 17.7.7             |           |                                                           |     |

|     |        | 17.7.8             |           |                                                           |     |

|     |        | 17.7.9             |           | nagement                                                  |     |

|     |        | 17.7.10            |           | Signals                                                   |     |

|     |        | 17.7.11            | •         | anagement                                                 |     |

|     |        | 17.7.12            |           |                                                           |     |

|     |        | 17.7.13            |           | O'con als                                                 |     |

|     |        | 17.7.14            |           | eous Signals                                              |     |

|     |        | 17.7.15<br>17.7.16 |           | klist                                                     |     |

| 40  | Lavav  |                    |           |                                                           |     |

| 18  | •      |                    |           | Du-                                                       |     |

|     | 18.1   |                    | -         | em Bus                                                    |     |

|     |        | 18.1.1<br>18.1.2   |           | gnals                                                     |     |

|     |        | 18.1.3             |           | nous GTL+ and Other Signals                               |     |

|     |        | 18.1.4             |           | Clocking Decoupling                                       |     |

|     |        | 18.1.5             |           | ecoupling                                                 |     |

|     |        | 18.1.6             |           | REF, HDVREF [3:0], HAVREF [1:0], and CCVREF)              |     |

|     | 18.2   |                    |           | uidelines                                                 |     |

|     | 10.2   | 18.2.1             | -         | als                                                       |     |

|     |        | 18.2.2             |           | olation:                                                  |     |

|     |        | 18 2 3             | Vterm Lav |                                                           | 333 |

|             |         | 18.2.4 Direct Rambus* Clock Generation (DRCG* Device) |     |

|-------------|---------|-------------------------------------------------------|-----|

|             |         | Recommendations                                       | 334 |

|             |         | 18.2.5 DRCG* Device Layout- Clean Power Supply        | 335 |

|             |         | 18.2.6 DRCG - CTM/CTM# Output Network Layout          | 336 |

|             |         | 18.2.7 RAMREF Routing                                 | 336 |

|             | 18.3    | AGP Guidelines                                        |     |

|             |         | 18.3.1 All 1X Signals                                 | 337 |

|             |         | 18.3.2 2X/4X Signals                                  |     |

|             |         | 18.3.3 MCH AGP Decoupling                             |     |

|             |         | 18.3.4 AGP Connector Decoupling                       |     |

|             | 18.4    | 8-Bit Hub Interface                                   | 341 |

|             |         | 18.4.1 Hub Decoupling                                 |     |

|             | 18.5    | 16-Bit Hub Interface                                  | 342 |

|             |         | 18.5.1 Hub Decoupling                                 | 342 |

|             | 18.6    | IDE Interface                                         | 343 |

|             | 18.7    | AC'97                                                 | 343 |

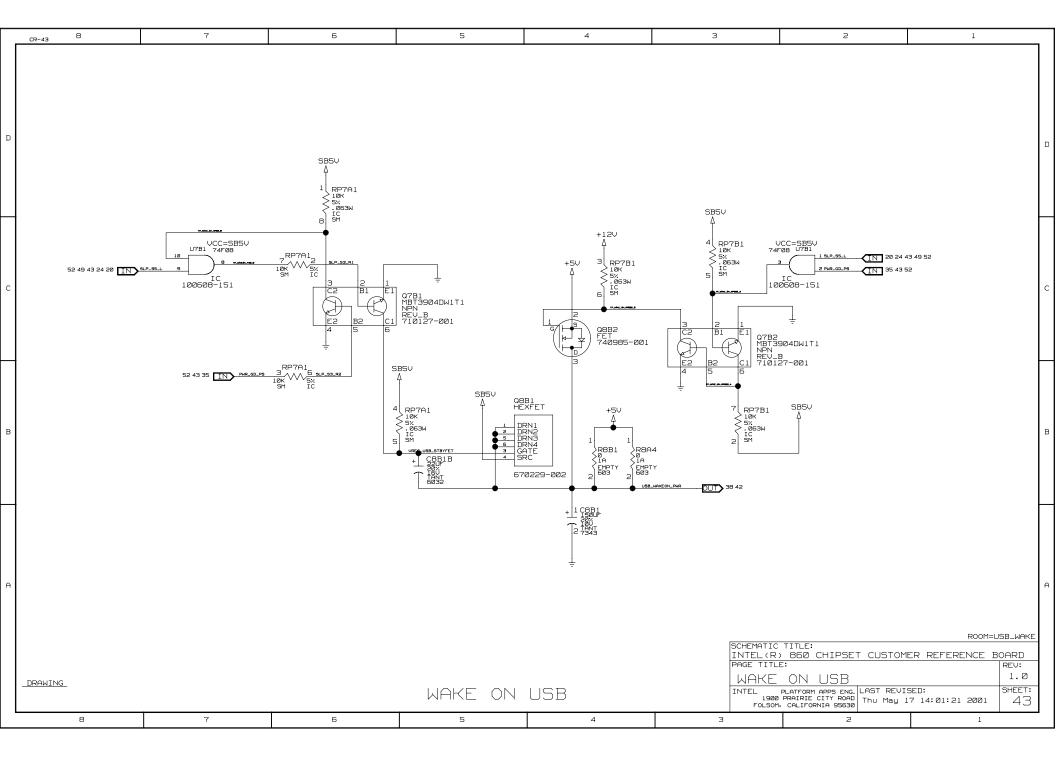

|             | 18.8    | USB                                                   | 343 |

|             | 18.9    | Intel® ICH2 Decoupling                                |     |

|             | 18.10   | RTC                                                   |     |

|             | 18.11   | LAN Connect I/F                                       |     |

|             | 18.12   | Miscellaneous Routing Guidelines                      |     |

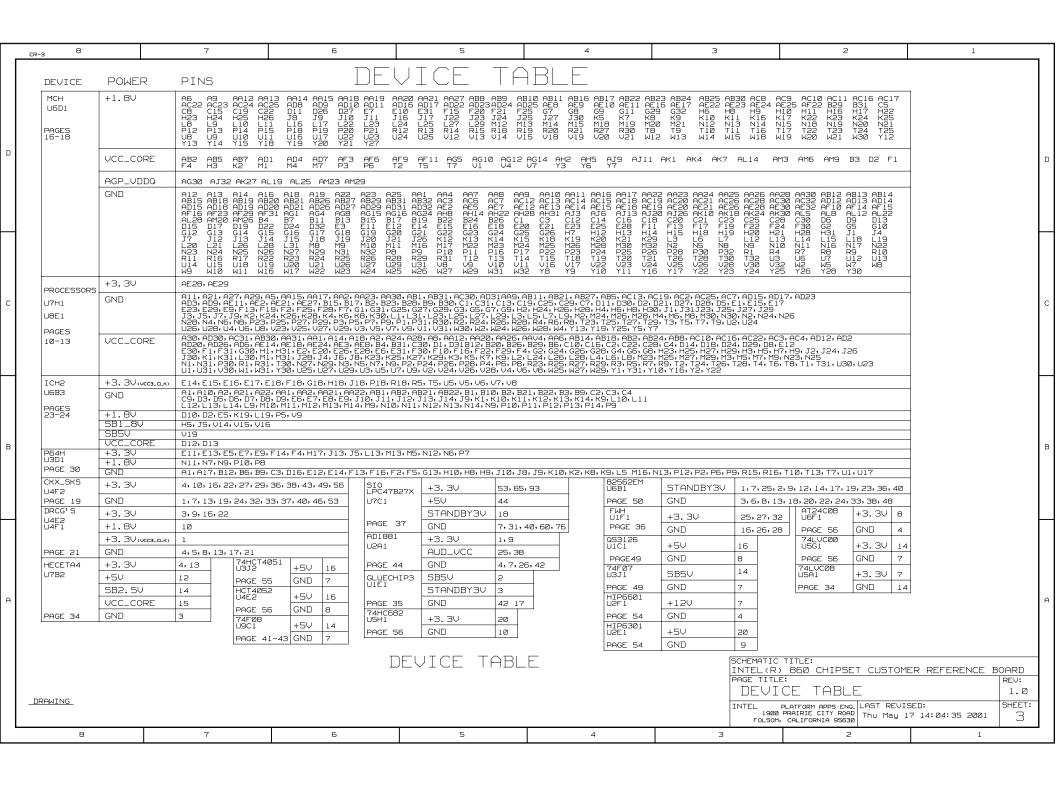

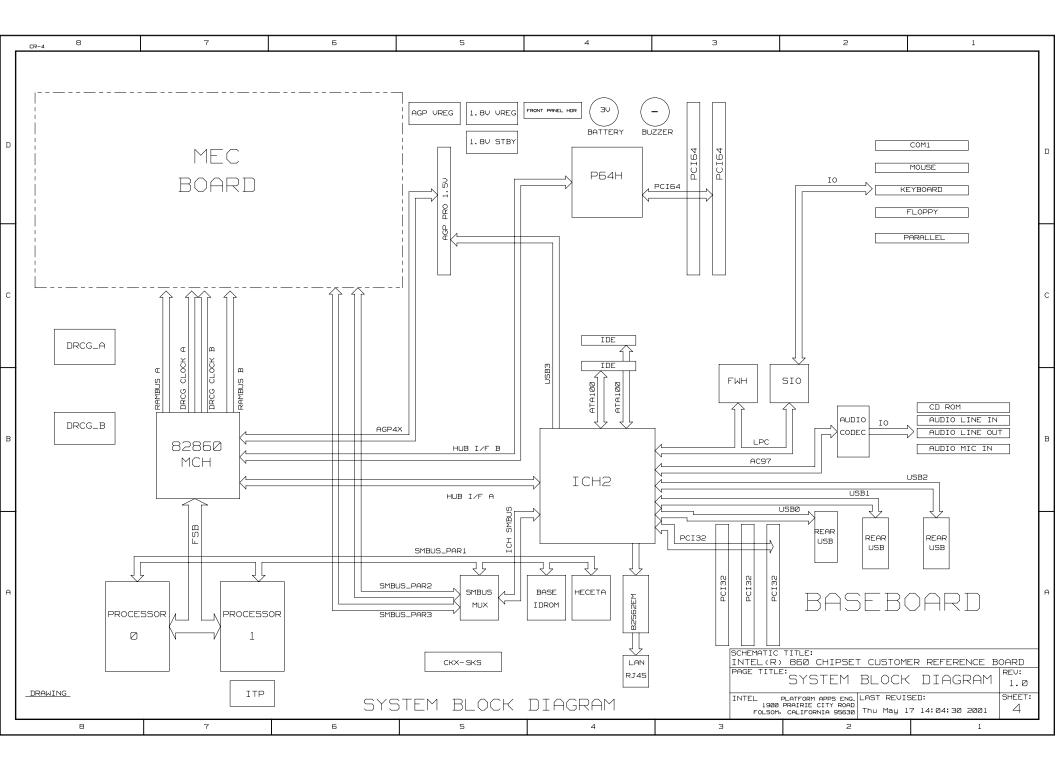

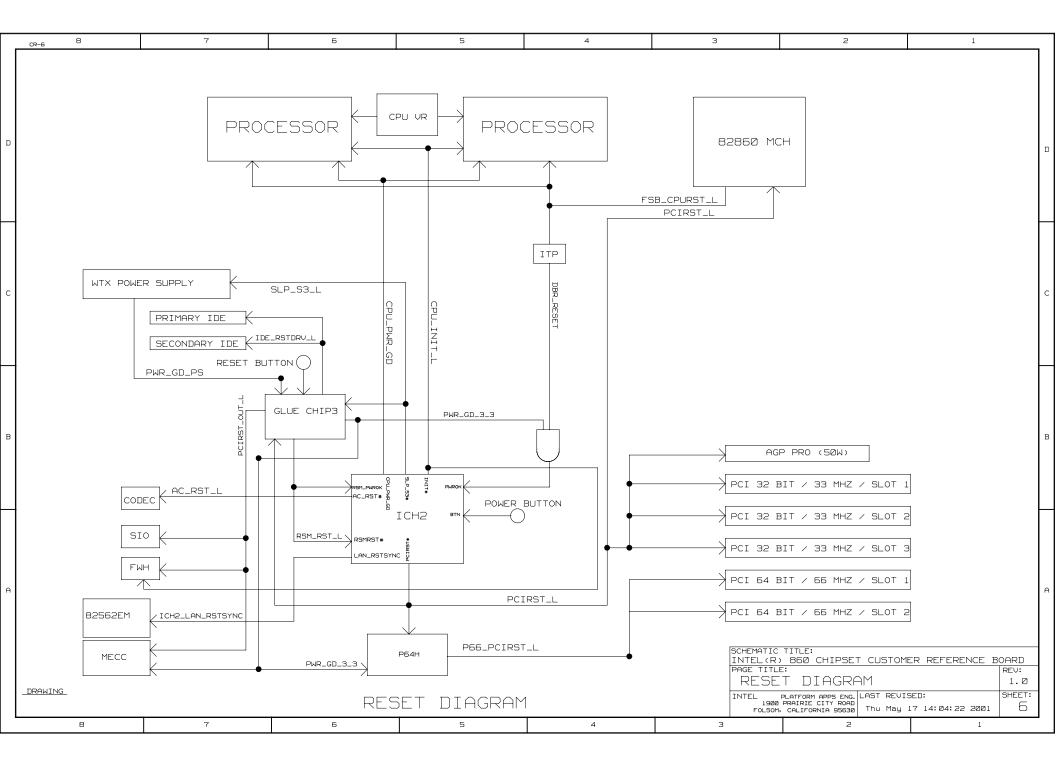

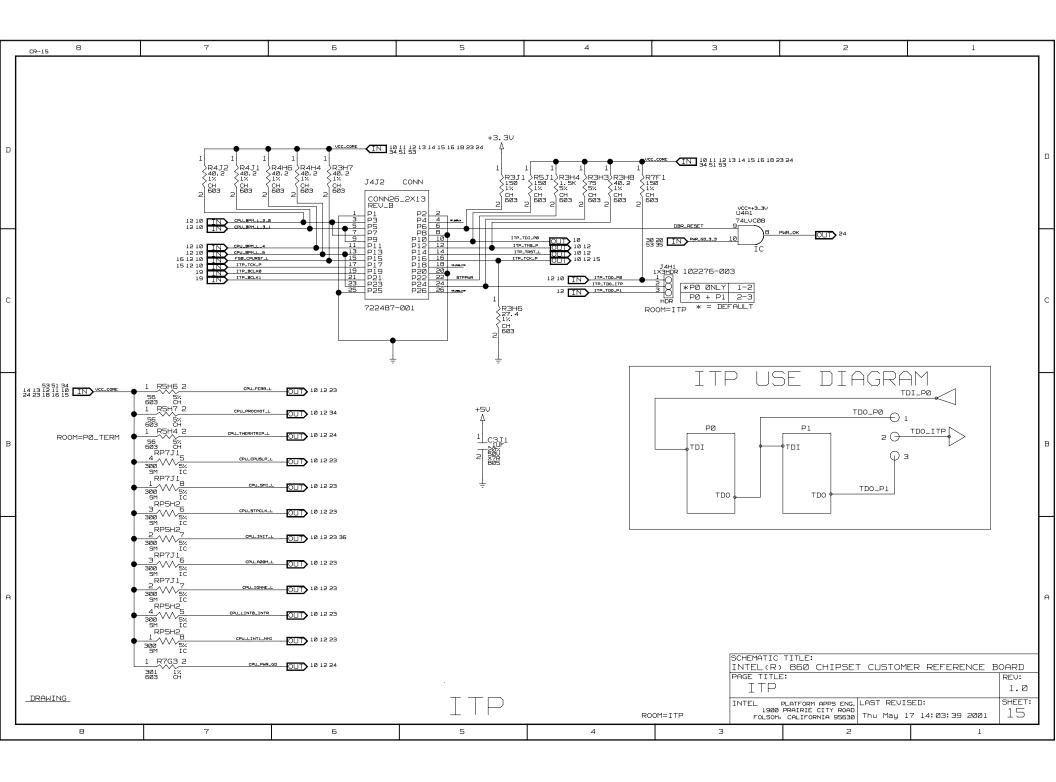

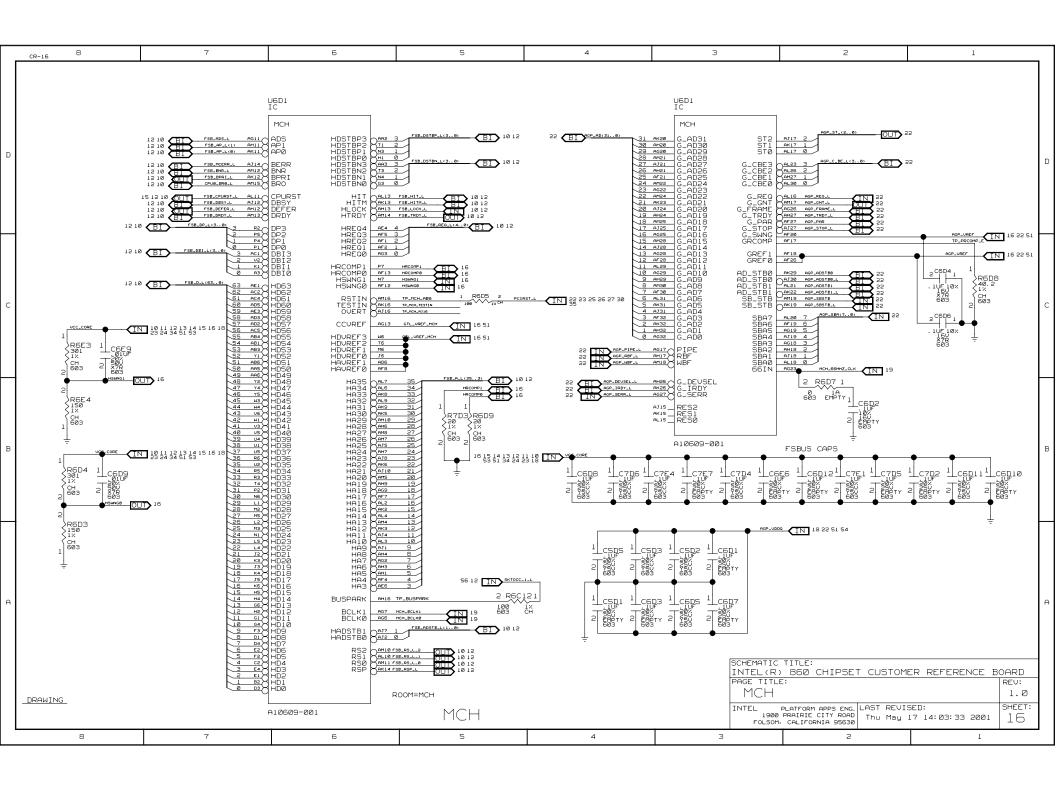

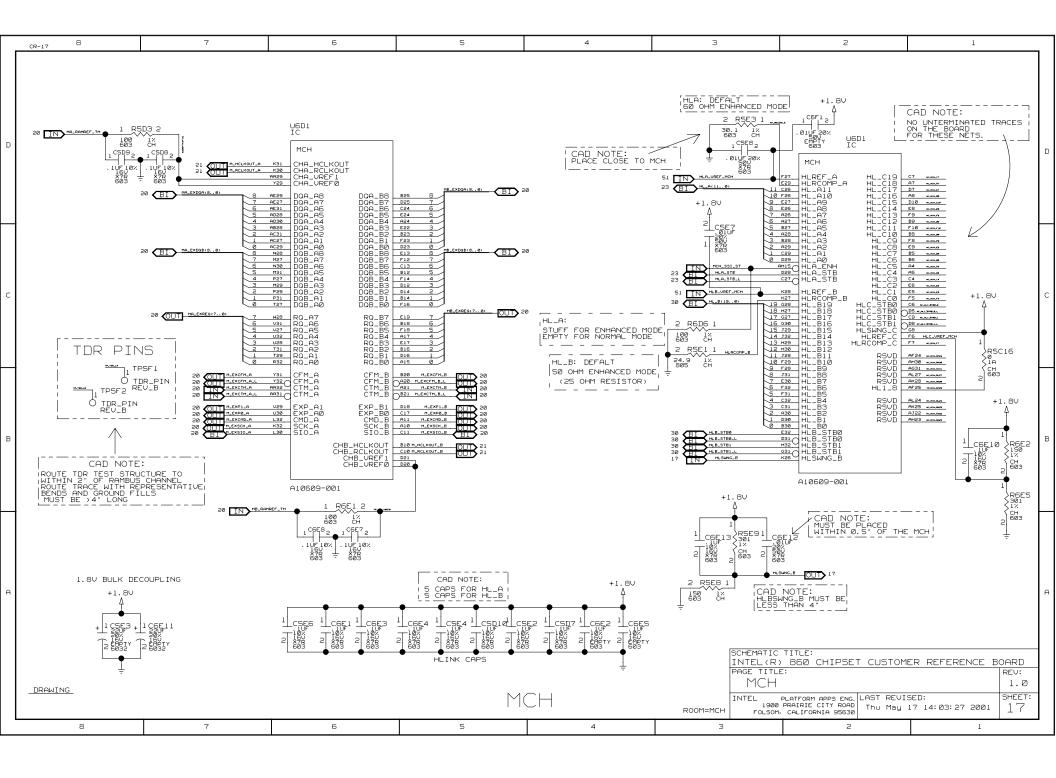

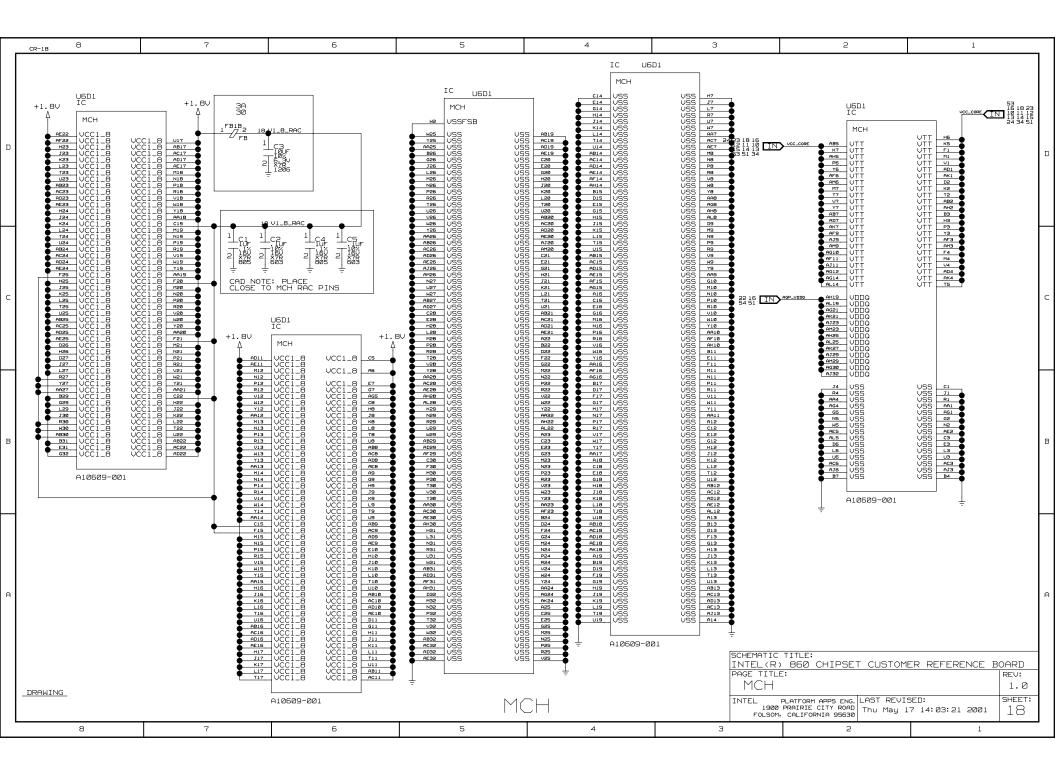

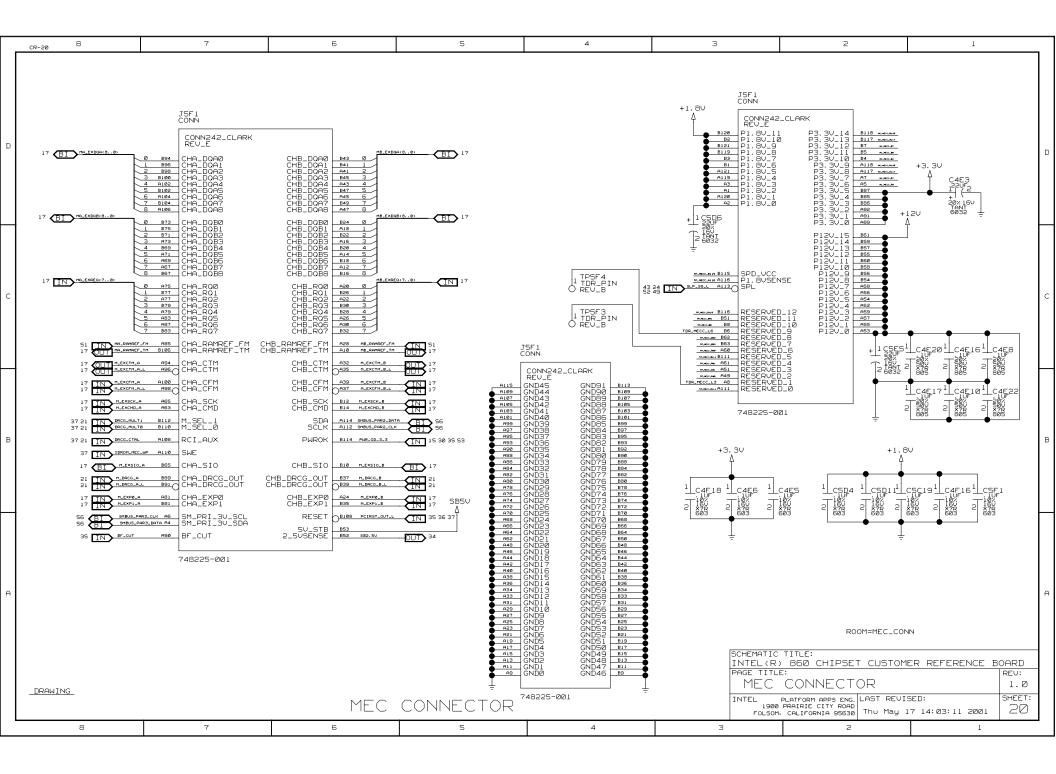

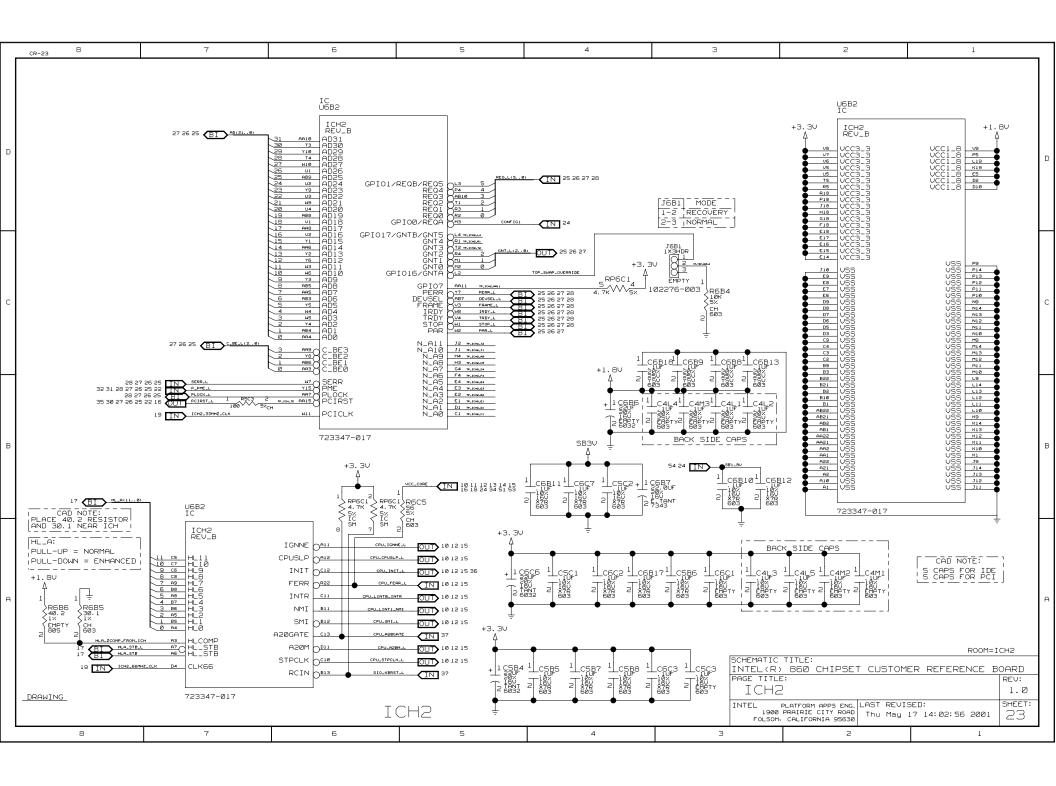

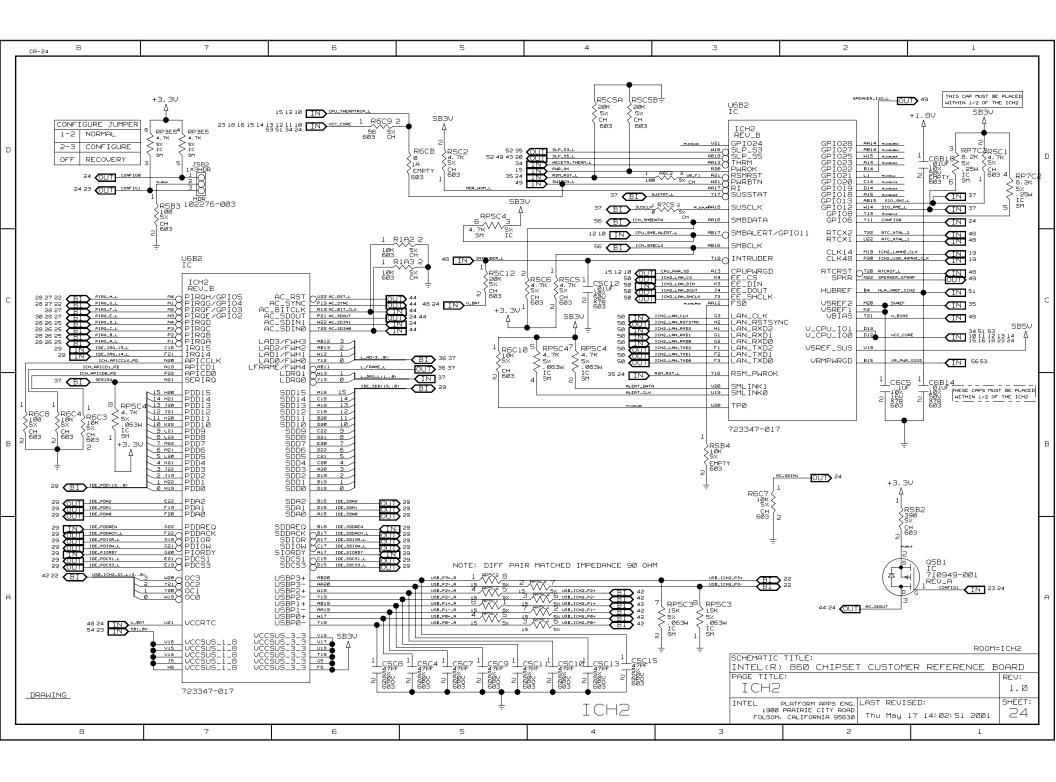

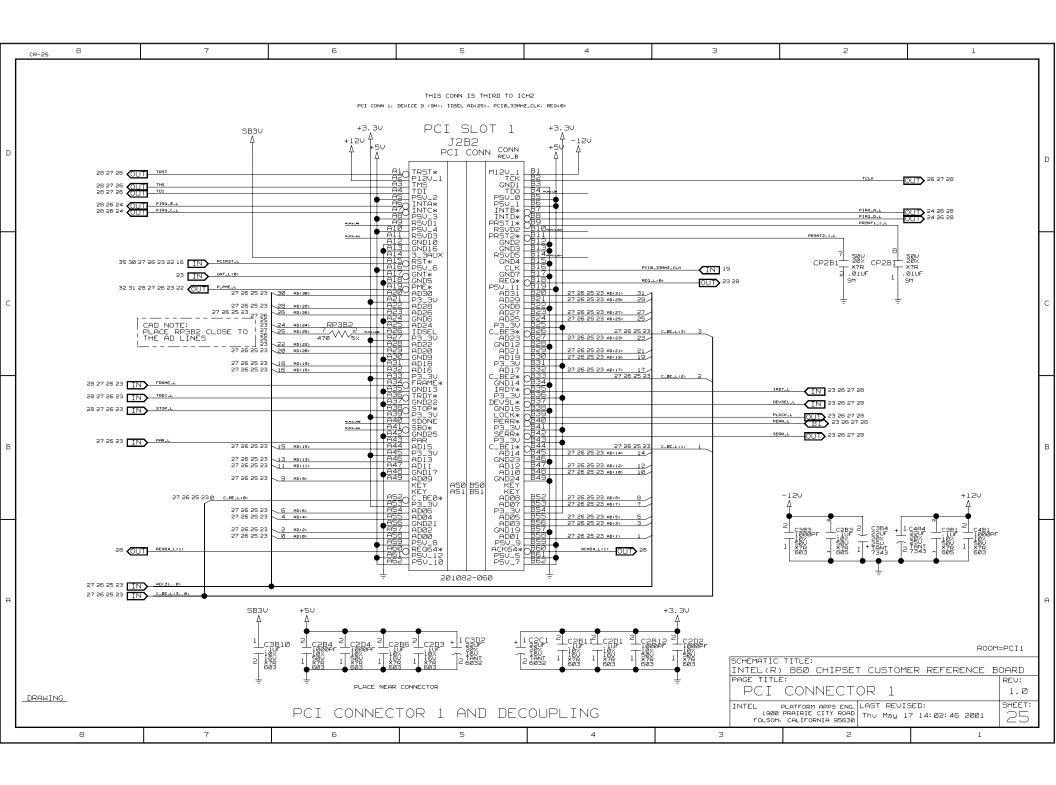

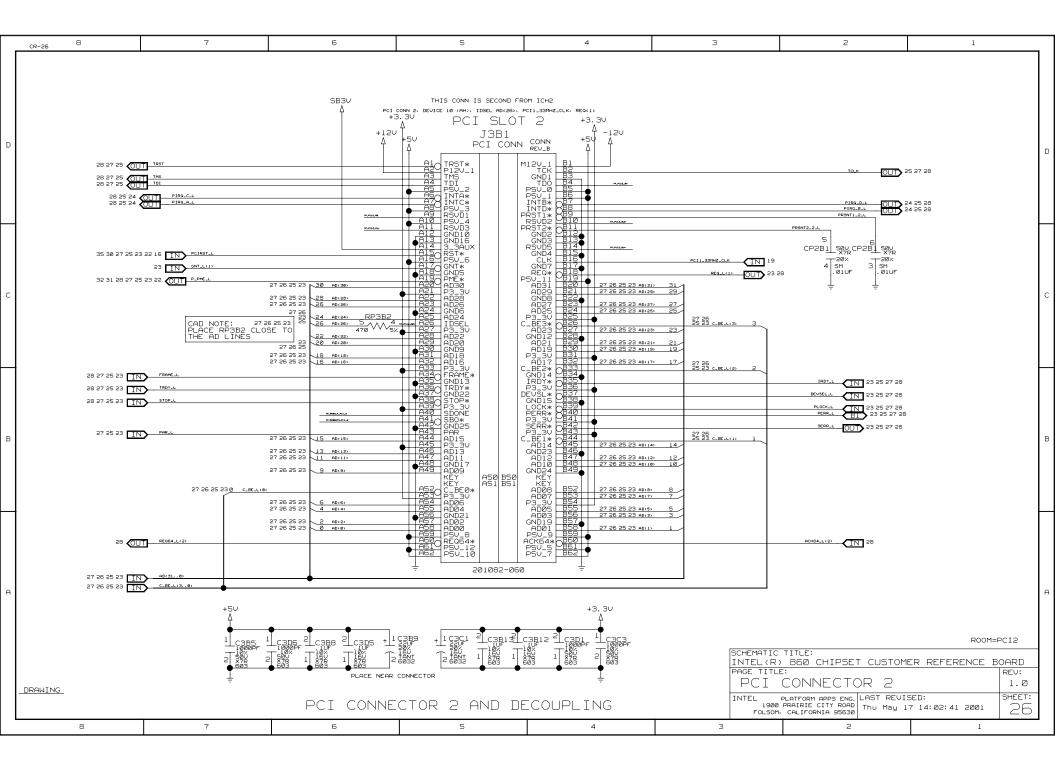

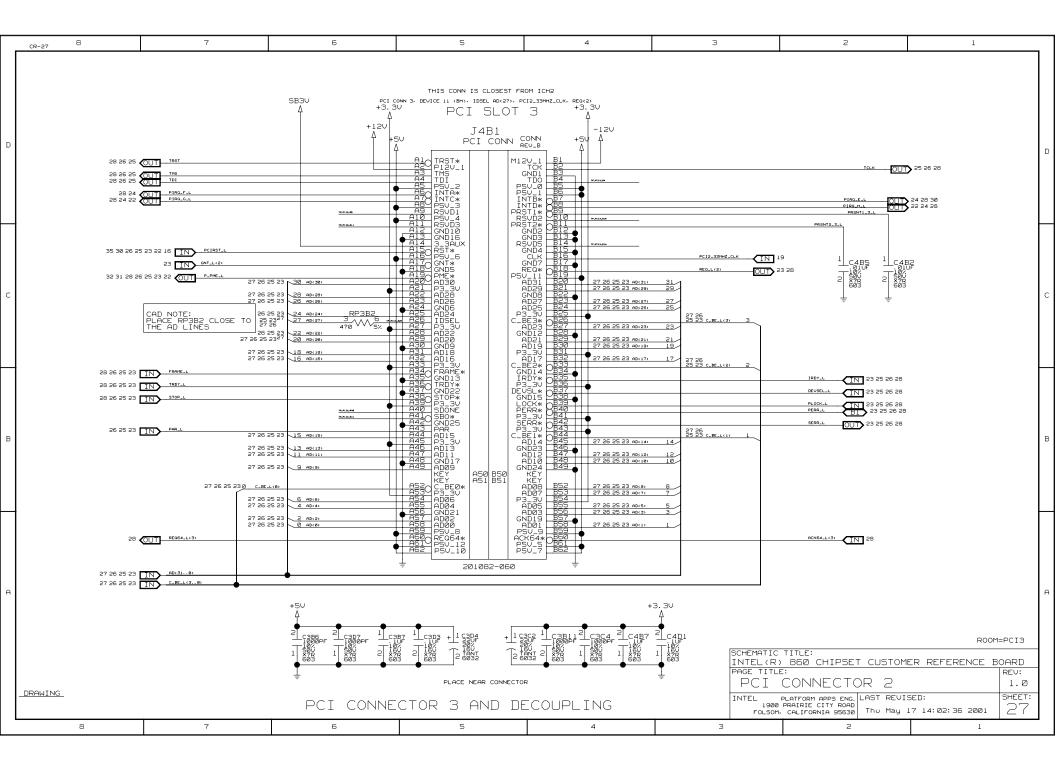

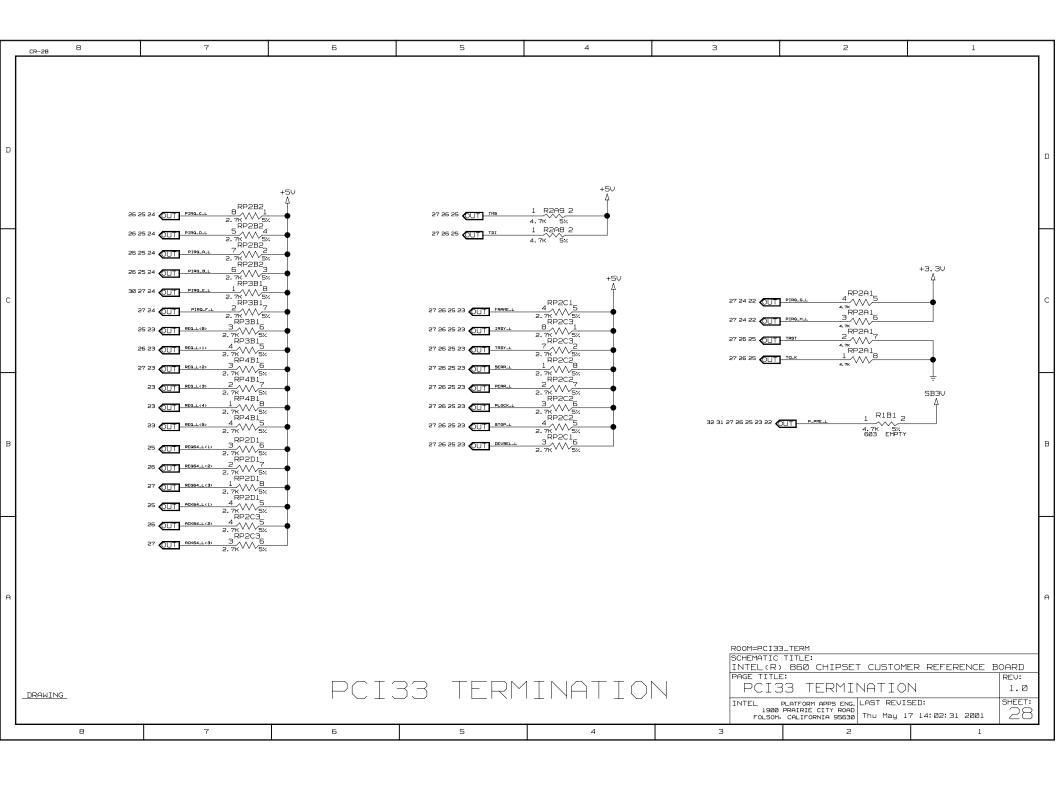

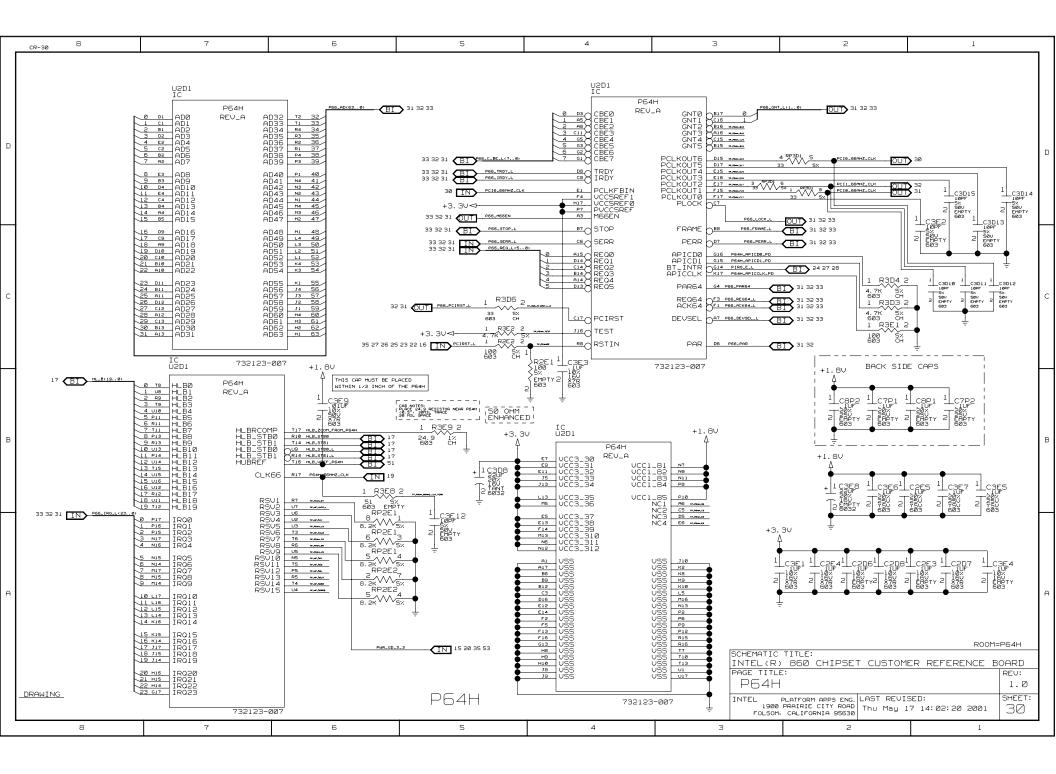

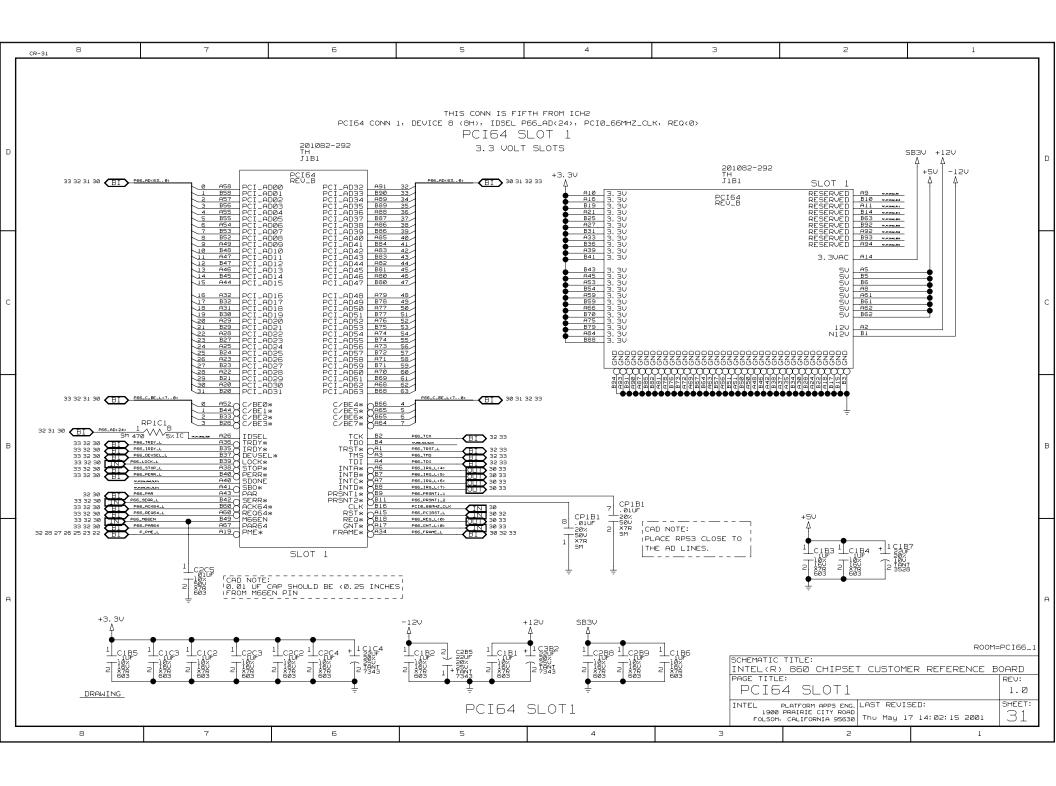

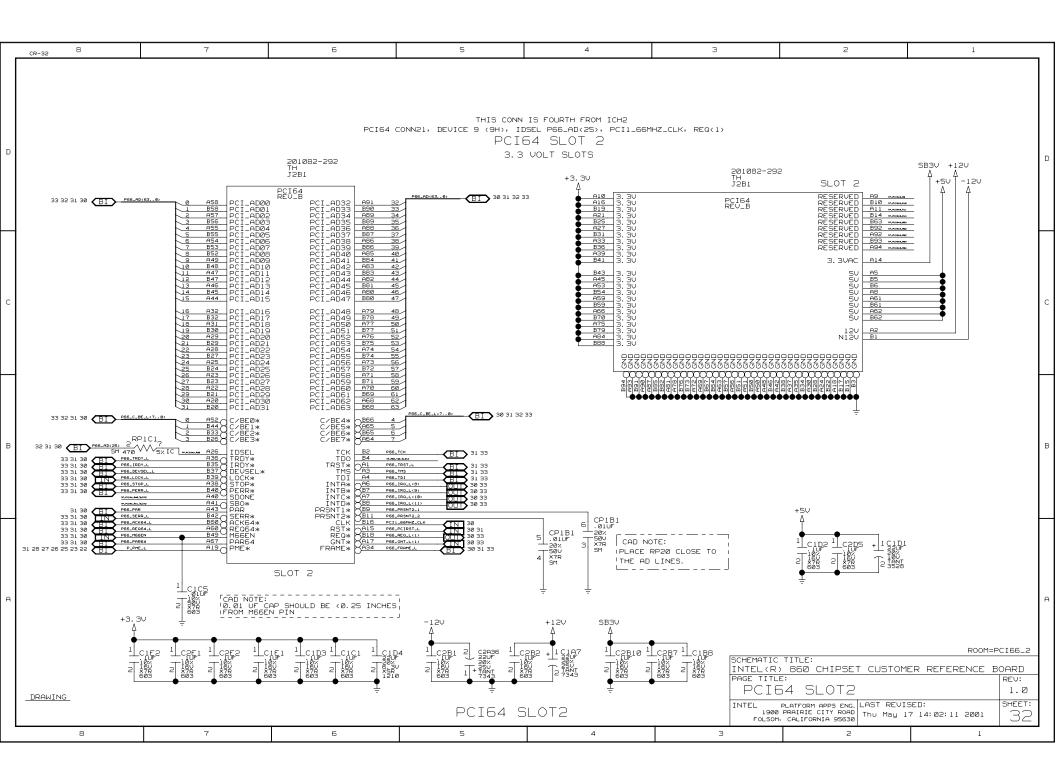

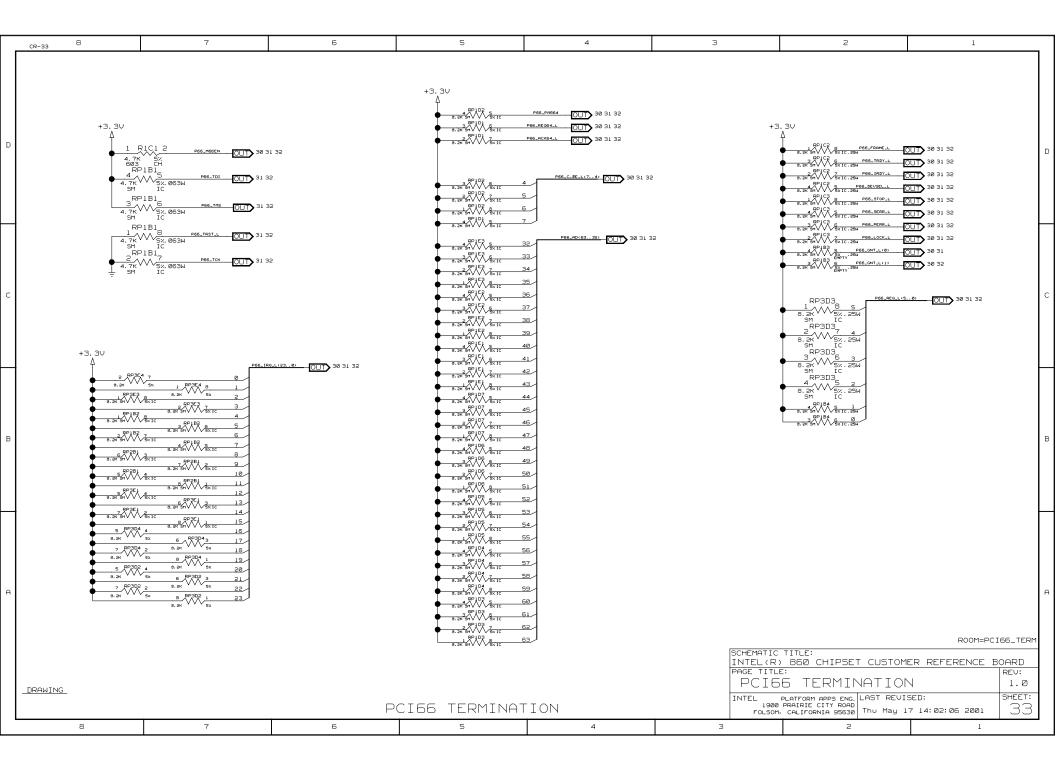

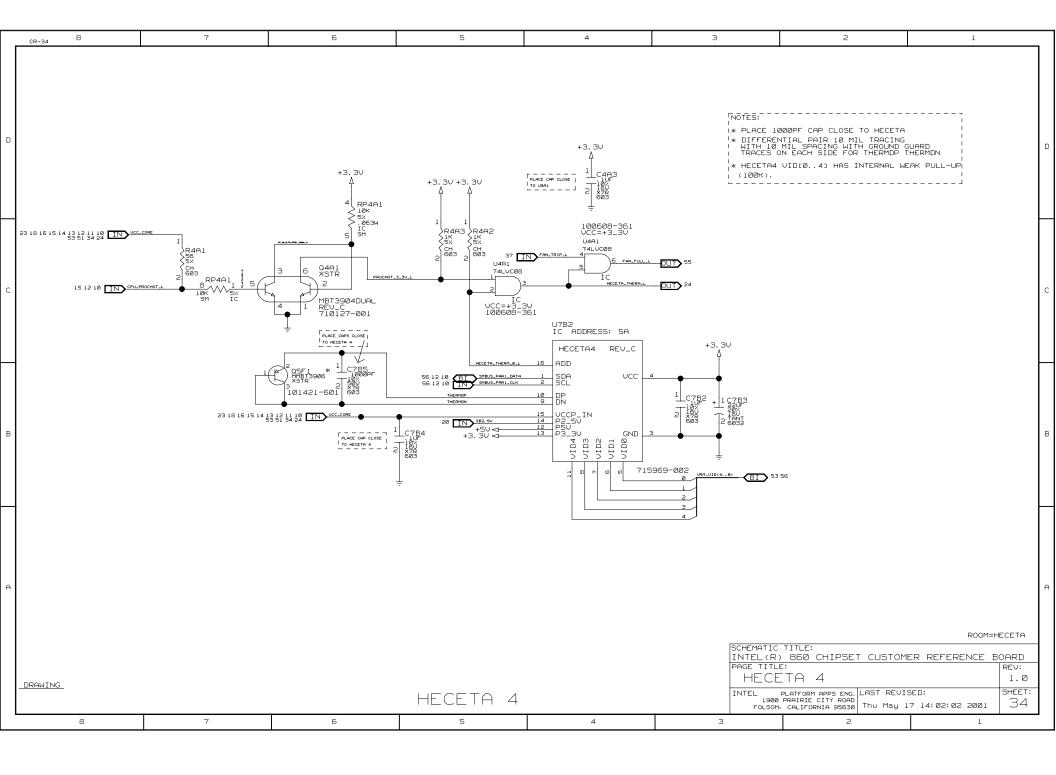

| Annendiy A. | Customa | er Reference Board Schematics                         | 347 |

|             |         |                                                       |     |

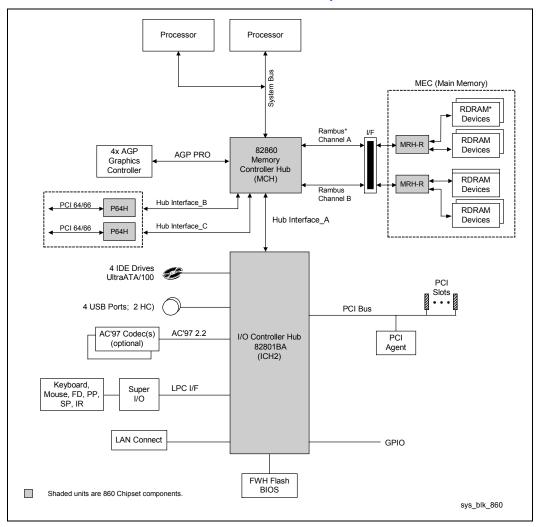

| Figure 1. Workstation System Configuration Using the Intel <sup>®</sup> Xeon <sup>™</sup> Processor/ |    |

|------------------------------------------------------------------------------------------------------|----|

| Intel Xeon Processor with 512 KB L2 Cache and Intel® 860 Chipset                                     | 29 |

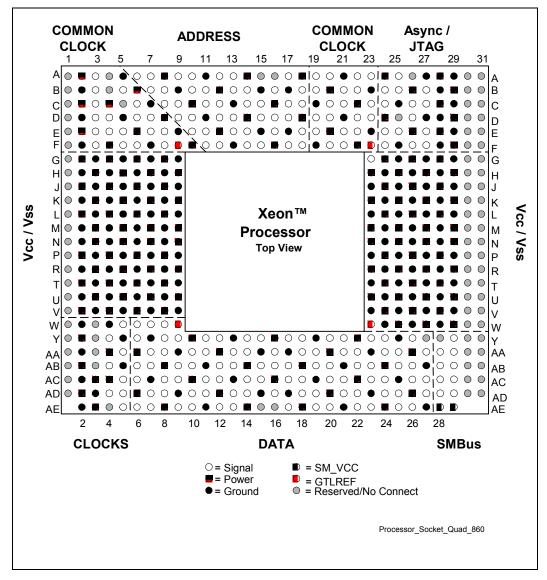

| Figure 2. TOP VIEW—Intel® Xeon™ Processor Socket Quadrant Layout                                     | 38 |

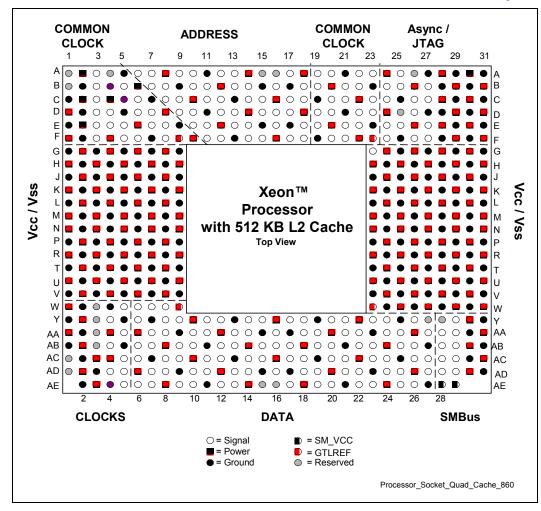

| Figure 3. TOP VIEW—Intel® Xeon™ Processor with 512 KB L2 Cache                                       |    |

| Socket Quadrant Layout                                                                               | 39 |

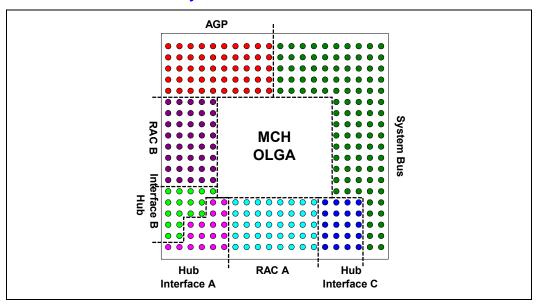

| Figure 4. TOP VIEW—MCH Quadrant Layout                                                               | 40 |

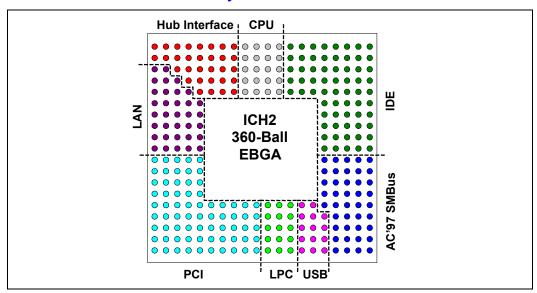

| Figure 5. TOP VIEW—Intel® ICH2 Quadrant Layout                                                       | 40 |

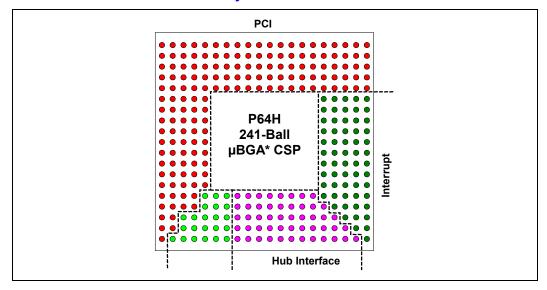

| Figure 6. TOP VIEW—Intel® P64H Quadrant Layout                                                       | 41 |

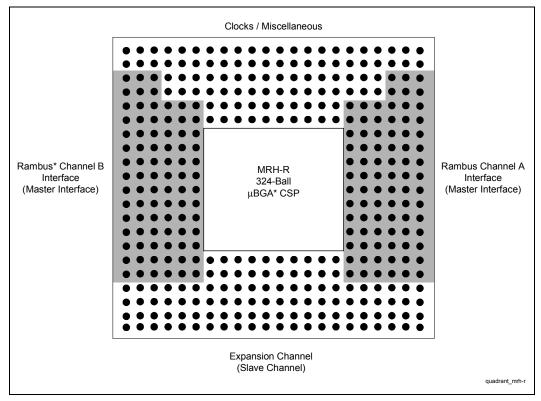

| Figure 7. TOP VIEW— Intel® MRH-R Quadrant Layout                                                     | 41 |

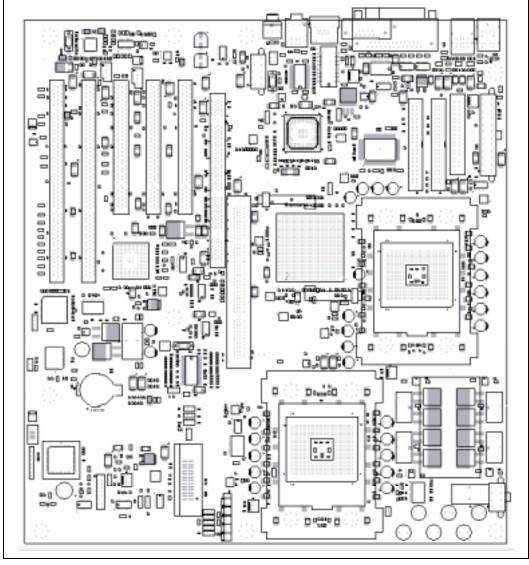

| Figure 8. DP Workstation Component Placement Example in an Extended ATX                              |    |

| Form Factor                                                                                          |    |

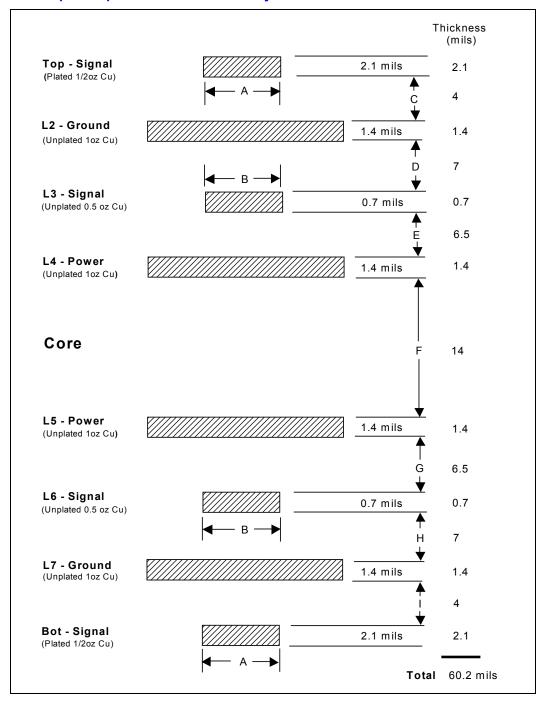

| Figure 9. Eight Layer Stack-Up for DP Configurations—Option A                                        | 45 |

| Figure 10. Eight Layer Stack-Up for DP Configurations—Option B                                       |    |

| Figure 11. Dual Processor Stack-Up Example                                                           |    |

| Figure 12. Dual Processor Example Stack-Up B                                                         |    |

| Figure 13. Stack-Up Example B Thickness Summary                                                      |    |

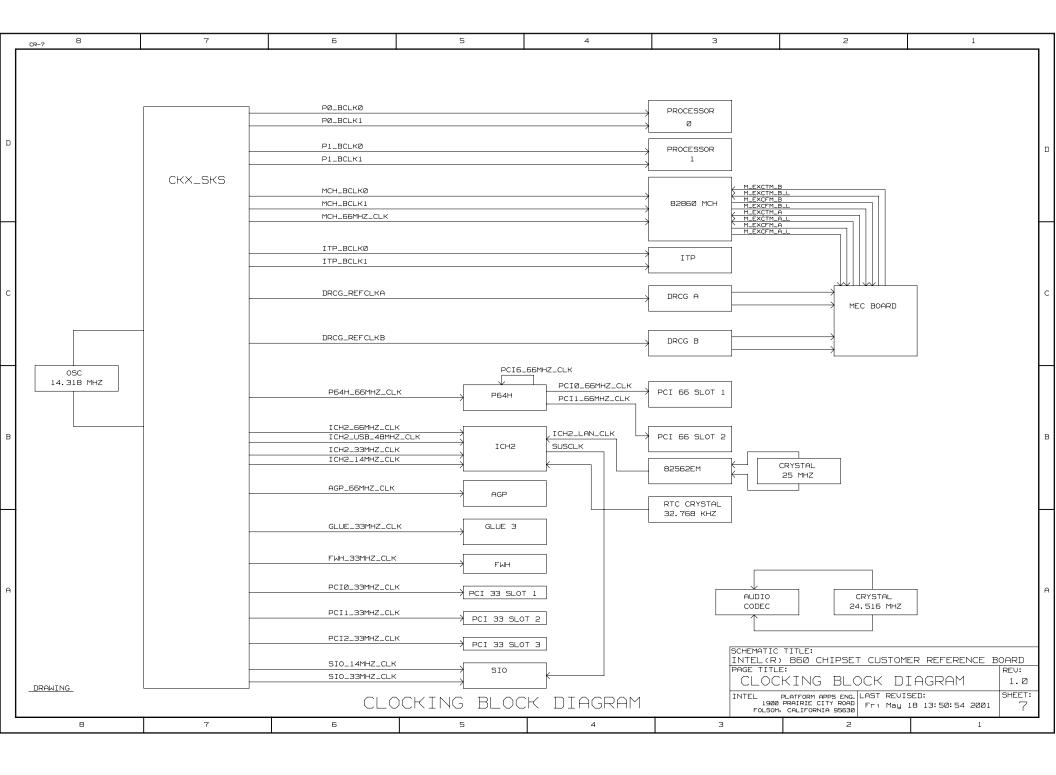

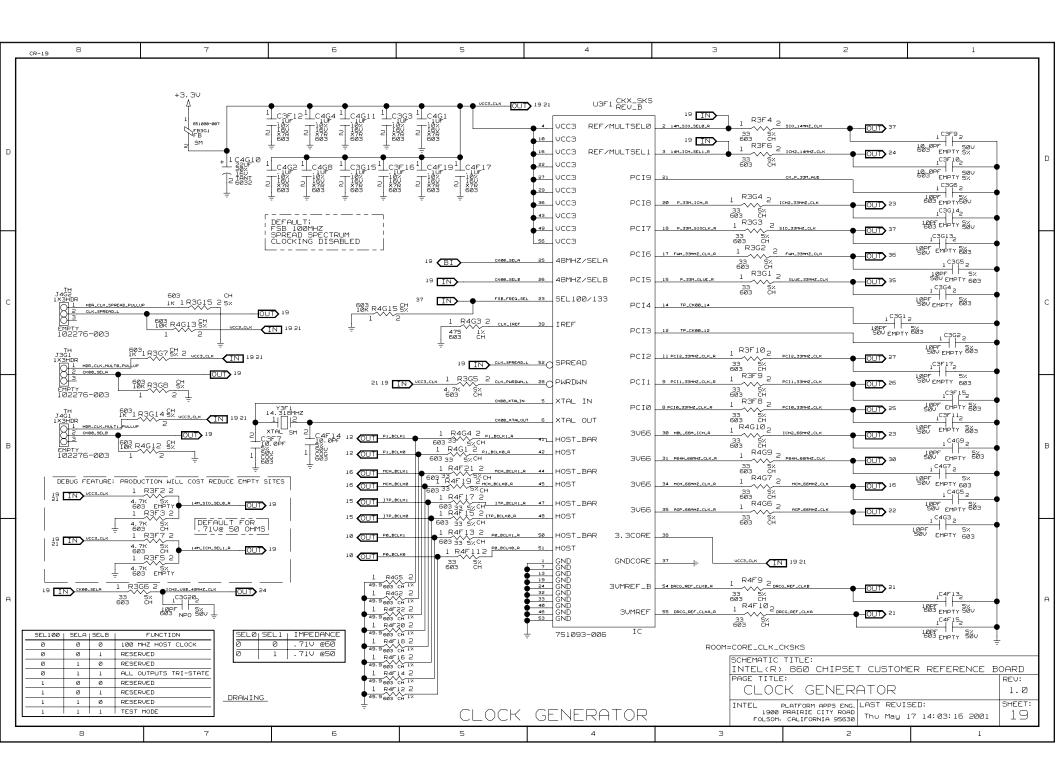

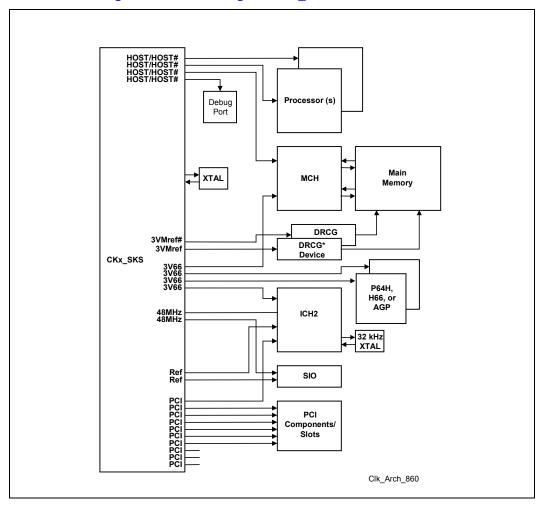

| Figure 14. Platform Clocking Architecture Using the CKx_SKS                                          |    |

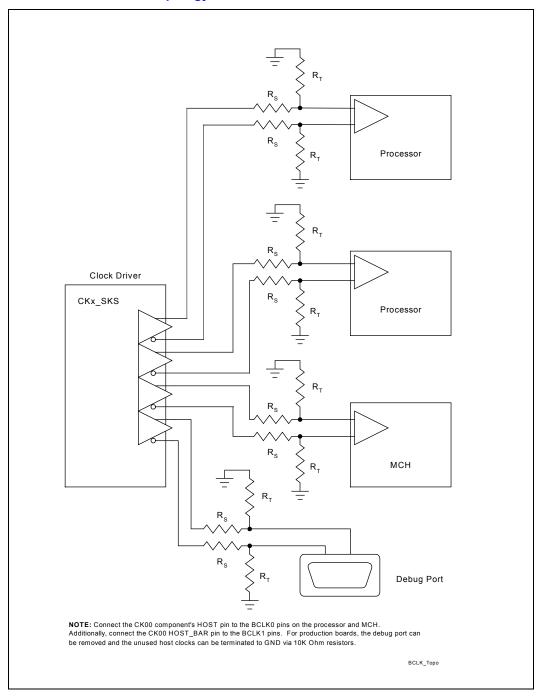

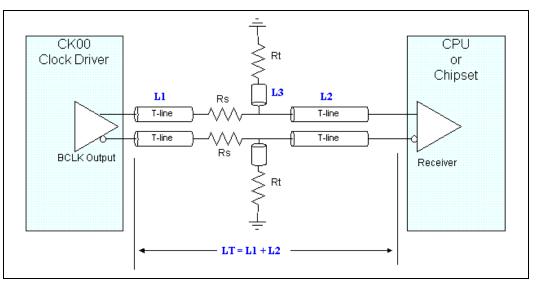

| Figure 15. Dual Processor BCLK Topology                                                              |    |

| Figure 16. Source Shunt Termination                                                                  |    |

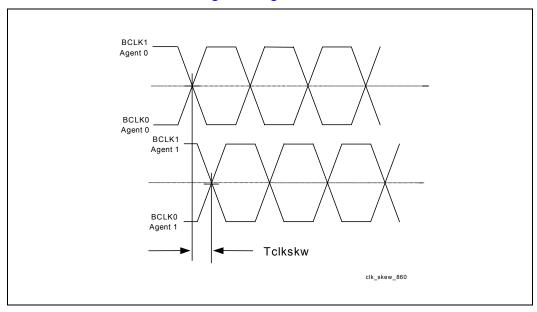

| Figure 17. Clock Skew as Measured from Agent-to-Agent                                                |    |

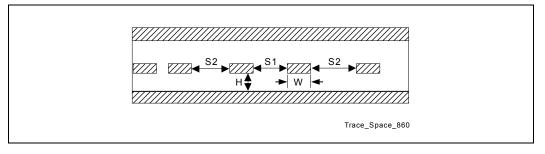

| Figure 18. Trace Spacing                                                                             |    |

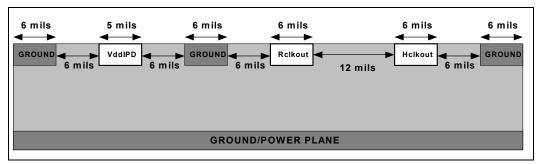

| Figure 19. VddIR and 3VMRef or 3VMRef# Routing                                                       |    |

| Figure 20. MCH to DRCG* Device Routing Diagram                                                       |    |

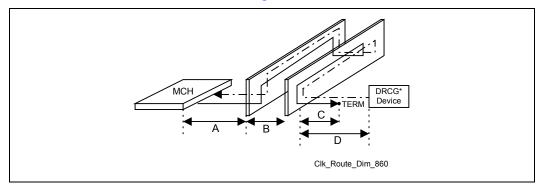

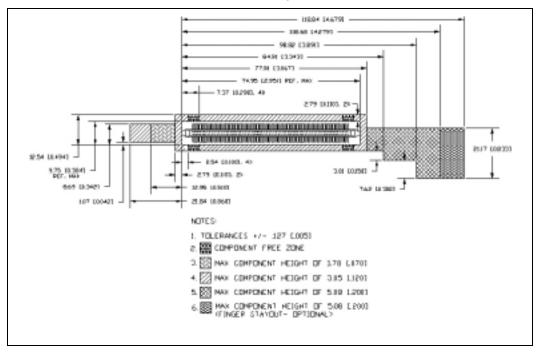

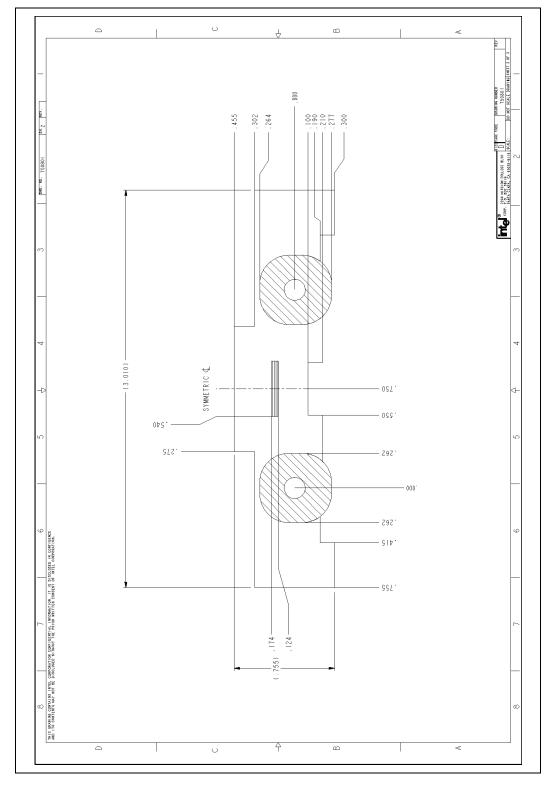

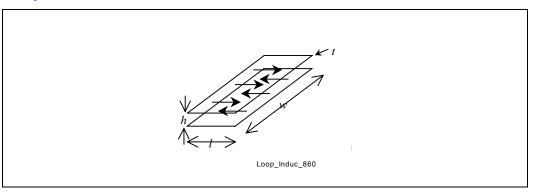

| Figure 21. Direct Rambus* Clock Generator Routing Dimension                                          |    |

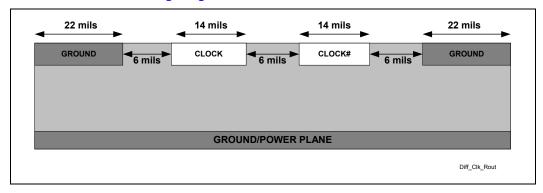

| Figure 22. Differential Clock Routing Diagram                                                        |    |

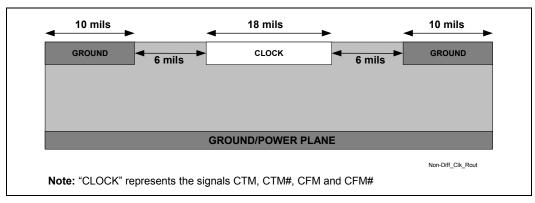

| Figure 23. Non-Differential Clock Routing Diagram                                                    |    |

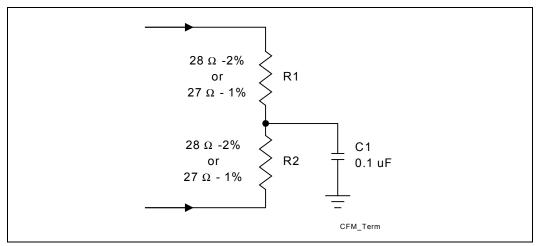

| Figure 24. CFM/CFM# Termination                                                                      |    |

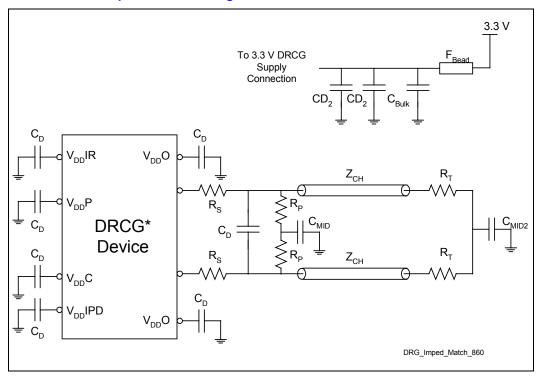

| Figure 25. DRCG* Device Impedance Matching Network                                                   |    |

| Figure 26. DRCG* Device Layout Example                                                               |    |

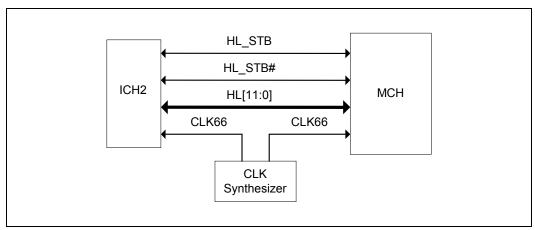

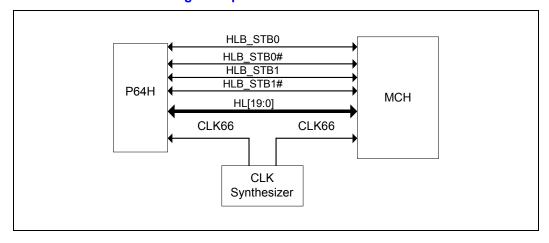

| Figure 27. 66 MHz/33 MHz Clock Relationships                                                         |    |

| Figure 28. AGP_66 Clock Routing Topology                                                             |    |

| Figure 29. CLK_66 Clock Routing Topology                                                             |    |

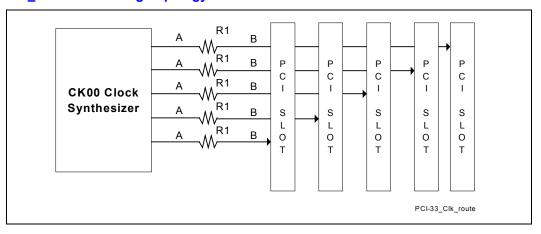

| Figure 30. PCI_33 Clock Routing Topology                                                             |    |

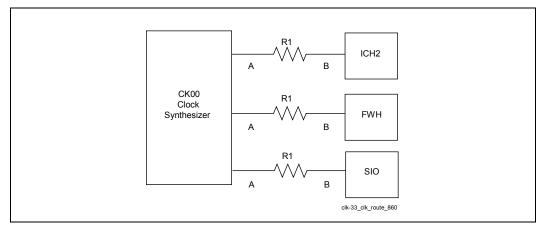

| Figure 31. CLK 33 Clock Routing Topology                                                             | 67 |

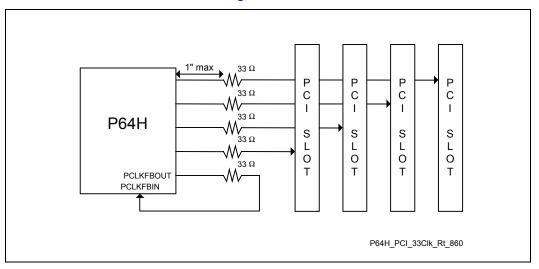

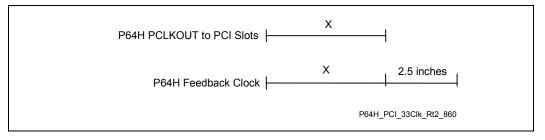

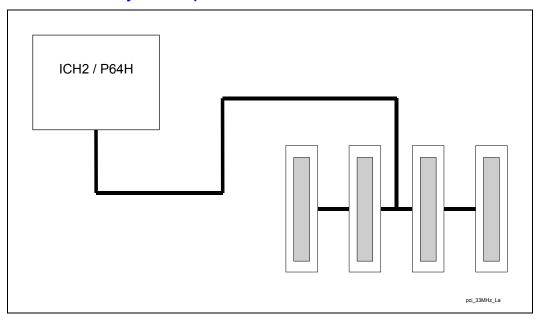

| Figure 32. Intel® P64H PCI 33 MHz Clock Routing                                                      | 68 |

| Figure 33. Intel® P64H PCI 33 MHz Clock Routing                                                      | 68 |

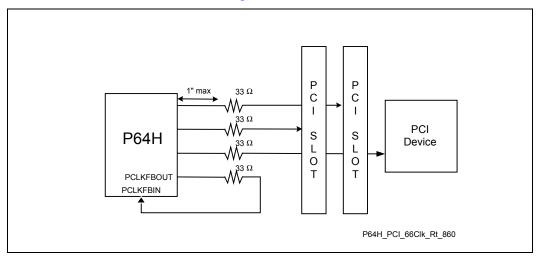

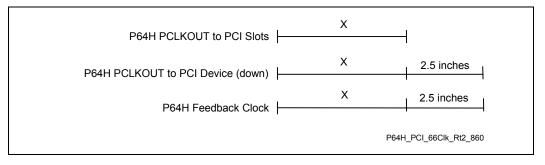

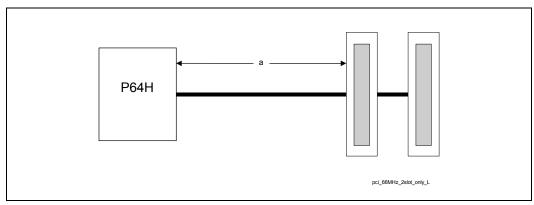

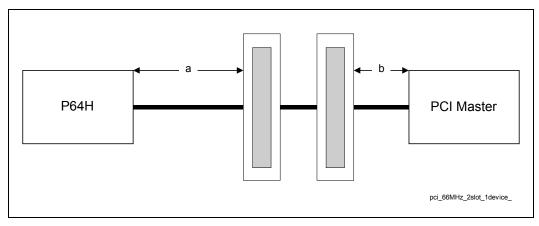

| Figure 34. Intel® P64H PCI 66 MHz Clock Routing                                                      | 69 |

| Figure 35. 66 MHz PCI Clock Routing                                                                  |    |

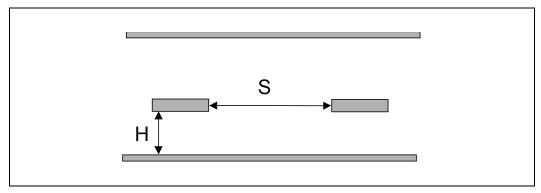

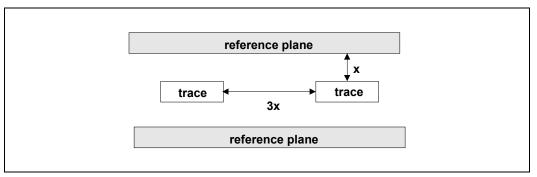

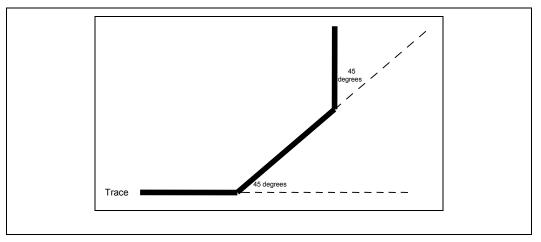

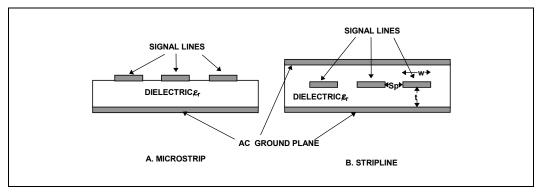

| Figure 36. Serpentine Spacing – Diagram of Spacing to Reference Plane                                |    |

| Height Ratio                                                                                         | 73 |

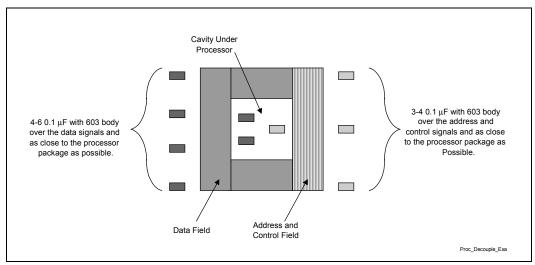

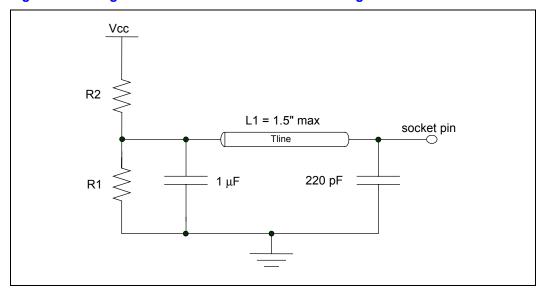

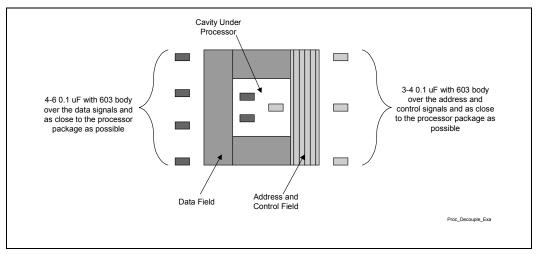

| Figure 37. I/O Decoupling Guidelines for the Processor                                               | 74 |

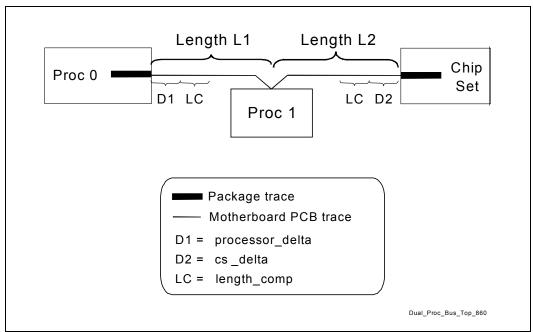

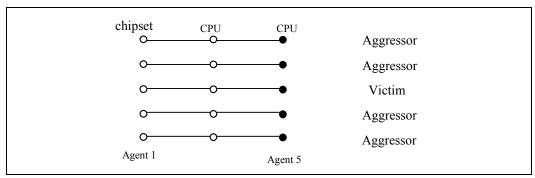

| Figure 38. Dual Processor System Bus Topology                                                        | 77 |

| Figure 39. Cross Sectional View of 3:1 Ratio for Stripline (Edge-to-Edge                             |    |

| Trace Spacing vs. Trace to Reference Plane Height)                                                   | 78 |

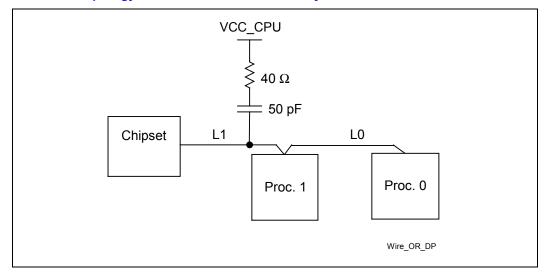

| Figure 40. Wired OR Topology for Dual Processor Based Systems                                        |    |

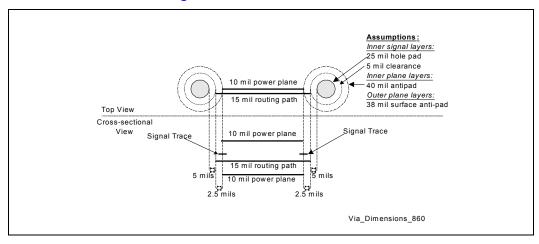

| Figure 41. Via Dimensions and Routing Path                                                           | 82 |

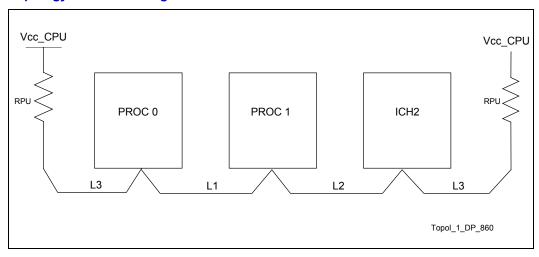

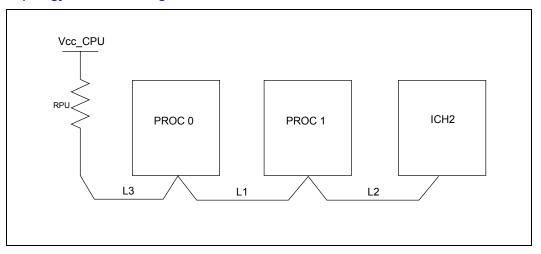

| Figure 42. Topology 1 for DP Configuration                                                           | 85 |

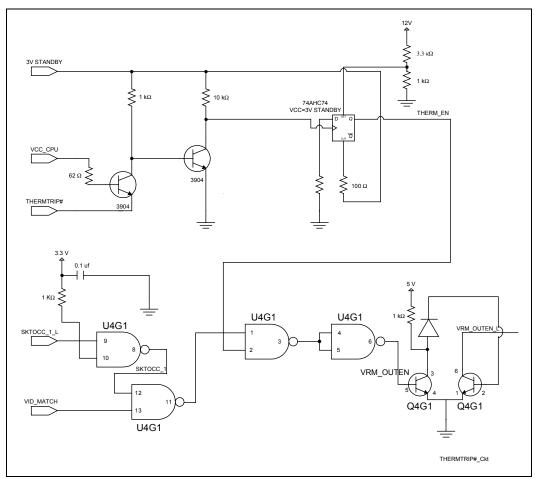

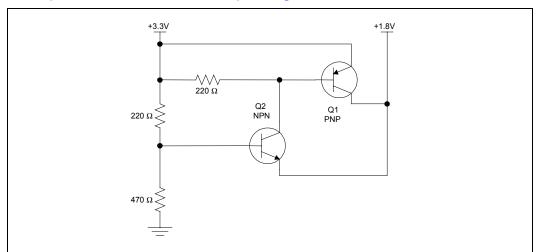

| Figure 43. Recommended THERMTRIP# Circuit                                                            | 86 |

| Figure 44. Topology 2 for DP Configuration                                                           |    |

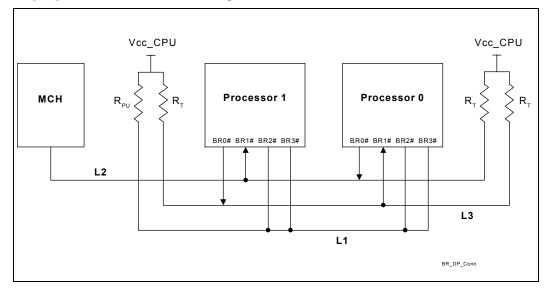

| Figure 45. BRI3:01# Connection for DP Configuration                                                  | 90 |

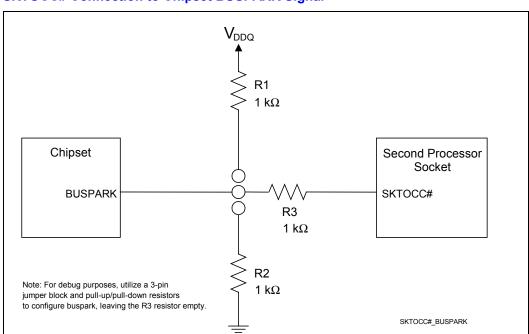

|                                                                                                                                                                                                                                        | SKTOCC# Connection to Chipset BUSPARK Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Figure 47.                                                                                                                                                                                                                             | Voltage Divider Network for Reference Voltage Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93                                                                                                                         |

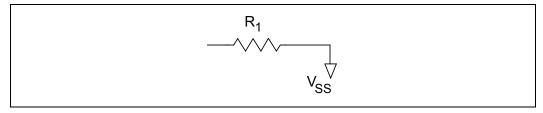

| Figure 48.                                                                                                                                                                                                                             | Pull-Down Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93                                                                                                                         |

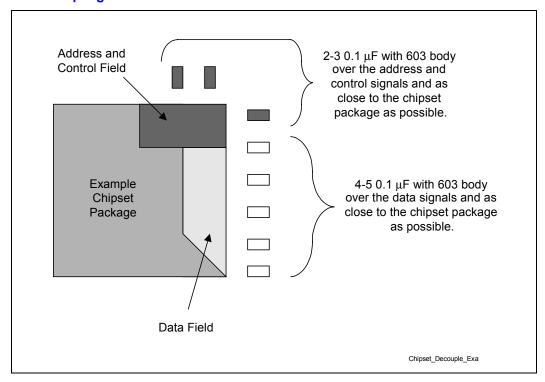

|                                                                                                                                                                                                                                        | I/O Decoupling Guidelines for the MCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

|                                                                                                                                                                                                                                        | Rambus* Channel Signal Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

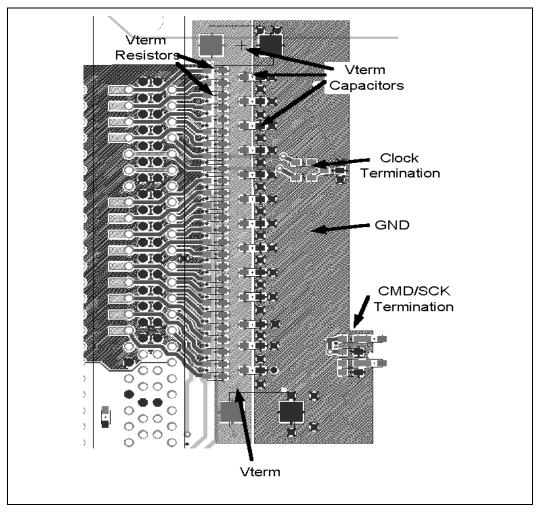

|                                                                                                                                                                                                                                        | Intel® 860 Chipset MCH Rambus* Channel Routing Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

|                                                                                                                                                                                                                                        | Example Rambus* Channel Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

|                                                                                                                                                                                                                                        | RSL Routing Diagram Showing Ground Isolation Traces with Via                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 100                                                                                                                      |

| rigure 55.                                                                                                                                                                                                                             | Around Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 101                                                                                                                        |

| Eiguro 54                                                                                                                                                                                                                              | Rambus* Channel Trace Length Matching Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

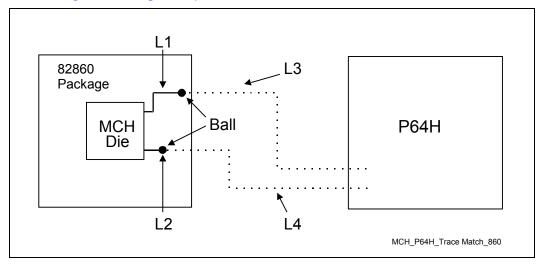

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

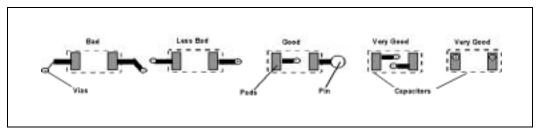

|                                                                                                                                                                                                                                        | "Dummy" vs. "Real" Vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

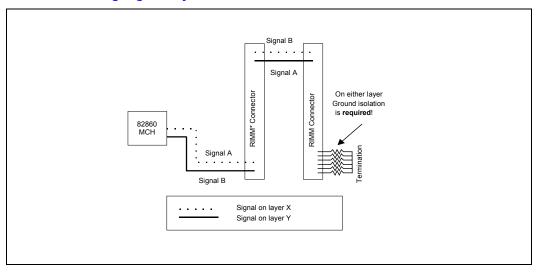

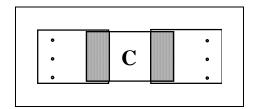

|                                                                                                                                                                                                                                        | RSL and Clocking Signal Layer Alteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 100                                                                                                                      |

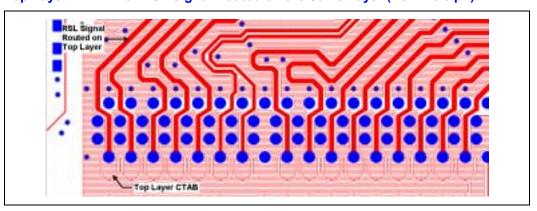

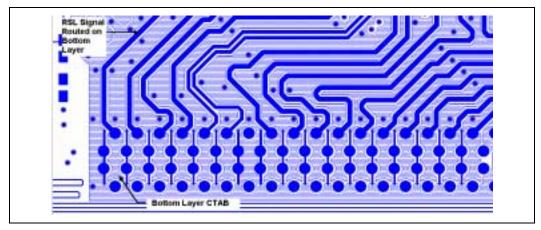

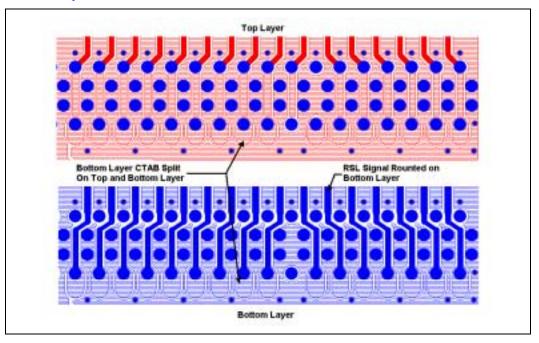

| Figure 57.                                                                                                                                                                                                                             | Top Layer CTAB with RSL Signal Routed on the Same Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 400                                                                                                                        |