# 82359 DRAM CONTROLLER

- Dual Ported Memory Controller

- Allows EISA/Host Bus Concurrency

- CPU Speed Independent

- Controls up to 256M of Motherboard DRAM

- LIM Hardware Support

- Support for Shadow/Disable/ Remap/Cacheing/Write Protect of Motherboard Memory

- **Flexible DRAM Support**

- 64K, 256K, 1M, 4M, 16M (4M x 4)

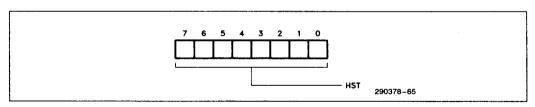

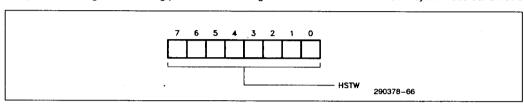

- 60 ns, 70 ns, 80 ns speeds

- Single or Double Density SIMMs

- Ability to Mix DRAM Sizes

- Supports 32-, 64-, or 128-Bit Wide Memory Configurations

- High Integration

- Integrated Posted Write Latch

- Cacheability/Write Protect Map

- Integrated Delay Lines

- Integrated Bus Drivers

- Integrated Delay Line

- Critical DRAM Timings Generated Internally

- DRAM Timings are Programmable with 2.61 ns Resolution

- Cache Support

- Support for 82385, 82395, 82485 Cache

- Built-in Snoop Filter

- **CPU Support**

- Support for Intel386™ and Intel486™ Microprocessors

- Intel486™ Burst Reads at 0 Wait State

- --- Posted Writes at 0 Wait State

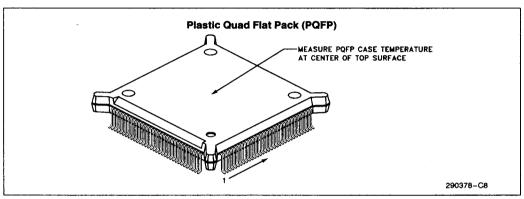

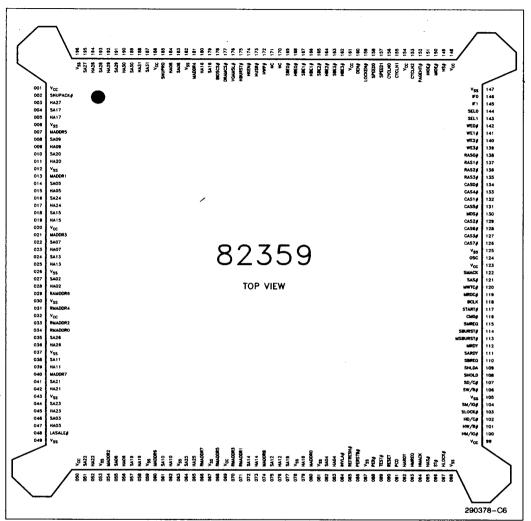

- **196-Pin PQFP Package**

(See Package Specification Order Number 240800, Package Type KU)

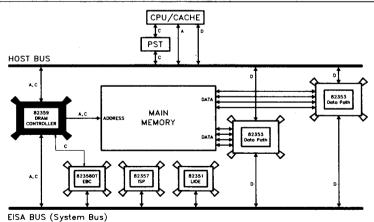

The 82359 DRAM Controller is a highly integrated advanced memory controller capable of supporting today's Intel386 and Intel486 high performance microprocessors. Its decoupled handshake protocol gives the 82359 independence over processor type and speed, allowing the system designer to implement a variety of CPU/cache combinations.

The 82359 implements a dual ported architecture by providing two independent address paths to main memory. This allows activity on each bus to run independently of the other, giving each greater bus throughput and decreased bus latency.

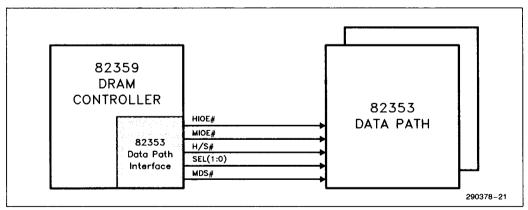

The 82359 provides address control, refresh generation, critical DRAM timing generation and, by working closely with two 82353 Advanced Data Path devices, provides a highly integrated 32-bit dual ported memory controller in just three VLSI components.

\*Diagram illustrates Standard Configuration

Intel386<sup>TM</sup> and Intel486<sup>TM</sup> are trademarks of Intel Corporation.

290378-1

October 1992 Order Number: 290378-005

1-522

## 1

# 82359 DRAM Controller

| CONTENTS PAGE                                                                                          | CONTENTS PAGE                                              |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 82359 BLOCK DIAGRAM 1-525                                                                              | 7.0 82353 ADVANCED DATA PATH                               |

| <b>1.0 INTRODUCTION</b> 1-526                                                                          | INTERFACE 1-572                                            |

| 2.0 PIN DESCRIPTION QUICK                                                                              | 8.0 INTERNAL DELAY LINES 1-574                             |

| REFERENCE 1-528                                                                                        | 9.0 THROTTLE MECHANISMS 1-577                              |

| 3.0 REGISTER QUICK REFERENCE 1-534                                                                     | 9.1 Introduction                                           |

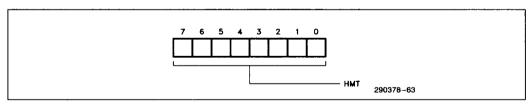

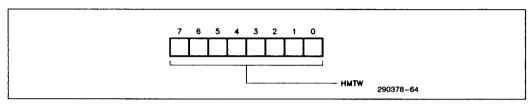

| 4.0 HARDWARE OVERVIEW 1-547                                                                            | 9.2 Host-to-Memory Throttle and Watchdog (HMT, HMTW) 1-578 |

| 4.1 Host Interface                                                                                     | 9.3 System-to-Memory Throttle (SMT)1-578                   |

| <ul><li>4.2 Host Address, Cycle Definition 1-548</li><li>4.3 Memory Ownership Protocol 1-549</li></ul> | 9.4 Host-to-System Throttle and Watchdog (HST, HSTW)       |

| 4.4 Start of Host Cycles 1-550                                                                         |                                                            |

| 4.5 Host Cycle Types 1-550                                                                             | <b>10.0 SNOOP FILTER</b> 1-579                             |

| 4.6 Deterministic Cycles 1-550                                                                         | <b>11.0 CONCURRENCY</b> 1-581                              |

| 4.7 Non-Deterministic Cycles 1-551                                                                     | 11.1 Concurrent Mode 1-581                                 |

| 4.8 Locked Cycles 1-551                                                                                | 11.2 Non-Concurrent Mode 1-581                             |

| 4.9 Programmable Attributes       1-551         4.10 Snooping       1-551                              | 12.0 LIM SUPPORT 1-581                                     |

|                                                                                                        | 13.0 THE INTERNAL REGISTERS 1-582                          |

| 5.0 SYSTEM PORT                                                                                        | 13.1 Programming the Internal                              |

| 5.1 System Interface Overview 1-553                                                                    | Registers 1-582                                            |

| 5.2 System Address, Cycle Definition                                                                   | 13.2 Register Listing1-585                                 |

| 5.3 System Control Signals 1-554                                                                       | 13.3 Detailed Register Descriptions 1-586                  |

| 5.4 Memory Ownership Protocol 1-555                                                                    | 14.0 DETAILED PIN DESCRIPTIONS 1-626                       |

| 5.5 System Cycles 1-556                                                                                | 14.1 Host Port Interface 1-626                             |

| 5.6 Deadlock Conditions 1-558                                                                          | 14.2 System Port Interface 1-631                           |

| 6.0 MEMORY INTERFACE 1-559                                                                             | 14.3 Memory Interface1-636                                 |

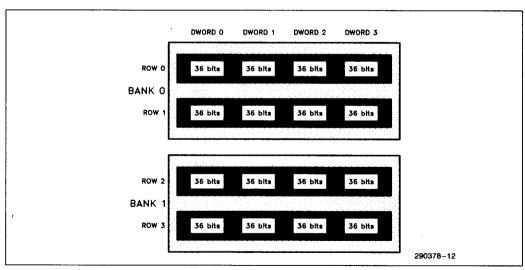

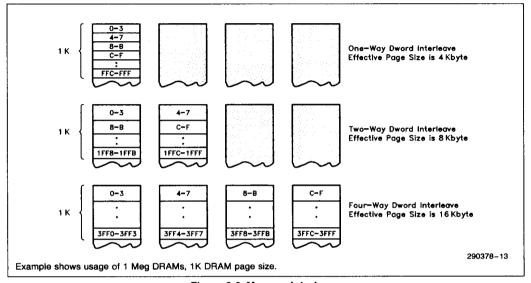

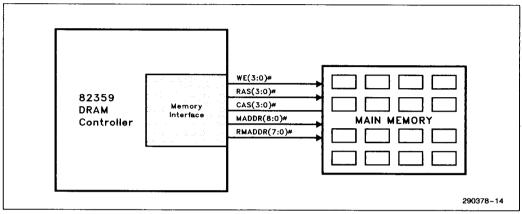

| 6.1 Memory Array Overview 1-559                                                                        | 14.4 82353 Interface 1-638                                 |

| 6.2 Memory Interface Signals 1-562                                                                     | 14.5 Miscellaneous Decodes and                             |

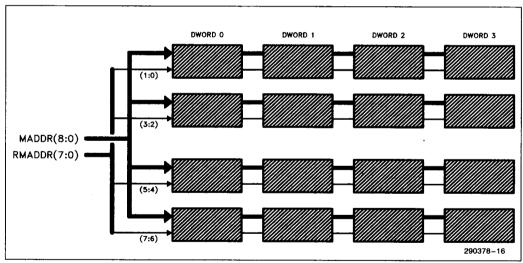

| 6.3 DRAM Address Generation 1-564                                                                      | Control Signals 1-639                                      |

| 6.4 RAS# Modes of Operation 1-567                                                                      |                                                            |

| · ·                                                                                                    |                                                            |

| 6.5 Special Considerations 1-569<br>6.6 DRAM Refresh Generation 1-570                                  |                                                            |

| 6.7 Decoupled Refresh Mode                                                                             |                                                            |

|                                                                                                        |                                                            |

6.8 Coupled Refresh Mode ...... 1-571

| CONTENTS                                                                                                                                                               | PAGE                          | CONTENTS                                                                                                       | PAGE                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------|

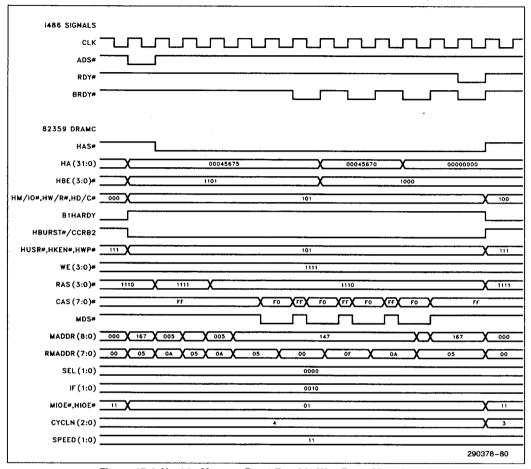

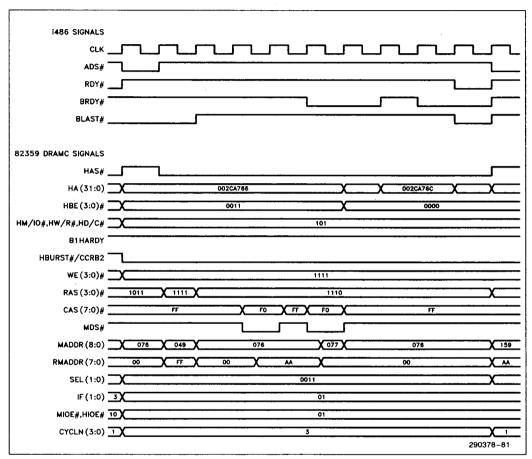

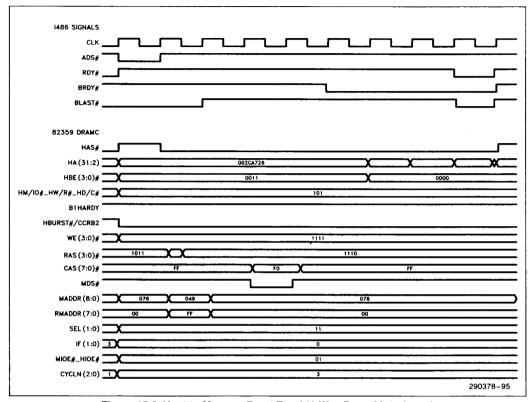

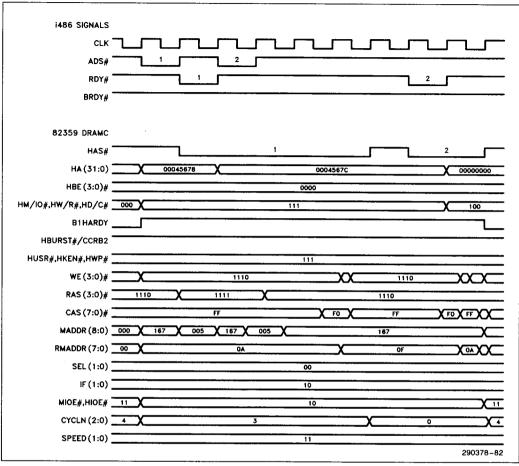

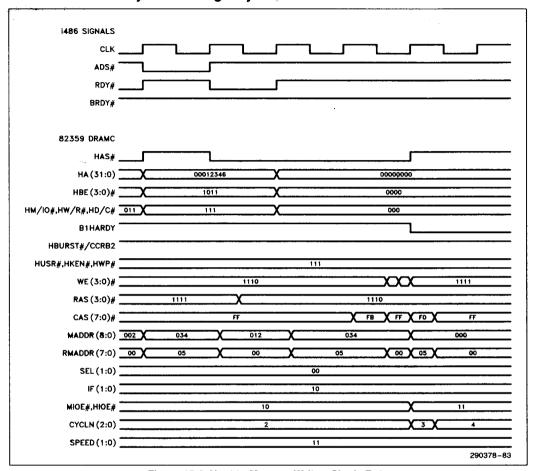

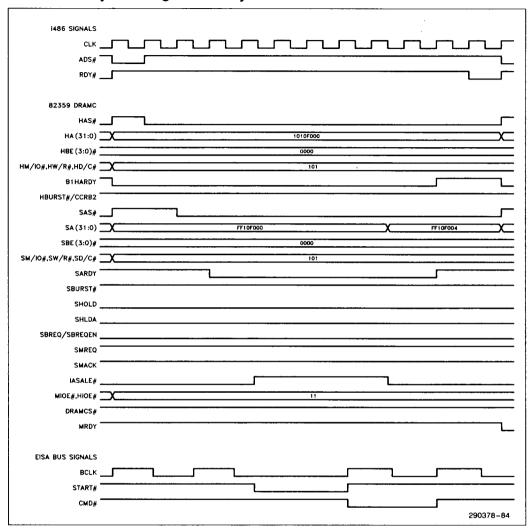

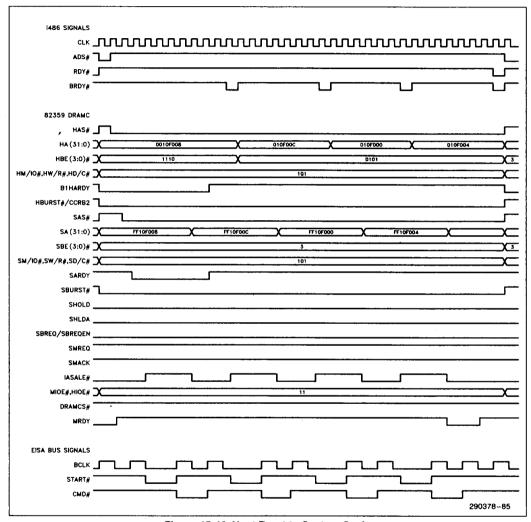

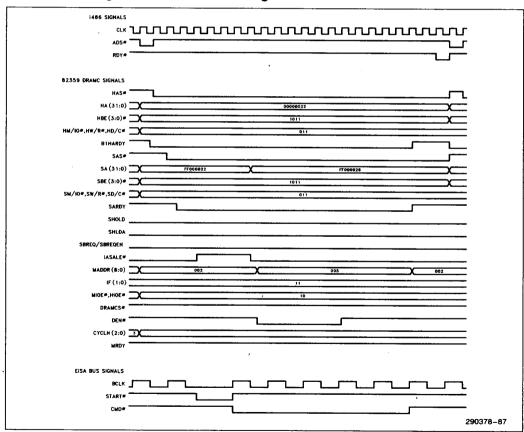

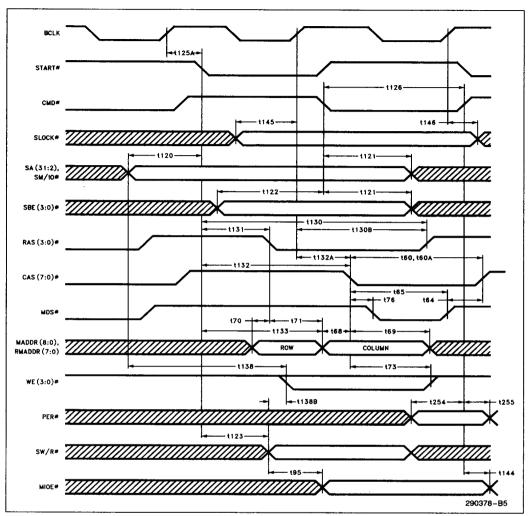

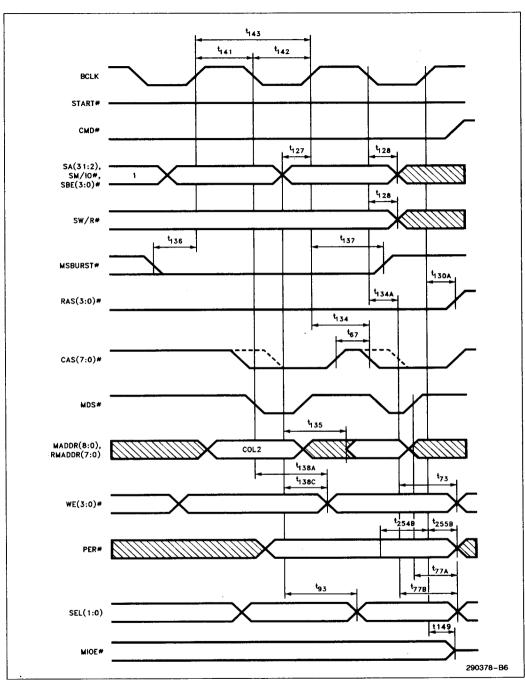

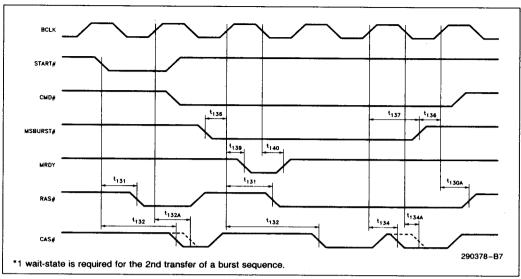

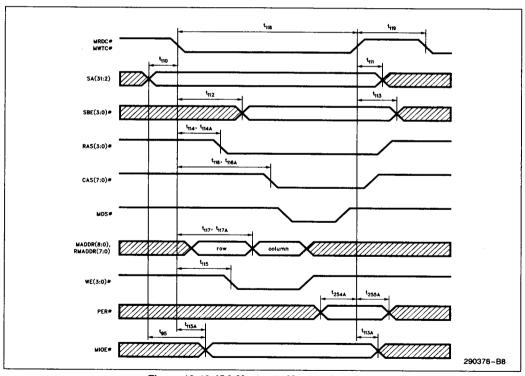

| 15.0 FUNCTIONAL TIMING DIAGRAMS  15.1 Host to Memory Read—Page Hit                                                                                                     |                               | 16.0 ELECTRICAL CHARACTERISTICS 16.1 Absolute Maximums                                                         | 1-657                         |

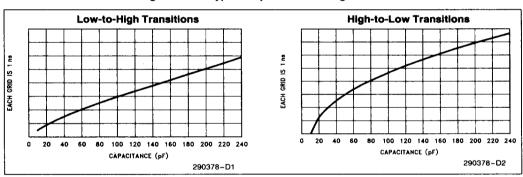

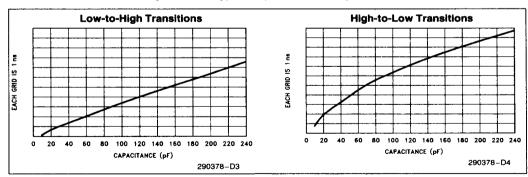

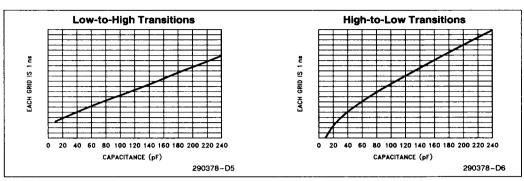

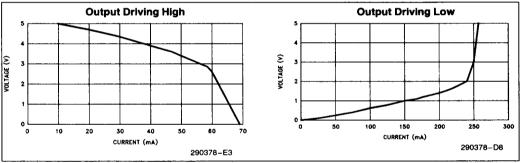

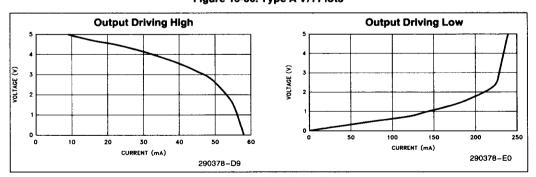

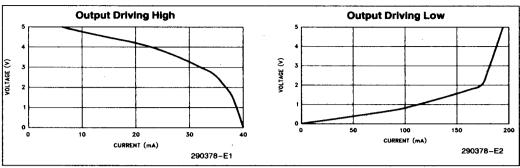

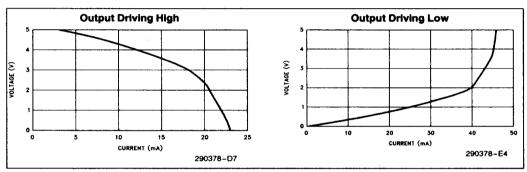

| 15.2 Host to Memory Read—Page Miss 15.3 Host to Memory Read—Row Miss 15.4 Host to Memory Burst Read (1-Way Interleave)                                                 | 1-644                         | 16.2 D.C. Specifications 16.3 A.C. Specifications 16.4 Driver Characterization  17.0 MECHANICAL SPECIFICATIONS | 1-658<br>Data 1-682           |

| 15.5 Host to Memory Burst Read (2-Way Interleave)  15.6 Host to Memory Burst Read (4-Way Interleave)  15.7 Host to Memory Write  15.8 Host to Memory Write—Single Byte | 1-647<br>1-648<br>1-649       | 18.0 THERMAL SPECIFICATION 19.0 NUMERICAL PIN LISTING 20.0 ALPHABETICAL PIN LISTING 21.0 PINOUT DIAGRAM        | 1-687  TING 1-688 1-689 1-690 |

| 15.9 Host to System Single Dword Cycle  15.10 Host Burst to System Cycle  15.11 Accessing the 82359's Interna Registers  15.12 Snoop Cycle  15.13 Snoop Filter Example | 1-652<br>Il<br>1-653<br>1-655 | General Register List  LIM Registers  APPENDIX B  Memory Sizing Algorithm  Revision Summary                    |                               |

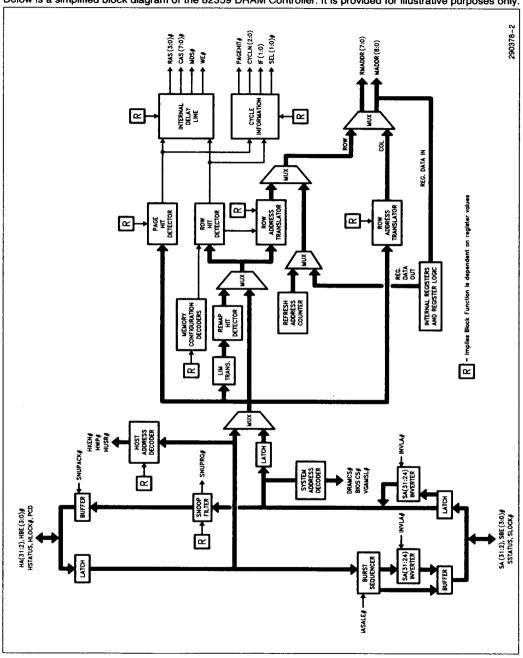

### 82359 BLOCK DIAGRAM

Below is a simplified block diagram of the 82359 DRAM Controller. It is provided for illustrative purposes only.

1-525

#### 1.0 INTRODUCTION

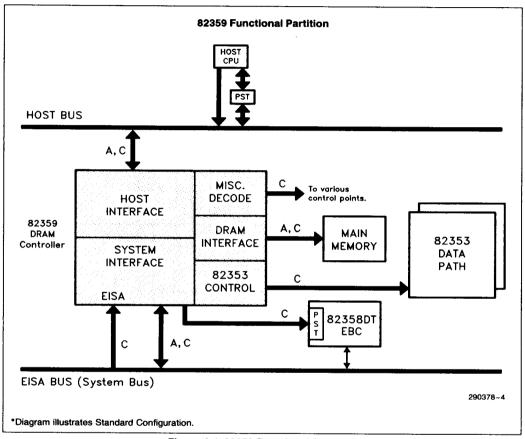

The 82359 DRAM Controller is a highly integrated EISA DRAM memory controller based on a dual ported memory architecture. It provides address and control signals for DRAM based main memory and it works very closely with two 82353 Advanced Data Path devices.

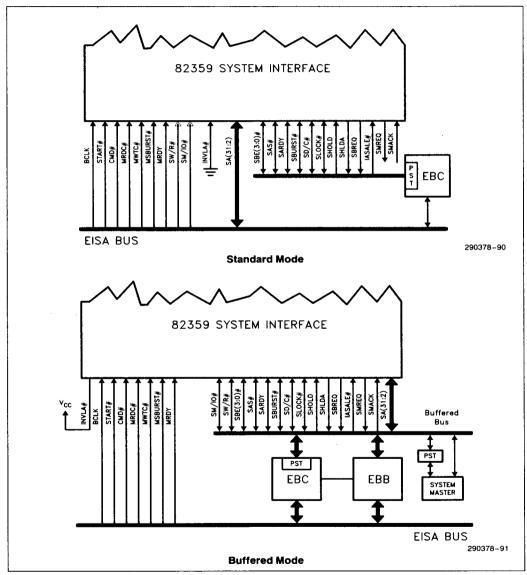

The 82359 may operate in one of two modes: (1) Standard Mode in which the 82359 connects directly to the EISA address bus; and (2) Buffered Mode, in which a new bus exists between the 82359 and the EISA bus and functions similar to the host bus. In this mode, the EISA bus is "buffered" from the 82359. For a full discussion of Buffered and Standard Mode, see the "82350DT System Architecture Overview" document.

The 82359 has two ports, or address gateways, to main memory; one exclusively for the host and one exclusively for EISA. This allows CPU activity to be isolated from EISA bus activity, allowing the host to run out of main memory at the same time system bus (EISA) activity is occurring. This dual ported architecture provides four routes which a cycle may follow: (1) Host to main memory; (2) Host to system slave; (3) System master to main memory and; (4) System address to host cache (for cache line invalidation).

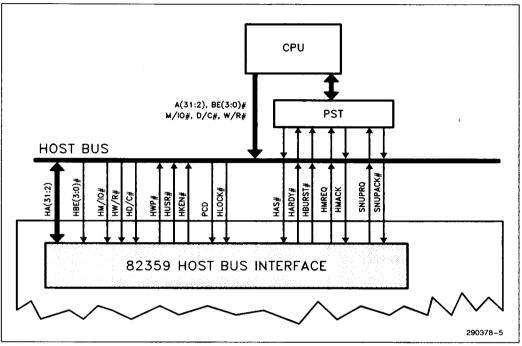

One port, labeled "Host Port", provides a one-way path for host cycles to DRAM memory or to the system bus. It is capable of accepting a 32-bit host address and host cycle definition. From the address and cycle definition, the 82359 determines if the cycle is bound for main memory, in which case the 82359 executes a DRAM cycle, or if not to main memory, the 82359 forwards the cycle to the system bus. Although the host port is considered one-way in direction in that it is only capable of receiving host originated cycles, it does drive the host address lines when forwarding cache invalidation addresses to the host cache (if one exists).

The second port, labeled "System Port", acts as the gateway to/from the system bus. Unlike the host port, the system port is bi-directional, capable of sending as well as receiving 32-bit addresses and system bus cycle definitions. The system port accepts system bus cycles and, if the cycle is to an address contained in main memory, it executes the DRAM cycle. If the address of the system cycle is not contained in main memory, no action is taken by the 82359.

Since the 82359 was designed to support an EISA based expansion bus, it closely communicates with the 82358DT EISA Bus Controller (EBC). All host-to-system cycles are sent through the 82359 to the EBC for correct EISA/ISA cycle generation. All EISA bus activity is directly monitored and interpreted by the 82359, and the 82359 automatically acts upon EISA cycles to main memory without EISA protocol translation by the EBC.

The 82359 does not follow the typical ADS# and READY# protocol of the microprocessor. Instead, it uses a clockless protocol on both the host and system ports which isolates the CPU clock from the DRAM controller. This allows the 82359 to become CPU frequency independent.

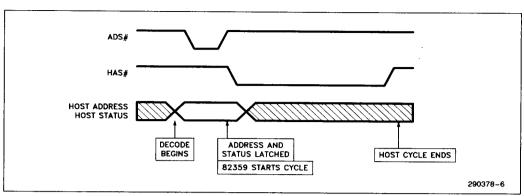

A typical design would take the cycle definition (M/IO#, W/R#, D/C#) and ADS# of the CPU and interpret these to communicate with the 82359, telling it to start a cycle and what type of cycle is required. The 82359 decodes the address presented with the start of the cycle and returns a 3-bit code for the cycle length. From this cycle length, the protocol converter knows when to return READY# to the CPU.

The 82359 contains many programmable registers which control functions such as memory block enable/remap/shadow, DRAM timing generation, memory array population, and memory cycle length to name a few. These registers are typically programmed by the BIOS at power-up. It is through these registers that the 82359 achieves its flexibility.

Four registers are provided for memory array population information. The BIOS typically tests memory at power-up and provides DRAM SIMM size and population information to the 82359.

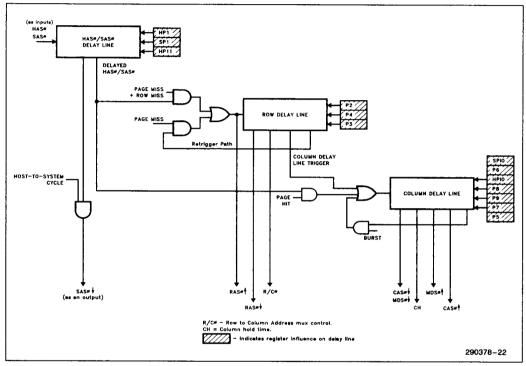

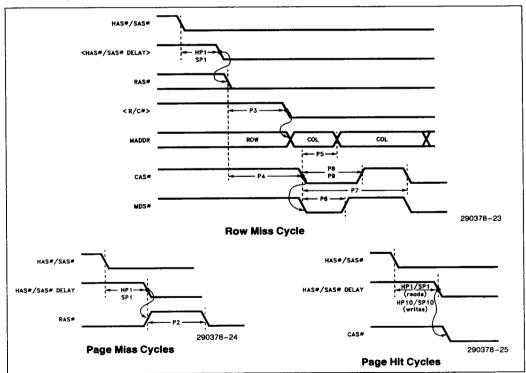

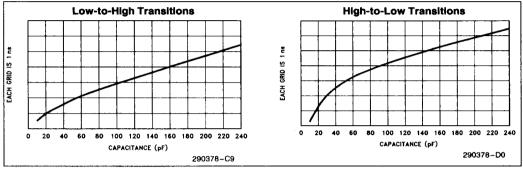

DRAM access times of 60, 70, or 80 ns are supported by the 82359. To facilitate the critical timings specific to each speed of the DRAM, the 82359 has programmable registers which access an internal delay line. Through these programmable timing registers, DRAM parameters such as RAS# precharge, RAS# to CAS# delay, etc. can be tailored to the DRAM's required times with 2.61 ns resolution.

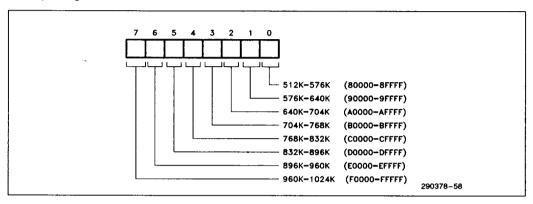

Portions of the memory array may be individually disabled, remapped, write-only or read-only under program-mable register control. Through the use of these registers, BIOS may be shadowed to DRAM. Also the memory map may be configured to "jump over" areas which contain other system functions (such as video, BIOS, etc.) by disabling portions of DRAM in 16k increments. Memory in the 512k-1M range may be disabled and remapped to the top of main memory in 64k blocks.

The 82359 provides four Programmable Attribute Map (PAM) registers to be used in systems which utilize caches on the host bus. Three bits of attribute are provided for each range: (1) Cache Enable, (2) Write Protect, and (3) a User-Defined bit. These registers allow software to determine the attributes for a programmable range size at a programmable starting address.

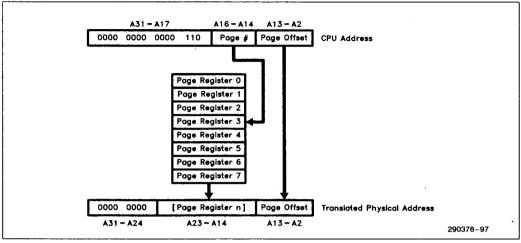

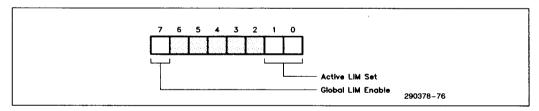

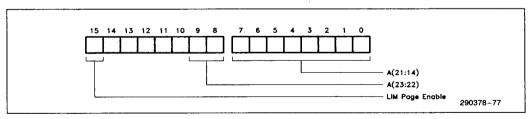

Eight LIM registers are provided for those systems which take advantage of the Lotus/Intel/Microsoft convention for expanded memory. These registers may be programmed to swap 16k pages of memory from anywhere in the lower 16M address range into and out of DOS accessibility.

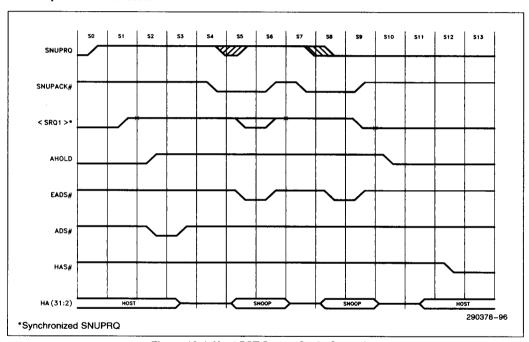

The 82359 is designed to support write-through caches on the host bus. System write cycles are sent to the host cache as snoop cycles. Also, the 82359 performs "Snoop Filtering" which eliminates needless snoop cycles. Should a system write cycle occur to a location contained in the cache line which the 82359 invalidated by the previous snoop cycle, the 82359 will not broadcast the second, redundant snoop to the host. By eliminating redundant snoops, the host bus has increased bandwidth.

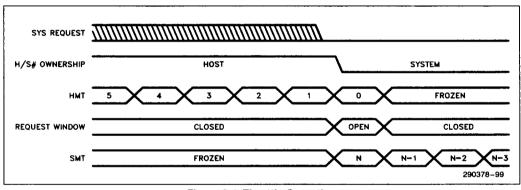

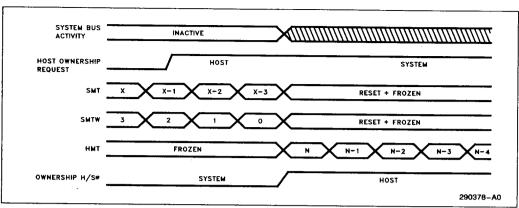

As EISA masters become more and more abundant, main memory accessibility becomes an increasingly important factor. With many EISA master devices installed in a system, the portion of memory bandwidth available to the CPU decreases significantly. To eliminate inefficient allocation of memory bandwidth, the 82359 has internal throttles which can be programmed to hold off memory ownership requests for a determined period of time so that others who desperately require memory bandwidth can have a greater time-slice than EISA arbitration allows. The net effect of these throttles allows the main memory ownership resource to be allocated for best system performance.

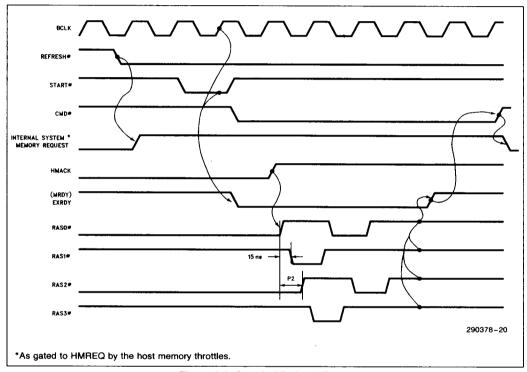

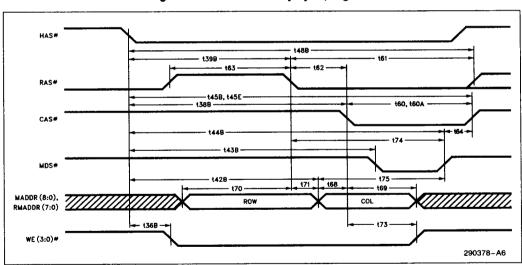

The 82359 provides two modes of DRAM refresh generation: (1) Coupled Refresh, in which the refresh timing is provided by the EISA bus, and (2) Decoupled Refresh, in which the 82359 refreshes main memory by generating the refresh request and address internally.

To facilitate the CPU frequency independence of the 82359, a new host bus protocol was devised. This protocol does not follow the synchronous ADS# and RDY# of the processor. Instead, it is asynchronous in nature in that it has no clock. This protocol is implemented by an external Programmable State Tracker (or PST) which converts the CPU's ADS# and RDY# protocol to the asynchronous protocol used by the 82359. This PST can typically be implemented in a two or three PLD solution.

Although the protocol is asynchronous, it does not detriment CPU to memory performance like other asynchronous protocols. This is achieved by the unique implementation of the protocol. The protocol defines two types of cycles; (1) the Deterministic Cycle, and; (2) the Non-deterministic Cycle. Deterministic cycles are cycles to main memory. The exact length of these cycles is known by the 82359 at the beginning of the cycle since it is aware of exactly how long that cycle to memory (page hit, page miss) will require for completion. The 82359 immediately relays that information to the host PST via a "DRAM Page Hit" indicator and a 3-bit code containing wait state information. From this, the host PST knows exactly when to send the RDY# to the CPU. Thus the RDY# is returned at the exact moment the memory cycle finishes and no synchronization penalty is incurred.

Non-deterministic cycles are host cycles to system bus slaves or locked cycles. Before these cycles can complete, the host must gain ownership of the system bus and thus, arbitration may be required. Since the 82359 does not know exactly how long the host must wait before gaining system bus ownership, or exactly how long the host-to-system cycle will require to complete (due various speeds of system slaves), the 82359 can not return an exact cycle length to the host CPU. Instead, an asynchronous signal is used to indicate the completion of the host- to-system cycle. In this case, a one CPU clock synchronization penalty is paid when returning RDY #. It is important to note that host-to-system cycles are the only cycles which pay this synchronization penalty and that the more important host-to-main memory cycles pay no synchronization penalty what-soever.

### 2.0 PIN DESCRIPTION QUICK-REFERENCE

The following is a brief description of the interface pins of the 82359. For a more complete explanation of each pin, refer to the section entitled Detailed Pin Description.

| Symbol                   | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOST PORT                | INTERF | ACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

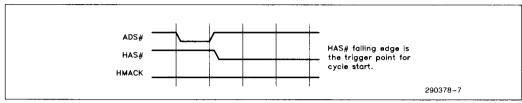

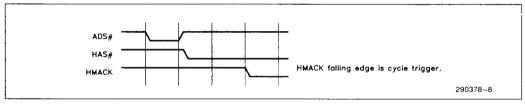

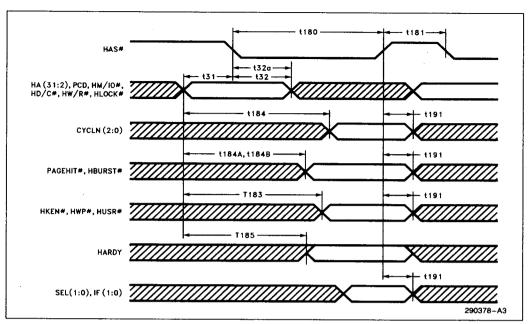

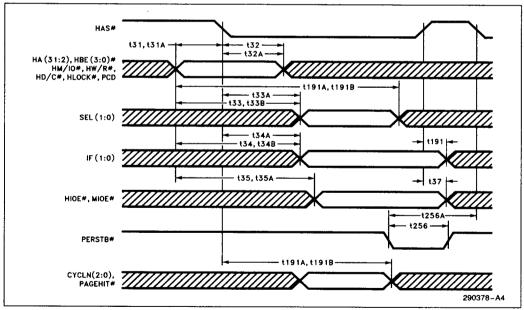

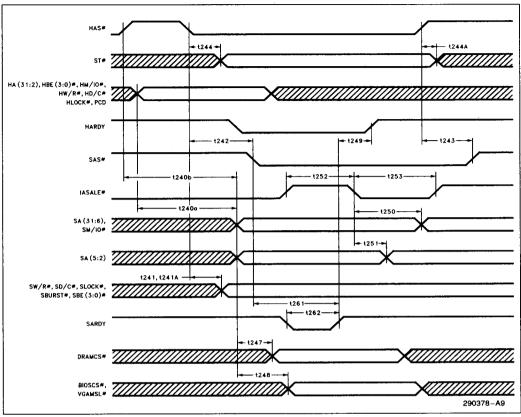

| HAS#                     | 1      | HOST ADDRESS STROBE: The falling edge of HAS# is the host cycle start indicator to the 82359 and causes the 82359 to latch HA(31:2), HBE(3:0)#, HM/IO#, HW/R#, HD/C#, HLOCK#, and PCD. HAS# rising edge indicates the end of the current host cycle and re-opens the latch.                                                                                                                                                                                                               |

| HA(31:2)                 | 1/0    | HOST ADDRESS: The HA(31:2) signals provide the 82359 with its 30-bit host address. These address signals are inputs for host cycles and outputs when the 82359 drives snoop addresses to the host cache.                                                                                                                                                                                                                                                                                  |

| HBE(3:0)#                | 1      | <b>HOST BYTE ENABLES:</b> Byte enable input bits indicate active bytes during host cycles.                                                                                                                                                                                                                                                                                                                                                                                                |

| HM/IO#<br>HW/R#<br>HD/C# |        | <b>HOST BUS DEFINITION:</b> HM/IO#, HW/R#, and HD/C# comprise the host cycle definition and are inputs to the 82359 from the host bus. These three signals define the current host bus cycle type.                                                                                                                                                                                                                                                                                        |

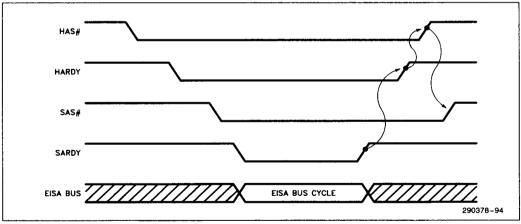

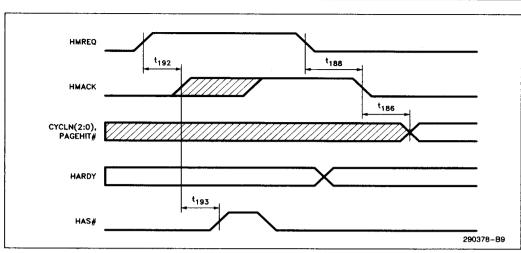

| HARDY                    | 0      | HOST ASYNCHRONOUS READY: HARDY is an asynchronous ready indicator from the 82359 to the host PST driven off of a decode of the host address and status. During non-deterministic cycles, the 82359 de-asserts HARDY indicating a "not ready" condition to the host PST. HARDY is used only for host-to-system cycles and locked host cycles.                                                                                                                                              |

| HMREQ                    | 0      | HOST MEMORY REQUEST: HMREQ is asserted by the 82359 to the host PST to indicate the 82359 would like ownership of main memory. The 82359 requests ownership of main memory on behalf of Refresh or a system master.                                                                                                                                                                                                                                                                       |

| HMACK                    | 1      | HOST MEMORY ACKNOWLEDGE: HMACK is an input from the host PST in response to a 82359 request of memory ownership (HMREQ). HMACK asserted indicates that the HMREQ has been honored and that the 82359 has memory ownership.                                                                                                                                                                                                                                                                |

| HBURST#/<br>CCRB2        | 0      | HOST BURST/CCRB2: The HBURST #/CCRB2 is an output of the 82359 and may take on one of two functions. As HBURST, the pin functions as a decode of the host address and cycle definition to indicate to the host PST that the memory address being accessed is capable of a burst transfer. As CCRB2, this pin is a direct reflection of Cache Control Register, bit2. The HBURST #/CCRB2 pin's functionality is determined by the setting of the PCDOVERRIDE bit (Mode Register B, bit 1). |

| PCD                      | l      | <b>PAGE CACHE DISABLE:</b> PCD is an input from the host to the 82359, typically driven from the i486 PCD output. The PCD input is used by the 82359 in determining the cacheability of addresses.                                                                                                                                                                                                                                                                                        |

| HLOCK#                   | I      | HOST LOCK: The HLOCK # pin indicates that the current bus cycle is a locked cycle. When the current cycle is locked, the system bus will be arbitrated for and system bus ownership obtained before the 82359 runs the host cycle, irrespective of the destination of that cycle. System bus ownership will remain in the host's possession until the complete lock sequence is done. Locked cycles are always run as non-deterministic cycles.                                           |

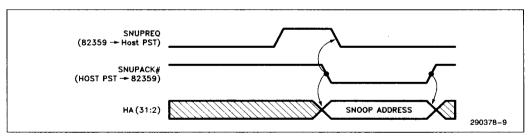

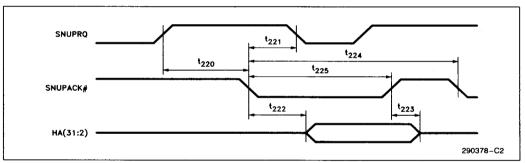

| SNUPRQ                   | 0      | SNOOP REQUEST: The 82359 asserts this signal to the host interface when it has a pending cache invalidation cycle. The 82359 de-asserts SNUPRQ from the falling edge of SNUPACK#.                                                                                                                                                                                                                                                                                                         |

| SNUPACK#                 |        | SNOOP ACKNOWLEDGE: SNUPACK# is an input from the host PST to acknowledge the 82359's request to run a snoop cycle. The 82359 de-asserts it SNUPRQ from the falling edge of SNUPACK# and the snoop address is driven onto the host bus while SNUPACK# is asserted.                                                                                                                                                                                                                         |

| Symbol                 | Туре    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOST POR               | T INTER | RFACE (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

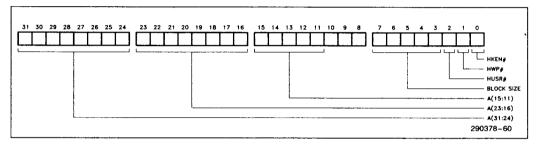

| HUSR#<br>HWP#<br>HKEN# | 0       | HOST PROGRAMMABLE ATTRIBUTES: HUSR#, HWP# and HKEN# are three programmable attribute bits available through the PAM registers. The attribute bits will reflect the setting of one of the Programmable Attribute Map registers if the host address falls within one of the registers programmed address ranges.                                                                                                                                                                                                                                                                                                                                               |

| ST#                    | 1       | START (Continue) HOST CYCLE: If ST# is sampled inactive after a DRAM cycle has started, the cycle will be aborted. ST# is typically used by parallel caches to terminate the DRAM cycle if a cache hit is detected. Another way to look at the ST# signal is to consider it a "continue" signal, causing the 82359 to continue its current cycle as long as ST# remains asserted.                                                                                                                                                                                                                                                                            |

|                        |         | NOTE:  The ST# signals should be used to abort DRAM cycles only when the HP1 register (offset 10h) is programmed to a value of 0 through 4 (inclusive).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SYSTEM P               | ORT INT | ERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

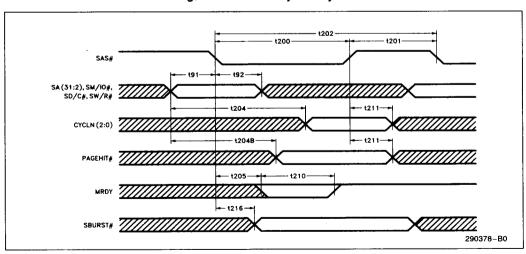

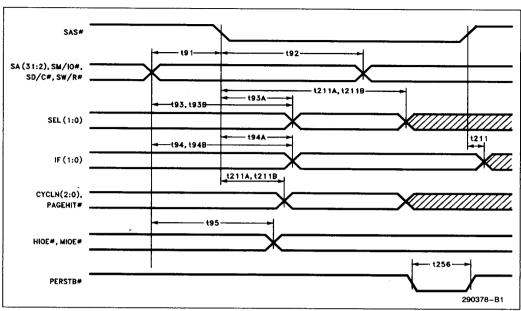

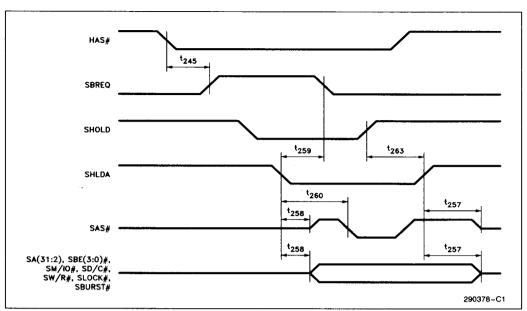

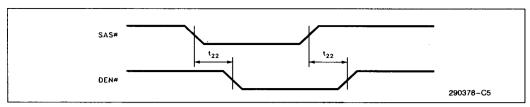

| SAS#                   | 1/0     | SYSTEM ADDRESS STROBE: SAS # indicates the beginning of an 82359 system-side cycle. SAS # becomes an output when the host is sending a cycle through the 82359 to the system bus. SAS # becomes an input when the host does not own the system bus. The falling edge of SAS # transparently latches SA(31:2), SBE(3:0) #, SD/C#, SW/R#, SM/IO#, and SLOCK#.                                                                                                                                                                                                                                                                                                  |

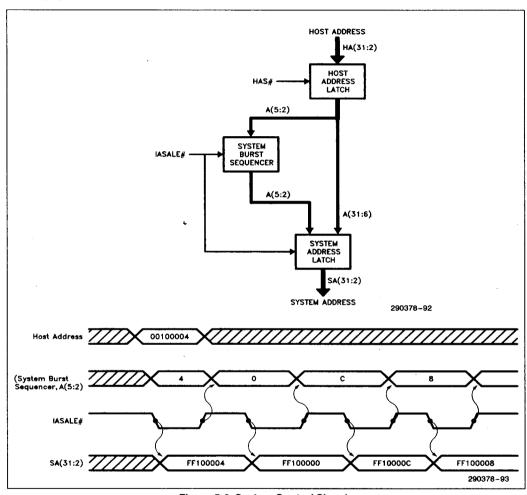

| IASALE#                | 1       | <b>INTERNAL ADDRESS TO SYSTEM ADDRESS LATCH ENABLE:</b> IASALE # controls the latching of host addresses which need to be driven to the system bus. It is an input typically driven by the EISA Bus Controller. IASALE # asserted causes the system address latch to become transparent and the address held in the host address latch will be driven to the system address lines. The rising edge of IASALE # closes the system address latch. During host-to-system burst cycles, the first rising edge of IASALE # causes the lead-off address to be latched and subsequent rising edges increment the system burst order counter which controls SA(5:2). |

| SHOLD                  | 1       | SYSTEM HOLD: SHOLD is an input to the 82359 which indicates that a system master or DMA is requesting ownership of the system bus. The 82359 will respond with a SHLDA when the 82359 has given ownership of the system bus to the requesting master.                                                                                                                                                                                                                                                                                                                                                                                                        |

| SHLDA                  | 0       | SYSTEM HOLD ACKNOWLEDGE: SHLDA is an output from the 82359 acknowledging the SHOLD from the system and indicates that the 82359 has given-up the ownership of system bus. SHLDA will remain asserted as long as SHOLD remains asserted. When the 82359 asserts SHLDA, all 82359 system address and control signals will be tri-stated.                                                                                                                                                                                                                                                                                                                       |

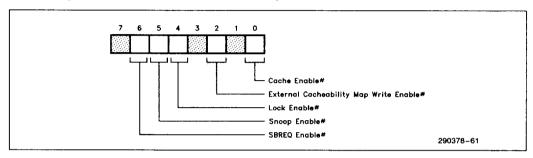

| SBREQ/<br>SBREQEN      | 0       | SYSTEM BUS REQ/SYSTEM BUS REQ ENABLE: The generation of SBREQ is dependent on EISA Cache Control Register, bit 6, and Mode Register B, bit 2. As SBREQEN, the function of this pin is a direct reflection of the EISA Cache Control Register, bit 6. As SBREQ, the function of this pin is to generate a request to the system arbiter on behalf of the host to get ownership of the system bus so as to run host-to-system cycles.                                                                                                                                                                                                                          |

| SARDY                  | 1       | SYSTEM ASYNCHRONOUS READY: SARDY is an input to the 82359 used to indicate a "not ready" condition of the system slaves when the 82359 is propagating host cycles to the system bus. The rising edge of SARDY indicates the end of the system cycle.                                                                                                                                                                                                                                                                                                                                                                                                         |

| Symbol                   | Туре                              | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|--------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SYSTEM PO                | SYSTEM PORT INTERFACE (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| SBURST#                  | 1/0                               | SYSTEM BURST INDICATOR: SBURST # is an input when system PST masters are running cycles. If SBURST # is asserted during system PST master cycles, the 82359 will run the appropriate number of memory cycles to satisfy the system line size. If SBURST # is not asserted, 82359 will run one and only one memory cycle. SBURST # becomes an output when the host is running bus cycles to the system bus and indicates to the system bus controller that the host would like to run multiple system bus cycles to satisfy the host burst.                                            |  |  |  |  |  |

| SW/R#<br>SM/IO#<br>SD/C# | 1/0                               | SYSTEM CYCLE DEFINITION: SD/C#, SM/IO#, and SW/R# are bi-directional system cycle definition signals and are defined the same as their host counterparts. These pins are inputs when the a system master owns the system bus. These signals become outputs when a host cycle is being forwarded to the system bus.                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| SBE(3:0)#                | 1/0                               | SYSTEM BYTE ENABLES: SBE(3:0) # are the byte enables for each one of the four bytes in the dword. The SBE #'s become outputs when host cycles are run to the system bus and are a reflection of the host port HBE #'s. When a system master owns the system bus, the SBE #'s become inputs receiving the BE #'s from the system cycle.                                                                                                                                                                                                                                                |  |  |  |  |  |

| SA(31:2)                 | 1/0                               | SYSTEM ADDRESS: The SA lines provide a 30-bit address port into/out of the 82359. They become outputs for host-to-system cycles and provide the cycle address to the 30-bit system address bus. SA(5:2) are also controlled by the internal system burst sequencer and provide the correct address for host burst to system cycles. The SA lines become inputs whenever a system master owns the system bus. The system address will be latched on the falling edge of SAS# for system PST masters or START#, IORC#, or IOWC# (delayed internally by 30 ns) for EISA/ISA bus masters. |  |  |  |  |  |

| SLOCK#                   | 1/0                               | SYSTEM LOCK CYCLE INDICATOR: SLOCK# is an input to the 82359 when a system master owns the system bus and indicates that the master is running a locked cycle. SLOCK# is an output when the host owns the system bus. The assertion of SLOCK# during a system master cycle causes all throttles to be overridden.                                                                                                                                                                                                                                                                     |  |  |  |  |  |

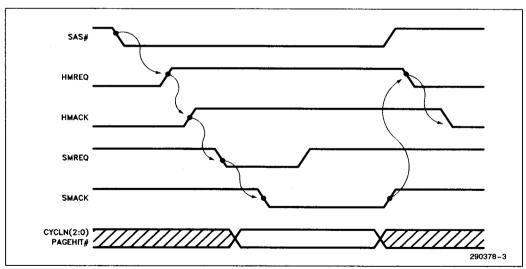

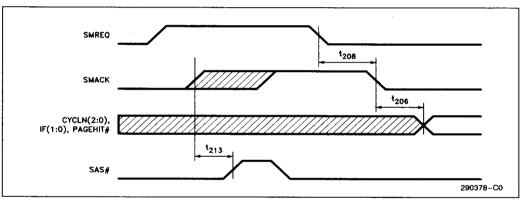

| SMREQ                    | 0                                 | SYSTEM MEMORY REQUEST: The 82359 will assert SMREQ to system PSTs when it or the host wants to own memory. The 82359 will immediately assert SMREQ whenever the system does not request memory ownership (i.e., the default state of SMREQ is asserted). SMREQ is not typically used in Standard Mode.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| SMACK                    | 1                                 | SYSTEM MEMORY ACKNOWLEDGE: SMACK is controlled by the system PST and when asserted indicates that the system PST has released memory ownership to the 82359. When SMACK becomes de-asserted, the system PST master has memory ownership. SMACK should be pulled high in Standard Mode.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| INVLA#                   | 1                                 | INVERTED LA ADDRESS LINES: This is a strap which indicates to the 82359 to treat the most significant byte of the system address, SA(31:24), as inverted. If INVLA # is tied low, all SA(31:24) address bits are inverted before being driven or read from the system bus. If this strap is high, SA(31:24) are treated as non-inverted.                                                                                                                                                                                                                                              |  |  |  |  |  |

| BCLK                     | ı                                 | EISA BUS CLOCK: BCLK provides the 82359 with a reference for sampling EISA specific signals. Since the EISA bus is synchronous to BCLK, the 82359 samples EISA events synchronous to BCLK edges without regard to frequency or duty cycle.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| START#                   |                                   | EISA START # SIGNAL: START # indicates the start of an EISA cycle. A bus master asserts START # after SA(31:2) and SM/IO # become valid, and negates START # on a rising edge of BCLK after one BCLK period.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

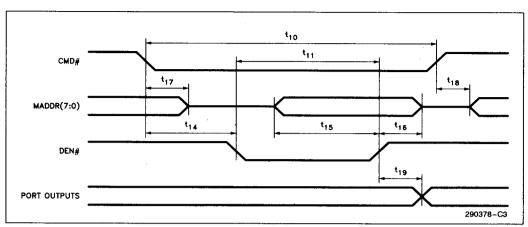

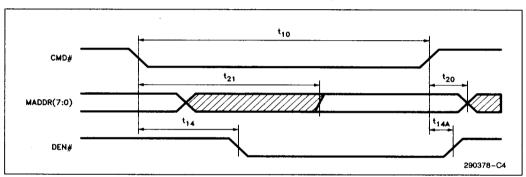

| CMD#                     | 1                                 | EISA CMD# SIGNAL: This input is the EISA CMD# signal monitored by the 82359 in directly tracking EISA master cycles. CMD# controls the bus data timings and its rising edge signals the end of the current EISA cycle.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Symbol       | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM PORT  | INTER  | FACE (Continued)                                                                                                                                                                                                                                                                                                                                                                             |

| MRDC#        | l      | MEMORY READ COMMAND: MRDC# is an ISA signal monitored by the 82359 in Non-concurrent Mode. It indicates to the 82359 that an ISA master wants to run a cycle. In Concurrent Mode, this signal is a "don't care" since only EISA signals are monitored.                                                                                                                                       |

| MWTC#        | ŀ      | MEMORY WRITE COMMAND: MWTC# is an ISA signal monitored by the 82359 in Non-concurrent Mode. The ISA master will assert MWTC# to indicate that the slave may latch the data bus. This is a "don't care" for Concurrent mode, since the 82359 monitors only EISA signals.                                                                                                                      |

| MSBURST#     | ı      | EISA BURST CYCLE INDICATOR: MSBURST# is the EISA burst cycle indicator monitored by the 82359. When the 82359 samples MSBURST# asserted, the 82359's EISA burst state machine is activated and all subsequent memory cycles are run as page hits.                                                                                                                                            |

| MEMORY INTE  | RFACE  | SIGNALS                                                                                                                                                                                                                                                                                                                                                                                      |

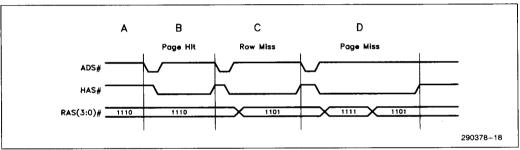

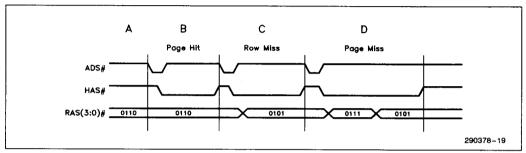

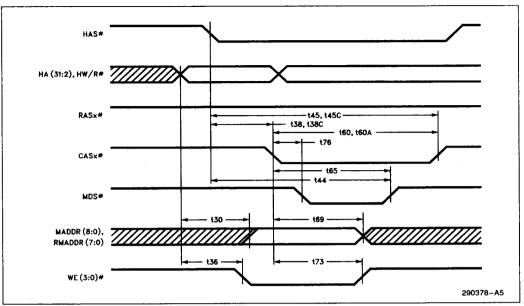

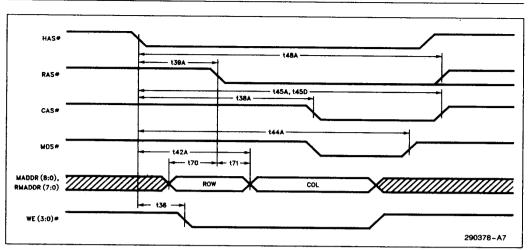

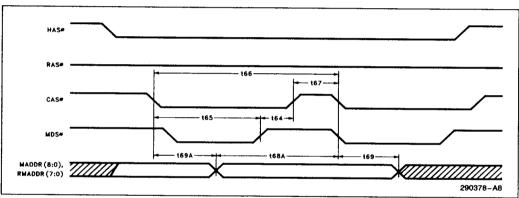

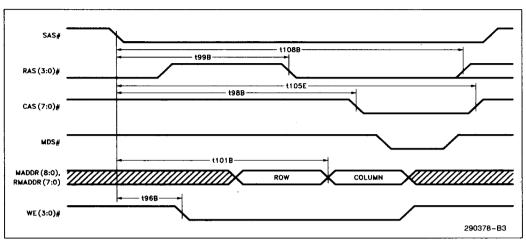

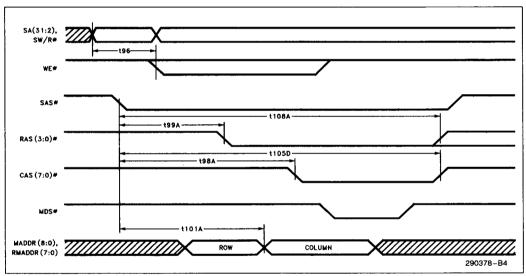

| RAS(3:0)#    | 0      | ROW ADDRESS STROBE: The 82359 provides four RAS# signals for the DRAM array, one per row. RAS0#, RAS1#, RAS2# and RAS3# are connected to row 0, 1, 2 and 3 of the memory array respectively. The assertion of RAS# signals is dependent on memory array population and mode of operation.                                                                                                    |

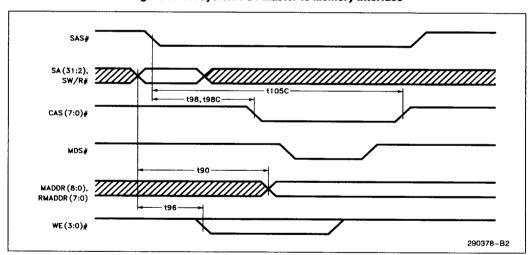

| CAS(7:0)#    | 0      | COLUMN ADDRESS STROBE: The 82359 provides eight CAS # signals for the DRAM array. These eight CAS lines are broken-up into two groups of four; CAS(3:0) # for row1 and row2 to share, CAS(7:4) # for row 2 and row 3 to share. The CAS # signals are "byte based" meaning that CAS0 # is connected to byte 0 of all eight dwords in the two rows, CAS1 # to byte 1 of all eight dwords, etc. |

| WE(3:0)#     | 0      | <b>MEMORY WRITE ENABLES:</b> The WE# signals select one of four dwords within a row during write operations and remain de-asserted for read operations. The WE#'s are also used for 82353 output enables for driving data to the DRAMs during memory writes.                                                                                                                                 |

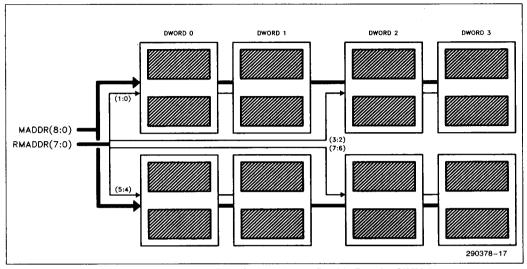

| MADDR(8:0)   | 1/0    | MEMORY ADDRESS: The MADDR(8:0) are the nine address bits common to all rows of the memory array. Typically these address lines are outputs, providing row and column address information to the DRAM array. As a second function, eight of these bits, MADDR(7:0), become the slave port used in programming the 82359's internal registers.                                                 |

| RMADDR(7:0)  | 0      | ROW SPECIFIC MEMORY ADDRESS: RMADDR(7:0) are row-specific DRAM address bits. In addition to the common memory address line of MADDR(8:0), the 82359 provides a second group of row-specific memory address lines. These eight bits are broken into four groups of two and each group connects to the corresponding row of the memory array, giving each row eleven total address bits.       |

| 82353 DATA P | ATH IN | TERFACE SIGNALS                                                                                                                                                                                                                                                                                                                                                                              |

| H/S#         | 0      | HOST/SYSTEM SELECT: The H/S# output indicates which port currently has ownership of main memory. H/S# is driven by the 82359 to the 82353 Data Path for data routing and control.                                                                                                                                                                                                            |

| SEL(1:0)     | 0      | SELECT SIGNALS: The SEL(1:0) determine which one of the four possible dwords latched into the 82353 is requested by the current cycle. Should the cycle be a burst, SEL(1:0) points to the lead-off dword and the remaining sequence of dwords is known by the 82353 (since the i486 burst sequence is fixed, it can be determined by the lead-off address).                                 |

| MDS#         | 0      | MEMORY DATA STROBE: The 82359 generates MDS# to control data latching in the 82353 Data Path. During memory read cycles, MDS# falls with CAS# and after a precise delay (controlled by an internal delay line in the 82359), goes high causing the memory data to be latched into the 82353.                                                                                                 |

| Symbol     | Туре    | Name and Function                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                 |                        |                                       |                                           |  |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------|-------------------------------------------|--|

| 82353 DATA | PATH II | NTERFACE SIGNALS (Cor                                                                                                                                                                                                                                                                                                                                             | ntinued)                                                                                                                                                                                                                                        |                        |                                       |                                           |  |

| HIOE#      | 0       | to configure the 82353 Da                                                                                                                                                                                                                                                                                                                                         | HOST INTERNAL OUTPUT ENABLE: The 82359 uses HIOE # (along with MIOE #) to configure the 82353 Data Path for the current cycle. HIOE # is asserted during host write cycles to enable the host data port to drive the internal bus of the 82353. |                        |                                       |                                           |  |

| MIOE#      | 0       | MEMORY INTERNAL OUTPUT ENABLE: The 82359 uses MIOE# (and HIOE#) to configure the 82353 Data Path for the current cycle. The 82359 will assert MIOE# and de-assert HIOE# when memory has been selected as the source of data (i.e., memory read cycles). The combination of MIOE# and HIOE# de-asserted causes the 82353's system port to drive its internal bus.  |                                                                                                                                                                                                                                                 |                        |                                       |                                           |  |

|            |         |                                                                                                                                                                                                                                                                                                                                                                   | HIOE#                                                                                                                                                                                                                                           | MIOE#                  | Data Source                           |                                           |  |

|            |         |                                                                                                                                                                                                                                                                                                                                                                   | 0<br>1<br>1                                                                                                                                                                                                                                     | X<br>0<br>1            | Host<br>Memory<br>System              |                                           |  |

| CHIP SELEC | TS AND  | OTHER SIGNALS                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                 |                        |                                       | <del></del>                               |  |

| IF(1:0)    | 0       | INTERLEAVE FACTOR: IF(1:0) reflect the dword interleave factor of the current row of the memory array being accessed by the 82359. The dword interleave factor is programmed into the configuration registers on a row basis when the system is booted (derived from a BIOS check of main memory).                                                                |                                                                                                                                                                                                                                                 |                        |                                       |                                           |  |

|            |         |                                                                                                                                                                                                                                                                                                                                                                   | IF(1:0) Dword Interleave Factor                                                                                                                                                                                                                 |                        |                                       |                                           |  |

|            |         |                                                                                                                                                                                                                                                                                                                                                                   | 00<br>01<br>10<br>11                                                                                                                                                                                                                            | Sys                    | 4-Way<br>2-Way<br>1-Way<br>stem Cycle |                                           |  |

| REFRESH#   | ı       | SYSTEM REFRESH: REF<br>a refresh cycle. If the 823<br>asserted causes the 8235<br>is programmed for Decou                                                                                                                                                                                                                                                         | 59 is prog<br>i9 to exec                                                                                                                                                                                                                        | rammed f<br>ute a refr | or Coupled Ref                        | resh, REFRESH#<br>in memory. If the 82359 |  |

| PER#       | ì       | PARITY ERROR: PER# i<br>82359 to generate PERST<br>ISA masters).                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                 |                        |                                       |                                           |  |

| PERSTB#    | 1/0     | PARITY STROBE: PERSTB# is the main memory parity error indication. It is an open-drain signal and will be driven by the 82359 when a parity error is generated by the 82353 Data Path during non-PST master (DMA, EISA, ISA masters) read cycles to main memory. Signaling of a parity error causes the contents of the Parity Error Trap Registers to be frozen. |                                                                                                                                                                                                                                                 |                        |                                       |                                           |  |

| MRDY       | 1/0     | MEMORY READY: MRDY<br>bus signal EXRDY. The 82<br>inserted in system cycles.<br>State Tracker portion of the                                                                                                                                                                                                                                                      | 2359 will<br>MRDY is                                                                                                                                                                                                                            | de-assert<br>monitore  | MRDÝ when wa                          | ait states need to be                     |  |

1

| Symbol     | Туре   | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIP SELEC | TS AND | OTHER SIGNALS (Continued)                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIOSCS#    | 0      | BIOS CHIP SELECT: BIOSCS# is an output from the 82359's system address decoder to indicate the BIOS ROM on the system bus is being accessed. BIOSCS# responds to both addresses 000E0000h to 000FFFFFh and FFFE0000h to FFFFFFFh.                                                                                                                                                                                                   |

| VGAMSL#    | 0      | VGA MEMORY SELECT: VGAMSL# is an output from the system address decoder to indicate the current system address resides in VGA memory space. VGA memory is that which resides within the address range 000A0000h to 000BFFFFh.                                                                                                                                                                                                       |

| DRAMCS#    | 0      | DRAM CHIP SELECT: DRAMCS# is an output from the 82359 by the system address decoder to indicate that the address on the SA(31:2) lines exists in main memory.                                                                                                                                                                                                                                                                       |

| LOCKEN#    | 0      | LOCK ENABLE: This is a static output that is a direct reflection of the Lock Enable bit (bit 4 of the Cache Control Register). This pin is used to enable or disable the LOCK # signal of the 386 from reaching the cache controller. This signal is not used in i486 systems.                                                                                                                                                      |

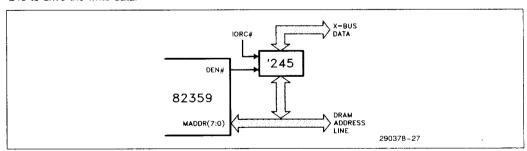

| DEN#       | 0      | DATA ENABLE: This pin is asserted in response to host-to-system cycles which program the 82359's internal registers and, if enabled by Mode Register A, bit 3, in response to a 486-initiated cache flush cycle. Specifically, DEN# is asserted during all host I/O write cycles to the Index and Data registers (typically 22h or 23h). When DEN# is driven by the 82359, the MADDR(7:0) bus carries 82359 internal register data. |

| SPEED(1:0) | 1/0    | <b>DRAM SPEED:</b> These are open drain pins accessible via the 82359's DRAM Speed Register. These bits can be used to reflect the binary code for the speed of DRAM in the memory array.                                                                                                                                                                                                                                           |

| CYCLN(2:0) | 0      | CYCLE LENGTH FEEDBACK: CYCLN(2:0) reflects a 3-bit code for the required number of wait states for the current host or system deterministic cycle. These bits are driven directly from the values programmed in the CYCLN registers.                                                                                                                                                                                                |

| PAGEHIT#   | 0      | PAGE HIT: This output is asserted by the 82359 when it detects that the current memory cycle has resulted in a DRAM page hit. This signal is available slightly before the CYCLN(2:0) signals and should be monitored by both host and system PSTs to indicated that the current cycle is the fastest memory cycle capable of occurring.                                                                                            |

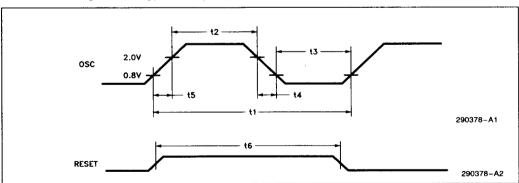

| OSC        | ı      | <b>REFERENCE FREQUENCY CLOCK:</b> This pin is driven by a 40 MHz, $50\% \pm 10\%$ duty cycle input used by the internal programmable delay line and for internal signal synchronization purposes.                                                                                                                                                                                                                                   |

| RESET      | 1      | <b>POWER-ON RESET:</b> RESET causes all programmable registers and state machines to be set to the initial state. This input should be activated only during the power-up sequence.                                                                                                                                                                                                                                                 |

| TEST#      | 1      | <b>TEST:</b> This pin is used for testing only and should be tied to V <sub>CC</sub> through a 10K resistor for normal 82359 operation.                                                                                                                                                                                                                                                                                             |

#### 3.0 REGISTER QUICK REFERENCE

\*Indicates the bit position is undefined. These bits should be programmed as logical 0. Also, these bits should be masked when reading the register as their logic state is not guaranteed.

Default values are shown in parenthesis.

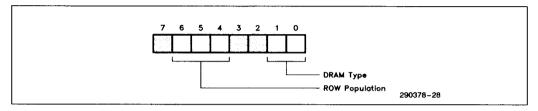

**ROWO CONFIGURATION REGISTER**

Offset:

00h

Default: Access: \*000\*\*01b

Bit Descriptions:

W/R

1:0

**DRAM Size**

(256k)

6:4

**Row Population**

(Dword 0)

**ROW1 CONFIGURATION REGISTER**

Offset:

01h

Default:

\*111\*\*01b W/R

Access:

Bit Descriptions:

1:0 6:4

**DRAM Size**

**Row Population**

(256k) (Empty)

**ROW2 CONFIGURATION REGISTER**

Offset:

02h \*111\*\*01b

Default: Access:

W/R

Bit Descriptions:

1:0

**DRAM Size**

6:4

**Row Population**

(256k) (Empty)

**ROW3 CONFIGURATION REGISTER**

Offset:

Default: Access: \*111\*\*01b W/R

Bit Descriptions:

1:0

**DRAM Size**

(256k)

6:4

**Row Population**

(Empty)

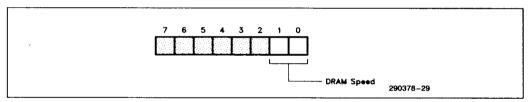

**DRAM SPEED REGISTER**

Offset:

Default:

\*\*\*\*\*\*11b

Access:

W/R

Bit Description:

1:0

DRAM Speed

(Slowest)

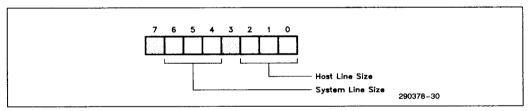

**LINE SIZE REGISTER**

Offset:

Default:

\*100\*100b W/R

Access

Bit Descriptions:

2:0

Host Line Size

(16 Bytes) (16 Bytes)

6:4

System Line Size

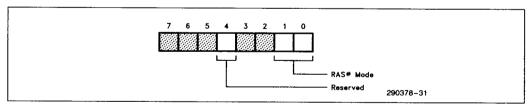

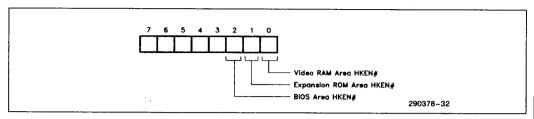

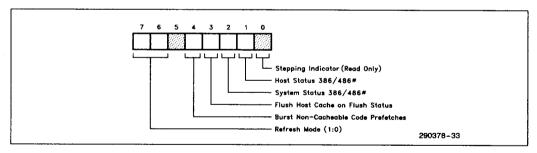

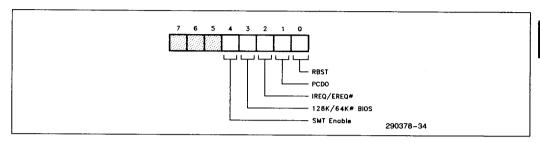

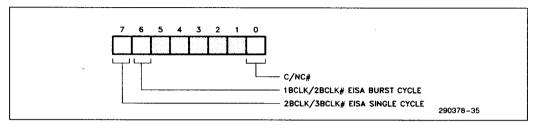

**RAS# MODE REGISTER** Offset: 0\*\*1\*\*01b Default: Access: W/R Bit Descriptions: 1:0 RAS# Mode (1 Active RAS # Mode) 4 Reserved (Must be "1") **BLOCK CACHE ENABLE REGISTER** Offset: N7h \*\*\*\*\*111b Default: Access: W/R Bit Descriptions: 0 Video RAM Area HKEN# (Non-cacheable) 1 Expansion ROM Area HKEN# (Non-cacheable) 2 BIOS Area HKEN# (Non-cacheable) **MODE REGISTER A** Offset: 08h Default: 00\*01000b Access: W/R Bit Descriptions: 0 Stepping Indicator (Read Only, A-2) 1 Host Status 386/486# (486)2 System Status 386/486# (486)3 Flush Host Cache on Flush Status (Enabled) 4 **Burst Non-Cacheable Code Prefetches** (Disabled) 7:6 Refresh Mode (1:0) (Coupled) MODE REGISTER B Offset: 09h Default: \*\*\*11101b Access: W/R Bit Descriptions: 0 **Restricted Burst** (Enabled-Restricted) 1 PCD Override (Disabled) 2 IREQ/EREQ# (Internal SBREQ) 3 128K/64K# BIOS (128K BIOS) 4 SMT Enable (SMT Enabled) MODE REGISTER C Offset: 0Ah 00\*\*\*\*\*0b Default: Access: W/R Bit Descriptions: 0 Concurrent/Non-Concurrent# (Non-Concurrent) 6 1BCLK/2BCLK# EISA BURST CYCLE (2 BCLK) 7 2BCLK/3BCLK# EISA SINGLE CYCLE (3 BCLK)

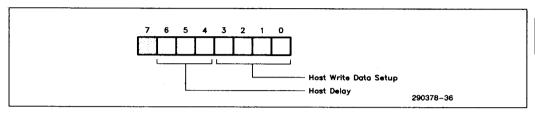

HOST TIMING REGISTER

Offset:

Default:

\*1101000b

Access:

W/R

Bit Descriptions:

3:0 6:4 HP10 HP1

(52.20 ns) (18.27 ns)

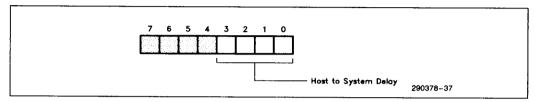

Offset:

11h

**HOST TO SYSTEM DELAY REGISTER**

Default: Access: \*\*\*\*1010b W/R

Bit Descriptions:

3:0

HP11

(67.86 ns)

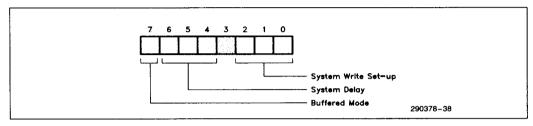

SYSTEM TIMING REGISTER

Offset:

Default:

0101\*101b

Access:

W/R

Bit Descriptions: 2:0

SP10 6:4

SP1

(20.88 ns) (20.88 ns)

7

**Buffered Mode**

(Standard Mode)

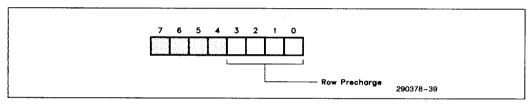

**ROW PRECHARGE TIMING REGISTER**

Offset:

13h

Default: Access: \*\*\*\*1110 W/R

Bit Description: 3:0

P2

(80.91 ns)

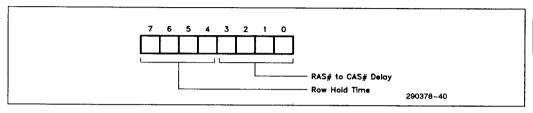

**ROW TIMING REGISTER**

Offset:

Default: Access: 01011000b

Bit Descriptions:

W/R

3:0

P4

РЗ

(83.52 ns)

7:4

(46.98 ns)

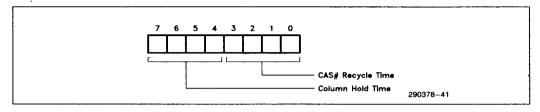

**COLUMN TIMING REGISTER**

Offset:

15h

Default:

01111100b W/R

Access: Bit Descriptions:

3:0

**P**7

(83.52 ns)

7:4

P5

(28.71 ns)

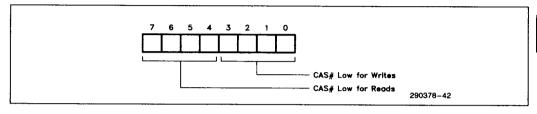

**CAS# LOW TIMING REGISTER**

Offset: 16h Default:

10000100b W/R

Access:

Bit Descriptions:

3:0 P9

7:4 Pβ (31.32 ns) (62.64 ns)

**CAS# TO MDS# DELAY REGISTER**

Offset:

Default: Access: \*\*\*01010b W/R

Bit Description:

3:0

P6

(57.42 ns)

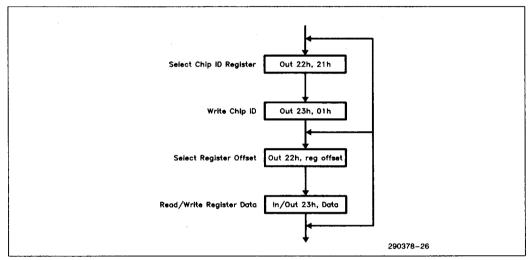

**CHIP IDENTIFICATION REGISTER (CIR)**

Offset:

21h

Default: Access: 11111111b W/R

Bit Description:

7:0

Chip ID (CID)

(Invalid Index)

**INDEX RELOCATION REGISTER (IRR)**

Offset:

22h

Default: Access: 00100010b W/R

Bit Description:

7:0

**IRR**

(22h)

(23h)

**DATA RELOCATION REGISTER (DRR)**

Offset:

23h

Default: Access:

00100011b W/R

Bit Description:

7:0

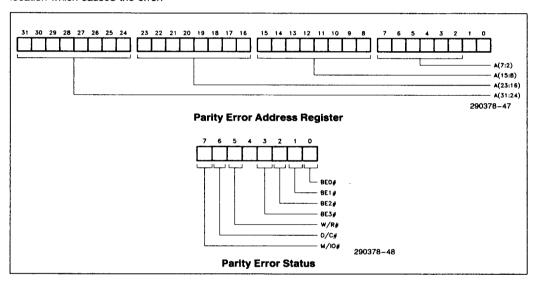

**PARITY ERROR ADDRESS REGISTER**

Offset:

2Bh:28h

DRR

Default:

(See bit descriptions)

Access:

R

Bit Description:

2Ah-

2Bh-

28h-7:2 29h-7:0

Parity Error A(7:2) Parity Error A(15:8)

7:0 Parity Error A(23:16) Parity Error A(31:24) 7:0

(000000\*\*b) (0000000b)

(00000000b)(0000000b)

1-537

| PARITY ERROR S    | TATUS REGISTER         |     | V-4       | $\neg$ |

|-------------------|------------------------|-----|-----------|--------|

| Offset:           | 2Ch                    |     |           |        |

| Default:          | 000*0000b              |     |           |        |

| Access:           | R                      |     |           |        |

| Bit Descriptions: | **                     |     |           |        |

| 3:0               | Parity Error BE(3:0) # |     | (0000)    |        |

| 5                 | Parity Error W/R#      |     | (Read)    |        |

| 6                 | Parity Error D/C#      |     | (Command) |        |

| 7                 | Parity Error M/IO#     |     | (IO)      | l      |

| ,                 | Famy Enter WillO#      |     | (10)      |        |

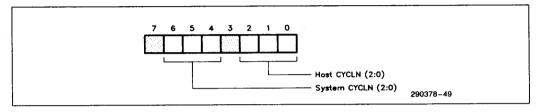

| CYCLE LENGTH R    | EGISTER-READ PAGE HIT  | Г   |           | - 1    |

| Offset:           | 30h                    |     |           |        |

| Default:          | *111*111               |     |           | 1      |

| Access:           | W/R                    |     |           |        |

| Bit Descriptions: |                        |     |           |        |

| 2:0               | Host CYCLN             | *   | (7)       |        |

| 6:4               | System CYCLN           |     | (7)       |        |

|                   |                        |     |           |        |

| 3                 | EGISTER-READ PAGE MIS  | 55  |           | ı      |

| Offset:           | 31h                    |     |           | -      |

| Default:          | *111*111               |     |           |        |

| Access:           | W/R                    |     |           |        |

| Bit Descriptions: |                        |     |           |        |

| 2:0               | Host CYCLN             |     | (7)       |        |

| 6:4               | System CYCLN           |     | (7)       |        |

| CYCLE LENGTH R    | EGISTER-READ ROW MIS   | ss  |           |        |

| Offset:           | 32h                    |     |           |        |

| Default:          | *111*111               |     |           |        |

| Access:           | W/R                    |     |           |        |

| Bit Descriptions: |                        |     |           |        |

| 2:0               | Host CYCLN             |     | (7)       |        |

| 6:4               | System CYCLN           |     | (7)       |        |

| OVOLE / ENGT:: E  | FOIOTED METT DAGE      |     |           |        |

|                   | EGISTER-WRITE PAGE H   | 11  |           |        |

| Offset:           | 33h                    |     |           | ļ      |

| Default:          | *111*111               | ı   |           |        |

| Access:           | W/R                    |     |           | 1      |

| Descriptions:     | Hank CVCI N            |     | (7)       | -      |

| 2:0               | Host CYCLN             |     | (7)       | 1      |

| 6:4               | System CYCLN           |     | (7)       |        |

| CYCLE LENGTH R    | EGISTER-WRITE PAGE M   | ISS |           |        |

| Offset:           | 34h                    |     |           |        |

| Default:          | *111*111               |     |           |        |

| Access:           | W/R                    |     |           |        |

| Bit Descriptions: |                        |     |           |        |

| 2:0               | Host CYCLN             |     | (7)       | 1      |

| 6:4               | System CYCLN           |     | (7)       |        |

|                 | REGISTER-WRITE ROW N   | <del></del> |   |  |

|-----------------|------------------------|-------------|---|--|

| Offset:         | 35h                    | 1133        |   |  |

| Default:        | *111*111               |             |   |  |

| Access:         | W/R                    |             |   |  |

| Bit Description |                        |             |   |  |

| •               |                        | (7)         |   |  |

| 2:0<br>6:4      | Host CYCLN             | (7)         |   |  |

| 0:4             | System CYCLN           | (7)         |   |  |

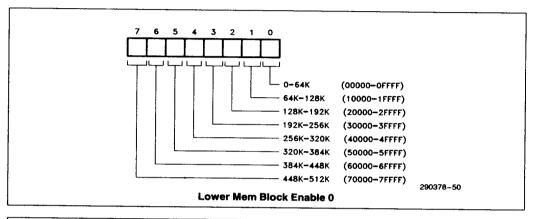

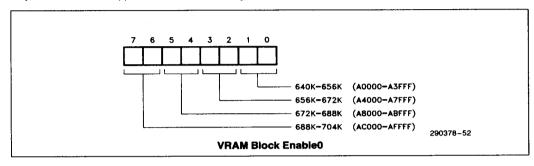

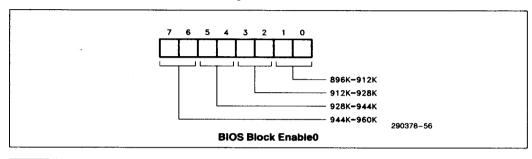

|                 | RY BLOCK ENABLE REGIST | TER 0       |   |  |

| Offset:         | 40h                    |             |   |  |

| Default:        | 11111111b              |             | • |  |

| Access:         | W/R                    |             |   |  |

| Bit Description |                        |             |   |  |

| 0               | 00000h-0FFFFh          | (Enabled)   |   |  |

| 1               | 10000h-1FFFFh          | (Enabled)   |   |  |

| 2               | 20000h-2FFFFh          | (Enabled)   |   |  |

| 3               | 30000h-3FFFFh          | (Enabled)   |   |  |

| 4               | 40000h-4FFFFh          | (Enabled)   |   |  |

| 5               | 50000h-5FFFFh          | (Enabled)   |   |  |

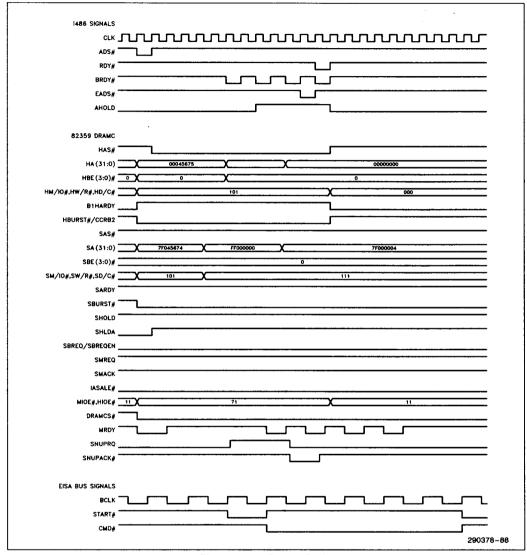

| 6               | 60000h-6FFFFh          | (Enabled)   |   |  |